Багатопортова пам’ять

Номер патенту: 23358

Опубліковано: 31.08.1998

Автори: Цмоць Іван Григорович, Рашкевич Юрій Михайлович, Демида Богдан Адамович

Формула / Реферат

Багатопортова пам'ять, яка містить модуль пам'яті, n шин даних, де n - кількість портів, до яких підключаються зовнішні пристрої, n інтерфейсних модулів, кожний з яких містить вхідний і вихідний регістри даних та лічильник адреси, при цьому в кожному І-ому інтерфейсному модулі, де i=1,...,n, інтерфейсний вхід вихідного регістра даних є І-ою шиною даних багатопортової пам'яті, яка відрізняється тим, що додатково містить n входів запису даних, n входів читання даних, n входів читання адреси, n входів запису адреси, n тактових входів і n входів вибірки, кожний із інтерфейсних модулів додатково містить чотири шинні формувачі, три елементи І та три формувачі імпульсів, кожний з яких містить п'ять тригерів, три елементи І, два елементи АБО І два елементи І-НЕ, при цьому в кожному І-ому інтерфейсному модулі І та шина даних багатопортової пам'яті з'єднана з входом лічильника адреси, з виходами вхідного регістра даних і з виходами першого шинного формувача, входи якого з'єднані з входами другого шинного формувача та з виходами лічильника адреси, синхровхід вихідного регістра з'єднаний з другим входом третього формувача імпульсів І є 1-им входом запису даних багатопортової пам'яті, вхід читання вхідного регістра з'єднаний з другим входом другого формувача імпульсів і з першим входом першого елемента І і є І-им входом читання даних багатопортової пам'яті, вхід управління першого шинного формувача є І-им входом читання адреси багатопортової пам'яті, вхід паралельного запису лічильника адреси з'єднаний з другим входом першого формувача імпульсів і є 1-им входом запису адреси багатопортової пам'яті, перші входи формувачів імпульсів з'єднані з входом управління третього шинного формувача і є І-им тактовим входом багатопортової пам'яті, вхід управління четвертого шинного формувача є І-им входом вибірки багатопортової пам'яті, вихід першого формувача імпульсів з'єднаний з першим входом другого елемента І і з другим входом третього елемента І, перший вхід якого з'єднаний з другим входом другого елемента І і з виходом другого формувача імпульсів, вихід третього формувача імпульсів з'єднаний з третім входом третього елемента І, з другим входом першого елемента І, з входом читання вихідного регістра даних І з інформаційним входом третього шинного формувача, вихід третього елемента І з'єднаний з входом управління другого шинного формувача і інформаційним входом четвертого шинного формувача, вихід другого елемента І з'єднаний з синхровходом вхідного регістра даних, вихід першого елемента І з'єднаний з синхровходом лічильника адреси, в кожному формувачі імпульсів синхровходи другого і п'ятого тригерів з'єднані з першими входами першого і другого елементів І-НЕ і є першим входом формувача імпульсів, лічильний вхід третього тригера з'єднаний з першим входом першого елемента АБО І з другим входом другого елемента АБО І є другим входом формувача імпульсів, прямий вихід третього тригера з'єднаний з другим входом першого елемента АБО, вихід якого з'єднаний з першим входом першого елемента І формувача імпульсів, другий вхід якого з'єднаний з першим входом другого елемента І формувача імпульсів І з виходом першого елемента І-НЕ, другий вхід якого з'єднаний з виходом другого тригера, інформаційний вхід якого з'єднаний з третім входом першого елемента І-НЕ і з виходом першого тригера, лічильний вхід якого з'єднаний з виходом першого елемента І формувача імпульсів, інверсний вихід третього тригера з'єднаний з першим входом другого елемента АБО, вихід якого з'єднаний з першим входом третього елемента І формувача імпульсів, другий вхід якого з'єднаний з другим входом другого елемента І формувача імпульсів І з виходом другого елемента І-НЕ, другий вхід якого з'єднаний з виходом п'ятого тригера, інформаційний вхід якого з'єднаний з третім входом другого елемента І-НЕ і з виходом четвертого тригера, лічильний вхід якого з'єднаний з виходом третього елемента І формувача імпульсів, вихід другого елемента І формувача імпульсів є виходом формувача імпульсів, виходи вихідного регістра даних з'єднані з входами вхідного регістра даних І є шиною даних інтерфейсного модуля, вихід другого шийного формувача є адресною шиною інтерфейсного модуля, вихід третього шинного формувача є першим виходом управління інтерфейсного модуля, другим виходом управління якого є вихід четвертого шинного формувача, шина даних модуля пам'яті з'єднана з шинами даних всіх інтерфейсних модулів, шини адреси яких з'єднані з шиною адреси модуля пам'яті, вхід читання-запису модуля пам'яті з'єднаний з першими виходами управління інтерфейсних модулів, другі виходи управління яких з'єднані з входом вибірки модуля пам'яті.

Текст

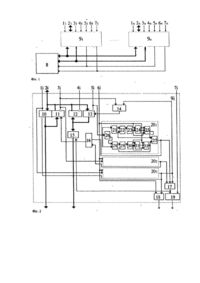

Винахід відноситься до обчислювальної техніки і може бути використаний при побудові запам'ятовуючих пристроїв паралельних ЕОМ І багатопроцесорних систем, Відомий запам'ятовуючий пристрій [Авт. св. СССР №1529287, кл. G 11 С 11/00, 1989], який містить два блоки пам'яті, два регістри, лічильник, два комутатори і тригер. Однак даний пристрій дозволяє одночасний доступ до пам'яті тільки двох користувачів, що значно обмежує область його використання. Найбільш близькою до запропонованої є багатопортова пам'ять [Жаровський С.Н., Лучук Д.А. Системная организация мультипроцессорной ЭВМ на базе многопортовой памяти // Управляющие системы и машины 1992. - №1/2 - С. 74-75], яка містить модуль пам'яті, n шин даних, де n - кількість портів до яких підключаються зовнішні пристрої, n інтерфейсних модулів, кожен з яких містить вхідний і вихідний регістри даних, лічильник адреси, при цьому в кожному і-му інтерфейсному модулі, де і=1.....n, інформаційний вхід вихідного регістра даних є і-ою шиною даних багатопортової пам'яті. Однак дана багатопортова пам'ять має великий час вибірки інформації, який рівний 3t, де t - мінімальний інтервал часу між сусідніми звертаннями до багатопортової пам'яті. В основу винаходу поставлена задача створити багатопортову пам'ять, в якій введення нових елементів і зв'язків між ними дозволило б зменшити час вибірки інформації з багатопортової пам'яті та забезпечило б простоту зміни кількості портів, Поставлена задача вирішується таким чином, що в багатопортову пам'ять, яка містить модуль пам'яті, n шин даних, де n - кількість портів, до яких підключаються зовнішні пристрої, n інтерфейсних модулів, кожний з яких містить вхідний і вихідний регістри даних та лічильник адреси, при цьому в кожному і-ому інтерфейсному модулі, де і=1,...,n, інтерфейсний вхід вихідного регістра даних є і-ою шиною даних багатопортової пам'яті, відрізняється тим, що додатково містить n входів запису даних, n входів читання даних, n входів читання адреси, n входів запису адреси, n тактових входів і n входів вибірки, кожний із інтерфейсних модулів додатково містить чотири шинні формувачі, три елементи І та три формувачі імпульсів, кожний з яких містить п'ять тригерів, три елементи І, два елементи АБО і два елементи І-НЕ, при цьому в кожному і-ому інтерфейсному модулі і та шина даних багатопортової пам'яті з'єднана з входом лічильника адреси, з виходами вхідного регістра даних І з виходами першого шинного формувача, входи якого з'єднані з входами другого шинного формувача та з виходами лічильника адреси, синхровхід вихідного регістра з'єднаний з другим входом третього формувача імпульсів і є і-им входом запису даних багатопортової пам'яті, вхід читання вхідного регістру з'єднаний з другим входом другого формувача імпульсів і з першим входом першого елемента І і є і-им входом читання даних багатопортової пам'яті, вхід управління першого шинного формувача є і-им входом читання адреси багатопортової пам'яті, вхід паралельного запису лічильника адреси з'єднаний з другим входом першого формувача імпульсів і є і-им входом запису адреси багатопортової пам'яті, перші входи формувачів імпульсів з'єднані з входом управління третього шинного формувача І є і-им тактовим входом багатопортової пам'яті, вхід управління четвертого шинного формувача є і-им входом вибірки багатопортової пам'яті, вихід першого формувача імпульсів з'єднаний з першим входом другого елемента І і з другим входом третього елемента І, перший вхід якого з'єднаний з другим входом другого елемента І і з виходом другого формувача імпульсів, вихід третього формувача імпульсів з'єднаний з третім входом третього елемента І, з другим входом першого елемента І, з входом читання вихідного регістра даних І з інформаційним входом третього шинного формувача, вихід третього елемента І з'єднаний з входом управління другого шинного формувача і інформаційним входом четвертого шинного формувача, вихід другого елемента І з'єднаний з синхровходом вхідного регістра даних, вихід першого елемента І з'єднаний з синхровходом лічильника адреси, в кожному формувачі імпульсів синхровходи другого і п'ятого тригерів з'єднані з першими входами першого і другого елементів І-НЕ і є першим входом формувача імпульсів, лічильний вхід третього тригера з'єднаний першим входом першого елемента АБО і з другим входом другого елемента АБО і є другим входом-формувача імпульсів, прямий вихід третього тригера з'єднаний з другим входом першого елемента АБО, вихід якого з'єднаний з першим входом першого елемента і формувача імпульсів, другий вхід якого з'єднаний з першим входом другого елемента і формувача імпульсів і з виходом першого елемента І-НЕ, другий вхід якого з'єднаний з виходом другого тригера, інформаційний вхід якого з'єднаний з третім входом першого елемента І-НЕ і з виходом першого тригера, лічильний вхід якого з'єднаний з виходом першого елемента І формувача імпульсів, інверсний вихід третього тригера з'єднаний з першим входом другого елемента АБО, вихід якого з'єднаний з першим входом третього елемента І формувача імпульсів, другий вхід якого з'єднаний з другим входом другого елемента І формувача імпульсів і з виходом другого елемента І-НЕ, другий вхід якого з'єднаний з виходом п'ятого тригера, інформаційний вхід якого з'єднаний з третім входом другого елемента І-НЕ і з виходом четвертого тригера, лічильний вхід якого з'єднаний з виходом третього елемента І формувача імпульсів, вихід другого елемента І формувача імпульсів є виходом формувача імпульсів, виходи вихідного регістра даних з'єднані з входами вхідного регістра даних і є шиною даних інтерфейсного модуля, вихід другого шинного формувача є адресною шиною інтерфейсного модуля, вихід третього шинного формувача є першим виходом управління інтерфейсного модуля, другим виходом управління якого є вихід четвертого шинного формувача, шина даних модуля пам'яті з'єднана з шинами даних всіх інтерфейсних модулів, шини адреси яких з'єднані з шиною адреси модуля пам'яті, вхід читання-запису модуля пам'яті з'єднаний з першими виходами управління інтерфейсних модулів, другі виходи управління яких з'єднані з входом вибірки модуля пам'яті. Ведення додатково в кожний інтерфейсний модуль чотирьох шинних Формувачів, трьох елементів І та трьох формувачів імпульсів, кожен з яких містить два елементи АБО, три елементи І, два елементи І-НЕ і п'ять тригерів, забезпечило часовий розподіл ресурсу пам'яті в заданих пропорціях між асинхронно працюючими пристроями та попереднє читання інформації з пам'яті в вхідний регістр І, тим самим, дозволило зменшити час вибірки інформації з багатопортової пам'яті до часу спрацювання регістру. На фіг.1 представлена схема багатопортової пам'яті; на фіг.2 - схема інтерфейсного модуля, Багатопортова пам'ять містить n входів запису даних 11,...,1n, n шин даних 21,...,2n, n входів читання даних 31,...,3n, n входів читання адреси 41,...,4n, n входів запису адреси 51,...,5n, n тактових входів 61.....6n, n входів вибірки 71.....7n, модуль пам'яті 8, n інтерфейсних модулів 91,...,9n, кожен з яких містить вихідний регістр даних 10, вхідний регістр даних 11, перший шинний формувач 12, лічильник адреси 13, перший елемент І 14, другий шинний формувач 15, другий 16 і третій 17 елементи І, третій 18 і четвертий 19 шинні формувачі, перший 201, другий 202 і третій 203 формувачі імпульсів, кожний з яких містить перший елемент АБО 21, перший елемент І 22, перший 23 і другий 24 тригери, перший елемент І-НЕ 25, третій тригер 26, другий елемент І 27, другий елемент АБО 28, третій елемент І 29, четвертий 30 і п'ятий 31 тригери та другий елемент І-НЕ 32. Шина даних модуля пам'яті 8 з'єднана з шинами даних всіх інтерфейсних модулів 91,...,9n, шини адреси яких з'єднані з шиною адреси модуля пам'яті 8, вхід читання-запису якого з'єднаний з першими виходами управління інтерфейсних модулів 91.....9n, другі виходи управління яких з'єднані з входом вибірки модуля пам'яті 8, в кожному і-ому інтерфейсному модулі 9i інформаційний вхід регістра 10 з'єднаний з виходом регістра 11, з виходом шинного формувача 12, з входом лічильника 13 і з і-ою шиною даних, 2i багатопортової пам'яті, синхровхід регістра 10 з'єднаний з другим входом формувача імпульсів 203 і з і-им входом запису даних 1i багатопортової пам'яті, вхід читання регістра 11 з'єднаний з другим входом формувача імпульсів 202, з першим входом елемента І 14 і з і-им входом читання даних 3і багатопортової пам'яті, вхід управління шинного формувача 12 з'єднаний з і-им входом читання даних 4, багатопортової пам'яті, вхід паралельного запису лічильника 13 з'єднаний з другим входом формувача імпульсів 20і і з і-им входом запису адреси 5і багатопортової пам'яті, вхід управління шинного формувача 18 з'єднаний з першими входами формувачів імпульсів 201, 202, 203 і з і-им тактовим входом 6і багатопортової пам'яті, вхід шинного формувача 19 з'єднаний з і-им входом вибірки багатопортової пам'яті, вихід регістра 10 з'єднаний з інформаційним входом регістра 11 і є шиною даних інтерфейсного модуля, вихід шинного формувача 15 є адресною шиною інтерфейсного модуля, вихід лічильника адреси 13 з'єднаний з входами шинних формувачів 12 і 15, синхровхід лічильника адреси 13 з'єднаний з виходом елемента І 14, другий вхід якого з'єднаний з виходом формувача імпульсів 203, з входом шинного формувача 18, з третім входом елемента І 17 і з входом читання регістра 10, вихід формувача імпульсів 201, з'єднаний з другим входом елемента І 17 і першим входом елемента І 16, вихід якого з'єднаний з синхровходом регістра 11, вихід формувача імпульсів 202 з'єднаний з першим входом елемента І 17 і з другим входом елемента І 16, вихід елемента І 17 з'єднаний з входом управління шинних формувачів 15 і 19, вихід шинного формувача 18 є першим виходом управління інтерфейсного модуля, другим виходом управління якого є вихід шинного формувача 19, в формувачах імпульсів 201, 202, і 203 синхровходи тригерів 24 і 31 з'єднані з першими входами елементів І-НЕ 25 і 32 і є першими входами формувачів імпульсів 201, 202, 203, другими входами яких є лічильний вхід тригера 26, який з'єднаний з першим входом елемента АБО 21 і з другим входом елемента АБО 28, перший вхід якого з'єднаний з інверсним виходом тригера 26, прямий вихід якого з'єднаний з другим входом елемента АБО 21, вихід якого з'єднаний з першим входом елемента І 22, другий вхід якого з'єднаний з першим входом елемента І 27 і з виходом елемента І-НЕ 25, другий вхід якого з'єднаний з виходом тригера 24, інформаційний вхід якого з'єднаний третім входом елемента І-НЕ 25 і з виходом тригера 23, лічильний вхід якого з'єднаний з виходом елемента І 22, вихід елемента АБО 28 з'єднаний з першим входом елемента І 29, другий вхід якого з'єднаний з другим входом елемента І 27 і виходом елемента І-НЕ 32, другий вхід якого з'єднаний з виходом тригера 31, інформаційний вхід якого з'єднаний з третім входом елемента І-НЕ 32 і з виходом тригера 30, лічильний вхід якого з'єднаний з виходом елемента І 29, вихід елемента І 27 в формувачах імпульсів 201, 202, 203 є виходом даних формувачів імпульсів. Багатопортова пам'ять працює наступним чином. Зовнішні пристрої підключаються до багатопортової пам'яті через інтерфейси! модулі 91,...,9n, які фіксують сигнали управління від зовнішніх пристроїв та у виділені моменти часу надають можливість доступу до модуля пам'яті 8. На i-ий тактовий вхід 6i, та i-ий вхід вибірки 7i кожного i-го iнтерфейсного модуля 9i поступають безперервні додатні імпульси з періодом повторення рівним: Тп=Тмп х n, де Тмп - період звертання до модуля пам'яті 8. Тривалість імпульсів, що поступають на тактові входи 61,...,6n та входи вибірки 71,...,7n рівна відповідно часу Тмп і часу запису (читання) інформації в модуль пам'яті 8. На і-ий тактовий вхід 6і та і-ий вхід вибірки 7і поступають імпульси з затримкою в часі відносно імпульсів на першому тактовому вході 61 і першому вході вибірки 71 рівною: tзат.і = (і-1) x Tмп. Така затримка імпульсів в часі дозволяє рівномірно розділити часовий ресурс модуля пам'яті 8 між інтерфейсними модулями 91,...,9n, при якому кожний і-ий інтерфейсний модуль 9і може за час одного періоду Тп звернутись одни раз до модуля пам'яті 8. Кожний і-ий зовнішній пристрій може виконувати запис або читання інформації з багатопортової пам'яті як послідовно, так і масивами. При послівному звертанні до багатопортової пам'яті і-го зовнішнього пристрою кожний запис або читання інформації вимагає попереднього запису адреси в лічильник 13 і-го інтерфейсного модуля 9і. При записуванні або читанні масиву інформації і-им зовнішнім пристроєм з багатопортової пам'яті попередній запис адреси: в лічильник 13 і-го інтерфейсного модуля 9і виконується одни раз на початку записування або читання масива. Процес попереднього запису адреси, за якою буде здійснюватися читання або запис інформації в модуль пам'яті 8 для 1-го зовнішнього пристрою, виконується наступним чином. Перед початком запису або читання Інформації з багатопортової пам'яті і-им зовнішнім пристроєм в лічильник 13 і-го інтерфейсного модуля 9і необхідно записати адрес. Для цього необхідно на і-ту шину даних 2і подати адрес, а на і-ий вхід запису адреси 5і - імпульс від'ємної полярності. По приходу на вхід запису лічильника 13 імпульса від'ємної полярності виконується запис адреси з шини даних 2і в лічильник 13, крім цього даний імпульс поступає на другий вхід формувача імпульсів 201. Формувачі імпульсів 201, 20 2, 203 призначені для фіксації сигналів, що поступають на другі входи та для формування одиночних імпульсів від'ємної полярності тривалістю приблизно рівною тривалості додатнього імпульса з тактового входу 6і. Розглянемо роботу одного з трьох формувачів імпульсів 20k, де k=1, 2, 3, Перед початком поступлення імпульсів на другий вхід формувача імпульсів 20k тригери 23, 30 знаходяться в стані лог. 0. По передньомуфронту (перепаду рівня сигналу з лог. 0 в лог. 1) від'ємного імпульсу, що поступає на другий вхід формувача імпульсів 20k в залежності від стану тригера 26 виконується переключення в одиницю тригера 23 (тригер 26 - в стані лог. 0) або тригера 30 (тригер 26 - в стані лог. 1) та зміна стану тригера 26 на протилежний. Сигнал лог. 1 з виходу тригера 23 (тригера 30) поступає на інформаційний вхід тригера 24 (тригера 31) і переднім фронтом додатнього імпульсу, що поступає на перший вхід формувача імпульсів 20k, записується в даний тригер. Рівень лог. 1 на другому і третьому входах елемента І-НЕ 25 (елемента І-НЕ 26) дозволяє формування на його виході від'ємного імпульсу приблизно рівного за тривалістю імпульсу, що поступає на його перший вхід. Імпульс від'ємної полярності з виходу елемента І-НЕ 25 (елемента І-НЕ 26) поступає через елемент і 27 на вихід формувача імпульсів 20k, а також проходить через елемент І 22 (елемент І 29) і переднім фронтом переключає тригер 23 (тригер 30) в стан. лог. 0. По приходу наступних від'ємних імпульсів на другий вхід формувача імпульсів 20к він працює аналогічно. Після запису адреси в лічильник 13 виконується формування сигналів для читання інформації з модуля пам'яті 8 в регістр 11. Імпульс від'ємної полярності, що сформувався на виході формувача імпульсів 201, поступає на вхід елемента I 17 і встановлює на його виході сигнал лог. 0, який дозволяє передачу інформації з лічильника 13 через шинний формувач 15 на шину адреси модуля пам'яті 8. Сигнал лог. 1 з тактового входу 6i та входу вибірки 7i дозволяють передачу через шинний формувач 18 сигналу лог. 1 з виходу формувача імпульсів 203, а через шинний формувач 19 - лог. 0 з виходу елемента І 17. Інформація з виходів шинних формувачів 18 і 19 поступає на входи відповідно читання-запису та вибірки модуля пам'яті 8. Дана інформація встановлює модуль пам'яті 8 в режим читання. Інформація, яка зчитується з модуля пам'яті 8, поступає на вхід регістра 11 і переднім фронтом імпульса з виходу елемента І 16 записується в даний регістр. Розглянемо процес читання інформації за попередньо записаною адресою з багато-портової пам'яті і-им зовнішнім пристроєм. Для читання інформації необхідно на і-ий вхід читання даних 3і подати імпульс від'ємної полярності. Даний імпульс поступає на вхід читання регістра 11 і дозволяє передачу інформації з виходів даного регістра 11 на іту шину даних 2і, тобто здійснюється зчитування інформації за раніше записаною адресою. Крім цього, імпульс читання поступає на другий вхід другого формувача імпульсів 202 та на перший вхід елемента І 14. Переднім фронтом імпульса з виходу елемента І 14 збільшується вміст лічильника 13 на одиницю. На виході другого формувача імпульсів 20г формується від'ємний імпульс, який поступає на входи елементів І 16 і 17 та встановлює їх виходи в нуль. Сигнал лог. 0 з виходу елемента І 17 поступає на вхід управління шинного формувача 15 і дозволяє передачу на шину адреси інформації з виходів лічильника 13. Сигнали лог. 1 з 1-го тактового входу 6і та і-го входу вибірки 7і поступають на входи управління шинних формувачів 18, 19 і дозволяють передачу інформації через дані шинні формувачі на входи читання-запису і вибірки модуля пам'яті 8. Інформація з виходів шинних формувачів 18 (лог. 1) і 19 (лог. 0) встановлює модуль пам'яті 8 в режим читання. Інформація, яка зчитується з модуля пам'яті 8, поступає на вхід регістра 11 і переднім фронтом імпульса з виходу елемента І 16 записується в даний регістр. На цьому процедура зчитування одного слова за попередньо записаною адресою закінчується. У випадку коли зчитується масив інформації, елементи якого записані в модулі пам'яті 8 за послідовними адресами, то читання наступних елементів масиву виконується аналогічно. Попередній запис адреси та попереднє читання інформації з модуля пам'яті 8 дозволили зменшити час вибірки інформації з багатопортової пам'яті до часу спрацювання регістра. Запис інформації і-им зовнішнім пристроєм в багатопортову пам'ять за раніше записаною адресою здійснюється наступним чином. Інформація, яку необхідно записати в пам'ять, подається на І-ту шину даних 2і. Сигнал запису від'ємної полярності з і-го входу запису даних 1і поступає на синхровхід регістра 10 і на другий вхід третього формувача імпульсів 203. Переднім фронтом сигналу запису інформація з шини даних 2і записується в регістр 10. На виході третього формувача 203 формується імпульс від'ємної полярності, який поступає на другий вхід елемента І 14, на третій вхід елемента І 17, на вхід читання регістра 10 і на інформаційний вхід шинного формувача 18. Сигнал лог. 0 на входах читання регістра 10 і управління шинним формувачем 15 встановлює їх на передачу інформації відповідно на шину даних і шину адреси модуля пам'яті 8. Сигнали лог. 1 з і-го тактового входу 6і та і-го входу вибірки 7і поступають на входи, управління шинних формувачів 18, 19 і дозволяють передачу інформації через дані шинні формувачі на входи читання-запису і вибірки модуля пам'яті 8. Інформація з виходів шинних формувачів 18 (лог. 0) і 19 (лог. 0) встановлює модуль пам'яті 8 в режим запису. По переходу сигналів запису-читання І вибірки пам'яті в одиницю інформація з виходу інтерфейсного модуля 9і записується в модуль пам'яті 8 за адресою, яка встановилася на адресних виходах даного інтерфейсного модуля 9і. Переднім фронтом сигналу з вихода елемента І 14 вмістиме лічильника 13 збільшується на одиницю. На цьому процедура запису одного слова за попередньо записаною адресою закінчується. У випадку коли записується масив інформації - запис наступних елементів буде проводитись аналогічно за послідовними адресами. Кожний і-ий зовнішній пристрій може зчитати інформацію з лічильника 13 і-го інтерфейсного модуля 9і. Для зчитування вмісту лічильника 13 необхідно на і-ий вхід читання адреси подати від'ємний імпульс, який дозволить передачу інформації з виходів лічильника 13 через шинний формувач 12. Інформація з виходів шинного формувача 12 поступає на і-ту шину даних, тобто виконується читання вмісту лічильника 13 (адреси) і-им зовнішнім пристроєм.

ДивитисяДодаткова інформація

Назва патенту англійськоюMultiport memory device

Автори англійськоюDemyda Bohdan Adamovych, Rashkevych Yurii Mykhailovych, Tsmots Ivan Hryhorovych

Назва патенту російськоюМногопортовое запоминающее устройство

Автори російськоюДемида Богдан Адамович, Рашкевич Юрий Михайлович, Цмоць Иван Григорьевич

МПК / Мітки

МПК: G11C 11/00

Мітки: пам'ять, багатопортова

Код посилання

<a href="https://ua.patents.su/4-23358-bagatoportova-pamyat.html" target="_blank" rel="follow" title="База патентів України">Багатопортова пам’ять</a>

Попередній патент: Буферний запам’ятовуючий пристрій

Наступний патент: Спосіб одержання консервованих томатів

Випадковий патент: Литьова форма для виготовлення виробів з пластмас з піднутренням