Пристрій затримки імпульсних сигналів

Номер патенту: 31880

Опубліковано: 25.04.2008

Автори: Столяр Володимир Володимирович, Яновський Фелікс Йосипович

Формула / Реферат

Пристрій затримки імпульсних сигналів, який містить генератор тактових імпульсів, вихід якого підключений до входу блока формування керуючих сигналів, перший вихід якого з'єднаний з лічильним входом лічильника, другий та третій виходи з'єднані відповідно з входами "Зчитування-запис" першого та другого оперативних запам'ятовуючих пристроїв (ОЗП), часозадавальний блок, підключений до лічильника, виходи якого з'єднані з адресними входами першого ОЗП, інформаційні входи першого та другого ОЗП з'єднані між собою і є входом пристрою, виходи першого та другого ОЗП з'єднані відповідно з входами першого та другого формувачів імпульсів, відповідні виходи яких з'єднані з входами елемента АБО, вихід якого є виходом пристрою, який відрізняється тим, що в нього введено регістр запам'ятовування, виходи якого підключені до адресних входів другого ОЗП, вхід "Запис" якого підключений до четвертого виходу блока формування керуючих сигналів, а інформаційні входи регістра підключені до виходів лічильника.

Текст

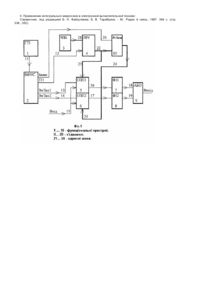

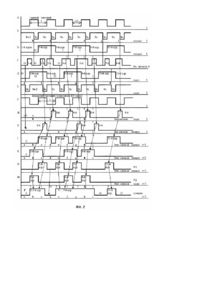

Корисна модель відноситься до імпульсної техніки, автоматики, обчислювальної техніки, радіотехніки, радіолокації, телемеханіки, техніки зв'язку, а саме до пристроїв декодування імпульсних послідовностей, і може бути використана в пристроях обробки інформації. Відомий пристрій дискретної лінії затримки, що містить генератор тактових імпульсів, блоки управління, лічильники імпульсів, запам'ятовуючий пристрій (ЗП), підсилювачі, формувачі імпульсів та датчик коду [1]. Недоліком пристрою є те, що використання в цьому пристрої окремих ліній з'єднання зчитування та запису, запис в ЗП інформації про кількість імпульсів генератора, які поступили у проміжку часу між імпульсами вхідної послідовності, що обумовлено використанням багато розрядного ЗП, а також відсутність багатократного використання для запису імпульсів, вужчих від стандартних чарунок пам'яті, збільшують апаратурні затрати, знижують надійність і призводять до лінійної залежності необхідного об'єму ЗП від величини затримки. При цьому для його реалізації необхідно: 5 лічильників, 2 блоки управління, 2 підсилювачі, 4 формувачі імпульсів, 1 генератор тактових імпульсів, 3 тригери, дешифратор і 3 елемента “I” Порівняння аналога-пристрою [1] та прототипа-пристрою [2] показує, що аналог дуже складний. Тому, що в двоканальному пристрої-прототипі використовують значно менше комплектуючих виробів: 2 лічильники, 2 формувачі імпульсів, 1 генератор тактових імпульсів і 1 блок управління. Відомий також, вибраний як прототип, пристрій затримки імпульсних сигналів [2], що містить, як і заявлений пристрій, генератор тактових імпульсів і блок пам'яті, підключений відповідними входами до виходу вхідного блока, вхід якого є входом пристрою, блок формування сигналів "Зчитування-запис", два формувачі, елемент АБО, фазозсуваючий блок, підключений входом до виходу генератора тактових імпульсів, два п-розрядних лічильники, виходи яких з'єднані з адресними входами блока пам'яті, який має два оперативних запам'ятовуючих пристрої, та час-задаючий блок, входи якого з'єднані з одним із n-розрядних лічильників, а вихід з'єднаний з установочними входами лічильників, при цьому одні виходи фазозсуваючого блока з'єднані із лічильними входами п-розрядних лічильників та першими входами формувачів, а другі - з входами блока формування сигналів "Зчитування-запис", виходи блока формування сигналів "Зчитування-запис" з'єднані з входами "Зчитування-запис" блока пам'яті, виходи якого з'єднані з другими входами формувачів, а виходи останніх з'єднані з входами елемента АБО, вихід якого є виходом пристрою. У цьому пристрої використовуються МС 155ИЕ7 або 133ИЕ7 - 4-х - розрядні лічильники, які є лічильниками із наскрізним переносом. Вони можуть рахувати поступаючі тактові сигнали в режимах прямого та зворотного відліку. Така МС має 16 виводів: 4 Д-входи, 1 вхід попереднього запису, 1 вхід установки в "0" 2- лічильні входи прямого та зворотного відліку та 2 входи прямого та зворотного переносу, 4 виходи, та 2 виходи для підключення напруги, всього 16 виходів, (див. стр. 338-342 Справочника) [4]. Таким чином зрозуміло, що усі виводи МС 155ИЕ7 - задіяні. Крім того, МС 155ИЕ7[4] споживає значну потужність. Наявність лічильника (МС 155ИЕ7) впливає на кількість МС, які задіяні в пристрої, перешкоджає подальшому зменшенню загальної кількості МС. Уведення регістра запам'ятовування, який виконаний на МС 155ТМ9, замість одного із лічильників, виконаного на МС 155ИЕ7 дозволяє зменшити кількість мікросхем та знизити енергетичні витрати. Порівняння показує, що якщо в пристрої-прототипі [2] перший та другий лічильники мають 12 розрядів, а в якості адресних лічильників використовуються по 3 МС 155ИЕ7 [4] - 1-й та 2-й лічильники - всього 6 МС, перший 12- адресний ОЗП - 1 МС РУ470[4] та мультиплексор 3 МС 533КП16[4], то всього необхідно 10 МС. 2)В заявленому пристрої, якщо перший лічильник має 12 розрядів (3 МС), а введений 12 - розрядний регістр (замість другого лічильника), використовує 2 МС 155ТМ9[4]- кожна МС має шість розрядів, перший та другий 12-адресний ОЗП - 2 МС РУ470[4]. Всього це буде 7 МС. Порівняння пунктів 1) та 2) показує, що при цьому швидкодія цього пристрою збільшується вдвічі, а кількість МС зменшується на 3 МС по відношенню до пристрою-прототипу [2]. 3)Якщо порівняти одно-канальний пристрій [2], який би реалізувався як двох-канальний пристрій, аналогічний одно канальному, то двох-канальний пристрій би мав 24 МС, в той час, як необхідна кількість МС у заявленому пристрої складає 7 МС, тобто зменшена втричі. Задачею корисної моделі є удосконалення пристрою затримки імпульсних сигналів шляхом уведення регістра запам'ятовування, виходи якого підключені до адресних входів другого ОЗП, вхід "Запис" якого підключений до шостого виходу БФУС, а інформаційні входи регістра підключені до виходів лічильника, що забезпечить зменшення апаратно - потужністних витрат та підвищення вдвічі швидкодії та розділової здатності пристрою. Уведення регістра запам'ятовування МС 155ТМ9 замість лічильника МС 155ИЕ7 дозволяє зменшити кількість мікросхем та знизити енергетичні витрати. Поставлена задача вирішується тим, що в пристрій затримки імпульсних сигналів, який містить генератор тактових імпульсів, вихід якого підключений до входу блоку формування управляючих сигналів, перший вихід якого з'єднаний з лічильним входом лічильника, другий та третій виходи з'єднані відповідно з входами "Зчитування-запис" першого та другого оперативних запам'ятовуючих пристроїв (ОЗП), час-задаючий блок, підключений до лічильника, виходи якого з'єднані з адресними входами першого ОЗП, інформаційні входи першого та другого ОЗП з'єднані між собою і є входом пристрою, виходи першого та другого ОЗП з'єднані відповідно з входами першого та другого формувачів імпульсів, відповідні виходи яких з'єднані з входами елемента АБО, вихід якого є виходом пристрою, згідно з корисною моделю, в нього введено регістр запам'ятовування, виходи якого підключені до адресних входів другого ОЗП, вхід "Запис" якого підключений до четвертого виходу блоку формування управляючих сигналів, а інформаційні входи регістра підключені до виходів лічильника. Уведення в пристрій регістра запам'ятовування, виходи якого підключені до адресних входів другого ОЗП, вхід "Запис" якого підключений до четвертого виходу БФУС, а інформаційні входи регістра підключені до виходів лічильника, вигідно відрізняє запропонований пристрій затримки імпульсних сигналів від прототипу, оскільки збільшує вдвічі швидкодію та розділову здатність пристрою та вдвічі зменшує похибку величини затримки сигналів. В результаті цього підвищується точність формування величини затримки вхідних сигналів та зменшення апаратно - потужністних затрат, за рахунок зменшення кількості мікросхем, та підвищення пропускної здатності потоків вхідних імпульсних сигналів вдвічі. Наприклад, для реалізації 24 розрядного регістра запам'ятовування необхідно 3 МС 155ИР13, а 24розрядного лічильника - 6 МС 155ИЕ7. Всього 9 МС. Для порівняння: при реалізації двох-канального способу згідно прототипу - пристрою необхідно: мультиплексор - 6 МС 155КП16, перший - 6 МС та другий - 6 МС лічильники - всього 12 МС 155ИЕ7. Сумарно це буде складати 18 МС. Порівняння показує, що варіант, з використанням МС 155ИР13 має удвічі кращі показники як по кількості елементів, так і по апаратно-потужністним затратам. Суть корисної моделі пояснюється кресленнями, де зображені: - на Фіг.1 - функціональна схема заявленого пристрою затримки імпульсних сигналів, - на Фіг.2 - епюри електричних сигналів, які пояснюють принцип дії пристрою. Для пояснення суті корисної моделі нижче наведено приклад конкретного виконання пристрою затримки імпульсних сигналів. Приклад ілюструється кресленням, на якому схематично показано зазначений пристрій. Креслення, що пояснює Корисна модель, а також нижченаведені приклади конкретного виконання способу і пристрою для його здійснення ніяким чином не обмежують обсяг домагань, викладений у формулі, а тільки пояснюють суть корисної моделі. Як показано на Фіг.1 пристрій затримки імпульсних сигналів містить генератор 1 тактових імпульсів (ГТІ), вихід 11 якого підключений до входу БФУС 2, перший 12 вихід якого з'єднаний з лічильним входом лічильника 4 (ЛІЧ), другий 13 та третій 14 виходи з'єднані відповідно з входами 13 "3ч/3ап" першого 5 ОЗП1 та 14 "3ч/3ап2" другого б ОЗП2, час-задаючий 3 блок, підключений 21 до лічильника 4, виходи якого з'єднані з адресними 23 входами ОЗП1, інформаційні 15 входи ОЗП1 та ОЗП2 з'єднані між собою і є входом пристрою, виходи 16 та 77 першого ОЗП1 та другого ОЗП2 з'єднані відповідно з входами першого 7 та другого 8 формувачів імпульсів ФІ1 та ФІ2, відповідні виходи яких 18 та 79 з'єднані з входами елемента 9 АБО, вихід якого є виходом пристрою, регістр 10 запам'ятовування (РгЗпм), виходи 24 якого підключені до адресних входів другого ОЗП2, вхід "Запис" якого підключений до четвертого 20 виходу БФУС, а інформаційні 22 входи регістра 10 підключені до виходів лічильника 4. На діаграмах А), Б) і В) показані: тактові сигнали, сигнали Зч/Зп1 з періодом чередування та адресні сигнали першого потоку сигналів (непарні). На діагр. Г) зображені вхідні сигнали. На діагр. Д), Е) і Є) показані: адресні сигнали, сигнали Зч/Зп2 з періодом чередування та тактові сигнали другого потоку сигналів (парні). На діагр. Ж) і 3) показані імпульсні сигнали, які записані у відповідні чарунки першого (3-й, 4-й, 5-й та 8-й імпульси) та другого (2-й, 5-й та 6-й імпульси) потоків сигналів. На діаграмах А), Б), В), Г), Д), Е), Є), Ж) і 3) показані сигнали в поточному часі t. На діагр. І) та К) показані адреси чарунок, в які записані відповідні імпульсні сигнали першого (3-я, 5-а, 7-а та 11-а) та другого (2-а, 6-а, та 8-а) потоків сигналів. затримані на час t + T. На діагр. Л) і М) показані затримані на час t + T імпульсні сигнали, сформовані на виходах першого (3-й, 5-й, 7-й та 11-й) та другого (2-й, 6-й, та 8-й) формувачів імпульсів. На діагр. Н) показані об'єднані та затримані на час t + T імпульсні сигнали, які сформовані на виходах першого та другого формувачів імпульсів. На діагр. І), К), Л) М) і Н) показані поточні затримані на час Т сигнали в часі (t + T). Примітка: діаграми, зображені на рис.2 носять пояснюючий характер і в реальних умовах, при технічній реалізації можуть відрізняться від приведених по полярності, амплітуді та фазі. Пристрій працює таким чином. Генератор 7 генерує тактові імпульси типу меандр (діагр. А), які поступають на вхід БФУС 2, на виходах якого формуються наступні управляючі сигнали: тактові сигнали 1) "Запис" - для запису інформації в регістр 10 запам'ятовування (діагр. Є); 2)ТІ – типу меандр, для формування часового інтервалу затримки за допомогою лічильника 4 (діагр. Є), “Зч/'Зч/Зап1” (діагр. Б) та 4)"3ч/3ап2" (діагр. Е) - для забезпечення зчитування та запису вхідної інформації у відповідні ОЗП1 та ОЗП2. Так як час-задаючий 3 блок, підключений до лічильника 4, то лічильник рахує наперед задану кількість N імпульсів. Це означає що в першому 5 ОЗП1 та другому 6 ОЗП2 перебирається відповідна кількість N чарунок, причому Т і N зв'язані наступною формулою: T = Nx1/f T = Nxt де f T - частота тактових імпульсів, - період чередування тактових імпульсів. Одночасно на інформаційні входи першого 5 ОЗП1 та другого 6 ОЗП2, які з'єднані між собою входами і є входом пристрою, поступають вхідні сигнали(діагр. Г), які асинхронними сигналами "Зч/Зап1 "(діагр. Б) та "Зч/3ап2"(діагр. Е) спочатку зчитують із відповідних чарунок, а потім записують в ці чарунки нову інформацію. Далі, через час Т, затримані сигнали поступають відповідно на входи першого 7 ФІ1 та другого 8 ФІ2 формувачів імпульсів (діагр. Л та М), які формують імпульси наперед заданої тривалості, які поступають на відповідні входи елемента 9 АБО та об'єднуються на його виході (діагр. Н), який є виходом пристрою. На інформаційні входи регістра 10 запам'ятовування (РгЗпм) поступають сигнали з виходів лічильника 4, які під дією тактових сигналів "Запис" БФУС запам'ятовують стан лічильника 4. З виходів регістра 10 РгЗпм сигнали поступають адресні входи ОЗП2, якими перебирається відповідна кількість чарунок другого потоку. Далі управляючі сигнали поступають відповідно на рахунковий вхід п-розрядного лічильника 4, вхід БФУС 2 "Зч/Зап", та вхід ТІ2 регістра 10 запам'ятовування. При цьому БФУС 3 "Зч/Зап" формує відповідні сигнали, які поступають на входи зчитування/запис ОЗП1 та ОЗП2, на об'єднані входи яких поступають інформаційні сигнали, і у відповідності з вибраною адресою записуються в ці ОЗП. При цьому перебирання чарунок ОЗП1 здійснюється лічильником 4, а перебирання чарунок ОЗП2 - регістром 10 РгЗпм, інформаційні входи якого підключені до виходів ЛІЧ 4. Блок БФУС 3 формує сигнали, які забезпечують роботу ОЗП. Час-задаючий 3 блок формує через відповідний часовий інтервал сигнал установки. Джерела інформації 1. А.с. №961123 Н 03Н 7/30, 23.09.1982 2. А.с. №1769357 Н ОЗК 5/13, 14.08.1989 3. А.с. №1182647 Н ОЗК 5/13, 23.08.1982 4. Применение интегральньїх микросхем в злектронной вьічислительной технике: Справочник, под редакцией Б. Н. Файзулаева, Б. В. Тарабрина. - М.: Радио й связь, 1987. 384 с. (стр. 338...352).

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for pulse signal delaying

Автори англійськоюStoliar Volodymyr Volodymyrovych, Yanovskyi Felix Yosypovych

Назва патенту російськоюУстройство задержки импульсных сигналов

Автори російськоюСтоляр Владимир Владимирович, Яновский Феликс Иосифович

МПК / Мітки

МПК: H03K 5/135

Мітки: затримки, імпульсних, пристрій, сигналів

Код посилання

<a href="https://ua.patents.su/4-31880-pristrijj-zatrimki-impulsnikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій затримки імпульсних сигналів</a>

Попередній патент: Ергатична система з контуром стабілізації параметрів стану біологічної складової

Наступний патент: Спосіб екстракорпоральної корекції гомеостазу

Випадковий патент: Пристрій для регулювання навантаження на ведучі осі шахтного локомотива