Символьний процесор

Номер патенту: 42590

Опубліковано: 15.09.2003

Автори: Дергачов Володимир Андрійович, Чумаченко Ігор Володимирович, Жихарев Володимир Якович, Світличний Олександр Володимирович, Кас'ян Ольга Викторівна

Формула / Реферат

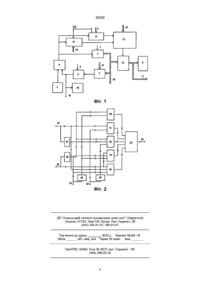

1. Символьний процесор, що має вхід запуску, першу інформаційну шину, генератор імпульсів, двійковий лічильник, тригер, схему порівняння, елемент І, блок пам'яті, сигнальний вихід, шину результату, вхід «скидання», з'єднаний з входом скидання двійкового лічильника, який відрізняється тим, що містить демультиплексор, операційний блок, перший і другий регістри зсуву, другу інформаційну шину, шину потужності множини, індикатор, шину коду операції, шину адреси, вхід «запис», причому вхід запуску з'єднаний з входом установки тригера, одиничний вихід якого з'єднаний з входом індикатора, сигнальним виходом і другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, з керуючим входом другого регістра зсуву, з керуючим входом першого регістра зсуву, вихід першого регістра зсуву з'єднаний з першим інформаційним входом операційного блока, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи демультиплексора з'єднані з шиною результату і з інформаційними входами блока пам'яті, шина потужності множини з'єднана з першою групою входів схеми порівняння, вихід якої з'єднаний з входом скидання тригера, перша інформаційна шина з'єднана з входами першого регістра зсуву, друга інформаційна шина з'єднана з входами другого регістра зсуву, вихід якого з'єднаний з другим інформаційним входом операційного блока, шина кода операції з'єднана з керуючими входами операційного блока, виходи двійкового лічильника з'єднані з шиною адреси, з адресними входами демультиплексора, другою групою входів схеми порівняння, вихід генератора з'єднаний з першим входом елемента І, вхід «запис» з'єднаний з входом запису першого і другого регістра зсуву.

2. Символьний процесор за п. 1, який відрізняється тим, що операційний блок містить елемент АБО, п'ять елементів І, чотири елементи НІ, перший і другий керуючі входи, перший і другий інформаційні входи, вихід результату, причому перший керуючий вхід з'єднаний з першим входом четвертого елемента І, першим входом п'ятого елемента І, входом першого елемента НІ, вихід якого з'єднаний з першим входом першого елемента І, першим входом третього елемента І, вихід третього елемента І з'єднаний з третім входом елемента АБО, вихід якого є виходом результату, другий керуючий вхід з'єднаний з першим входом другого елемента І, другим входом п'ятого елемента І, входом другого елемента НІ, вихід якого з'єднаний з другим входом третього елемента І, перший інформаційний вхід з'єднаний з другим входом четвертого елемента І, третім входом п'ятого елемента І, входом третього елемента НІ, вихід якого з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з першим входом елемента АБО, другий інформаційний вхід з'єднаний з другим входом другого елемента І, третім входом четвертого елемента І, входом четвертого елемента НІ, вихід якого з'єднаний з третім входом третього элемента І, вихід другого элемента І з'єднаний з другим входом елемента АБО, вихід четвертого элемента І з'єднаний четвертим входом элемента АБО, вихід п'ятого елемента І з‘єднаний п'ятим входом элемента АБО.

Текст

1 Символьний процесор, що має вхід запуску, першу інформаційну шину, генератор імпульсів, двійковий лічильник, тригер, схему порівняння, елемент І, блок пам'яті, сигнальний вихід, шину результату, вхід "скидання" з'єднаний з входом скидання двійкового лічильника, який відрізняється тим, що містить демультиплексор, операційний блок, перший і другий регістри зсуву, другу інформаційну шину, шину потужності множини, індикатор, шину коду операції, шину адреси, вхід "запис", причому вхід запуску з'єднаний з входом установки тригера, одиничний вихід якого з'єднаний з входом індикатора, сигнальним виходом і другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, з керуючим входом другого регістра зсуву, з керуючим входом першого регістра зсуву, вихід першого регістра зсуву з'єднаний з першим інформаційним входом операційного блока, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи демультиплексора з'єднані з шиною результату і з інформаційними входами блока пам'яті, шина потужності множини з'єднана з першою групою входів схеми порівняння, вихід якої з'єднаний з входом скидання тригера, перша інформаційна шина з'єднана з входами першого регістра зсуву, друга інформаційна шина з'єднана з входами дру гого регістра зсуву, вихід якого з єднаний з другим інформаційним входом операційного блока, шина кода операції з'єднана з керуючими входами операційного блока, виходи двійкового лічильника з'єднані з шиною адреси, з адресними входами демультиплексора, другою групою входів схеми порівняння, вихід генератора з'єднаний з першим входом елемента І, вхід "запис" з'єднаний з входом запису першого і другого регістра зсуву 2 Символьний процесор по п 1, який відрізняється тим, що операційний блок містить елемент АБО, п'ять елементів І, чотири елементи НІ, перший і другий керуючі входи, перший і другий інформаційні входи, вихід результату, причому перший керуючий вхід з'єднаний з першим входом четвертого елемента І, першим входом п'ятого елемента І, входом першого елемента НІ, вихід якого з'єднаний з першим входом першого елемента І, першим входом третього елемента І, вихід третього елемента І з'єднаний з третім входом елемента АБО, вихід якого є виходом результату, другий керуючий вхід з'єднаний з першим входом другого елемента І, другим входом п'ятого елемента І, входом другого елемента НІ, вихід якого з'єднаний Пристрій відноситься до області автоматики і обчислювальної техніки і призначений для реалізації операцій над символьними множинами і може використовуватися як співпроцесор для реалізації макрокоманд обробки символьних множин Відомий пристрій для перетворення множин в польський інверсний запис, якій містить два регіс тра, дешифратор лексичних одиниць, блок пам'яті, дешифратор, блок мікропрограмного керування, регістр зсуву, комутатор (авторське свідотство СРСР № 1290358, кл G06F15/38, опуб бюл №6, 1987) Недоліком відомого пристрою є обмежені функціональні можливості і висока складність 3 другим входом третього елемента І, перший інформаційний вхід з'єднаний з другим входом четвертого елемента І, третім входом п'ятого елемента І, входом третього елемента НІ, вихід якого з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з першим входом елемента АБО, другий інформаційний вхід з'єднаний з другим входом другого елемента І, третім входом четвертого елемента І, входом четвертого елемента НІ, вихід якого з'єднаний з третім входом третього элемента І, вихід другого элемента І з'єднаний з другим входом елемента АБО, вихід четвертого элемента І з'єднаний четвертим входом элемента АБО, вихід п'ятого елемента І з'єднаний п'ятим входом элемента АБО О ю 42590 Найбільш близьким по технічній суті і результату, що досягається, є пристрій для об'єднання лексичних множин (авторське свідотство СРСР №1508236, кл G06F15/38, опубл бюл № 34, 1989), який містить три двійкових лічильники, першу інформаційну шину, генератор імпульсів, двійковий лічильник, три тригера, схему порівняння, три елементи І, блок пам'яті, сигнальний вихід, шину результату, вхід "скидання" з'єднаний з входом скидання першого двійкового лічильника, перший і другий дешифратори, два елементи АБО, елементи затримки, m блоків аналізу характеристик слів, де m - КІЛЬКІСТЬ можливих слів, перший і другий мультиплексори, елемент 1І I, перший і -— другий елемент НІ Недоліком відомого пристрою є обмежені функціональні можливості і висока складність В основу винаходу поставлена задача створити пристрій, який в залежності від керуючого коду виконував би більш широкий набір операцій над символьними множинами, з меншими апаратними витратами Поставлена задача вирішується тим, що в символьному процесорі, який містить вхід запуску, першу інформаційну шину, генератор імпульсів, двійковий лічильник, тригер, схему порівняння, елемент І, блок пам'яті, сигнальний вихід, шину результату, вхід "скидання" з'єднаний з входом скидання двійкового лічильника, ВІДПОВІДНО ДО винаходу містить демультиплексор, операційний блок, перший і другий регістри зсуву, другу інформаційну шину, шину потужності множини, індикатор, шину коду операції, шину адреси, вхід "запис", причому вхід запуску з'єднаний з входом установки тригера, одиничний вихід якого з'єднаний з входом індикатора, сигнальним виходом і другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, з керуючим входом другого регістра зсуву, з керуючим входом першого регістра зсуву, вихід першого регістра зсуву з'єднаний з першим інформаційним входом операційного блока, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи демультиплексора з'єднані з шиною результату і з інформаційними входами блока пам'яті, шина потужності множини з'єднана з першою групою входів схеми порівняння, вихід якої з'єднаний з входом скидання тригера, перша інформаційна шина з'єднана з входами першого регістра зсуву, друга інформаційна шина з'єднана з входами другого регістра зсуву, вихід якого з'єднаний з другим інформаційним входом операційного блока, шина кода операції з'єднана з керуючими входами операційного блока, виходи двійкового лічильника з'єднані з шиною адреси, з адресними входами демультиплексора, другою групою входів схеми порівняння, вихід генератора з'єднаний з першим входом елемента І, вхід "запис" з'єднаний з входом запису першого і другого регістра зсуву Поставлена задача вирішується також тим, що операційний блок містить елемент АБО, п'ять елементів І, чотири елементи НІ, перший і другий керуючі входи, перший і другий інформаційні входи, вихід результату, причому перший керуючий вхід з'єднаний з першим входом четвертого елемента І, першим входом п'ятого елемента І, входом першого елемента НІ, вихід якого з'єднаний з першим входом першого елемента І, першим входом третього елемента І, вихід третього елемента І з'єднаний з третім входом елемента АБО, вихід якого є виходом результату, другий керуючий вхід з'єднаний з першим входом другого елемента І, другим входом п'ятого елемента І, входом другого елемента НІ, вихід якого з'єднаний з другим входом третього елемента І, перший інформаційний вхід з'єднаний з другим входом четвертого елемента І, третім входом п'ятого елемента І, входом третього елемента НІ, вихід якого з'єднаний з другим входом першого елемента І, вихід першого елемента І з'єднаний з першим входом елемента АБО, другий інформаційний вхід з'єднаний з другим входом другого елемента І, третім входом четвертого елемента І, входом четвертого елемента НІ, вихід якого з'єднаний з третім входом третього елемента І, вихід другого елемента І з'єднаний з другим входом елемента АБО, вихід четвертого елемента І з'єднаний з четвертим входом елемента АБО, вихід п'ятого елемента І з'єднаний з п'ятим входом елемента АБО Запропонований пристрій має новий склад елементів, та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості винаходу Технічний результат, як наслідок цих властивостей - розширені функціональні можливості пристрою На фіг 1 представлена функціональна схема символьного процесора На фіг 2 представлена функціональна схема операційного блоку Символьний процесор містить вхід "скидання" 1, вхід запуску 2, першу інформаційну шину З, генератор імпульсів 4, двійковий лічильник 5, тригер 6, схему порівняння 7, елемент І 8, блок пам'яті 9, сигнальний вихід 10, шина результату 11, демультиплексор 12, операційний блок 13, другий і перший регистри зсуву 14 і 15, другу інформаційну шину 16, шину потужності множини 17, індикат о р і в , шину коду операції 19, шину адреси 20, вхід "запис" 21 Вхід "скидання" 1 з'єднаний з входом скидання двійкового лічильника 5, вхід запуску 2 з'єднаний з входом установки тригера 6, одиничний вихід якого з'єднаний з входом індикатора 18, сигнальним виходом 10 і другим входом елемента І 8, вихід якого з'єднаний з рахунковим входом двійкового лічильника 5, з керуючим входом другого регістра зсуву 14, з керуючим входом першого регістра зсуву 15, вихід якого з'єднаний з першим інформаційним входом операційного блоку 13, вихід якого з'єднаний з інформаційним входом демультиплексора 12, виходи демультиплексора з'єднані з шиною результату 11 і з інформаційними входами блоку пам'яті 9, шина потужності множини 17 з'єднана з першою групою входів схеми порівняння 7, вихід якої з'єднаний з входом скидання тригер 6, перша інформаційна шина З з'єднана з входами першого регістра зсуву 15, друга інформаційна шина 16 з'єднана з входами другого регістра зсуву 14, вихід якого з'єднаний з другим інформаційним входом операційного блока 13, шина коду операції 19 з'єднана з керуючими входами операційного блока 13, виходи двійкового лічильника 5 з'єднані з шиною адреси 20, з адресними входами демультиплексора 12, другою групою входів схеми порівняння 7, вихід генератора 4 з'єднаний з першим входом елемента І 8, вхід "за 42590 пис" 21 з'єднаний з входом запису першого і другого регістра зсуву 15 и 14 Операційний блок 13 містить елемент АБО 35, п'ять елементів І 30-34, чотири елементи НІ 26-29, перший керуючий вхід 24, другий керуючий вхід 25, перший інформаційний вхід 22, другий інформаційний вхід 23, вихід результату 36 Перший керуючий вхід 24 з'єднаний з першим входом четвертого елемента І 33, першим входом п'ятого елемента І 34, входом першого елемента НІ 26, вихід якого з'єднаний з першим входом першого елемента І ЗО, першим входом третього елемента І 32, вихід третього елемента 132 з'єднаний з третім входом елемента АБО 35, вихід якого є виходом результату 36, другий керуючий вхід 25 з'єднаний з першим входом другого елемента І 31, другим входом п'ятого елемента І 34, входом другого елемента НІ 27, вихід якого з'єднаний з другим входом третього елемента І 32, перший інформаційний вхід 22 з'єднаний з другим входом четвертого елемента І 33, третім входом п'ятого елемента І 34, входом третього елемента НІ 28, вихід якого з'єднаний з другим входом першого елемента І ЗО, вихід першого елемента І з'єднаний з першим входом елемента АБО 35, другий інформаційний вхід 23 з'єднаний з другим входом другого елемента І 31, третім входом четвертого елемента І 33, входом четвертого елемента НІ 29, вихід якого з'єднаний з третім входом третього елемента І 32, вихід другого елемента І 31 з'єднаний з другим входом елемента АБО 35, вихід четвертого елемента І 33 з'єднаний з четвертим входом елемента АБО 35, вихід п'ятого елемента І 34 з'єднаний с п'ятим входом елемента АБО 35 Всі елементи пристрою є стандартними елементами обчислювальної техніки і можуть бути виконані по будь-якій ВІДОМІЙ схемі Пристрій працює таким чином На вхід "скидання" 2 подається сигнал установки двійкового лічильника 5 в початковий стан Нехай А={а1, а2 an} і В={Ь1, Ь2 bn} - початкові множини, причому аі, Ьі {0,1} Значення аі=1 вказує на входження і-го елемента в розглянуту множину Наприклад, А={0,1,0,1,1} відповідає множині елементів {а2, а4, а5} Значення елементів множини А подається на першу шину 3 Значення елементів множини В - на другу інформаційну шину 16 Потім після подачі сигналу "запис" на вхід 21 відбувається запис вказаних вище значень в регістри зсуву 15 і 14 На шину 17 подається значення КІЛЬКОСТІ елементів множини На шину коду операції 19 подається код операції, що виконується операційним блоком Пристрій готовий до роботи При подачі на вхід "запуск" 2 сигналу " 1 " тригер 6 встановлюється в одиничний стан, через логічний елемент І 8 імпульси з генератора 4 проходять на вхід двійкового лічильника 5 і входи регістрів зсуву 14 і 15 Регістри зсуву 14 і 15 здійснюють зсув ліворуч на один розряд На виходах регістрів формуються значення аі і Ьі, які поступають на інформаційні входи операційного блока 13 На вхід демультиплексора 12 з виходу операційного блоку поступає результат операції, на адресні входи демультиплексора з двійкового лічильника 5 по шині адреси 20 поступає адреса комірки блока пам'яті 11 У процесі роботи схема порівняння 7 проводить порівняння двійкового коду поточного номера елемента і двійкового коду КІЛЬКОСТІ елементів множини При рівності значень на виході схеми порівняння формується одиничний сигнал, який поступає на вхід скидання тригера 6, який закриває елемент І 8 для проходження імпульсів з виходу генератора 4 На сигнальному виході 10 формується сигнал "0", вказуючий на закінчення процесу рішення задачі Функції, що виконуються пристроєм, залежність від коду операції представлені в таблиці Таблиця Код операції Вхід 24 Вхід 25 0 0 0 1 1 1 0 1 Вихід пристрою AvB AvB АВ AvB Розглянемо приклад роботи пристрою Нехай на першу інформаційну шину пристрою поступає множина А={0,0,1,0,1,1}, на другу інформаційну шину поступає множина В={0,1,1,1,0,0} При коді операції "1 1" внаслідок роботи пристрою отримаємо F={0,1,1,1,1,1} Порівняння пристрою, що пропонується, і прототипу показує, що при меншій складності пристрою (в схемі відсутні перший і другий дешифратори, другий і третій ДВІЙКОВІ лічильники, другий тригер, елементи АБО, блоки аналізу характеристик слів, елемент 1І I, другий і третій елементи І, -— мультиплексори, елементи НІ, друга схема порівняння), пристрій реалізовує більш широкий клас функцій і його застосування дасть позитивний ефект 42590 10 ФІГ. 1 25 22 Фіг. 2 ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Киів-133, бульв Лесі Українки, 26 (044)295-81-42, 295-61-97 Підписано до друку Обсяг обл -вид арк 2002 р Формат 60x84 1/8 Тираж 50 прим Зам УкрІНТЕІ, 03680, Киів-39 МСП, вул Горького, 180 (044) 268-25-22

ДивитисяДодаткова інформація

Назва патенту англійськоюSymbol processor

Автори англійськоюChumachenko Ihor Volodymyrovych, Derhachov Volodymyr Andriiovych, Svitlychnyi Oleksandr Volodymyrovych

Назва патенту російськоюПроцессор для обработки символов

Автори російськоюЧумаченко Игорь Владимирович, Дергачов Владимир Андреевич, Свитличный Александр Владимирович

МПК / Мітки

МПК: G06F 17/00, G06F 19/00

Мітки: символьний, процесор

Код посилання

<a href="https://ua.patents.su/4-42590-simvolnijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Символьний процесор</a>

Попередній патент: Концентрат технологічного засобу для механічної обробки металів “інкомет-1″

Наступний патент: Пристрій для імпульсного дозування порошкоподібних матеріалів

Випадковий патент: Спосіб контролю чисельності популяцій пильщиків (hymenoptera, tenthredinidae)