Обчислювальний пристрій

Номер патенту: 6112

Опубліковано: 15.04.2005

Автори: Ковінько Юрій Олексійович, Кожем'яко Володимир Прокопович, Новицький Руслан Михайлович

Формула / Реферат

Обчислювальний пристрій, що містить два лічильники, перший з яких підключений лічильним входом до виходу першого елемента І, а виходами - до першої групи входів блока порівняння кодів, з'єднаного другою групою входів з виходами другого лічильника, а виходом - з першим входом першого елемента АБО, другий вхід якого через одновібратор підключений до шини вводу першого часово-імпульсного сигналу та до першого входу першого елемента І, який відрізняється тим, що в нього додатково введені блок обчислення суми і різниці, що містить n груп по n елементів I та дві групи по (n-1) елементів АБО, причому кожний і-й елемент І кожної j-ї групи елементів (і=1,n, j=1,n) підключений першим входом до 7-го входу першої групи входів блока обчислення суми і різниці, а другим входом – до j-го входу другої групи входів блока обчислення суми і різниці, вихід першого елемента I першої групи з'єднаний з виходом n-го розряду коду різниці блока обчислення суми і різниці, вихід n-го елемента I першої групи підключений до виходу першого розряду коду суми блока обчислення суми і різниці, кожний К-й елемент АБО першої групи (К=1, n-1) з'єднаний виходом з виходом (К+1)-го розряду коду суми блока обчислення суми і різниці, а входами - з виходами (n+j - К-1)-х елементів І кожної j-ї групи (I=7, К+1), причому кожний К-й елемент АБО другої групи підключений до виходу К-го розряду коду різниці блока обчислення суми і різниці, а входами - до виходів (n-j - К+2)-х елементів І кожної j-ї групи (j=1, n-К+1), чотири комутатори, три регістри і другий тригер, підключений входом установки в "1" до входу другого часово-імпульсного сигналу пристрою, входом обнуління - до входу обнуління пристрою та входом обнуління першого тригера і лічильників, а виходом - до другого входу третього елемента I, при цьому виходи розрядів першого лічильника з'єднані з інформаційними входами першого регістра та першою групою інформаційних входів першого комутатора, підключених другою групою інформаційних входів до виходів першого регістра, а виходами - до першої групи входів блока обчислення суми і різниці, з'єднаного другою групою входів з виходами другого комутатора, підключеного першою групою інформаційних входів до виходів розрядів другого лічильника та інформаційним входам другого регістра, при цьому виходи кодів суми і різниці блока обчислення суми і різниці з'єднані з першою та другою групами інформаційних входів третього комутатора відповідно, перший керуючий вхід якого підключений до виходу третього елемента 7, другий керуючий вхід - до першого входу задавання коду операції пристрою, а виходи - до інформаційних входів третього регістра і до першої групи інформаційних входів четвертого комутатора, з'єднаного другою групою інформаційних входів з виходами третього регістра, керуючим входом - з другим входом задавання коду операції пристрою, з керуючими входами першого і другого комутаторів та входами дозволу зчитування першого, другого та третього регістрів, а виходами - з виходами пристрою.

Текст

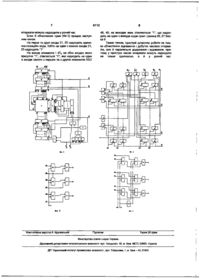

Обчислювальний пристрій, що містить два лічильники, перший з яких підключений лічильним входом до виходу першого елемента І, а виходами - до першої групи входів блока порівняння кодів, з'єднаного другою групою входів з виходами другого лічильника, а виходом - з першим входом першого елемента АБО, другий вхід якого через одновібратор підключений до шини вводу першого часовоімпульсного сигналу та до першого входу першого елемента І, який відрізняється тим, що в нього додатково введені блок обчислення суми і різниці, що містить п груп по п елементів І та дві групи по (п-1) елементів АБО, причому кожний і-й елемент І кожної J-I групи елементів (i=1,n, j=1,n) підключений першим входом до 7-го входу першої фупи входів блока обчислення суми і різниці, а другим входом - до j-ro входу другої групи входів блока обчислення суми і різниці, вихід першого елемента І першої групи з'єднаний з виходом п-го розряду коду різниці блока обчислення суми і різниці, вихід п-го елемента І першої групи підключений до виходу першого розряду коду суми блока обчислення суми і різниці, кожний К-й елемент АБО першої групи (К=1, п-1) з'єднаний виходом з виходом (К+1)-го розряду коду суми блока обчислення суми і різниці, а входами - з виходами (n+j - К-1)-х елементів І кожної J-I групи (1=7, К+1), причому кожний К-й елемент АБО другої групи під ключений до виходу К-го розряду коду різниці блока обчислення суми і різниці, а входами - до виходів (n-j - К+2)-х елементів І кожної J-I групи (j=1, п-К+1), чотири комутатори, три регістри і другий тригер, підключений входом установки в "1" до входу другого часово-імпульсного сигналу пристрою, входом обнуління - до входу обнуління пристрою та входом обнуління першого тригера і ЛІЧИЛЬНИКІВ, а виходом - до другого входу третього елемента І, при цьому виходи розрядів першого лічильника з'єднані з інформаційними входами першого регістра та першою групою інформаційних входів першого комутатора, підключених другою групою інформаційних входів до виходів першого регістра, а виходами - до першої групи входів блока обчислення суми і різниці, з'єднаного другою групою входів з виходами другого комутатора, підключеного першою групою інформаційних входів до виходів розрядів другого лічильника та інформаційним входам другого регістра, при цьому виходи кодів суми і різниці блока обчислення суми і різниці з'єднані з першою та другою групами інформаційних входів третього комутатора ВІДПОВІДНО, перший керуючий вхід якого підключений до виходу третього елемента 7, другий керуючий вхід - до першого входу задавання коду операції пристрою, а виходи - до інформаційних входів третього регістра і до першої фупи інформаційних входів четвертого комутатора, з'єднаного другою групою інформаційних входів з виходами третього регістра, керуючим входом - з другим входом задавання коду операції пристрою, з керуючими входами першого і другого комутаторів та входами дозволу зчитування першого, другого та третього регістрів, а виходами - з виходами пристрою Корисна модель відноситься до автоматики та обчислювальної техніки та може бути використаний в інформаційно-вимірювальних системах для побудови спеціалізованих обчислювальних пристроїв з часово-імпульсною формою представлення інформації Аналогом є пристрій для обчислення відношень часових інтервалів [Авторське свідоцтво СРСР №966705, кл МПК7 G06G7/16, 1981], який містить тригер, дешифратор нуля, третій та четвертий елементи І, поділювач частоти з постійним коефіцієнтом ділення і поділювач частоти з керованим коефіцієнтом ділення, інформаційні виходи другого лічильника підключені до входів дешифратора нуля, вихід якого підключений до першого входу тригера, другий вхід тригера підключений до другого входу пристрою, а вихід підключений до перших входів третього та четвертого елементів І, другий вхід третього елемента І підключений до виходу поділювана частоти з постійним коефіцієнтом ділення, вхід якого підключений до виходу генератора імпульсів, другий вхід четвертого елемента І підключений до інформаційного входу CM S 6112 поділювана частоти з керуючим коефіцієнтом ділення, керуючі входи якого підключені до інформаційних входів першого лічильника, а вихід підключений до входу молодших розрядів лічильника результату, вихід третього елемента І підключений до віднімаючого входу другого лічильника. Недоліками аналога є: граничні функціональні можливості, так як він дозволяє виконувати тільки операції ділення. Прототипом являється обчислювальний пристрій [Авторське свідоцтво СРСР №985795, кл. МПК7 G06G7/12, 1981.], який містить лічильники, перший з яких підключений лічильним входом до виходу першого елемента І, а виходами - до першої трупа входів блоку порівняння кодів, з'єднаного другою фупою входів з виходами другого лічильника, а виходом - з першим входом першого елемента АБО, другий вхід якого через одновібратор підключений до шини вводу першого часово-імпульсного сигналу та до першого входу першого елемента І, з'єднаного другим входом з виходом генератора імпульсів та з першим входом другого елемента І, підключеного другим входом до шини вводу другого часово-імпульсного сигналу, а виходом - до підсумовуючого входу другого лічильника, тригер, дешифратор нуля, елемент IНІ, другий елемент АБО, третій, четвертий та п'ятий елементи І керований дільник частоти, з'єднаний лічильним входом з виходом третього елемента І і з першим входом другого елемента АБО, керуючими входами - з виходами першого лічильника, а виходом - з віднімаючим входом другого лічильника, підключеного виходами до входів дешифратора нуля, а входом обнуління - до виходу четвертого елемента І, з'єднаного першим входом з шиною установки режиму "Ділення", з першим входом елемента І-НІ, та з першим входом п'ятого елемента І, а другим входом - з першим входом першого елемента АБО, підключеного виходом до другого входу п'ятого елемента І, вихід якого з'єднаний з другим входом другого елемента АБО, підключеного виходом до лічильного входу третього лічильника, причому вихід шифратора нуля з'єднаний з першим входом тригера, підключеного другим входом до шини вводу другого часово-імпульсного сигналу, а виходом - до першого входу третього елемента І, з'єднаного другим та третім входами відповідно з виходом генератора імпульсів та з шиною установки режиму "Множення". Недоліками прототипу є те, що він має обмежені функціональні можливості, так, як він дозволяє виконувати лише операції ділення та множення часовоімпульсних інтервалів. В основу корисної моделі поставлена задача створення обчислювального пристрою з розширеними функціональними можливостями за рахунок введення трьох елементів І 2, генератора імпульсів, двох лічильників, блока обчислення суми та різниці чотирьох комутаторів, трьох регістрів, двох тригерів і зв'язків між ними, з'являється можливість виконання операцій додавання та віднімання. Пристрій перетворює тривалість вхідних часово-імпульсних сигналів в одинично-позиційний код з наступною обробкою. Пристрій виконує операції множення-ділення та сумування-віднімання, дозволяє обробляти імпульси, що надходять як одночасно, так і в різні моменти часу. Поставлена задача досягається за рахунок виконання операцій додавання та віднімання, в нього введені блок обчислення суми і різниці, чотири комутатора, три регістри і другий тригер, підключений входом установки в " 1 " до входу другого часовоімпульсного сигналу пристрою, входом обнуління до входу обнуління пристрою та входом обнуління першого тригера і лічильників, а виходом - до другого входу третього елемента І, при цьому виходи розрядів першого лічильника з'єднані з інформаційними входами першого регістра та першою групою інформаційних входів першого комутатора, підключених другою фупою інформаційних входів до виходів першого регістра, а виходами - до першої групи входів блока обчислення суми і різниці, з'єднаного другою групою входів з виходами другого комутатора, підключеного першою фупою інформаційних входів до виходів розрядів другого лічильника та інформаційним входам другого регістра, при цьому виходи кодів суми і різниці блока обчислення суми і різниці з'єднані з першою та другою групами інформаційних входів третього комутатора відповідно, перший керуючий вхід якого підключений до виходу третього елемента І, другий керуючий вхід - до першого входу задавання коду операції пристрою, а виходи - до інформаційних входів третього регістра і до першої групи інформаційних входів четвертого комутатора, з'єднаного другою групою інформаційних входів з виходами третього регістра, керуючим входом - з другим входом задавання коду операції пристрою, з керуючими входами першого і другого комутаторів та входами дозволу зчитування першого, другого та третього регістрів, а виходами - з виходами пристрою. Блок обчислення суми і різниці містить п груп по п елементів І та дві групи по (п-1) елементів АБО, причому кожний і-й елемент І кожної j-ї групи елементів (і=1, n, j=1, n) підключений першим входом до іго входу першої фупи входів блока обчислення суми і різниці, а другим входом - до j-ro входу другої групи входів блока обчислення суми і різниці, вихід першого елемента І першої групи з'єднаний з виходом п-го розряду коду різниці блоку обчислення суми і різниці, вихід п-го елементу І першої фупи підключений до виходу першого розряду коду суми блока обчислення суми і різниці, кожний К-й елемент АБО першої групи (К=1, п-1) з'єднаний виходом з виходом (К+1)го розряду коду суми блока обчислення суми і різниці, а входами - з виходами (n+j - К-1)-х елементів І кожної j-ї групи (j=1, K+1), причому кожний К-й елемент АБО другої групи підключений до виходу К-го розряду коду різниці блока обчислення суми і різниці, а входами - до виходів (n-j - К+2)-х елементів І кожної j-ї групи (j=1, п-К+1). На Фіг.1 представлена блок-схема обчислювального пристрою; на Фіг.2 - функціональна блок-схема обчислення суми та різниці; на Фіг.З - функціональна схема першого, другого та четвертого комутаторів; на Фіг.4 - функціональна схема третього комутатора. Обчислювальний пристрій має перший-третій елементи І 1-3, генератор 4 імпульсів, перший і другий лічильники 5 і 6, причому лічильний вхід 7 першо 6112 го лічильника 5 підключений до виходу елемента І 1, входи якого підключені до входу 8 першого часовоімпульсного сигналу пристрою та до виходу генератора 4 імпульсів, блок 9 обчислення суми і різниці, перший-четвертий комутатори 10-13, перший-третій регістри 14-16 та перший і другий тригери 17 і 18. Крім того, на Фіг.1 позначені: 19 і 20 - перша і друга фупи інформаційних входів комутатора 10; 21 - перша група входів блока 9; 22 - лічильний вхід лічильника 6; 23 і 24 - перша і друга групи інформаційних входів комутатора 11; 25 - друга група входів блока 9; 26 і 27 - виходи кодів суми і різниці блока 9 відповідно; 28 і 29 - перша і друга групи інформаційних входів комутатора 12; ЗО і 31 - перша і друга групи інформаційних входів комутатора 13; 32 - виходи пристрою; 33 - вхід другого часово-імпульсного сигналу пристрою; 34 і 35 - входи установки в "1" тригерів 17 і 18; 36 і 37 - перший і другий керуючі входи комутатора 12; 38 і 39 - перший і другий входи завдання коду операції пристрою; 40 - входи дозволу зчитування регістрів; 41 - керуючі входи комутаторів 10, 11 і 13; 42 - вхід обнуління пристрою; 43 і 44 - входи обнуління лічильників 5 і 6, 45 і 46 - входи обнуління тригерів 17 і 18. Блок 9 обчислення суми і різниці (Фіг.2) має п фуп по п елементів І 47і, і, 47і,2,..., 47,, j 47n, n , (де і - номер елемента, j - номер групи) та дві групи по (п1) елементів АБО 48 і 49. Перший, другий і четвертий комутатори 10, 11, 13 мають фупу елементів І 50 та фупу лементів АБО 51, третій комутатор 12 має елемент НІ 52, перші і другі елементи І 53, 54 та елемент АБО 55. Пристрій працює наступним чином. В початковий момент часу на вході 42 обнуління присутній "0", який не справляє ніякої дії на роботу пристрою. На другий вхід 39 завдання операції також подається "0", який надходить на входи дозволу зчитування 40 регістрів 14-16 та керуючі входи 41 комутаторів 10, 11, 13. На перший вхід 38 завдання коду операції подається "0", що надходить на другий керуючий вхід 37 керування третього комутатора 12. На перший та другий входи 8, 33 пристрою подаються імпульси, що мають тривалість відповідну часовим інтервалам Т-і та Т2, відношення яких потрібно обчислити. Імпульси зразкової частоти з виходу генератора 4 проходять через перший та другий елементи І 1, 2 на протязі часових інтервалів Ті та Тг на рахункові входи 7, 44 першого та другого лічильників 5, 6. Кількість імпульсів, що надійшли на лічильники 5, 6 на протязі часових інтервалів Ті та Тг представляються в них у одинично-позиційному коді, тобто збудженому одному розряду лічильника відповідає вага числа. Ці значення кодів у подальшому зберігаються незмінними в лічильниках 5, 6 на протязі всього часу вимірювання. На виходах тригерів 17, 18 весь час присутні "0". По закінченню часових інтервалів, на них з'являються "1", тобто обидва тригера 17, 18 переходять в одиничний стан по задньому фронту часового інтервалу і запам'ятовують його. Сигнали "1" надходять на входи третього елемента І 3, з виходу якого "1" надходить на перший керуючий вхід 36 третього комутатора 12. Коди з виходів лічильників 5, 6 надходять на входи першого та другого регістрів 14, 15 та на перші входи 19,23 першого та другого комутаторів 10,11. На входах першого та другого лічильників присутні одинично-позиційні входи чисел А та В, що відповідають тривалостям вхідних імпульсів. Відповідно на виходах першого та другого комутаторів 10, 11 будуть присутні одинично-позиційні коди чисел А та В або коди ІодА та ІодВ, в залежності від керуючих сигналів на керуючих входах 40 та 41. Ці коди надходять відповідно на перші та другі входи 21 та 25 блока 9 обчислення суми. Так як на керуючих кодах 40, 41 регістрів 14-16 і комутаторів 10, 11, 13 присутній "0", то на виходах першого та другого комутаторів 10, 11 з'являються коди, що надходять з виходів першого та другого регістрів 14, 15 на другі входи 20, 24 комутаторів 10,11. На виходах 27 блока 9 обчислення суми з'являється код відмінності вхідних кодів (для нашого прикладу logA-logB=logA/B). Код з виходів 27 надходить на другі входи 29 третього комутатора 12 та з'являється на його виходах, надходячи на входи третього регістру 16 та на перші входи ЗО четвертого комутатора 13. У відповідності з кодом на входах 40 та 41 третього регістру 16 та четвертого комутатора 13 код з перших входів ЗО четвертого комутатора 13 не надходить на його виходи 32. Код А/В вже перетворений третім регістром 16, надходить на другі входи 31 четвертого комутатора 13 та надходить на його виходи 32, який і відповідає співвідношенню тривалостей часових інтервалів. Для множення інтервалів Ті та Тг на вхід 38 пристрою подається "1". Відповідно код буде формуватися на виходах 26 блока 9 обчислення суми і надходити на перші входи 28 третього комутатора 12 та на його виходи, так як на його другому керуючому вході 37 присутня "1". Код буде відповідати log AxB = LogA + logB і перетворюватися у третьому регістрі 16 у відповідний одинично-позиційний код АхВ, який через четвертий комутатор 13 надходить на виходи 32 пристрою. Для додавання часових інтервалів на перший та другий входи 38, 39 пристрою подається "1", яка відключає регістри 14-16, тобто на їх виходах будуть присутні "0". Отже, коди обох лічильників 5, 6 не перетворюються на коди логарифмів. Створюється безпосереднє додавання обох величин А та В. Результат додавання з перших виходів 26 через третій та четвертий комутатори 12,13 надходить на виходи 32 пристрою. Для віднімання часових інтервалів на вхід 39 пристрою подається "1", а на вхід 38 подається "0". В даному режимі, як і в попередньому, перетворення в коди логарифмів не відбувається, а відбувається безпосереднє віднімання кодів А та В, результат якого з виходів 27 блока 9 обчислення суми через третій та четвертий комутатори 12, 13 надходить на виходи 32 пристрою. Обнуління лічильників 5, 6 та тригерів 17, 18 відбувається шляхом подачі "1" на вхід 42 обнуління, що надходить на входи 43, 44, 45, 46 відповідно першого та другого лічильників 5, 6 та першого і другого тригерів 17, 18. Обчислення здійснюється тільки після появи "1" на вході третього елемента І 3, а це можливо після спрацьовування обох тригерів 17, 18, які спрацьовують по закінченню часових інтервалів. Таким чином, безперечно, що обидва часових 8 6112 інтервали можуть надходити у різний час Блок 9 обчислення суми (Фіг 2) працює наступним чином На перші та другі входи 21, 25 надходять одиниЧНО-ПОЗИЦІЙНІ коди, тобто на один з кожних входів 21, 25 надходить "1" На виході елемента І 47У, на обох входах якого присутня "1", з'являється "1", яка надходить на один із входів одного з перших та з других елементів АБО 48, 49, на виходах яких з'являються "1", що надходять на один з виходів кодів суми і різниці 26, 27 блока 9 Таким чином, пристрій дозволяє робити не тільки обчислення віднімання і добуток часових інтервалів, але й паралельне додавання і віднімання, причому у пристрої часові інтервали можуть надходити не тільки одночасно, а й у різний час Фіг З Комп ютерна верстка А Крулевський Підписне Тираж 28 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності вул Урицького 45, м Київ МСП, 03680, Україна ДП 'Український інститут промислової власності, вул Глазунова, 1, м Київ-42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюComputing device

Автори англійськоюKozhemyako Volodymyr Prokopovych, Novtstkyy Ruslan Mykhailovych

Назва патенту російськоюВычислительное устройство

Автори російськоюКожемяко Владимир Прокофьевич, Новицкий Руслан Михайлович

МПК / Мітки

МПК: G06G 7/12, G06G 7/14, G06G 7/24

Мітки: пристрій, обчислювальній

Код посилання

<a href="https://ua.patents.su/4-6112-obchislyuvalnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Обчислювальний пристрій</a>

Попередній патент: Клапан-пульсатор

Наступний патент: N-6-заміщені 7-деазапурини (варіанти), спосіб їх одержання, фармацевтична композиція для лікування аденозинопосередкованих захворювань (варіанти)

Випадковий патент: Пристрій для утилізації теплоти відхідних димових газів доменних повітронагрівників