Двотактний симетричний підсилювач струму

Номер патенту: 66030

Опубліковано: 26.12.2011

Автори: Теплицький Михайло Юхимович, Пономарьова Марія Валеріївна, Азаров Олексій Дмитрович, Крупельницький Леонід Віталійович

Формула / Реферат

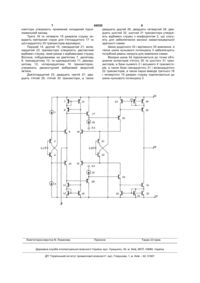

Двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, емітери першого і другого транзисторів об'єднано між собою, бази третього і четвертого транзисторів з'єднано з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, колектори п'ятого і шостого транзисторів об'єднано між собою та з'єднано з вихідною шиною, який відрізняється тим, що у нього введено двадцять транзисторів, два джерела струму, причому бази сьомого та восьмого транзисторів з'єднано між собою та під'єднано до шини нульового потенціалу, колектори - до шин додатного та від'ємного живлення відповідно, емітер сьомого транзистора з'єднано з базою третього та першим виводом першого джерела струму, емітер восьмого транзистора з'єднано з базою десятого транзистора та першим виводом другого джерела струму, колектори третього і четвертого транзисторів з'єднано з колекторами десятого і одинадцятого транзисторів, а також з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази дев'ятого і тринадцятого транзисторів об'єднані між собою та з'єднані з об'єднаними колектором дев'ятого і емітером десятого транзисторів, колектори дев'ятого і тринадцятого транзисторів під'єднано до шини додатного живлення колектор тринадцятого транзистора з'єднано з базою десятого і колектором першого транзисторів, база одинадцятого транзистора з'єднана з об'єднаними колекторами другого і чотирнадцятого транзисторів, колектор одинадцятого транзистора - з об'єднаними базами дванадцятого і чотирнадцятого транзисторів та колектором дванадцятого транзистора, емітери дванадцятого і чотирнадцятого та колектор шістнадцятого транзисторів під'єднано до шини від'ємного живлення, база двадцять першого транзистора з'єднана з об'єднаними емітером шістнадцятого транзистора і другим виводом четвертого джерела струму, перший вивід четвертого джерела струму під'єднано до шини нульового потенціалу, база двадцятого транзистора з'єднана з об'єднаними емітером п'ятнадцятого транзистора і другим виводом третього джерела струму, колектор п'ятнадцятого транзистора під'єднано до шини додатного живлення, а перший вивід третього джерела струму - до шини нульового потенціалу, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з об'єднаними базою першого і колектором двадцятого, базою другого та колектором двадцять першого транзисторів відповідно, об'єднані бази сімнадцятого та вісімнадцятого транзисторів під'єднано до шини нульового потенціалу, колектори сімнадцятого та вісімнадцятого транзисторів під'єднано до шин від'ємного та додатного живлення відповідно, емітери дев'ятнадцятого, двадцять третього і двадцять п'ятого транзисторів під'єднано до шини додатного живлення, а їхні бази з'єднані між собою, база п'ятого транзистора з'єднана з об'єднаними колектором дев'ятнадцятого та емітером двадцятого транзисторів, колектор двадцять третього транзистора з'єднано з об'єднаними колектором двадцять п'ятого і емітером п'ятого транзисторів та колектором двадцять третього транзистора, емітери двадцять другого, двадцять четвертого і двадцять шостого транзисторів під'єднані до шини від'ємного живлення, а їхні бази з'єднані між собою, база шостого транзистора з'єднана з об'єднаними емітером двадцять першого та колектором двадцять другого транзисторів, колектор двадцять четвертого транзистора з'єднаний з об'єднаними емітером шостого і колектором двадцять шостого транзисторів та базою двадцять четвертого транзистора.

Текст

Двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, емітери першого і другого транзисторів об'єднано між собою, бази третього і четвертого транзисторів з'єднано з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, колектори п'ятого і шостого транзисторів об'єднано між собою та з'єднано з вихідною шиною, який відрізняється тим, що у нього введено двадцять транзисторів, два джерела струму, причому бази сьомого та восьмого транзисторів з'єднано між собою та під'єднано до шини нульового потенціалу, колектори - до шин додатного та від'ємного живлення відповідно, емітер сьомого транзистора з'єднано з базою третього та першим виводом першого джерела струму, емітер восьмого транзистора з'єднано з базою десятого транзистора та першим виводом другого джерела струму, колектори третього і четвертого транзисторів з'єднано з колекторами десятого і одинадцятого транзисторів, а також з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази дев'ятого і тринадцятого транзисторів об'єднані між собою та з'єднані з об'єднаними колектором дев'ятого і емітером десятого транзисторів, колектори дев'ятого і тринадцятого транзисторів під'єднано до шини додатного живлення колектор тринадцятого транзистора з'єднано з базою десятого і колектором першого транзисторів, база одинадцятого транзистора з'єднана з об'єднаними 2 (19) 1 3 Корисна модель належить до імпульсної техніки і може бути використана в аналогово-цифрових перетворювачах і цифрових вимірювальних приладах. Відомо підсилювач постійного струму (А.с. № 1548841, H03 F3/25, 1989 р.), який містить перший і другий транзистори, які мають різну структуру. Емітери першого і другого транзисторів з'єднано, а точка з'єднання є входом підсилювача постійного струму. Третій і четвертий транзистори мають структуру відповідно другого і першого транзисторів, їх колектори є виходами підсилювача постійного струму, а бази третього і четвертого транзисторів з'єднано з колекторами першого і другого транзисторів відповідно. Бази першого і другого транзисторів з'єднано з шиною нульового потенціалу через перший і другий транзистори відповідно у діодному включенні та перше і друге джерела струмів, які включено між шинами додатного та від'ємного живлення та базами першого і другого транзисторів відповідно. Перший та другий транзистори у діодному включенні мають структуру відповідно до першого і другого транзисторів відповідно. Перший та другий струмозадаючі елементи виконано відповідно на першому і другому відбивачах струму та п'ятому і шостому транзисторах, які мають структуру відповідно до третього і четвертого транзисторів. Бази п'ятого і шостого транзисторів є виходами відповідно першого і другого струмозадаючого елементів, їх колектори з'єднано з шиною нульового потенціалу, а емітери - з виходами відповідно першого і другого відбивачів струму. Входи відбивачів струму з'єднано через двополюсний струмозадаючий елемент. Колектори третього і четвертого транзисторів з'єднано через коло зміщення. Коло зміщення виконано на третьому і четвертому транзисторах в діодному включенні. Виводи кола зміщення підключено до баз сьомого і восьмого транзисторів, які ввімкнено по схемі із загальним колектором. Емітери сьомого і восьмого транзисторів з'єднано, вони є виходом підсилювача. Недоліком пристрою є низький коефіцієнт підсилення та низька швидкодія. За прототип вибрано двотактний симетричний підсилювач струму (Push-pull amplifier with current mirrors for determining the quiescent operating point, United States Patent 3,852,678, Dec. 3, 1974), який містить перше і друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього четвертого транзисторів відповідно, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, другі виводи першого і другого джерел струму та емітери п'ятого і шостого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, колектори п'ятого і шостого транзисторів з'єднано з вихідною шиною. 66030 4 Недоліком прототипу є низький коефіцієнт підсилення, що обмежує галузь використання пристрою. В основу корисної моделі поставлено задачу створення двотактного симетричного підсилювача струму, в якому за рахунок введення нових елементів та зв'язків між ними збільшується коефіцієнт підсилення, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у двотактний симетричний підсилювач струму, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, шість транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, емітери першого і другого транзисторів об'єднано між собою, бази третього і четвертого транзисторів з'єднано з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, колектори п'ятого і шостого транзисторів об'єднано між собою та з'єднано з вихідною шиною, крім того введено двадцять транзисторів, два джерела струму, причому бази сьомого та восьмого транзисторів з'єднано між собою та під'єднано до шини нульового потенціалу, колектори - до шин додатного та від'ємного живлення відповідно, емітер сьомого транзистора з'єднано з базою третього та першим виводом першого джерела струму, емітер восьмого транзистора з'єднано з базою десятого транзистора та першим виводом другого джерела струму, колектори третього і четвертого транзисторів з'єднано з колекторами десятого і одинадцятого транзисторів, а також з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази дев'ятого і тринадцятого транзисторів об'єднані між собою та з'єднані з об'єднаними колектором дев'ятого і емітером десятого транзисторів, колектори дев'ятого і тринадцятого транзисторів під'єднано до шини додатного живлення, колектор тринадцятого транзистора з'єднано з базою десятого і колектором першого транзисторів, база одинадцятого транзистора з'єднана з об'єднаними колекторами другого і чотирнадцятого транзисторів, колектор одинадцятого транзистора - з об'єднаними базами дванадцятого і чотирнадцятого транзисторів та колектором дванадцятого транзистора, емітери дванадцятого і чотирнадцятого та колектор шістнадцятого транзисторів під'єднано до шини від'ємного живлення, база двадцять першого транзистора з'єднана з об'єднаними емітером шістнадцятого транзистора і другим виводом четвертого джерела струму, перший вивід четвертого джерела струму під'єднано до шини нульового потенціалу, база двадцятого транзистора з'єднана з об'єднаними емітером п'ятнадцятого транзистора і другим виводом третього джерела струму, колектор п'ятнадцятого транзистора під'єднано до шини додатного живлення, а перший вивід третього джерела струму до шини нульового потенціалу, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з об'єднаними базою першого і колектором двадця 5 66030 6 того, базою другого та колектором двадцять перними колектором десятого 8 і третього 9 транзисшого транзисторів відповідно, об'єднані бази сімторів, база дванадцятого транзистора 12 з'єднана надцятого та вісімнадцятого транзисторів під'єдз об'єднаними емітером одинадцятого транзистонано до шини нульового потенціалу, колектори ра 11 і колектором дванадцятого транзистора 12, сімнадцятого та вісімнадцятого транзисторів під'єбаза одинадцятого транзистора 11 з'єднана з днано до шин від'ємного та додатного живлення об'єднаними колектором другого 15 і чотирнадцявідповідно, емітери дев'ятнадцятого, двадцять того 16 транзисторів, база шістнадцятого транзистретього і двадцять п'ятого транзисторів під'єднатора 20 з'єднана з об'єднаними колектором четвено до шини додатного живлення, а їхні бази з'єдртого 10 і одинадцятого 11 транзисторів, емітери нані між собою, база п'ятого транзистора з'єднана першого 14 і другого 15 транзисторів з'єднані між з об'єднаними колектором дев'ятнадцятого та емісобою, база двадцятого 15 транзистора з'єднана з тером двадцятого транзисторів, колектор двадцяоб'єднаними емітером п'ятнадцятого 17 транзисть третього транзистора з'єднано з об'єднаними тора і другим виводом третього 18 джерела струколектором двадцять п'ятого і емітером п'ятого му, база двадцять першого 25 транзистора з'єднатранзисторів та колектором двадцять третього на з об'єднаними емітером шістнадцятого 20 транзистора, емітери двадцять другого, двадцять транзистора і другим виводом четвертого 20 джечетвертого і двадцять шостого транзисторів під'єрела струму, емітер сімнадцятого 21 транзистора днані до шини від'ємного живлення, а їхні бази з'єднано з об'єднаними базою першого 14 і колекз'єднані між собою, база шостого транзистора тором двадцятого 24 транзисторів, емітер вісімназ'єднана з об'єднаними емітером двадцять першодцятого 22 транзистора з'єднано з об'єднаними го та колектором двадцять другого транзисторів, базою другого 15 і колектором двадцять першого колектор двадцять четвертого транзистора з'єдна25 транзисторів, об'єднані між собою бази дев'ятний з об'єднаними емітером шостого і колектором надцятого 23 і двадцять третього 27 транзисторів двадцять шостого транзисторів та базою двадцяз'єднано з колекторами двадцять третього 27 і ть-четвертого транзистора. двадцять п'ятого 29 транзисторів та з емітером На кресленні представлено принципову схему п'ятого 30 транзистора, база п'ятого 30 транзистодвотактного симетричного підсилювача постійного ра з'єднана з об'єднаними колектором та емітером струму. дев'ятнадцятого 23 і двадцятого 24 транзисторів Пристрій містить вхідну шину 6, яку з'єднано з відповідно, об'єднані бази двадцять другого 26 і емітерами третього 9 і четвертого 10 транзисторів, двадцять четвертого 28 транзисторів з'єднано з шину додатного живлення 33, яку з'єднано з еміколекторами двадцять четвертого 28 і двадцять терами двадцять п'ятого 29, двадцять третього 27, шостого 32 транзисторів та з емітером шостого 31 дев'ятнадцятого 23, тринадцятого 13 і дев'ятого 7 транзистора, база шостого 31 транзистора з'єднатранзисторів, колекторами вісімнадцятого 22, п'ятна з об'єднаними емітером та колектором двадцянадцятого 17 і восьмого 4 транзисторів та другим ть першого 25 і двадцять другого 26 транзисторів. виводом першого джерела струму 1, шину від'ємПристрій працює таким чином. ного живлення, яку з'єднано з емітерами двадцять Вхідний сигнал у вигляді струму поступає на шостого 32, двадцять четвертого 28, двадцять вхідну шину 6. Якщо вхідний струм втікає у схему, другого 26, чотирнадцятого 16 і дванадцятого 12 то четвертий 10 транзистор привідкривається, а транзисторів, колекторами сімнадцятого 21, шісттретій 9 транзистор призакривається, відповідно надцятого 20 і сьомого 2 транзисторів, та другим шістнадцятий 20 транзистор призакривається, а виводом другого джерела струму 5, вихідну шину п'ятнадцятий 17 транзистор привідкривається, 34, яку з'єднано з об'єднаними колекторами п'ятовідповідно двадцять перший 25 транзистор привіго 30 і шостого 31 транзисторів, шину нульового дкривається, а двадцятий 24 транзистор призакпотенціалу, яку з'єднано з об'єднаними базами ривається, відповідно шостий 31 транзистор присьомого 2 і восьмого 4, сімнадцятого 21 і вісімнадвідкривається, а п'ятий 30 транзистор цятого 22 транзисторів, першими виводами трепризакривається. Різниця струмів на колекторах тього 18 і четвертого 19 джерел струму, об'єднані п'ятого 30 і шостого 31 транзисторів поступає на між собою перший вивід першого джерела струму вихід схеми. 1 і емітер сьомого транзистора 2 з'єднано з базою Якщо вхідний струм витікає зі схеми, - то четтретього транзистора 9, об'єднані між собою первертий 10 транзистор призакривається, а третій 9 ший вивід другого джерела струму 5 і емітер восьтранзистор привідкривається, відповідно шістнамого транзистора 4 з'єднано з базою четвертого дцятий 20 транзистор привідкривається, а п'ятнатранзистора 10, бази дев'ятого 7 і тринадцятого 13 дцятий 17 транзистор призакривається, відповідно транзисторів, а також бази дванадцятого 12 і чодвадцять перший 25 транзистор призакривається, тирнадцятого 16 транзисторів, та бази дев'ятнаа двадцятий 24 транзистор привідкривається, віддцятого 23, двадцять третього 27 і двадцять п'ятоповідно шостий 31 транзистор призакривається, а го 29 транзисторів, а також бази двадцять другого п'ятий 30 транзистор привідкривається. Різниця 26, двадцять четвертого 28 і двадцять шостого 32 струмів на колекторах п'ятого 30 і шостого 31 тратранзисторів відповідно з'єднані між собою, база нзисторів поступає на вихід схеми. дев'ятого транзистора 7 з'єднана, з об'єднаними Перше 1 і друге 5 джерела струму та сьомий об'єднані між собою емітером десятого 8 і колек2, восьмий 4, третій 9, четвертий 10 транзистори тором дев'ятого 7 транзисторів, база десятого утворюють схему завдання напруги зміщення на транзистора 8 з'єднана з об'єднаними колектором вхідному каскаді. тринадцятого 13 і першого 14 транзисторів, база П'ятнадцятий 17 і двадцятий 24 транзистори, а п'ятнадцятого транзистора 17 з'єднана з об'єднатакож шістнадцятий 19 і двадцять перший 25 тра 7 66030 8 нзистори утворюють проміжний складений підсидвадцять другий 26, двадцять четвертий 28, двалювальний каскад. дцять шостий 32, шостий 31 транзистори утворюТретє 18 та четверте 19 джерела струму зають відбивачі струму з коефіцієнтом 2, що слугувдають емітерний струм для п'ятнадцятого 17 та ють для забезпечення високої навантажувальної шістнадцятого 20 транзисторів відповідно. здатності схеми. Перший 14, другий 15, сімнадцятий 21, вісімШини додатного 33 і від'ємного 35 живлення, а надцятий 22 транзистори утворюють двотактний також шина нульового потенціалу 3 забезпечують відбивач струму, який разом з відбивачами струму потрібний рівень напруги для живлення схеми. Вілсона, побудованими на дев'ятому 7, десятому Вихідна шина 34 підключається до точки об'є8, тринадцятому 13, та одинадцятому 11, дванадднання колекторів п'ятого 30 та шостого 31 транцятому 12, чотирнадцятому 16 транзисторах, зисторів, а бази сьомого 2 і восьмого 4 транзистоутворюють двоконтурний вибірковий зворотній рів, а також бази сімнадцятого 21 і вісімнадцятого зв'язок. 22 транзисторів, а також перші виводи третього 18 Дев'ятнадцятий 23, двадцять третій 27, дваі четвертого 19 джерел струму підключаються до дцять п'ятий 29, п'ятий 30 транзистори, а також шини нульового потенціалу 3. Комп’ютерна верстка М. Ломалова Підписне Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюPull-push balanced current amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Krupelnytskyi Leonid Vitaliiovych, Teplytskyi Mykhailo Yukhymovych, Ponomariova Mariia Valeriivna

Назва патенту російськоюДвухтактный симметричный усилитель тока

Автори російськоюАзаров Алексей Дмитриевич, Крупельницкий Леонид Витальевич, Теплицкий Михаил Ефимович, Пономарёва Мария Валерьевна

МПК / Мітки

Мітки: підсилювач, симетричний, двотактний, струму

Код посилання

<a href="https://ua.patents.su/4-66030-dvotaktnijj-simetrichnijj-pidsilyuvach-strumu.html" target="_blank" rel="follow" title="База патентів України">Двотактний симетричний підсилювач струму</a>

Попередній патент: Спосіб лікування двобічного плеврального випоту неясного генезу

Наступний патент: Вимірювач магнітного поля

Випадковий патент: Спосіб прогнозування розвитку анемії у хворих на хронічну серцеву недостатність