Буферний каскад

Номер патенту: 92963

Опубліковано: 27.12.2010

Автори: Азаров Олексій Дмитрович, Богомолов Сергій Віталійович

Формула / Реферат

Буферний каскад, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, дванадцять транзисторів, причому вхідну шину з'єднано з емітерами четвертого і п'ятого транзисторів, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, бази дев'ятого і десятого транзисторів з'єднано з базами третього і шостого транзисторів відповідно, бази другого і сьомого транзисторів з'єднано з шинами додатного і від'ємного живлення через перше і друге джерела струму відповідно, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що введено перший і другий компенсатори струму та двонаправлений відбивач струму, причому бази дев'ятого і десятого транзисторів з'єднано з базами та колекторами третього і шостого транзисторів відповідно, а також з емітерами другого і сьомого транзисторів відповідно, колектори дев'ятого і десятого транзисторів з'єднано з базами другого і сьомого транзисторів відповідно, а також з шинами додатного і від'ємного живлення через перше і друге джерела струму відповідно, колектори другого і сьомого транзисторів з'єднано з базами першого і восьмого транзисторів відповідно, а також з виходами першого і другого компенсаторів струму відповідно, входи додатного і від'ємного живлення першого і другого компенсаторів струму та емітери першого і другого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, входи першого і другого компенсаторів струму з'єднано з першим і другим виходами двонаправленого відбивача струму відповідно, колектори першого і восьмого транзисторів з'єднано з першим і другим входами двонаправленого відбивача струму відповідно, третій вихід двонаправленого відбивача струму з'єднано з колекторами четвертого і п'ятого транзисторів, а також з базами і колекторами одинадцятого і дванадцятого транзисторів та з вихідною шиною.

Текст

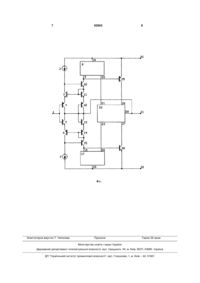

Буферний каскад, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, дванадцять транзисторів, причому вхідну шину з'єднано з емітерами четвертого і п'ятого транзисторів, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, бази дев'ятого і десятого транзисторів з'єднано з базами третього і шостого транзисторів відповідно, бази другого і сьомого транзисторів з'єднано з шинами додатного і від'ємного живлення через перше і друге джерела струму відповідно, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзис C2 2 92963 1 3 п'ятого і шостого біполярних транзисторів з'єднано з вхідною шиною. Колектори п'ятого і шостого біполярних транзисторів з'єднано з емітерами сьомого і восьмого біполярних транзисторів відповідно. Колектори сьомого і восьмого біполярних транзисторів з'єднано з шинами додатного і від'ємного потенціалу відповідно. Колектори третього і четвертого біполярних транзисторів з'єднано з емітерами сьомого і восьмого біполярних транзисторів відповідно. Емітери третього і четвертого біполярних транзисторів з'єднано з вихідною шиною. Недоліками аналогу є низький вхідний опір та низька точність роботи. За прототип обрано буферний пристрій [Д.п. №15896 Н030К5/22, G05B1/00, 2006], який містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого і п'ятого транзисторів, колектори четвертого і п'ятого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, а також з емітерами другого і сьомого транзисторів відповідно, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, бази та колектори дев'ятого і десятого транзисторів з'єднано з базами третього і шостого транзисторів відповідно, а також базу та колектор дев'ятого транзистора з'єднано з емітером першого транзистора, базу та колектор десятого транзистора з'єднано з базою та колектором восьмого транзистора, базу та колектор першого транзистора з'єднано з шиною додатного живлення через перше джерело струму, а також з базою другого транзистора, емітер восьмого транзистора з'єднано з шиною від'ємного живлення через друге джерело струму, а також з базою сьомого транзистора, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною. Недоліками прототипу є висока нелінійність, що виникає через складність завдання робочих точок по постійному струму підсилювальних каскадів, що обмежує галузь використання. В основу винаходу поставлено задачу створення буферного каскаду, в якому введення нових елементів та зв'язків між ними дозволяє підвищити точність роботи за рахунок вирівнювання коефіцієнтів підсилення по струму верхнього і нижнього ярусів підсилювальних каскадів, які побудовано на транзисторах різної структури, а також підвищення лінійності за рахунок автоматизації процесу симетрування робочих точок по постійному струму підсилювальних каскадів. Це розширює галузь використання винаходу у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача досягається тим, що у буферний каскад, який містить перше та друге джерела струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, дванадцять 92963 4 транзисторів, причому вхідну шину з'єднано з емітерами четвертого і п'ятого транзисторів, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, бази дев'ятого і десятого транзисторів з'єднано з базами третього і шостого транзисторів відповідно, бази другого і сьомого транзисторів з'єднано з шинами додатного і від'ємного живлення через перше і друге джерела струму відповідно, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, введено перший і другий компенсатори струму та двонаправлений відбивач струму, причому бази дев'ятого і десятого транзисторів з'єднано з базами та колекторами третього і шостого транзисторів відповідно, а також з емітерами другого і сьомого транзисторів відповідно, колектори дев'ятого і десятого транзисторів з'єднано з базами другого і сьомого транзисторів відповідно, а також з шинами додатного і від'ємного живлення через перше і друге джерела струму відповідно, колектори другого і сьомого транзисторів з'єднано з базами першого і восьмого транзисторів відповідно, а також з виходами першого і другого компенсаторів струму відповідно, входи додатного і від'ємного живлення першого і другого компенсаторів струму та емітери першого і другого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, входи першого і другого компенсаторів струму з'єднано з першим і другим виходами двонаправленого відбивача струму відповідно, колектори першого і восьмого транзисторів з'єднано з першим і другим входами двонаправленого відбивача струму відповідно, третій вихід двонаправленого відбивача струму з'єднано з колекторами четвертого і п'ятого транзисторів, а також з базами і колекторами одинадцятого і дванадцятого транзисторів та з вихідною шиною. На кресленні (Фіг.) представлено принципову схему двотактного симетричного підсилювача струму. Пристрій містить вхідну шину вхідну шину 1, яку з'єднано з емітерами четвертого 4 і п'ятого 5 транзисторів, емітери четвертого 4 і п'ятого 5 транзисторів з'єднано з емітерами дев'ятого 3 і десятого 6 транзисторів відповідно, бази дев'ятого 3 і десятого 6 транзисторів з'єднано з базами та колекторами третього 11 і шостого 14 транзисторів відповідно, а також з емітерами другого 10 і сьомого 15 транзисторів відповідно, колектори дев'ятого 3 і десятого 6 транзисторів з'єднано з базами другого 10 і сьомого 15 транзисторів відповідно, а також з шинами додатного 30 і від'ємного 32 живлення через перше 2 і друге 7 джерела струму відповідно, емітери третього 11 і шостого 13 транзисторів з'єднано з емітерами одинадцятого 12 і дванадцятого 13 транзисторів відповідно, колектори другого 10 і сьомого 15 транзисторів з'єднано з базами першого 25 і восьмого 28 транзисторів відповідно, а також з виходами 9, 16 першого 8 і другого 17 компенсаторів струму відповідно, входи 5 додатного 18 і від'ємного 19 живлення першого 8 і другого 17 компенсаторів струму та емітери першого 25 і другого 28 транзисторів з'єднано з шинами додатного 30 і від'ємного 32 живлення відповідно, входи 20, 24 першого 8 і другого 17 компенсаторів струму з'єднано з першим 21 і другим 23 виходами двонаправленого відбивача струму 22 відповідно, колектори першого 25 і восьмого 28 транзисторів з'єднано з першим 26 і другим 27 входами двонаправленого відбивача струму 22 відповідно, третій 29 вихід двонаправленого відбивача струму 22 з'єднано з колекторами четвертого 4 і п'ятого 5транзисторів, а також з базами та колекторами одинадцятого 12 і дванадцятого 13 транзисторів та з вихідною шиною 31. Пристрій працює таким чином. Якщо вхідний сигнал у вигляді струму втікає на вхідну шину 1 пристрою, тоді п'ятий 5 транзистор привідкривається, а четвертий 4 транзистор призакривається. Емітерний струм п'ятого 5 транзистора збільшується і збільшується емітерний струм десятого 6 транзистора, що у свою чергу призводить до збільшення колекторного струму сьомого 15 транзистора. Емітерний струм четвертого 4 транзистора зменшується і зменшується емітерний струм дев'ятого 3 транзистора, що у свою чергу призводить до зменшення колекторного струму другого 10 транзистора. Базовий струм восьмого 28 транзистора збільшується, що призводить до його привідкривання. У цьому випадку струм із вхідної шини 31 втікає у схему, тому вихідна напруга третього 29 виходу двонаправленого відбивача струму 22 зменшується та наближається до напруги шини від'ємного живлення 32. В умовах асиметрії коефіцієнти передачі по струму першого 25 і восьмого 28 транзисторів будуть неідентичними. У даному випадку це призводить до зменшення струму першого 21 і другого 23 виходів двонаправленого відбивача струму 22 та входів 20, 24 першого 8 і другого 17 компенсаторів струму, а це у свою чергу призводить до зменшення струму виходів 9, 16 першого 8 і другого 17 компенсаторів струму. При цьому на перший 25 транзистор діє позитивний зворотній зв'язок, а на восьмий 28 транзистор діє від'ємний зворотній зв'язок. Зменшення вихідного струму першого 8 компенсатора струму призводить до додаткового привідкривання першого 25 транзистора і збільшення його колекторного струму. Водночас зменшення вихідного струму другого 17 компенсатора струму гальмує подальше привідкривання восьмого 28 транзистора. Вказаний процес регулювання триває доти, аж поки прирости базових струмів першого 25 і восьмого 28 транзисторів не будуть збалансовані. Симетрування призводить до того, що в зоні малих сигналів амплітуди приростів колекторних струмів першого 8 і восьмого 28 транзисторів вирівнюються, а в зоні великих сигналів співвідношення приростів будуть пропорційними. Якщо вхідний сигнал у вигляді струму витікає з вхідної шини 1 пристрою, тоді п'ятий 5 транзистор 92963 6 призакривається, а четвертий 4 транзистор привікривається. Емітерний струм п'ятого 5 транзистора зменшується і зменшується емітерний струм десятого 6 транзистора, що у свою чергу призводить до зменшення колекторного струму сьомого 15 транзистора. Емітерний струм четвертого 4 транзистора збільшується і збільшується емітерний струм дев'ятого 3 транзистора, що у свою чергу призводить до збільшення колекторного струму другого 10 транзистора. Базовий струм восьмого 28 транзистора зменшується, що призводить до його призакривання. У цьому випадку струм із вхідної шини 31 витікає зі схеми, тому вихідна напруга третього 29 виходу двонаправленого відбивача струму 22 збільшується та наближається до напруги шини додатного живлення 30. В умовах асиметрії коефіцієнти передачі по струму першого 25 і восьмого 28 транзисторів будуть неідентичними. У даному випадку це призводить до збільшення струму першого 21 і другого 23 виходів двонаправленого відбивача струму 22 та входів 20, 24 першого 8 і другого 17 компенсаторів струму, а це у свою чергу призводить до збільшення струму виходів 9, 16 першого 8 і другого 17 компенсаторів струму. При цьому на перший 25 транзистор діє позитивний зворотній зв'язок, а на восьмий 28 транзистор діє від'ємний зворотній зв'язок. Збільшення вихідного струму першого 8 компенсатора струму призводить до додаткового призакривання першого 25 транзистора і зменшення його колекторного струму. Водночас збільшення вихідного струму другого 17 компенсатора струму гальмує подальше призакривання восьмого 28 транзистора. Вказаний процес регулювання триває доти, аж поки прирости базових струмів першого 25 і восьмого 28 транзисторів не будуть збалансовані. Симетрування призводить до того, що в зоні малих сигналів амплітуди приростів колекторних струмів першого 8 і восьмого 28 транзисторів вирівнюються, а в зоні великих сигналів співвідношення приростів будуть пропорційними. Підвищення точності роботи та лінійності досягається тим, що автоматично задається режим по постійному струму першого 26 і другого 27 входів двонаправленого відбивача струму 22, а також шляхом симетрування значень коефіцієнтів передачі підсилювальних каскадів, які побудовано на транзисторах різних типів провідності, тобто першому 25 - p-n-р і восьмому 28 - n-p-п транзисторах відповідно. Перше 2 і друге 7 джерела струму та відбивачі струму, які побудовано на дев'ятому 3, другому 10, третьому 11, одинадцятому 12 та дванадцятому 13, десятому 6, шостому 14, сьомому 15 транзисторах відповідно, утворюють схему завдання режиму по постійному струму каскадів схеми. Шини додатного 30 і від'ємного 32 живлення забезпечують потрібний рівень напруги для живлення схеми. 7 Комп’ютерна верстка Т. Чепелева 92963 8 Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer stage

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych

Назва патенту російськоюБуферный каскад

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич

МПК / Мітки

МПК: H03F 3/34

Код посилання

<a href="https://ua.patents.su/4-92963-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Спосіб одержання поверхневої функціональної нанотекстури

Наступний патент: Пристрій для гребних гвинтів

Випадковий патент: Спосіб ранньої діагностики онкологічних захворювань органів травлення