Пристрій для аналізу форми обгинаючої частотних сигналів

Номер патенту: 10877

Опубліковано: 25.12.1996

Автори: Ракогон Аліна Володимирівна, Каук Віктор Іванович, Міхнов Дмитро Кіндратович

Формула / Реферат

Устройство для анализа формы огибающей частотных сигналов, содержащее генератор импульсов, аналого-цифровой преобразователь, первый и сторон регистры, блок сравнения, счетчик адреса считывания и счетчик адреса записи, делитель, коммутатор адресов, запоминающий блок, цифроаналоговый преобразователь, индикаторный блок, дешифратор нуля, первый и второй формирователи импульсов, первый и второй триггеры, первый и второй элементы И, первый и второй элементы задержки, при этом выход генератора импульсов соединен с первым плодом аналого-цифрового преобразователя и входом счетчика адреса считывания, выход котрого соединен с первыми входами коммутатора адресов и делителя и входом дешифратора нуля, выход дешифратора нуля соединен со вторым входом коммутатора адресов, первым ходом индикаторного блока и входами первого и второго формирователей импульсов, выход первого формирователя импульсов соединен с первым входом первого триггера, второй вход которого объединен с первым входом счетчика адреса записи и соединен с выходом делителя, первый выход счетчика адреса записи соединен с первым входом второго триггера, второй вход "Пуск" которого является управляющим входом устройства, а выход соединен со вторыми входами делителя и счетчика адреса записи, второй выход которого соединен с третьим входом коммутатора адресов, выход которого соединен с первым входом запоминающего блока, выход запоминающего блока соединен с накопителем и со входом цифро-налогового преобразователя, выход которого соединен со вторым входом индикаторного блока, кроме того, второй вход аналого-цифрового преобразователя является информационным входом устройства, а выход соединен с первым входом первого регистра, выход которого соединен с первыми входами второго регистра и первого блока сравнения, второй вход первого блока сравнения соединен с выходом второго регистра, а выход - с первым входом второго элемента И, выход которого соединен со вторым входом второго регистра, а второй вход - с выходом второго формирователя импульсов и входом второго элемента задержки, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход - со вторым входом запоминающего блока и входом первого элемента задержки, выход которого соединен с третьим входом второго регистра, отличающееся тем, что в него введены третий триггер, второй блок сравнения, третий регистр, третий элемент задержки, инвертор, при этом выход первого формирователя импульсов соединен с первым входом третьего триггера и со входом третьего элемента задержки, выход которого соединен со вторым входом первого регистра и с третьим входом аналого-цифрового преобразователя, выход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом первого регистра, а выход - со вторым входам третьего триггера, выход которого соединен с первым входом третьего регистра и входом инвертора, выход которого соединен с третьим входом второго элемента И, кроме того, второй вход третьего регистра соединен с выходом второго регистра, третий вход - с выходом первого элемента задержки, а выход - с третьим входом запоминающего блока.

Текст

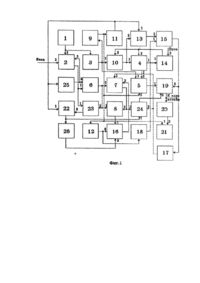

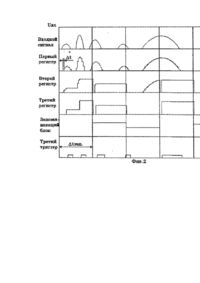

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для анализа формы детерминированных и случайных импульсных и частотны х сигналов. Наиболее близким по технической сущности к заявляемому является устройство для анализа формы непериодических импульсных и частотны х сигналов, которое содержит генератор импульсов, аналогоцифровой преобразователь, счетчик адреса считывания, счетчик адреса записи, первый и второй регистры, блок сравнения, коммутатор адресов, запоминающий блок, первый и второй формирователь коротких импульсов, дешифратор н уля, делитель, первый и второй триггеры, первый и второй элементы задержки, первый и второй элементы И, цифро-аналоговый преобразователь и индикаторный блок, при этом выход генератора импульсов соединен со входом счетчика адреса считывания и первым входом аналого-цифрового преобразователя, второй вход которого является информационным входом устройства, а выход- через первый регистр соединен с первыми входами блока сравнения и второго регистра, выход второго регистра соединен со вторым входом блока сравнения и первым входом запоминающего блока, второй вход запоминающего блока соединен с выходом коммутатора Адресов, второй вход которого соединен с первым выходом счетчика адреса записи, а первый вход коммутатора адресов соединен с входами дешифратора нуля, делителя и выходом счетчика адреса считывания, выход делителя соединен с первыми входами счетчика адреса записи И первого триггера, кроме того, выход де шифратора нуля соединен с третьим входом коммутатора, первым входом индикаторного блока и входами первого и второго формирователей коротких им пульсов, выход первого формирователя коротких импульсов соединен со вторым входом первого регистра, третьим входом аналого-цифрового преобразователя и вторым входом первого триггера, выход которого соединен с первым входом первого элемента И, второй вход первого элемента И соединен с выходом второго элемента задержки, а выход - с третьим входом запоминающего блока и через первый элемент задержки со вторым входом второго регистра, у которого третий вход соединен с выходом второго элемента И, первый вход второго элемента И соединен с выходом блока сравнения, а второй вход - со входом второго элемента задержки и выходом второго формирователя коротких импульсов, кроме того, первый вход второго триггера является входом "Пуск" устройства, второй вход второго триггера соединен со вторым выходом счетчика адреса записи, а выход - со вторым входом счетчика адреса записи и вторым входом делителя, кроме того, выход запоминающего блока через цифроаналоговый преобразователь соединен со вторым входом индикаторного блока. Устройство позволяет анализировать форму огибающей частотно-модулированных сигналов в реальном масштабе времени. Однако, устройство работает с сигналами ограниченного диапазона частот, поэтому анализировать огибающую сигнала, у которого период превышает временной интервал между моментами записи значений в запоминающий блок не представляется возможным. Задачей, решаемой изобретением, является расширение диапазона частот анализируемого частотномодулированного сигнала за счет возможности выделения огибающей низкочастотного сигнала, период которого превышает временной интервал между моментами записи информации. Поставленная задача решается тем, что в устройство, содержащее генератор импульсов, аналогоцифровой преобразователь, первый и второй регистры, блок сравнения, счетчик адреса считывания и счетчик адреса записи, делитель, коммутатор адресов, запоминающий блок, цифроаналоговый преобразователь, индикаторный блок, дешифратор нуля, первый и второй формирователи импульсов, первый и второй триггеры, первый и второй элементы И, первый и второй элементы задержки, при этом выход генератора импульсов соединен с первым входом аналого-цифрового преобразователя и входом счетчика адреса считывания, выход которого соединен с первыми входами коммутатора адресов и делителя и входом дешифратора нуля, выход дешифратора нуля соединен со вторым входом коммутатора адресов, первым входом индикаторного блока и входами первого и второго формирователей импульсов, выход первого формирователя импульсов соединен с первым входом первого триггера, второй вход которого объединен с первым входом счетчика адреса записи и соединен с выходом делителя, первый выход счетчика адреса записи соединен с первым входом второго триггера, второйвход "П уск" которого является управляющим входом устройства, а выход соединен со вторыми входами делителя и счетчика адреса записи, второй выход которого соединен с третьим входом коммутатора адресов, выход которого соединен с первым входом запоминающего блока, выход запоминающего блока соединен с накопителем и со входом цифроаналогового преобразователя, выход цифро-аналогового преобразователя соединен со вторым входом индикаторного блока, кроме того, второй вход аналого-цифрового преобразователя является информационным входом устройства, а выход соединен с первым входом первого регистра, выход которого соединен с первыми входами второго регистра и первого блока сравнения, второй вход первого блока сравнения соединен с выходом второго регистра, а выход - с первым входом второго элемента И, выход которого соединен со вторым входом второго регистра, второй вход второго элемента И соединен с выходом второго формирователя импульсов и входом второго элемента задержки, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход - со вторым входом запоминающего блока и входом первого элемента задержки, выход которого соединен с третьим входом второго регистра, введены третий триггер, второй блок сравнения, третий регистр, третий элемент задержки, инвертор, при этом выход первого формирователя импульсов соединен с первым входом третьего триггера и со входом третьего элемента задержки, выход которого соединен со вторым входом первого регистра и с третьим входом аналого-цифрового преобразователя, выход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом первого регистра, а выход - со вторым входом третьего триггера, выход которого соединен с первым входом третьего регистра и входом инвертора, выход которого соединен с третьим входом второго элемента И, кроме того, второй вход третьего регистра соединен с выходом второго регистра, третий вход соединен с выходом первого элемента задержки, выход третьего регистра соединен с третьим входом запоминающего блока. Введенные блоки и связи позволяют получить новый технический эффект - возможность организации визуального анализа огибающей сигнала в широком диапазоне частот. На фиг.1 представлена структурная схема заявляемого устройства. В его состав входят генератор 1 импульсов, аналого-цифровой преобразователь 2, счетчик 3 адреса считывания, счетчик4 адреса записи, коммутатор 5 адресов, первый регистр 6, второй регистр 7, первый блок 8 сравнения, дешифратор 9 нуля, делитель 10, первый формирователь 11 импульсов, второй формирователь 12 импульсов, первый триггер 13, второй триггер 14, первый элемент 15 И, второй элемент 16 И, первый элемент 17 задержки, второй элемент 18 задержки, запоминающий блок 19, цифро-аналоговый преобразователь 20, индикаторный блок 21, третий триггер 22, второй блок 23 сравнения, третий регистр 24. третий элемент 25 задержки, инвертор 26. На фиг. 2 приведены временные диаграммы работы устройства. Все процессы в устройстве син хронизированы генератором 1 импульсов, выход которого соединен с первым входом аналого-цифрового преобразователя 2 и входом счетчика 3 адреса считывания. Информационным входом устройства является второй вход аналого-цифрового преобразователя 2, выход которого соединен с первыми входами второго блока 23 сравнения и первого регистра 6, выход которого соединен со вторым входом второго блока.23 сравнения -для определения изменения знака приращения входного сигнала, и с первыми входами первого блока 8 сравнения и второго регистра 7. Выход второго регистра 7 соединен со вторыми входами первого блока 8 сравнения и третьего регистра 24, выход которого соединен с третьим (информационным) входом запоминающего блока 19. Выход счетчика 3 адреса считывания соединен со входом дешифратора 9 нуля. Выход дешифратора 9 нуля соединен со входами первого 11 и второго 12 формирователей импульсов, с первым входом индикаторного блока 21 -для определения момента передачи информации, и со вторым входом коммутатора 5 адресов, что обеспечивает его переключение при подаче на адресную шину запоминающего блока 19 адреса записи или считывания. Первый и третий входы коммутатора 5 адресов соединены соответственно с выходами счетчика 3 адреса считывания и счетчика 4 адреса записи, а выход коммутатора 5 адресов соединен с первым входом (адресной шиной) запоминающего блока 19, который соединен с накопителем и с цифро-аналоговым преобразователем 20, выполняющим подготовку аналогового сигнала для индикаторного блока 21. Выход счетчика 3 адреса считывания соединен с первым входом делителя, обеспечивая требуемую частоту записи. Выход делителя 10 соединен с первым входом счетчика 4 адреса записи, выход которого соединен с первым входом второго триггера 14, второй вход "П уск" которого является управляющим входом устройства, а вы ход соединен со вторыми входами счетчика 4 адреса записи и делителя 10, разрешения их работу после запуска. Выход делителя соединен также со вторым входом первого 13 триггера, выход которого соединен со вторым входом первого элемента 15 И. Для синхронизации работы устройства и для формирования сигналов управления выход первого формирователя 11 импульсов соединен с первыми входами первого триггера 13 и третьего триггера 22 и со входом элемента 25 задержки, выход которого соединен с третьим входом аналого-цифрового преобразователя 2 и вторым входом первого регистра 6. Выход третьего триггера 22 соединен со входом инвертора 26, выход которого соединен с третьим входом второго элемента 16 И. Выход второго формирователя 12 импульсов соединен со вторым входом второго элемента 16 И, первый вход которого соединен с выходом первого блока 8 сравнения. Выход второго элемента 16 И соединен со вторым входом второго регистра 7. Кроме того, выход второго формирователя 12 импульсов соединен со входом второго элемента 18 задержки, выход которого соединен с первым входом первого элемента 15 И, выход которого соединен со вторым входом запоминающего блока 10 и со входом первого элемента 17 задержки, выход которого соединен с третьими входами второго регистра 7 и третьего регистра 24. Устройство работает следующим образом: В исходном состоянии второй триггер 14, установленный сигналом переполнения счетчика адреса записи, запрещает работу делителю 10 и счетчику 4 адреса записи. На вход первого триггера 13 поступает сигнал, сформированный первым 11 формирователем импульсов по нулевому состоянию счетчика 3 адреса считывания, расшифрованному дешифратором 9 нуля. Этот сигнал подтверждает состояние первого триггера 13, который запрещает запись информации в запоминающий блок 19, то есть блокирует режим записи. Таким образом, в исходном состоянии происходит только циклическое считывание информации, начиная с произвольного адреса из запоминающего блока 19. При переключении второго триггера 14 командой "Пуск" разрешается счет делителю 10 и счетчику 4 адреса записи, что в свою очередь разрешает последовательную запись в ячейки запоминающего блока 19 вычисленных дискретных значений огибающей частотно-модулированного входного сигнала, когда на интервале времени Dt3an. между моментами записи в запоминающий блок 19 определяется наибольший из максимумов функции входного сигнала, либо нулей, в случае, если на интервале времени Dt3an. входной сигнал не достигнет максимального значения (экстремума функции). Определение максимального или наибольшего среди максимальных значений на интервале Dtзап. производится с учетом знака приращения входного сигнала. Знак приращения определяется при помощи третьего триггера 22, аналого-цифрового преобразователя 2, первого регистра 6. второго блока 23 сравнения и третьего элемента 25 задержки. Дискретное значение входного сигнала, полученное при помощи аналогоцифрового преобразователя 2, сравнивается с предыдущим дискретным значением входного сигнала, хранящимся в первом регистре 6. В результате - вторым блоком 23 сравнения формируется сигнал, поступающий на информационный вход третьего триггера 22, который по сигналу с выхода первого формирователя импульсов устанавливается в соответствующее состояние: активный уровень (логический "0", при положительном значении приращения, состояние логической "1", при отрицательном значении приращения. Сигнал с выхода третьего триггера 22 используется для записи в третий регистр 24 данных (максимального или наибольшего максимального значения), формируемых для запоминающего блока 19, а инвертированный при помощи инвертора 26 - для записи максимального или наибольшего значений на интервале At3an. во второй регистр 7. Π ос л є установки или сброса третьего триггера 22 по результатам сравнения с некоторой временной задержкой, формируемой третьим элементом 25 задержки, происходит запись вычисленного аналого-цифровым преобразователем 2 значения в первый регистр 6. Вычисление дискретных значений входного сигнала и определение максимального или наибольшего значения на интервале Dt3an. осуществляется при помощи аналого-цифрового преобразователя 2, первого регистра 6, второго регистра 7 и блока 8 сравнения. Частотно-модулированный сигнал обрабатывается по алгоритму нахождения максимального из мгновенных значений входного сигнала за интервал времени Dt3an. Полученные є выхода аналого-цифрового преобразователя 2 кодовые эквиваленты мгновенных значений амплитуд входного сигнала записываются в первый регистр 6, после чего производится сравнение его содержимого с содержимым второго регистра 7 в блоке 8 сравнения. Если код, записанный в первом регистре 6, больше, чем код во втором регистре 7, то он переписывается во второй регистр 7. Перезапись производится, если приращение дискретного значения сигнала положительно (функция входного сигнала возрастает). В противном случае, во втором регистре 7 остается ранее записанное значение. Определение на интервале Dt3an. значения, соответствующего максимуму входного сигнала, производится по сигналу на выходе третьего триггера 22. При смене знака приращения с положительного на отрицательный (переход из состояния логического "О" в состояние логической "1") значение, накопленное во втором регистре 7, записывается в третий регистр 24. Таким образом, во втором регистре 7 будет зафиксировано максимальное, наибольшее или нулевое значение на интервале Dt3an. Сброс третьего регистра 24 и второго регистра 7 производится перед началом вычисления значения на очередном интервале времени Dt3an . после записи в запоминающий блок 19. Все процессы в устройстве синхронизированы частотой генератора 1 импульсов. Для получения управляющий сигналов используются первый формирователь 11 и второй формирователь 12 коротких импульсов, работающие соответственно по заднему и переднему фронтам выходного сигнала дешифратора 9 нуля. Процессы управления и синхронизации распределены в устройстве так, что в момент установки нулевого такта счетчика 3 адреса считывания на выходе второго формирователя 12 коротких импульсов формируется импульс для стробирования второго элемента 16 И, который обеспечивает в случае необходимости запись большего мгновенного значения во второй 4 регистр. Он же, задержанный на втором элементе 18 задержки, поступает на вход первого элемента 15 И, и в случае, если первый триггер 13 будет находится в единичном состоянии, происходит перезапись вычисленного максимального значения из третьего регистра 24 в запоминающий блок 19, а после некоторой задержки сбрасывает в нулевое состояние второй регистр 7 и третий регистр 24. Первый триггер 13 устанавливается в единичное состояние при смене адреса записи, так как его счетный вход объединен со счетным входом счетчика 4 адреса записи. В момент окончания нулевого такта счетчика 3 адреса считывания по импульсу с выхода первого 11 формирователя коротких импульсов производится сброс первого триггера 13, синхронизации третьего триггера 22 и, с некоторой задержкой, запись преобразованной входной информации в первый регистр 6 и синхронизация аналого-цифрового преобразователя 2. Режим записи информации в ячейки запоминающего блока 19 и циклического опроса ячеек (в режиме считывания) осуществляется с помощью счетчика 3 адреса считывания, делителя 10, счетчика 4 адреса записи и коммутатора 5 адресов. Коммутатор 5 адресов подключает к адресным шинам запоминающего блока 19 коды адресов считывания и записи соответственно с выходов счетчика 3 адреса считывания и счетчика 4 адреса записи. Делитель 10 обеспечивает требуемую часто ту записи информации в запоминающий блок 19. Подключение адреса записи к адресной шине запоминающего блока 19 производится на нулевом адресе счетчика 3 адреса считывания, расшифровываемом при помощи дешифратора 9 нуля, что позволяет упростить формирование управляющих сигналов и не сказывается на качестве отображения, так как индикаторный блок 21 в это время может находиться в режиме обратного хода луча (га шения луча). Необходимый аналоговый сигнал для индикаторного блока 21 формируется при помощи цифроаналогового преобразователя 20, подключенного к информационному вы ходу запоминающего блока 19. Режим записи блокируется при переполнении счетчика 4 адреса записи. При этом формируется сигнал, поступающий на вход второго триггера 14 и возвращающий его в исходное состояние. Циклическое считывание будет продолжаться и на индикаторном блоке 21 останется изображение записанной информации. Заявляемое устройство позволяет расширить диапазон анализируемых сигналов в сторону низких частот и осуществлять визуальный контроль их огибающей в реальном масштабе времени с помощью индикаторного устройства.

ДивитисяДодаткова інформація

Назва патенту англійськоюAppliance for analysis of form of envelope of frequency signals

Автори англійськоюMikhnov Dmytro Kindratovych, Rakohon Alina Volodymyrivna, Kauk Viktor Ivanovych

Назва патенту російськоюУстройство для анализа формы огибающей частотных сигналов

Автори російськоюМихнов Дмитрий Кондратович, Ракогон Алина Владимировна, Каук Виктор Иванович

МПК / Мітки

МПК: G01R 29/02

Мітки: частотних, аналізу, сигналів, форми, обгинаючої, пристрій

Код посилання

<a href="https://ua.patents.su/5-10877-pristrijj-dlya-analizu-formi-obginayucho-chastotnikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для аналізу форми обгинаючої частотних сигналів</a>

Попередній патент: Противірусний та імуностимулюючий засіб

Наступний патент: Спосіб сушіння газопроникних матеріалів