Пристрій для накопичення сум чисел

Номер патенту: 110904

Опубліковано: 25.02.2016

Автори: Дрозд Юлія Володимирівна, Дрозд Олександр Валентинович, Мілейко Сергій Ігорович, Нестеренко Сергій Анатолійович

Формула / Реферат

Пристрій для накопичення сум чисел, що містить n-розрядний суматор та перший n-розрядний регістр, при цьому n-розрядний інформаційний вхід пристрою підключено до першого n-розрядного входу n-розрядного суматора, n-розрядний вихід якого підключено до n-розрядного інформаційного входу першого n-розрядного регістра, вхід скидання та синхровхід якого підключено відповідно до входу скидання пристрою та тактового входу пристрою, а n-розрядний вихід підключено до n-розрядного виходу пристрою, який відрізняється тим, що введено другий n-розрядний регістр, при цьому вхід скидання та тактовий вхід пристрою підключено відповідно до входу скидання та синхровходу другого n-розрядного регістра, n-розрядний інформаційний вхід якого підключено до n-розрядного виходу першого n-розрядного регістра, а n-розрядний вихід підключено до другого n-розрядного входу n-розрядного суматора.

Текст

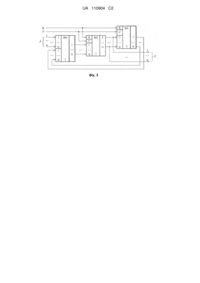

Реферат: Винахід належить до обчислювальної техніки, а саме до арифметичних цифрових пристроїв, і може бути використаний в машинобудівних технологіях. У пристрій для накопичення сум чисел, що містить n-розрядний суматор та перший n-розрядний регістр, при цьому n-розрядний інформаційний вхід пристрою підключено до першого n-розрядного входу n-розрядного суматора, n-розрядний вихід якого підключено до n-розрядного інформаційного входу першого n-розрядного регістра, вхід скидання та синхровхід якого підключено відповідно до входу скидання пристрою та тактового входу пристрою, а n-розрядний вихід підключено до nрозрядного виходу пристрою, введено: другий n-розрядний регістр, при цьому вхід скидання та тактовий вхід пристрою підключено відповідно до входу скидання та синхровходу другого nрозрядного регістра, n-розрядний інформаційний вхід якого підключено до n-розрядного виходу першого n-розрядного регістра, а n-розрядний вихід підключено до другого n-розрядного входу n-розрядного суматора. Технічним результатом, що досягається даним винаходом, є розширення функціональних можливостей пристрою щодо оцінки вхідної послідовності чисел. UA 110904 C2 (12) UA 110904 C2 UA 110904 C2 5 10 15 20 25 30 35 40 45 50 55 Пропонований винахід належить до обчислювальної техніки, а саме до цифрових арифметичних пристроїв, і може бути використаний в машинобудівних технологіях. Відомий пристрій на основі суматора двох чисел, входи першого та другого доданку якого підключено до першого та другого входів пристрою, а вихід є виходом пристрою [1]. Недоліки аналога: пристрій виконує додавання тільки двох чисел, що обмежує функціональні можливості пристрою. Найбільш близьким до запропонованого винаходу по технічній суті та результату, що досягається, є пристрій для накопичення суми чисел, який містить n-розрядний суматор та nрозрядний регістр, при цьому n-розрядний інформаційний вхід пристрою підключено до першого n-розрядного входу n-розрядного суматора, n-розрядний вихід якого підключено до nрозрядного інформаційного входу n-розрядного регістра, вхід скидання та синхровхід якого підключено відповідно до входу скидання пристрою та тактового входу пристрою, а n-розрядний вихід підключено до другого n-розрядного входу n-розрядного суматора та n-розрядного виходу пристрою [2]. Недоліки найближчого аналога: пристрій обчислює суму послідовності чисел, не розбиваючи її на суми чисел, що приходять у парних та непарних тактах, що обмежує функціональні можливості пристрою. Задача винаходу - створення пристрою для накопичення сум чисел, в якому шляхом введення другого n-розрядного регістра забезпечено обчислення двох сум для чисел, що приходять відповідно у парних та непарних тактах, в результаті чого розширюються функціональні можливості пристрою щодо оцінки вхідної послідовності чисел. Поставлена задача вирішується тим, що у пристрій для накопичення сум чисел, що містить n-розрядний суматор та перший n-розрядний регістр, при цьому n-розрядний інформаційний вхід пристрою підключено до першого n-розрядного входу n-розрядного суматора, n-розрядний вихід якого підключено до n-розрядного інформаційного входу першого n-розрядного регістра, вхід скидання та синхровхід якого підключено відповідно до входу скидання пристрою та тактового входу пристрою, а n-розрядний вихід підключено до n-розрядного виходу пристрою, згідно з винаходом введено другий n-розрядний регістр, при цьому вхід скидання та тактовий вхід пристрою підключено відповідно до входу скидання та синхровходу другого n-розрядного регістра, n-розрядний інформаційний вхід якого підключено до n-розрядного виходу першого nрозрядного регістра, а n-розрядний вихід підключено до другого n-розрядного входу nрозрядного суматора. Технічний ефект від запропонованого рішення полягає в тому, що шляхом введення другого n-розрядного регістра забезпечено обчислення двох сум чисел, які приходять відповідно у парні та непарні такти, що призводить до розширення функціональних можливостей пристрою щодо оцінки вхідної послідовності чисел. Розширення функціональних можливостей пристрою можна оцінити наступним чином. В найближчому аналогу обчислюється сума послідовності чисел, що дає інтегровану оцінку цієї послідовності. В запропонованому рішенні також можна одержувати таку оцінку, якщо кожне з чисел буде приходити протягом двох тактів. Разом з тим запропоноване рішення розширює функціональні можливості пристрою до обчислення двох сум, що дають більш інформативну оцінку послідовності, визначаючи внесок до загальної суми окремо чисел, що приходять у парні та непарні такти. Суть винаходу пояснюється кресленням на фіг. 1, де зображено n-розрядний суматор 1, перший 2 та другий 3 n-розрядні регістри, вхід скидання R, тактовий вхід Т, n-розрядний інформаційний вхід А та n-розрядний вихід S пристрою, при цьому входи R та T пристрою підключено відповідно до входів скидання R та синхровходів С регістрів 2 та 3, вхід А пристрою підключено до першого n-розрядного входу суматора 1, другий n-розрядний вхід якого підключено до n-розрядного виходу регістра 3, а n-розрядний вихід підключено до n-розрядного інформаційного входу регістра 2, n-розрядний вихід якого підключено до n-розрядного інформаційного входу регістра 3 та виходу S пристрою. На фіг. 2 показано часові діаграми роботи блоків, а саме для входів R Т, А пристрою, для виходу S пристрою та n-розрядного виходу регістра 3. Розглядається послідовність з п'яти чисел А1, А2, А3, А4, А5, які складаються з розрядів 1 … n та приходять на вхід А пристрою відповідно в тактах 1-5, що показані унизу діаграм. Пристрій працює у такий спосіб. На вхід R пристрою та відповідно входи скидання R регістрів 2 та 3 приходить сигнал, що скидає їх у нульове значення. 1 UA 110904 C2 5 10 15 20 На вхід Т пристрою та відповідно синхровходи С регістрів 2 та 3 подається серія тактових імпульсів типу "меандр", що за переднім фронтом забезпечують прийом чисел в регістри 2 та 3 з їх n-розрядних інформаційних входів. Послідовність чисел А1, А2, А3, А4, А5 подається з входу А пристрою на перший n-розрядний вхід суматора 1, який додає перші два числа до нульових значень регістра 2, тобто обчислює суми, що дорівнюють відповідно числам А1 та А2. Суми з n-розрядного виходу суматора 1 подаються на n-розрядний інформаційний вхід регістра 2, а з його n-розрядного виходу - на вихід S пристрою та n-розрядний інформаційний вхід регістра 3. Числа А1 та А2 отримуються на n-розрядних виходах регістрів 2 і 3 в тактах 2 та 3 і 3 та 4, відповідно. З n-розрядного виходу регістра 3 числа подаються на другий вхід суматора 1. Наступне число А3 додається в такті 3 до числа А1, а число А4 - в такті 4 до числа А2 з обчисленням сум S1-3 та S2-4 чисел, що приходять в непарних та парних тактах, відповідно. В такті 5 до суми S1-3 додається число А5 з обчисленням суми S1-5 чисел А1, А3, А5, які приходять в непарних тактах. Обчислені суми чисел, що приходять в непарних та парних тактах, записуються Пристрій може бути використаний для вивчення впливу чисел з парними та непарними номерами послідовності на обчислення загальної суми. ДЖЕРЕЛА ІНФОРМАЦІЇ: 1. Гаврилов Ю.В., Пучко А.Н. Арифметические устройства быстродействующих ЭЦВМ. 1970. - 280 с., стор. 69, рис. 2.3.1. 2. Применение интегральных микросхем в электронной вычислительной технике: Справочник / Р.В. Данилов, С.А. Ельцова, Ю.П. Иванов и др.; Под ред. Б.Н. Файзулаева, Б.В. Тарабрина. - М.: Радио и связь, 1987. - 384 с., стор. 114, рис. 5.59. ФОРМУЛА ВИНАХОДУ 25 30 Пристрій для накопичення сум чисел, що містить n-розрядний суматор та перший n-розрядний регістр, при цьому n-розрядний інформаційний вхід пристрою підключено до першого nрозрядного входу n-розрядного суматора, n-розрядний вихід якого підключено до n-розрядного інформаційного входу першого n-розрядного регістра, вхід скидання та синхровхід якого підключено відповідно до входу скидання пристрою та тактового входу пристрою, а n-розрядний вихід підключено до n-розрядного виходу пристрою, який відрізняється тим, що введено другий n-розрядний регістр, при цьому вхід скидання та тактовий вхід пристрою підключено відповідно до входу скидання та синхровходу другого n-розрядного регістра, n-розрядний інформаційний вхід якого підключено до n-розрядного виходу першого n-розрядного регістра, а n-розрядний вихід підключено до другого n-розрядного входу n-розрядного суматора. 2 UA 110904 C2 Комп’ютерна верстка Л. Литвиненко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 17/00, G06F 11/263

Мітки: накопичення, пристрій, чисел, сум

Код посилання

<a href="https://ua.patents.su/5-110904-pristrijj-dlya-nakopichennya-sum-chisel.html" target="_blank" rel="follow" title="База патентів України">Пристрій для накопичення сум чисел</a>

Попередній патент: Сільськогосподарський ґрунтообробний агрегат

Наступний патент: Опалювальний твердопаливний котел

Випадковий патент: Надтвердий матеріал