Аналізатор алгоритмічних перетворювачів

Номер патенту: 112426

Опубліковано: 12.12.2016

Автори: Косенко Віктор Васильович, Дергачов Володимир Андрійович, Павлик Ганна Володимирівна

Формула / Реферат

Аналізатор алгоритмічних перетворювачів, що має дві групи інформаційних входів, формувач адреси, двійковий лічильник, елемент І, керуючий вхід, елемент НІ, вихід наявності даних, мультиплексор, дешифратор, генератор імпульсів, шину результату, причому перша група інформаційних входів з'єднана з інформаційними входами першого мультиплексора, друга група інформаційних входів з'єднана з першою групою входів формувача адреси, виходи першого двійкового лічильника з'єднані з другою групою входів формувача адреси, виходи формувача адреси з'єднані з адресними входами першого мультиплексора, виходи першого мультиплексора з'єднані з входами дешифратора, керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення першого двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника, вихід генератора імпульсів з'єднаний з третім входом елемента І, який відрізняється тим, що містить другий мультиплексор, третю групу інформаційних входів, другий двійковий лічильник, причому виходи дешифратора з'єднані з інформаційними входами другого мультиплексора, третя група інформаційних входів з'єднана з адресними входами другого мультиплексора, вихід другого мультиплексора з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з шиною результату.

Текст

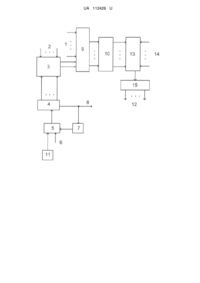

Реферат: Аналізатор алгоритмічних перетворювачів має дві групи інформаційних входів, формувач адреси, двійковий лічильник, елемент І, керуючий вхід, елемент НІ, вихід наявності даних, мультиплексор, дешифратор, генератор імпульсів, шину результату. Перша група інформаційних входів з'єднана з інформаційними входами першого мультиплексора. Друга група інформаційних входів з'єднана з першою групою входів формувача адреси. Виходи першого двійкового лічильника з'єднані з другою групою входів формувача адреси. Виходи формувача адреси з'єднані з адресними входами першого мультиплексора. Виходи першого мультиплексора з'єднані з входами дешифратора. Керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення першого двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника. Вихід генератора імпульсів з'єднаний з третім входом елемента І. Аналізатор додатково містить другий мультиплексор, третю групу інформаційних входів, другий двійковий лічильник. Виходи дешифратора з'єднані з інформаційними входами другого мультиплексора. Третя група інформаційних входів з'єднана з адресними входами другого мультиплексора. Вихід другого мультиплексора з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з шиною результату. UA 112426 U (12) UA 112426 U UA 112426 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначена для аналізу алгоритмічних перетворювачів, а саме - визначення підфункцій, що реалізуються під час настройок керуючих алгоритмів. Відомий пристрій для логічної обробки інформації, що містить вхідні шини коефіцієнтів рівняння, вхідну шину правої частини рівняння, шину результату, двійковий лічильник, групи з першої по n-ну елементів І, операційний пристрій, блок порівняння, тригер, два елементи НІ, два індикатори, генератор імпульсів, два елементи І, суматори по модулю 2, виходи операційного пристрою, елементи РІВНОЗНАЧНІСТЬ (а.с. СРСР N 1262519, o.G06F 15/20, 1985р.) Недоліком відомого пристрою є обмежені функціональні можливості, бо він не проводить аналіз алгоритмічних перетворювачів. Відомий пристрій для рішення логічних рівнянь (а.с. СРСР N 1411768, кл. G 06 F 15/20, опубл. 23.07.88р.), що містить дві групи інформаційних входів, генератор імпульсів, двійковий лічильник, елемент І, елемент НІ, керуючий вхід, вихід наявності даних, шину результату, причому керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, вихід генератора імпульсів з'єднаний з третім входом елемента І. Недоліком відомого пристрою є обмежені функціональні можливості, бо він не проводить аналіз алгоритмічних перетворювачів. Найбільш близьким по технічній суті і результату, що досягається є аналізатор алгоритмічних перетворювачів (Патент України № 52394, G06F 17/00. Опубл. 16.12.2002, Бюл. № 12, автори Чумаченко І.В., Косенко В.В.), що має дві групи інформаційних входів, формувач адреси, двійковий лічильник, елемент І, керуючий вхід, елемент НІ, вихід наявності даних, мультиплексор, дешифратор, генератор імпульсів, шину результату, причому перша група інформаційних входів з'єднана з інформаційними входами першого мультиплексора, друга група інформаційних входів з'єднана з першою групою входів формувача адреси, виходи першого двійкового лічильника з'єднані з другою групою входів формувача адреси, виходи формувача адреси з'єднані з адресними входами першого мультиплексора, виходи першого мультиплексора з'єднані з входами дешифратора, керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення першого двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника, вихід генератора імпульсів з'єднаний з третім входом елемента І. Недоліками відомого пристрою є обмежені функціональні можливості, бо він не дозволяє аналізувати виконання заданих операторів, та велика складність, обумовлена великою кількістю лічильників. В основу корисної моделі поставлено задачу вдосконалити аналізатор алгоритмічних перетворювачів шляхом введення нового складу елементів, та нової організації взаємозв'язків між ними, забезпечити ширші функціональні можливості при його використанні (аналіз виконання заданих операторів) та меншу складність схеми. Поставлена задача вирішується тим, що аналізатор алгоритмічних перетворювачів має дві групи інформаційних входів, формувач адреси, двійковий лічильник, елемент І, керуючий вхід, елемент НІ, вихід наявності даних, мультиплексор, дешифратор, генератор імпульсів, шину результату, причому перша група інформаційних входів з'єднана з інформаційними входами першого мультиплексора, друга група інформаційних входів з'єднана з першою групою входів формувача адреси, виходи першого двійкового лічильника з'єднані з другою групою входів формувача адреси, виходи формувача адреси з'єднані з адресними входами першого мультиплексора, виходи першого мультиплексора з'єднані з входами дешифратора, керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення першого двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника, вихід генератора імпульсів з'єднаний з третім входом елемента І, згідно з корисною моделлю містить другий мультиплексор, третю групу інформаційних входів, другий двійковий лічильник, причому виходи дешифратора з'єднані з інформаційними входами другого мультиплексора, третя група інформаційних входів з'єднана з адресними входами другого мультиплексора, вихід другого мультиплексора з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з шиною результату. Заявлений пристрій має новий склад елементів, та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості корисної 1 UA 112426 U 5 10 15 20 25 30 35 40 45 моделі. Технічний результат, як наслідок цих властивостей - розширені функціональні можливості пристрою, та спрощення схеми пристрою. На кресленні представлена функціональна схема аналізатора алгоритмічних перетворювачів. Аналізатор алгоритмічних перетворювачів має першу та групу інформаційних входів 1, 2, формувач адреси 3, перший двійковий лічильник 4, елемент І 5, керуючий вхід 6, елемент НІ 7, вихід наявності даних 8, перший мультиплексор 9, дешифратор 10, генератор імпульсів 11, шину результату 12, другий мультиплексор 13, третю групу інформаційних входів 14, другий двійковий лічильник 15, причому перша група інформаційних входів 1 з'єднана з інформаційними входами першого мультиплексора 9, друга група інформаційних входів 2 з'єднана з першою групою входів формувача адреси З, виходи першого двійкового лічильника 4 з'єднані з другою групою входів формувача адреси 3, виходи формувача адреси 3 з'єднані з адресними входами першого мультиплексора 9, виходи першого мультиплексора 9 з'єднані з входами дешифратора 10, керуючий вхід 6 з'єднаний з першим входом елемента І 5, вихід переповнення першого двійкового лічильника 5 з'єднаний з виходом наявності даних 8 та через елемент НІ 7 з другим входом елемента І 5, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника 4, вихід генератора імпульсів 11 з'єднаний з третім входом елемента І 5, виходи дешифратора 10 з'єднані з інформаційними входами другого мультиплексора 13, третя група інформаційних входів 14 з'єднана з адресними входами другого мультиплексора 13, вихід другого мультиплексора 13 з'єднаний з рахунковим входом другого двійкового лічильника 15, виходи якого з'єднані з шиною результату 12. Працює аналізатор алгоритмічних перетворювачів таким чином. У початковому стані двійкові лічильники 4 та 15 знаходяться в стані "0". На першу групу інформаційних входів 1 (далі на інформаційні входи мультиплексора 9) подаються значення послідовності виконання операторів на відповідних двійкових наборах змінних. На другу групу інформаційних входів 2 подаються фіксовані значення настроювальних сигналів. На третю групу інформаційних входів 14 подається номер оператора, виконання якого аналізується. На керуючий вхід 6 подається сигнал "1" і імпульси з виходу генератора 11 проходять через елемент І 5 на рахунковий вхід двійкового лічильника 4. Формувач адреси 3 об'єднує настроювальні сигнали та сигнали з виходів двійкового лічильника 4 і таким чином формує адресні сигнали мультиплексора 9. Мультиплексор 9 згідно з адресою формує на своєму виході значення послідовності операторів, що виконується на відповідному наборі змінних, яке поступає на входи дешифратора 10. Унітарний код, що при цьому з'являється на виходах дешифратора 10 поступає на інформаційні входи другого мультиплексора 13. Сигнали з третьої групи інформаційних входів 14 поступають на адресні входи другого мультиплексора 13 і на його виході формується значення "1", якщо оператор, що аналізується виконується і "0" якщо не виконується. Значення "1" на виході другого мультиплексора 13 поступає на рахунковий вхід другого двійкового лічильника 15 і додає одиницю до його стану. По закінченню процесу перебору значень двійкових наборів, про що свідчить сигнал "1" на виході 8 наявності даних, на шині результату 12 сформовано значення кількості наборів при яких виконується оператор, що досліджується. n Заявлений пристрій має лише 2 двійкових лічильника, у той час, як прототип має 2 +1 лічильників. Таким чином заявлений пристрій має ширші функціональні можливості при його використанні (аналіз виконання заданих операторів) та меншу складність схеми. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 50 55 60 Аналізатор алгоритмічних перетворювачів, що має дві групи інформаційних входів, формувач адреси, двійковий лічильник, елемент І, керуючий вхід, елемент НІ, вихід наявності даних, мультиплексор, дешифратор, генератор імпульсів, шину результату, причому перша група інформаційних входів з'єднана з інформаційними входами першого мультиплексора, друга група інформаційних входів з'єднана з першою групою входів формувача адреси, виходи першого двійкового лічильника з'єднані з другою групою входів формувача адреси, виходи формувача адреси з'єднані з адресними входами першого мультиплексора, виходи першого мультиплексора з'єднані з входами дешифратора, керуючий вхід з'єднаний з першим входом елемента І, вихід переповнення першого двійкового лічильника з'єднаний з виходом наявності даних та через елемент НІ з другим входом елемента І, вихід якого з'єднаний з рахунковим входом першого двійкового лічильника, вихід генератора імпульсів з'єднаний з третім входом елемента І, який відрізняється тим, що містить другий мультиплексор, третю групу 2 UA 112426 U інформаційних входів, другий двійковий лічильник, причому виходи дешифратора з'єднані з інформаційними входами другого мультиплексора, третя група інформаційних входів з'єднана з адресними входами другого мультиплексора, вихід другого мультиплексора з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з шиною результату. Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 9/305, G06F 17/00

Мітки: перетворювачів, аналізатор, алгоритмічних

Код посилання

<a href="https://ua.patents.su/5-112426-analizator-algoritmichnikh-peretvoryuvachiv.html" target="_blank" rel="follow" title="База патентів України">Аналізатор алгоритмічних перетворювачів</a>

Попередній патент: Автоматизована система контролю

Наступний патент: Абажур

Випадковий патент: Спосіб багатофакторного аналізу летальності у постраждалих з поєднаною травмою