Пристрій для визначення еквівалентності планів багатофакторного експерименту

Номер патенту: 120123

Опубліковано: 25.10.2017

Автори: Костенко Олена Михайлівна, Дергачов Володимир Андрійович, Кошовий Микола Дмитрович, Кошова Ірина Іванівна, Павлик Ганна Володимирівна

Формула / Реферат

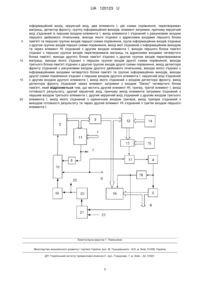

Пристрій для визначення еквівалентності планів багатофакторного експерименту має групу інформаційних входів, два двійкових лічильники чотири блоки пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, два елементи І, дві схеми порівняння, перетворювач матриць, детектор фронту, группу інформаційних виходів, елемент затримки, причому керуючий вхід з'єднаний із першим входом елемента І, вихід елемента І з'єднаний з рахунковим входом першого двійкового лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з інформаційним виходом та через елемент НІ з'єднаний з другим входом елемента І, виходи першого блока пам'яті з'єднані з першою групою входів перетворювача матриць та адресними входами четвертого блока пам'яті, виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, вихід детектора фронту з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з інформаційними входами четвертого блока пам'яті та групою інформаційних виходів, виходи другої схеми порівняння з'єднані з першим входом другого елемента І, керуючий вхід з'єднаний з другим входом другого елемента І, вихід якого з'єднаний з входом детектора фронту, вихід детектора фронту з'єднаний через елемент затримки з входом «Запис» четвертого блока пам'яті, який відрізняється тим, що містить другий елемент НІ, тригер, третій елемент І, вихід готовності результату, другий керуючий вхід, причому вихід елемента затримки з'єднаний з першим входом третього елемента І, другий керуючий вхід з'єднаний з другим входом третього елемента І, вихід якого з'єднаний з одиничним входом тригера, вихід тригера з’єднаний з виходом готовності результату та через другий елемент НІ з’єднаний з третім входом першого елемента І.

Текст

Реферат: Пристрій для визначення еквівалентності планів багатофакторного експерименту має групу інформаційних входів, два двійкових лічильники чотири блоки пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, два елементи І, дві схеми порівняння, перетворювач матриць, детектор фронту, группу інформаційних виходів, елемент затримки, причому керуючий вхід з'єднаний із першим входом елемента І, вихід елемента І з'єднаний з рахунковим входом першого двійкового лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з інформаційним виходом та через елемент НІ з'єднаний з другим входом елемента І, виходи першого блоку пам'яті з'єднані з першою групою входів перетворювача матриць та адресними входами четвертого блока пам'яті. Виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, вихід детектора фронту з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з інформаційними входами четвертого блока пам'яті та групою інформаційних виходів, виходи другої схеми порівняння з'єднані з першим входом другого елемента І, керуючий вхід з'єднаний з другим входом другого елемента І, вихід якого з'єднаний з входом детектора фронту, вихід детектора фронту з'єднаний через елемент затримки з входом "Запис" четвертого блока пам'яті, причому містить другий елемент НІ, тригер, третій елемент І, вихід готовності результату, другий керуючий вхід, причому вихід елемента затримки з'єднаний з першим входом третього елемента І, другий керуючий вхід з'єднаний з другим входом третього елемента І, вихід якого з'єднаний з одиничним входом тригера, вихід тригера з’єднаний з виходом готовності результату та через другий елемент НІ з’єднаний з третім входом першого елемента І. UA 120123 U (12) UA 120123 U UA 120123 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначена для рішення задачі визначення еквівалентності планів багатофакторного експерименту. Відомий пристрій для визначення еквівалентності бінарних матриць [Пат. 33713 України, МПК G 06 F 15/00. № 200802341; заявл. 22.02.2008; опубл. 10.07.2008, Бюл. № 13], що містить групу інформаційних входів, лічильник, перший блок пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, елемент І, першу схему порівняння, перетворювач матриць, другу схему порівняння, другий та третій блоки пам'яті. Недоліком відомого пристрою є обмежені функціональні можливості. Відомий пристрій для визначення еквівалентності планів багатофакторного експерименту [Пат. 60537 України, МПК G 06 F 15/00. № 201013497; заявл. 15.11.2010; опубл. 25.06.2011, Бюл. № 12], що містить групу інформаційних входів, два двійкових лічильника, чотири блоки пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, елемент І, дві схеми порівняння, перетворювач матриць, детектор фронту, групу інформаційних виходів. Недоліком відомого пристрою є обмежені функціональні можливості. Найбільш близьким по технічній суті і результату, що досягається, є пристрій для визначення еквівалентності планів багатофакторного експерименту [Пат. 67311 України, МПК G06F 15/00, заявл. 08.08.2011; опубл. 10.02.2012, Бюл. № 3], що містить групу інформаційних входів, два двійкових лічильники, чотири блоки пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, два елементи І, дві схеми порівняння, перетворювач матриць, детектор фронту, групу інформаційних виходів, елемент затримки, причому керуючий вхід з'єднаний із першим входом елемента І, вихід елемента І з'єднаний з рахунковим входом першого двійкового лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з інформаційним виходом та через елемент НІ з'єднаний з другим входом елемента І, виходи першого блока пам'яті з'єднані з першою групою входів перетворювача матриць та адресними входами четвертого блока пам'яті, виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, вихід детектора фронту з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з інформаційними входами четвертого блока пам'яті та групою інформаційних виходів, виходи другої схеми порівняння з'єднані з першим входом другого елемента І, керуючий вхід з'єднаний з другим входом другого елемента І, вихід якого з'єднаний з входом детектора фронту, вихід детектора фронту з'єднаний через елемент затримки з входом "Запис" четвертого блока пам'яті. Недоліком відомого пристрою є обмежені функціональні можливості. В основу корисної моделі поставлено задачу вдосконалити пристрій для визначення еквівалентності планів багатофакторного експерименту шляхом введення нового складу елементів, та нової організації взаємозв'язків між ними забезпечити ширші функціональні можливості. Поставлена задача вирішується тим, що пристрій для визначення еквівалентності планів багатофакторного експерименту, який має групу інформаційних входів, два двійкових лічильники, чотири блоки пам'яті, елемент НІ, інформаційний вихід, керуючий вхід, два елементи І, дві схеми порівняння, перетворювач матриць, детектор фронту, групу інформаційних виходів, елемент затримки, причому керуючий вхід з'єднаний із першим входом елемента І, вихід елемента І з'єднаний з рахунковим входом першого двійкового лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з інформаційним виходом та через елемент НІ з'єднаний з другим входом елемента І, виходи першого блока пам'яті з'єднані з першою групою входів перетворювача матриць та адресними входами четвертого блока пам'яті, виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, вихід детектора фронту з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з інформаційними входами четвертого блока пам'яті та групою інформаційних виходів, виходи другої схеми порівняння з'єднані з першим входом другого елемента І, керуючий вхід з'єднаний з другим входом другого елемента І, вихід якого з'єднаний з входом детектора фронту, вихід детектора фронту з'єднаний через елемент затримки з входом "Запис" четвертого блока пам'яті, згідно з корисною моделлю, містить другий елемент НІ, тригер, третій елемент І, вихід готовності результату, другий керуючий вхід, 1 UA 120123 U 5 10 15 20 25 30 35 40 45 50 55 причому вихід елемента затримки з'єднаний з першим входом третього елемента І, другий керуючий вхід з'єднаний з другим входом третього елемента І, вихід якого з'єднаний з одиничним входом тригера, вихід тригера з'єднаний з виходом готовності результату та через другий елемент НІ з'єднаний з третім входом першого елемента І. Заявлений пристрій має новий склад елементів, та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості пристрою. Технічний результат, як наслідок цих властивостей - спроможність не тільки встановлювати факт еквівалентності планів багатофакторного експерименту, але і формувати множину еквівалентних перетворювань. На кресленні представлена функціональна схема пристрою для визначення еквівалентності планів багатофакторного експерименту, який містить групу інформаційних входів 1, два двійкових лічильника 2, 5, чотири блоки пам'яті 3, 14, 15, 16, детектор фронту 4, елемент 6, інформаційний вихід 7, групу інформаційних виходів 8, керуючий вхід 9, елемент І 10, дві схеми порівняння 11, 13, перетворювач матриць 12, другий елемент І 17, елемент затримки 18, другий елемент НІ 19, тригер 20, третій елемент І 21, вихід готовності результату 22, другий керуючий вхід 23, причому керуючий вхід 9 з'єднаний із першим входом елемента І 10, вихід елемента І 10 з'єднаний з рахунковим входом першого двійкового лічильника 2, виходи якого з'єднані з адресними входами першого блока пам'яті 3 та першою групою входів першої схеми порівняння 11, група інформаційних входів 1 з'єднана з другою групою входів першої схеми порівняння 11, вихід якої з'єднаний з інформаційним виходом 7 та через елемент НІ 6 з'єднаний з другим входом елемента І 10, виходи першого блока пам'яті 3 з'єднані з першою групою входів перетворювача матриць 12 та адресними входами четвертого блока пам'яті 16, виходи другого блока пам'яті 14 з'єднані з другою групою входів перетворювача матриць 12, виходи якого з'єднані з першою групою входів другої схеми порівняння 13, виходи третього блока пам'яті 15 з'єднані з другою групою входів другої схеми порівняння 13, вихід детектора фронту 4 з'єднаний з рахунковим входом другого двійкового лічильника 5, виходи якого з'єднані з інформаційними входами четвертого блоку пам'яті 16 та групою інформаційних виходів 8, виходи другої схеми порівняння 13 з'єднані з першим входом другого елемента І 17, керуючий вхід 9 з'єднаний з другим входом другого елементу І 17, вихід якого з'єднаний з входом детектора фронту 4, вихід детектора фронту 4 з'єднаний через елемент затримки 18 з входом "Запис" четвертого блоку пам'яті 16, вихід елемента затримки 18 з'єднаний з першим входом третього елемента І 21, другий керуючий вхід 21 з'єднаний з другим входом третього елемента І 21, вихід якого з'єднаний з одиничним входом тригера 20, вихід тригера 20 з'єднаний з виходом готовності результату 22, та через другий елемент НІ 19 з'єднаний з третім входом першого елемента І 10. Працює пристрій таким чином. На інформаційні входи 1 подається двійковий код значення кількості варіантів перетворень матриць. На другий керуючий вхід 23 подається Сигнал "0", якщо потрібно визначити множину варіантів еквівалентних перетворень. Спочатку лічильники 2, 5 знаходяться в стані "0". Тригер 20 знаходиться у стані "0". На керуючий вхід 9 подаються імпульси, що поступово змінюють стан лічильника 2. Для кожного значення коду, що надходить на перший блок пам'яті 3 на його виході формується вид перетворень і на виходах перетворювача матриць 12 формується новий вид матриці. Ці значення порівнюються в другій схеми порівняння 13 зі значеннями, що записані в третьому блоці пам'яті 15. Якщо значення співпадають, то на виході другої схеми порівняння 13 формується сигнал "1", який через елемент І 17 та детектор фронту 4 надходить на рахунковий вхід двійкового лічильника 5, змінюючи його стан на наступний. В блок пам'яті 16 записується код відповідного перетворення плану синхронно з керуючим сигналом на вході 9 через час затримки, який задає елемент затримки 18. Це підвищує надійність роботи пристрою. Якщо перебрані всі варіанти перетворень, то на виході 7 формується сигнал "1" і елемент І 10 закривається. На інформаційних виходах 8 сформована кількість еквівалентних перетворень планів багатофакторного експерименту. Коди перетворень записані у блоці пам'яті 16. Для встановлення факту еквівалентності планів багатофакторного експерименту на другий керуючий вхід подається сигнал "1". Якщо буде визначена еквівалентність планів, то на виході елемента І 21 формується сигнал "1", який переводить тригер 20 у стан "1", на виході 22 формується сигнал "1", який вказує, що плани еквівалентні, елемент І 10 закривається і пристрій припиняє роботу. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 60 Пристрій для визначення еквівалентності планів багатофакторного експерименту має групу інформаційних входів, два двійкових лічильники чотири блоки пам'яті, елемент НІ, 2 UA 120123 U 5 10 15 20 інформаційний вихід, керуючий вхід, два елементи І, дві схеми порівняння, перетворювач матриць, детектор фронту, группу інформаційних виходів, елемент затримки, причому керуючий вхід з'єднаний із першим входом елемента І, вихід елемента І з'єднаний з рахунковим входом першого двійкового лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з інформаційним виходом та через елемент НІ з'єднаний з другим входом елемента І, виходи першого блока пам'яті з'єднані з першою групою входів перетворювача матриць та адресними входами четвертого блока пам'яті, виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, вихід детектора фронту з'єднаний з рахунковим входом другого двійкового лічильника, виходи якого з'єднані з інформаційними входами четвертого блока пам'яті та групою інформаційних виходів, виходи другої схеми порівняння з'єднані з першим входом другого елемента І, керуючий вхід з'єднаний з другим входом другого елемента І, вихід якого з'єднаний з входом детектора фронту, вихід детектора фронту з'єднаний через елемент затримки з входом "Запис" четвертого блока пам'яті, який відрізняється тим, що містить другий елемент НІ, тригер, третій елемент І, вихід готовності результату, другий керуючий вхід, причому вихід елемента затримки з'єднаний з першим входом третього елемента І, другий керуючий вхід з'єднаний з другим входом третього елемента І, вихід якого з'єднаний з одиничним входом тригера, вихід тригера з’єднаний з виходом готовності результату та через другий елемент НІ з’єднаний з третім входом першого елемента І. Комп’ютерна верстка Г. Паяльніков Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/00

Мітки: експерименту, еквівалентності, визначення, планів, пристрій, багатофакторного

Код посилання

<a href="https://ua.patents.su/5-120123-pristrijj-dlya-viznachennya-ekvivalentnosti-planiv-bagatofaktornogo-eksperimentu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення еквівалентності планів багатофакторного експерименту</a>