Аналого-цифровий перетворювач

Номер патенту: 12879

Опубліковано: 15.03.2006

Автори: Стальченко Олександр Володимирович, Бортник Геннадій Григорович, Бортник Сергій Геннадійович

Формула / Реферат

Аналого-цифровий перетворювач, який містить послідовно з'єднані джерело опорних напруг, ![]() компараторів, різницевий пристрій, причому перші входи компараторів з'єднані з шиною джерела вхідної напруги, що підлягає перетворенню, а другі входи під'єднані до шини джерела опорних напруг, виходи

компараторів, різницевий пристрій, причому перші входи компараторів з'єднані з шиною джерела вхідної напруги, що підлягає перетворенню, а другі входи під'єднані до шини джерела опорних напруг, виходи ![]() компараторів з'єднані з входами

компараторів з'єднані з входами ![]() елементів пам'яті через першу групу елементів І та групу елементів АБО, входи

елементів пам'яті через першу групу елементів І та групу елементів АБО, входи ![]() елементів пам'яті під'єднані до шин старших розрядів, який відрізняється тим, що введені аналоговий комутатор,

елементів пам'яті під'єднані до шин старших розрядів, який відрізняється тим, що введені аналоговий комутатор, ![]() D-тригери, друга група елементів І, елементи І з інверсним входом, елемент затримки, елемент АБО з

D-тригери, друга група елементів І, елементи І з інверсним входом, елемент затримки, елемент АБО з ![]() входами, RS-тригер, два аналогових ключі, елемент І, причому аналогові входи аналогового комутатора під'єднані до шини джерела опорної напруги, а виходи аналогового комутатора з'єднані з інверсним входом різницевого пристрою, прямий вхід якого, як і вхід першого аналогового ключа, під'єднаний до шини джерела вхідної напруги, що підлягає перетворенню, вихід різницевого пристрою з'єднаний з входом другого аналогового ключа, вихід якого, як і вихід першого аналогового ключа під'єднаний до шини джерела вхідної напруги, що підлягає перетворенню, керуючий вхід першого аналогового ключа з'єднаний з інверсним виходом RS-тригера, а керуючий вхід другого аналогового ключа - з прямим виходом RS-тригера, R-вхід якого під'єднаний до вхідної шини керуючого сигналу, до R-входів елементів пам'яті і до інверсних входів елементів І з інверсним входом, а S-вхід тригера під'єднаний до виходу елемента АБО з

входами, RS-тригер, два аналогових ключі, елемент І, причому аналогові входи аналогового комутатора під'єднані до шини джерела опорної напруги, а виходи аналогового комутатора з'єднані з інверсним входом різницевого пристрою, прямий вхід якого, як і вхід першого аналогового ключа, під'єднаний до шини джерела вхідної напруги, що підлягає перетворенню, вихід різницевого пристрою з'єднаний з входом другого аналогового ключа, вихід якого, як і вихід першого аналогового ключа під'єднаний до шини джерела вхідної напруги, що підлягає перетворенню, керуючий вхід першого аналогового ключа з'єднаний з інверсним виходом RS-тригера, а керуючий вхід другого аналогового ключа - з прямим виходом RS-тригера, R-вхід якого під'єднаний до вхідної шини керуючого сигналу, до R-входів елементів пам'яті і до інверсних входів елементів І з інверсним входом, а S-вхід тригера під'єднаний до виходу елемента АБО з ![]() входами,

входами, ![]() входи якого з'єднані відповідно з

входи якого з'єднані відповідно з ![]() прямими виходами елементів пам'яті, а останній вхід елемента АБО з

прямими виходами елементів пам'яті, а останній вхід елемента АБО з ![]() входами з'єднаний з входом елемента І, перший вхід якого з'єднаний з інверсним виходом першого компаратора, а другий - з входом елемента затримки, вхід якого з'єднаний з інверсним виходом RS-тригера, з другими входами другої групи елементів І, перші входи яких з'єднані з виходами групи елементів АБО і з шинами молодших розрядів, виходи другої групи елементів І з'єднані з S-входами елементів пам'яті, інверсний вихід RS-тригера під'єднаний до керуючих входів D-тригерів, інформаційні входи яких з'єднані з виходами першої групи елементів І і прямим виходом n-го компаратора відповідно, виходи D-тригерів під'єднані до прямих входів елементів І з інверсним входом, виходи яких з'єднані з керуючими входами аналогового комутатора.

входами з'єднаний з входом елемента І, перший вхід якого з'єднаний з інверсним виходом першого компаратора, а другий - з входом елемента затримки, вхід якого з'єднаний з інверсним виходом RS-тригера, з другими входами другої групи елементів І, перші входи яких з'єднані з виходами групи елементів АБО і з шинами молодших розрядів, виходи другої групи елементів І з'єднані з S-входами елементів пам'яті, інверсний вихід RS-тригера під'єднаний до керуючих входів D-тригерів, інформаційні входи яких з'єднані з виходами першої групи елементів І і прямим виходом n-го компаратора відповідно, виходи D-тригерів під'єднані до прямих входів елементів І з інверсним входом, виходи яких з'єднані з керуючими входами аналогового комутатора.

Текст

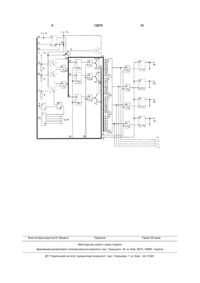

Аналого-цифровий перетворювач, який містить послідовно з'єднані джерело опорних напруг, n 2 2 1 компараторів, різницевий пристрій, причому перші входи компараторів з'єднані з шиною джерела вхідної напруги, що підлягає перетворенню, а другі входи під'єднані до шини джерела опоn рних напруг, виходи 2 2 1 компараторів з'єднані з n входами елементів пам'яті через першу групу 2 n елементів І та групу елементів АБО, входи 2 елементів пам'яті під'єднані до шин старших розрядів, який відрізняється тим, що введені аналоn говий комутатор, 2 2 1 D-тригери, друга група елементів І, елементи І з інверсним входом, елеn мент затримки, елемент АБО з 1 входами, RS2 тригер, два аналогових ключі, елемент І, причому аналогові входи аналогового комутатора під'єднані до шини джерела опорної напруги, а виходи аналогового комутатора з'єднані з інверсним входом різницевого пристрою, прямий вхід якого, як і вхід U 2 UA 1 3 12879 4 першим входом першого перетворювача кодn струм, вихід якого з'єднаний з першим виходом цевий пристрій, перші входи 2 2 1 компараторів резистивного подільника, другий вихід блоку керуз'єднані з шиною джерела вхідної напруги, яка вання з'єднаний з першим входом другого перетпідлягає перетворенню, а другі входи під'єднані до m ворювача код-струм, вихід якого з'єднаний з 2 -1 шини джерела опорних напруг, виходи компаратовиходом резистивного подільника, а вхід резистирів з'єднані з входами елементів пам'яті через грувного подільника з'єднаний з шиною джерела попу елементів І та АБО, виходи елементів пам'яті чаткового зміщення, третій вихід блоку керування під'єднані до шини старших розрядів, введені аназ'єднаний з входом блоку пам'яті, перший вихід n якого через цифро-аналоговий перетворювач (ЦАП) з'єднаний з другими входами першого і друлоговий комутатор, 2 2 1 D-тригери, друга група гого перетворювачів код-струм, другий вихід блоку елементів І, елементи І з інверсним входом, елепам'яті з'єднаний з першими входами додаткових n мент затримки, елемент АБО з 1 входами, RSперетворювачів код-струм, вихід одного з яких 2 з'єднаний з першим входом резистивного подільтригер, два аналогових ключа, причому аналогові ника, а вихід другого з 2m-1 виходом резистивного входи аналогового комутатора під'єднані до шини подільника [авторське свідоцтво СРСР №651475 джерела опорної напруги, а входи аналогового МКИ - Н03К13/02 бюлетень №9, 1979р.]. комутатора з'єднані з інверсним входом різницевоНедоліком цього пристрою є низька швидкодія го пристрою, прямий вхід якого і вхід першого анаі складність АЦП. логового ключа під'єднані до шини джерела вхідВідомий аналого-цифровий перетворювач, ної напруги, що підлягає перетворенню, вихід який містить малорозрядний АЦП, виходи якого різницевого пристрою з'єднаний з входом другого підключені до шин старших розрядів, ЦАП, вихід аналогового ключа, вихід якого і вихід першого якого з'єднаний з входом подільника напруги, до аналогового ключа під'єднані до перших входів виходів подільника під'єднані компаратори, другі компараторів, керуючий вхід першого аналогового входи яких під'єднані до шини вхідної напруги, ключа з'єднаний з інверсним виходом RS-тригера, виходи компараторів під'єднані до шин молодших а керуючий вхід другого аналогового ключа - з розрядів [заявка ФРН №274316, кл. Н03К13/05]. прямим виходом RS-тригера, R-вхід якого підклюНедоліком даного АЦП є низька швидкодія печений до вхідної шини керуючого сигналу, до Rретворення. входів елементів пам'яті і до інверсних входів Найбільш близьким є 8-розрядний аналогоелементів І з інверсним входом, а S-вхід тригера цифровий перетворювач, який містить два 4n розрядних АЦП, кожен з яких містить послідовно під'єднаний до виходу елемента АБО з 1 вхо2 n n дами, перші входи якого з'єднані відповідно з з'єднані джерело опорних напруг і набір 2 2 1 2 компараторів, різницевий пристрій, перші входи прямими виходами елементів пам'яті, а останній компараторів першого 4-розрядного АЦП з'єднані з n шиною джерела вхідної напруги, що підлягає певхід елемента АБО 1 входами з'єднаний з виретворенню, виходи компараторів першого 42 розрядного АЦП з'єднані з входами елементів паходом елемента І, перший вхід якого з'єднаний з м'яті через групу елементів І та АБО, виходи елеінверсним виходом першого компаратора, а друментів пам'яті під'єднані до шин старших розрядів і гий - з виходом елемента затримки, вхід якого до входів ЦАП, вихід якого з'єднаний з другим з'єднаний з інверсним виходом RS-тригера, з друвходом різницевого пристрою, перший вхід якого гими входами другої групи елементів І, перші вхопід'єднаний до шини джерела вхідної напруги, що ди яких з'єднані з виходами групи елементів АБО і підлягає перетворенню, вихід різницевого приз шинами молодших розрядів, виходи елементів І строю з'єднаний з першими входами компараторів другої групи з'єднані з S-входами елементів пам'ядругого 4-розрядного АЦП, другі входи яких і другі ті, інверсний вихід RS-тригера під'єднаний до кевходи першого 4-розрядного АЦП під'єднані до руючих входів D-тригерів, інформаційні входи яких шини джерела опорних напруг, виходи компаратоз'єднані з виходами елементів І першої групи і з рів другого 4-розрядного АЦП через групу елеменn тів І та АБО під'єднані до шин молодших розрядів прямим виходом 2 2 1 компаратора відповідно, [патент США №41248224, кл. 330/252 МКИ – виходи D-тригерів під'єднані до прямих входів Н03М1/36]. елементів І з інверсним входом, виходи яких з'єдНедоліком даного АЦП є обмеження по швиднані з керуючими входами аналогового комутатокодії перетворення і складність пристрою. ра. В основу корисної моделі поставлено задачу На креслені наведена структурна електрична створення аналого-цифрового перетворювача, в схема аналого-цифрового перетворювача. якому за рахунок введення нових блоків та зв'язків Пристрій містить шину 1 джерела вхідної напідвищується швидкодія та спрощується пристрій. пруги, що підлягає перетворенню Uвх, вхід шини 2 Поставлена задача досягається тим, що в керуючого сигналу EК, вхід 3 джерела опорної наАЦП, який містить послідовно з'єднані джерело n n n пруги, коло 2 2 1 резисторів 4, 2 2 1 компараопорних напруг, набір 2 2 1 компараторів, різниторів 5 з прямими і інверсними виходами, першу 5 12879 6 групу елементів І 6, елемент затримки 7, зокрема тів пам'яті 15, інверсний вихід RS-тригера 18 під'єднаний до керуючих входів D-тригерів 10, інфорn елемент АБО, елемент І 8, елемент АБО 9 з 1 маційні входи яких з'єднані з виходами елементів І 2 n n першої групи 6 і з прямим виходом 2 2 1 компавходами, 2 2 1 D-тригери 10, елементи І 11 з раторів 5 відповідно, виходи D-тригерів 10 під'єдінверсним входом, аналоговий комутатор 12, групу нані до прямих входів елементів І 11 з інверсним n елементів АБО 13, другу групу елементів І 14, входом, виходи яких з'єднані з керуючими входами 2 аналогового комутатора 12. елементи пам'яті 15, зокрема RS-тригери, з вихоАналого-цифровий перетворювач працює надами 16 старших розрядів, виходи 17 молодших ступним чином. розрядів, RS-тригер 18, перший аналоговий ключ В аналоговому комутаторі 12 з елементом І 8 19, другий аналоговий ключ 20, різницевий приn стрій 21, зокрема диференціальний підсилювач. та елементом АБО 9 з 2 2 1 входами, причому Число компараторів і ключів в аналогодо аналогового комутатора 12 підключають опорну цифровому комутаторі в АЦП, який заявляється напругу з лінійки компараторів 5 безпосередньо до залежить від n - двійкових розрядів перетворення і входу різницевого пристрою 21, аналогові ключі 19 n n та 20, які комутують вхідну шину лінійки компарадорівнює 2 2 1 , причому перші входи 2 2 1 комторів 5 в залежності від величини вхідного сигнапараторів 5 з'єднані з шиною 1 джерела вхідної лу, керуючі імпульси надходять на вхід шини 2 напруги, що підлягає перетворенню, а другі входи керуючого сигналу встановлюють RS-тригер 18 в під'єднані до входу 3 джерела опорної напруги, нульовий стан (Q 0, Q 1) і при надходженні на n інверсні входи елементів І 11 з інверсними входавиходи 2 2 1 компараторів 5 з'єднані з входами ми, встановлюють їх в „0", відкриваючи таким чиn ном всі ключі аналогового комутатора 12. В реелементів пам'яті 15 через першу групу елемезультаті встановлення RS-тригера 18 в нульовий 2 стан перший аналоговий ключ 19 замикається, а n нтів І 6 та групу елементів АБО 13, входи еледругий аналоговий ключ 20 розмикається. Еле2 n мент І 8 і елемент АБО 9 з 1 входами через ментів пам'яті 15 під'єднані до виходів старших 2 розрядів 16, аналогові входи аналогового комутаприсутність елемента затримки 7 спрацьовують тора 12 під'єднані до входу 3 джерела опорної дещо пізніше моменту встановлення RS-тригера напруги, а входи аналогового комутатора 12 з'єд18, що дозволяє вирівняти запізнення в першому нані з інверсним входом різницевого пристрою 21, аналоговому ключі 19 і в компараторах 5. прямий вхід якого і вхід першого аналогового клюНа шину 1, джерела вхідної напруги, яка підляча 19 під'єднані до шини 1 джерела вхідної напругає перетворенню надходить аналоговий сигнал. ги, що підлягає перетворенню, вихід різницевого Через перший аналоговий ключ 19 цей сигнал попристрою 21 з'єднаний з входом другого аналогодається на перші входи компараторів 5, другі вхового ключа 20, вихід якого і вихід першого аналоди яких підключені до кола резисторів 4, які форгового ключа 19 під'єднані до перших входів мують опорні напруги після того, як на вхід 3 n джерела опорної напруги подана опорна напруга 2 2 1 компараторів 5, керуючий вхід першого Uоп. При цьому можуть мати місце два випадки: аналогового ключа 19 з'єднаний з інверсним вихо- значення, яке реєструється, менше напруги, дом RS-тригера 18, а керуючий вхід другого анаяка прикладена до нижнього по схемі резистора логового ключа 20 - з прямим виходом RS-тригера кола резисторів 4; 18, R-вхід якого підключений до вхідної шини 2 - значення, яке реєструється, більше напруги, керуючого сигналу, до R-входів елементів пам'яті яка прикладена до нижнього по схемі резистора 15 і до інверсних входів елементів І 11 з інверсним кола резисторів 4. входом, а S-вхід RS-тригера 18 під'єднаний до В першому випадку на всіх виходах першої n n групи елементів І 6 з'являється логічний „0", і в виходу елемента АБО 9 з 1 входами, перші силу цього всі ключі аналогового комутатора 12 2 2 залишаються розімкнутими, а на інверсний вхід входи якого з'єднані відповідно з прямими виходарізницевого пристрою 21, відповідно подається ми елементів пам'яті 15, а останній вхід елемента логічний „0". Так як на виходи елементів пам'яті 15 n АБО 9 з 1 входами з'єднаний з виходом елесигнал не надходить, тому що на входах групи 2 елементів АБО 13 логічні „0", що веде за собою мента І 8, перший вхід якого з'єднаний з інверсним появу логічних „0" на перших входах другої групи виходом першого компаратора 5, а другий - з виелементів І 14 і, відповідно, на S-входах елементів ходом елемента затримки 7, вхід якого з'єднаний з пам'яті 75, то на виходах 16 старших розрядів збеінверсним виходом RS-тригера 18, з другими вхорігається „0". З інверсного виходу першого компадами другої групи елементів 114, перші входи яких ратора 51 і з елемента затримки 7 подаються логіз'єднані з виходами групи елементів АБО 13 і з чні „І" на входи елемента І 8, з елемента І 8 виходами 17 молодших розрядів, виходи елеменn тів І другої групи 14 з'єднані з S-входами елеменподається „І" на вхід елемента АБО 9 з 1 вхо2 7 12879 8 RS-тригер 18 встановлюється в одиничний стан. У n дами, ця „1" з виходу елемента АБО 9 з 1 вхотой час, коли аналоговий сигнал перетворюється в 2 цифрову форму, група елементів І 6, D-тригери 10, дами надходить на S-вхід RS-тригера 18, який елементи 111 з інверсним входом формують для маючи на R-вході логічний „0", встановлюється в аналогового комутатора 12 керуючі сигнали таким одиничний стан (Q 1, Q 0) . При цьому перший чином, що на інверсний вхід різницевого пристрою аналоговий ключ 19 - розмикається, а другий анаn логовий ключ 20 замикається. Логічний „0" з інвер21 подається та точка кола 2 2 1 резисторів 4, сного виходу RS-тригера 18 забезпечує незмінний напруга якої завжди менше значення аналогового „0" на виходах 16 старших розрядів, тому що „0" на сигналу, який перетворюється. Різниця напруг між других входах 22 другої групи елементів І 14 веде значенням аналогового сигналу з шини 1 джерела до збереження „0" на S-входах елементів пам'яті вхідної напруги, яка підлягає перетворенню і вихі75. З виходу різницевого пристрою 27 аналоговий дним сигналом компаратора 12 з'являється на сигнал подається на перші входи компараторів 5, виході різницевого пристрою 21. RS-тригер 18 перетворюється за допомогою першої групи елевстановлюється в одиничний стан, перший аналоментів І 6 та групи елементів АБО 13 в двійковий говий ключ 19 розмикається, другий аналоговий код, який надходить на виходи 77 молодших розключ 20 замикається. При цьому на виходах 16 рядів. Так як RS-тригер 18 знаходиться в одиничстарших розрядів зберігається попередній стан ному стані, то „0" з його інверсного виходу, посту(так як R=0, S=0). На виході різницевого пристрою паючи на керуючі входи D-тригерів 10, залишає їх 21 зберігається підсилений різницевий сигнал, в попередньому стані. Таким чином, нові стани який, при надходженні на входи компараторів 5, першої групи елементів І б не можуть бути більше перетворюється, як і в першому випадку, і формуподаними на керуючі входи аналогового комутатоється у вигляді двійкового коду молодших розрядів ра 72. Тому потенціал на виході аналогового комуна виходах 17 молодших розрядів. татора 72 зберігає свій попередній стан. Внаслідок Виконання аналого-цифрового перетворювача цього аналоговий сигнал на виході різницевого згідно схеми корисної моделі з використанням пристрою 27 не перешкоджає формуванню коду аналогового комутатора, підключеного безпосерена виходах 77 молодших розрядів. дньо до кола резисторів, що задає величини опорДругий випадок. Якщо значення сигналу, що них напруг компараторів, дозволяє підвищити реєструється з шини 7 джерела вхідної напруги, швидкодію аналого-цифрового перетворювача з що підлягає перетворенню перевищить падіння одночасним спрощенням пристрою загалом. напруги на нижньому резисторі, то на виході елеДля реалізації 8-розрядного АЦП, який заявn мента АБО 9 з 1 входами з'являється логічний 8 2 ляється необхідно 2 2 1 15 компараторів, тоді „0". Аналоговий сигнал перетворюється компараяк 8-розрядний прототип пропонує використання торами 5, першою групою елементів І 6 та групою елементів АБО 13 в цифровий сигнал, який через двох 4-розрядних АЦП, тобто 2 24 1 30 комдругу групу елементів І 14 та елементи пам'яті 75 з'являється на виходах 16 старших розрядів, звідпараторів, що значно ускладнює вихідну кодуючу n логіку, а також весь пристрій загалом. ки надходить на входи елемента АБО 9 з 1 2 входами і встановлює його в „1". Тільки після цього 9 Комп’ютерна верстка М. Мацело 12879 Підписне 10 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog-to-digital converter

Автори англійськоюBortnyk Hennadii Hryhorovych, Bortnyk Serhii Hennadiiovych, Stalchenko Oleksandr Volodymyrovych

Назва патенту російськоюАналого-цифровой преобразователь

Автори російськоюБортник Геннадий Григорьевич, Бортник Сергей Геннадьевич, Стальченко Александр Владимирович

МПК / Мітки

МПК: H03M 1/36

Мітки: перетворювач, аналого-цифровий

Код посилання

<a href="https://ua.patents.su/5-12879-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач</a>

Попередній патент: Ідентифікатор об`єктів з дистанційною активізацією

Наступний патент: Закрита електрична машина

Випадковий патент: Настільний контейнер для сміття