Пристрій канального кодування

Номер патенту: 60624

Опубліковано: 15.10.2003

Автори: Марценюк Валерій Пантелеймонович, Родін Дмитро Сергійович

Формула / Реферат

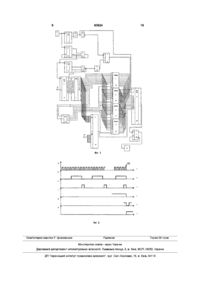

Пристрій канального кодування, який містить генератор синхроімпульсів, перший, другий та третій лічильники імпульсів, інвертор, схему І, формувач імпульсів, перший та другий лічильні тригери, перший та другий регістри зсуву, паралельний регістр, перший та другий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістра під'єднано до першого-десятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, перший-восьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першого-десятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний - до свого інформаційного входу, який відрізняється тим, що в нього введено схему 2І-НІ та другий елемент І, дешифратор, третій та четвертий блоки пам'яті, причому перший-другий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, а перший та другий входи першого елемента І з'єднано з першим та другим виходами першого лічильника імпульсів, вихід першого елемента І під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів другого елемента І відповідно, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано відповідно до першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті.

Текст

Пристрій канального кодування, який містить генератор синхроімпульсів, перший, другий та третій лічильники імпульсів, інвертор, схему І, формувач імпульсів, перший та другий ЛІЧИЛЬНІ тригери, перший та другий регістри зсуву, паралельний регістр, перший та другий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістра під'єднано до першого-десятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано ВІДПОВІДНО ДО першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті Винахід відноситься до обчислювальної техніки, а саме, до пристроїв формування сигналів для високо щільного запису цифрової інформації на магнітний носій Відомий пристрій для магнітного запису цифрової інформації (Ас СРСР №1674232 м кл , G11B5/09, 20/00, бюл №32-1991), який розрахований на збільшення ЩІЛЬНОСТІ магнітного запису за рахунок перекодування інформації в канальний код Каутса-Фібоначі з параметрами n=8, m=9, d=0, k=3 Недоліком пристрою є невисока ЩІЛЬНІСТЬ запису внаслідок малого значення вікна детектування За прототип обрано пристрій канального кодування (патент України №36869 м кл , G11B5/09, 16 04 2001, бюл №3-2001), який містить генератор синхроімпульсів, перший, другий та третій лічиль входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, першийвосьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першогодесятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний - до свого інформаційного входу, який відрізняється тим, що в нього введено схему 2ІНІ та другий елемент І, дешифратор, третій та четвертий блоки пам'яті, причому перший-другий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, а перший та другий входи першого елемента І з'єднано з першим та другим виходами першого лічильника імпульсів, вихід першого елемента І під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів другого елемента І ВІДПОВІДНО, ВИХІД ЯКОГО з'єднано (О о (О 60624 другий та третій лічильники імпульсів, інвертор, схему І, формувач імпульсів, перший та другий ЛІЧИЛЬНІ тригери, перший та другий регістри зсуву, паралельний регістр, перший та другий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра А вихід інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістру під'єднано до першогодесятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, перший-восьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першого-десятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний до свого Інформаційного входу, який відрізняється тим, що в нього введено схему 2І-НІ та другий елемент "І", дешифратор, третій та четвертий блоки пам'яті, при чому перший-другий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, а перший та другий входи першого елемента "І" з'єднано з першим та другим виходами першого лічильника імпульсів, вихід першого елемента "І" під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів другого елемента "І" ВІДПОВІДНО, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано ВІДПОВІДНО до першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті Недолік пристрою - недостатня ЩІЛЬНІСТЬ запису цифрової інформації на магнітний носій В основу винаходу поставлено задачу збільНа фіг 1 представлено функціональну схему шення ЩІЛЬНОСТІ запису цифрової інформації на пристрою канального кодування На фіг 2 предмагнітний носій при збереженні умов самосинхроставлені часові діаграми роботи пристрою канальнізації ного кодування Поставлена задача досягається за рахунок Пристрій складається з генератора (1), під'єдвведення нових блоків та зв'язків між ними, що наного виходом до лічильного входу першого (2) і забезпечує збільшення ЩІЛЬНОСТІ запису інформадругого (3) лічильника імпульсів Виходи першого ції на магнітний носій при використанні перекодулічильника (2) з'єднані з входами першого елеменвання в код Каутса-Фібоначі з параметрами п=10, та "І" (7), вихід якого під'єднаний до інвертора (8) 171=11, d=0, k=3 та синхровходу третього регістра зсуву (19), вихід інвертора (8) з'єднаний з синхровходом першого Для цього пристрій канального кодування, тригера (13), вихід якого під'єднаного до керуючого який містить генератор синхроімпульсів, перший, ники імпульсів, перший та другий інвертори, формувач імпульсів, перший та другий ЛІЧИЛЬНІ тригери, схему І, перший та другий регістри зсуву, паралельний регістр, перший блок пам'яті, цифровий компаратор, блок запису, шину опорного коду та вхідну шину, під'єднану до інформаційного входу першого регістру зсуву, перший-восьмий виходи якого з'єднані з першим-восьмим інформаційними входами паралельного регістра, синхровходи першого та другого ЛІЧИЛЬНИКІВ імпульсів з'єднані з виходом генератора, синхроімпульсів, вихід першого лічильника імпульсів під'єднаний до входу першого інвертора і синхровходу другого регістра зсуву, перший та другий виходи другого лічильника з'єднано з першим та другим входами елемента "І", вихід якого з'єднаний з R-входом установки в нуль другого лічильника імпульсів, другий вихід якого також під'єднано до синхровходу першого регістру зсуву і до синхровходу третього лічильника імпульсів, вихід якого з'єднаний з входом другого інвертора, вихід якого під'єднаний до синхровходу паралельного регістру і входу формувача імпульсів, вихід якого з'єднаний з входом установки в одиницю другого лічильного тригера, вхід синхронізації якого під'єднано до виходу першого інвертора, при цьому вихід другого лічильного тригера з'єднаний з Е-входом установки режиму роботи другого регістра зсуву, вихід якого під'єднано до входу синхронізації першого лічильного тригера, прямий вихід якого під'єднано до блоку запису, а зворотній до інформаційного D-входу другого лічильного тригера, перший-восьмим виходи паралельного регістра з'єднані з першим-восьмим входами цифрового компаратора, а перший-п'ятий виходи паралельного регістра з першим-восьмим входами цифрового компаратора, перший-п'ятий виходи паралельного регістра з першим-п'ятим адресними входами першого запам'ятовуючого пристрою, виходи якого під'єднані до першогоп'ятого інформаційних входів другого регістру зсуву, шина опорного сигналу з'єднана з першимвосьмим входами цифрового компаратора, крім цього другий запам'ятовуючий пристрій, першийчетвертий інформаційні входи якого під'єднано до шостого-дев'ятого виходів паралельного регістру, а виходи до шостого-дев'ятого входів другого регістру зсуву, вихід цифрового компаратора під'єднано до десятого входу другого регістра зсуву, дев'ятий вихід першого регістра зсуву під'єднано до дев'ятого входу паралельного регістра, шина опорного сигналу з'єднана з дев'ятим входом цифрового компаратора 60624 входу третього регістра (19), вихід якого з'єднаний режим паралельного чи послідовного зсуву В з лічильним входом другого тригера (20), інверсблоках пам'яті 15, 16, 17, 18, виконується переконий вихід якого з'єднано з інформаційним входом дування інформації з десяти розрядного двійковоцього тригера, а прямий вихід з'єднано з входом го коду в одинадцяти розрядний код Каутсаблоку запису (21) Вихід блоку запису (21) з'єднуФібоначі Третій регістр 19 перетворює паралельється з магнітною головкою (не показаний) Вихоний запис цього коду в послідовний зсув кодової ди другого лічильника імпульсів (3) зв'язані через інформації, яка після перетворення надходить в другий елемент "І" (9) з його входом скидання в блок запису (21) для формування сигналів запису нуль При цьому один з виходів другого лічильника на магнітний носій (3) під'єднаний до синхровходу третього лічильниВ загальному випадку канального кодування ка імпульсів (4) та синхровходу першого регістру інформаційні комбінації з п - символів двійкового (5) Виходи третього лічильника імпульсів (4) під'вхідного коду заміщується групою з m - символів єднані до входів схем 2І-НІ (10), вихід якої з'єднано канального коду При цьому відношення числа з формувачем імпульсів (12) та синхровходом друсимволів п до m визначає параметр, який називагого регістру (14) Вихід формувача імпульсів (12) ють кодовою швидкістю з'єднано з входом встановлення в одиницю перп Vkk = / m / шого тригера (13) До інформаційного входу D першого регістру (15) підключена вхідна шина (22), Параметр кодової швидкості характеризує перший-десятий інформаційні виходи цього регістступінь зменшення швидкості проходження інфорру під'єднані до першого-десятого інформаційних мації через фізичний канал магнітної реєстрації входів другого регістру (11) Перший-десятий випри її заміщенні за методами канального кодуванходи другого регістру (11) з'єднані з першимня Як правило, чим вища кодова швидкість канадесятим А входами компаратора (14), а входи (В) льного коду, тим менша його надлишковість компаратора (14) під'єднані до шини опорного сиг(m-n) налу (23), вихід компаратора з'єднаний з інформа•100% Н ційним входом D11 третього регістра (19) ПерКанальні коди є кодами з обмеженням довжин ший-восьмий виходи другого регістру (11) під'єдсерій нулів та одиниць Обмеження довжин серій нані до першого-восьмого адресних входів (А1-А8) символів канального коду дозволяє забезпечити першого (15), другого (16), третього (17) та четверможливість самосинхронізації каналу цифрової того (18) блоків пам'яті, виходи яких під'єднані до магнітної реєстрації 3 точки зору самосинхронізапершого-десятого інформаційних входів третього ції всі методи канального кодування можуть бути регістра (19) Виходи 9 та 10 другого регістра (11) охарактеризовані параметрами d та к, причому під'єднані до входів дешифратора (6), виходи якопараметр d визначає мінімальну КІЛЬКІСТЬ нулів між го з'єднані з входами установки режиму роботи Е двом одиницями (при реакції на одиницю), параВІДПОВІДНО, першого (15), другого (16), третього метр k визначає максимальну КІЛЬКІСТЬ нулів між (17) та четвертого (18) блоків пам'яті двома одиницями Ступінь самосинхронізації буде тим більший, чим менше відношення максимальВ запропонованому пристрої кодування двійної та мінімальної довжин переходів намагніченоскового десяти розрядного коду в одинадцяти розті носія інформації, що визначаються як рядний код Каутса-Фібоначі інформаційне десяти розрядне слово розвертається за допомогою першого регістра (5) з послідовної двійкової форми в паралельну В подальшому за допомогою елементів 15, 16, 17, 18, це слово перетворюється в одиде Т - довжина тактового інтервалу, що відпонадцяти розрядне кодове слово Каутса-Фібоначі відає одному біту, записаному за методом БПНМ За допомогою третього регістра (19) паралельне (без повернення до нуля модифікований) Ступінь кодове одинадцяти розрядне слово Каутсасамосинхронізації оцінюється коефіцієнтом самоФібоначі також переводиться в послідовну форму і синхронізації, що визначається як подається на блок запису (21) для подальшої реK s =T m a x /T m i n =Vk (k + 1) T/Vk (d+1) T = (k + 1)/(d + 1) єстрації на магнітний носій (стрічка, диск) На практиці значення коефіцієнту самосинхронізаПристрій працює таким чином Вхідний двійкоції вибирають в межах вий код розділяють на рівномірні часові ПОСЛІДОВKs=2 4 НОСТІ по десять бітових інтервалів, перетворюють Для визначення параметру густини переходу за допомогою канальних кодів Каутса-Фібоначі в намагніченості носія інформації, що характеризує одинадцяти символьні ПОСЛІДОВНОСТІ І В подальможливу ЩІЛЬНІСТЬ та швидкість реєстрація інфоршому в струм запису Сигнал тактової частоти мації використовують параметр, який називають (фіг 2а), сформований генератором 1 ділиться на коефіцієнтом можливої густини Цей коефіцієнт 10 за допомогою лічильника 2 (фіг 26) та на одивизначається як надцять за допомогою лічильника 3 (фіг 2в) Інфог^-гп— І mm' I рмаційні сигнали в двійковому коді з виходу пері має тим більше значення, чим дальше рознешого регістра 5 записуються в другий регістр 11 в сені по магнітному носію переходи намагніченості момент позитивного перепаду сигналу, який надРознесення переходів дозволяє зменшувати верхходить з виходу схеми 2І-НІ (10) (фіг 2г) ВИХІДНІ ню частоту в спектрі канального коду та звужувати імпульси формувача 12 (фіг 2д) надходять на вхід АЧХ каналу або ж в існуючому каналі реєструвати встановлення в одиницю тригера 13, вихідний сигінформацію з більшою швидкістю нал (фіг2е) якого подається на вхід установки реНа практиці проведення операцій заміщення п жиму роботи Е третього регістра 19 і встановлює - символів двійкової інформації m - символами 8 60624 канального коду призводить до появи надлишковості і, при d=0 параметр Ттщ=0 В той же час, можливе значення коефіцієнта збільшення швидкості реєстрації тісно, але обернено пропорційно пов'язане з таким параметром, як вікно детектування Вікно детектування визначає можливість правильного розпізнавання імпульсів сигналів на виході каналу магнітної реєстрації і залежить від кодової швидкості та довжини тактового інтервалу жимо Tg = V k -T ет = К т •Т д /Т = К е т " Порівняльний аналіз відомих та запропонованих канальних кодів по параметрах синхронізації Ks, вікна детектування Td, надлишковості Н та коефіцієнтів густини переходів Km та Кегп дозволяє побудувати табл 2 3 табл 2 можна зробити висновок, що при однаковому коефіцієнті самосинхронізації КФ коди з параметрами n=10, m = 1 1 , d=0, k=3 дозволяють забезпечити найбільш високе значення коефіцієнту ефективної густини переходів Кегп Причому Кегп у кодів КФ зростає ВІДПОВІДНО збільшенню КІЛЬКОСТІ розрядів коду Використання винаходу дозволяє збільшити ЩІЛЬНІСТЬ запису інформації на магнітний носій при умові самосинхронізації \ Виконавши деякі спрощення шляхом підстановки T g / T = V k , T m i n = V k - ( d + 1)-T, V k = n / m або K e m = V ^ - ( d + 1) Використовуючи запропонований коефіцієнт Kem, вибір канального коду проводять виходячи з максимального його значення при K s =2 4 Задачу побудови оптимального канального коду можна вирішити шляхом використання рекурентних рядів Каутса-Фібоначі, для яких вага члена ряду в любій позиції дорівнює деякій сумі попередніх членів ряду Таке відображення членів ряду дозволяє, при проведені операції кодування, одержувати обмежені серії нулів та одиниць, що забезпечує самосинхронізацію Найбільш поширені числові ряди Каутса-Фібоначі і позначення ВІДПОВІДНИХ їм канальних кодів наведені в таблиці 1 Зменшення вікна детектування призводить до значного ускладнення схем відтворення (детектування) на виході каналу магнітної реєстрації Враховуючи практично взаємо-зворотну дію коефіцієнта густини переходів намагніченості та вікна детектування слід при виборі оптимального методу канального кодування застосувати деякий комплексний показник Цей показник, назвемо його коефіцієнтом ефективної густини переходів намагніченості, визначається як К K e m = n -(d + IJ/m одер Таблиця 1 Умовне зображення канального коду КФ (d,k) КФ (0,1) КФ (0,2) КФ (0,3) КФ (1,2) КФ (1,3) КФ (1,4) КФ (2,3) Породжуюча формула YFY 1+Y Числовий ряд 1 1 2 3 5 8 1321 3455 1 1 2 4 7 1 3 2 4 4 4 81 149 1 1 2 4 8 152956108208 111223457912 1 1 23469131928 1 1 1 2 3 5 7 1 1 172640 111122 23445789 2 YFYM+Y^+Y.S 1+Y 2+Y, 3+Y 4 2+Y з Y F Y 2+Y 3+Y 4 Y F Y 2+Y 3+Y 4+Y 5 Y F Y 3+Y 4 YFY YFY Таблиця 2 Група кодів K s =4 K s =4 K s =4 K s =4 K s =4 K s =4 КОД ГК5/6 НДМ-3 3PM КФ (0,3,8,9) КФ (0,3,9,10) КФ (0,3,10,11) Km 0,833 2 1,5 0,889 0,9 0,91 Tfl=VK*T 0,833 0,33 0,5 0,889 0,9 0,91 Kern 0,694 0,66 0,75 0,79 0,81 0,83 H, % 20 200 100 12,5 11,1 10 60624 10 П П Фіг 2 Комп'ютерна верстка Л Ціхановська Підписне Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ДП "Український інститут промислової власності", вул Сім'ї Хохлових, 15, м Київ, 04119

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for channel-by-channel coding of data

Автори англійськоюMartseniuk Valerii Panteleimonovych

Назва патенту російськоюУстройство для поканального кодирования данных

Автори російськоюМарценюк Валерий Пантелеймонович

МПК / Мітки

МПК: G11B 5/09

Мітки: кодування, пристрій, канального

Код посилання

<a href="https://ua.patents.su/5-60624-pristrijj-kanalnogo-koduvannya.html" target="_blank" rel="follow" title="База патентів України">Пристрій канального кодування</a>

Попередній патент: Спосіб визначення структурних елементів та змін на дні ока

Наступний патент: Перетворювач напруги в код

Випадковий патент: Розбірний повітряний змій