Вузол квантування за часом

Формула / Реферат

1. Вузол квантування за часом, який містить блок початкової установки, вхідний подільник-формувач, виконаний у вигляді тригера, блок синхронізації, розподільник імпульсів, виконаний у вигляді лічильника-подільника, дешифратор, формувач початкової ділянки квазісинусоїдального сигналу, вихідний безконтактний перемикач напівперіодів квазісинусоїдального сигналу, який відрізняється тим, що блок початкової установки виконаний у вигляді логічного інвертора, на вході якого встановлене RC-коло, блок синхронізації виконаний у вигляді двох логічних інверторів, вихід одного через RC-коло підключений до першого входу логічного елемента І, на другий вхід якого подають напругу мережі, розподільник імпульсів виконаний у вигляді лічильника-дешифратора на дев'ять виходів, дешифратор виконаний шістнадцятиканальним, формувач початкової ділянки квазісинусоїдального сигналу виконаний у вигляді логічних елементів, на входи яких подають чотири частотних сигнали, синфазних з частотою напруги мережі, вихідний безконтактний перемикач напівперіодів квазісинусоїдального сигналу реалізований на 16-ти двовходових елементах виключне І.

2. Вузол квантування за часом за п. 1, який відрізняється тим, що частотні сигнали мають три фіксовані частоти - 50 Гц, 800 Гц і 1600 Гц, синфазні з частотою напруги мережі.

Текст

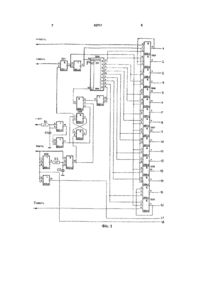

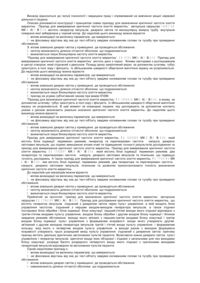

1 Вузол квантування за часом, який містить блок початкової установки, вхідний подільникформувач, виконаний у вигляді тригера, блок синхронізації, розподільник імпульсів, виконаний у вигляді лічильника-подільника, дешифратор, формувач початкової ділянки квазісинусоїдального сигналу, вихідний безконтактний перемикач напівперюдів квазісинусоїдального сигналу, який відрізняється тим, що блок початкової установки виконаний у вигляді логічного інвертора, на вході якого встановлене RC-коло, блок синхронізації виконаний у вигляді двох логічних інверторів, вихід одного через RC-коло підключений до першого входу логічного елемента І, на другий вхід якого подають напругу мережі, розподільник імпульсів виконаний у вигляді лічильника-дешифратора на дев'ять виходів, дешифратор виконаний шістнадцятиканальним, формувач початкової ділянки квазісинусоїдального сигналу виконаний у вигляді логічних елементів, на входи яких подають чотири частотних сигнали, синфазних з частотою напруги мережі, вихідний безконтактний перемикач напівперюдів квазісинусоїдального сигналу реалізований на 16-ти двовходових елементах виключне І 2 Вузол квантування за часом за п 1, який відрізняється тим, що частотні сигнали мають три фіксовані частоти - 50Гц, 800Гц і 1600Гц, синфазні з частотою напруги мережі Винахід відноситься до електротехніки і може бути використаний в джерелах харчування, що перетворюють постійну напругу від нетрадиційних джерел харчування в перемінну синусоїдальну чи квазісинусоїдальну напругу промислової частоти Відомий «Перетворювач постійної напруги в багатоступінчасту квазисинусоїдальну» (А с СРСР №1415380, МПК-4 Н02М7/5395, БВ-29-88р) Новим у перетворювачі є введення блоку формування програмних сигналів, що мають вихід коду програмної синусоїди, вихід тактових імпульсів, вихід нульового сигналу, вихід керування полярністю, аналого-цифровий перетворювач, блок порівняння кодів, що має два кодових входи, вихід пріоритету числа на першому вході, вихід пріоритету числа на другому вході, дві схеми збігу, М блоків керування осередками Недоліком відомого пристрою є складна схемотехніка вихідного каскаду разом із пристроєм М блоків керування осередками Відомий «Інвертор зі східчастою, близької до синусоїди, формою кривої вихідної напруги» (А с СРСР №565365, МПК-2 Н02М7/537, БИ-26-77р), що містить основний преобразуючий осередок із прямокутною вихідною напругою і кілька додаткових преобразуючих осередків, що формують схід часту напругу для добудування синусоїди через підсумовуюче пристрій, з'єднана послідовно з виходом основного осередку, при цьому основний осередок виконаний на тиристорах, а додаткові на транзисторах, причому сумарна вихідна напруга додаткових осередків на початку і наприкінці кожного напівперюду вихідної напруги інвертора обрана більш напруги харчування інвертора, крім того, основна осередок виконаний за напівмостовою схемою, а вихід и шунтований двома з'єднаними паралельно тиристорами Недоліком відомого пристрою є високий рівень напруги вищих гармонік, генеруемих інвертором Найбільш близьким по технічній сутності і результату, який досягається, і обраним як прототип є «Інвертор квазісинусоїдальної напруги» (Висновок про видачу деклараційного патенту України від 26 березня 2003р за заявкою №2002108344, пріоритет від 22 жовтня 2002р), якій містить вихідний трансформатор, блок керування, двотактні ВИХІДНІ інвертори, ланцюги керування якими з'єднані з ВІДПОВІДНИМИ виходами блоку керування, блок керування містить генератор, що задає, імпульсного стабілізатора напруги, пристрій керування вихідним каскадом імпульсного стабілізатора напруги, широтно-імпульсний модулятор імпульсного стабі (О 62711 лізатора напруги, формувач модульованих імпульсів керування імпульсного стабілізатора напруги, пристрій токового захисту імпульсного стабілізатора напруги, а двотактні ВИХІДНІ інвертори виконані у вигляді перетворювача з вихідним трансформатором і з пристроєм керування перетворювачем, крім того, уведені попередній підсилювач потужності імпульсного стабілізатора напруги, перший випрямляч напруги харчування перетворювача, підсилювач потужності імпульсного стабілізатора напруги, другий випрямляч напруги харчування перетворювача, пристрій контролю напруги і параметричний стабілізатор напруги, причому пристрій містить шість двотактні вихідних інверторів, виходи яких підключені до одного вихідного трансформатора При цьому пристрій керування перетворювачем по прототипі складається з наступних елементів - блоку початкової установки, виконаного у вигляді паралельно з'єднаних резистора і конденсатора, - вхідного подільник-формувача, виконаного у вигляді тригера, - блоку синхронізації, виконаного у вигляді тригера, - розподільника імпульсів, виконаного у вигляді лічильника-дільника з десятьма вихідними каналами, - восьмиканального дешифратора, виконаного у вигляді дюдно-резистивної схеми, - формувача початкової ділянки квазісинусоїдального сигналу, виконаного у вигляді логічних мікросхем, - вихідного безконтактного перемикача напівперюдів квазисинусоїдального сигналу, виконаного у вигляді 12-ти двохвходових логічних елементів "И" Недоліком прототипу є недосконала схемотехніка пристрою керування перетворювачем інвертора квазісинусоїдальної напруги, що не дозволяє одержати якісний квазісинусоїдальний сигнал на виході інвертора Задачею дійсного винаходу є розробка нової схемотехніки вузла квантування з часу інвертора квазісинусоїдальної напруги з досягненням технічного результату - поліпшення якості напруги на виході інвертора Поставлена задача досягається тим, що в «Вузлі квантування з часу», якій включає блок початкової установки, вхідний подільник-формувач, виконаний у вигляді тригера, блок синхронізації, розподільник імпульсів, виконаний у вигляді лічильника-дільника, дешифратор, формувач початкової ділянки квазісинусоїдального сигналу, вихідний безконтактний перемикач напівперюдів квазисинусоїдального сигналу, блок початкової установки виконаний у вигляді логічного інвертора, на вході якого встановлений RC-ланцюжок, блок синхронізації виконаний у вигляді двох логічних інверторів, вихід одного через RC-ланцюжок підключений у першому входу логічного елемента «І», на другий вхід якого подається напруга мережі, розподільник імпульсів виконаний у вигляді лічильникадешифратора на дев'ять виходів, дешифратор виконаний шестнадцатиканальним, формирувач початкової ділянки квазисинусоїдального сигналу виконаний у вигляді логічних елементів, на входи яких подаються чотири частотних сигнали, синфазних з частотою сіткової напруги, вихідний безконтактний перемикач напівперюдів квазисинусоїдального сигналу реалізований на 16-ти 2-х входових елементах «виключне «І» Крім того, частотні сигнали мають три фіксовані частоти 50Гц, 800Гц і 1600Гц, синфазні з частотою напруги мережі Новим у пристрої, що заявляється, є нова схемотехніка побудови вузла квантування з часу інвертора квазисинусоїдальної напруги, що дозволяє одержати якісну квазісинусоїдальну напругу на виході інвертора, керованого вузлом квантування з часу, якій заявляється Тому очевидно, що реалізація пристрою, що заявляється, дозволить виконати задачу, поставлену в дійсному винаході, з досягненням технічного результату - поліпшення якості напруги на виході інвертора Суттєвими ознаками пристрою, що заявляється, співпадаючими з прототипом, є наступні ознаки - блок початкової установки, - вхідний подільник-формувач, виконаний у вигляді тригера, - блок синхронізації, - розподільник імпульсів, виконаний у вигляді лічильника-дільника, - дешифратор, - формувач початкової ділянки квазісинусоїдального сигналу, - вихідний безконтактний перемикач напівперіодів квазисинусоїдального сигналу ВІДМІТНИМИ ВІД прототипу суттєвими ознаками пристрою, що заявляється, є наступні ознаки - блок початкової установки виконаний у вигляді логічного інвертора, на вході якого встановлений RC-ланцюжок, - блок синхронізації виконаний у вигляді двох логічних інверторів, вихід одного через RCланцюжок підключений у першому входу логічного елемента «І», на другий вхід якого подається напруга мережі, - розподільник імпульсів виконаний у вигляді лічильника-дешифратора на дев'ять виходів, - дешифратор виконаний шістнадцятиканальним, - формирувач початкової ділянки квазісинусоїдального сигналу виконаний у вигляді логічних елементів, на входи яких подаються чотири частотних сигнали, синфазних з частотою напруги мережи, - вихідний безконтактний перемикач напівперіодів квазисинусоїдального сигналу реалізований на 16-ти 2-х входових елементах «виключне «І» Приватною ВІДМІТНОЮ від прототипу суттєвою ознакою пристрою, що заявляється, є наступна ознака частотні сигнали мають три фіксовані частоти - 50Гц, 800Гц і 1600Гц, синфазні з частотою напруги мережи Винахід ілюстрований наступними кресленнями 62711 На фіг 1 і фіг 2 зображена принципова електрична схема пристрою, що заявляється Для того, щоб одержати квазісинусоїдальну напругу, що вірогідно відображає синусоїдальну форму сигналу, необхідно виконати квантування за рівнем і з часу, тобто необхідно одержати квантування по 32-м рівнях напруги і з часу Для одержання цих рівнів квантування на схему вузла квантування необхідно подати три напруги різних частот, синхронні з частотою напруги мережі, а саме f=50fL| - для синхронізації по фазі вихідного сигналу перетворювача, f=800fL| і 1600Гц - щоб одержати початкову V4 і кінцеву % частина синусоїди інтервалу для квантування з часу Синхронний помножувач частоти (умовно не показаний) формує напруги цих трьох частот, синхронні з частотою напруги мережі Сигнали із синхронного помножувача частоти з частотами f=50fL|, f =800Гц, f=1600Гц надходять на входи мікросхем DD2-1, DD2-3, DD3-3, DD1-1, D D 5 - 1 , D D 9 - 2 В І Д П О В І Д Н О Напруга 15 В зі стабілізатора напруги (умовно не показаний) надходить на блок початкової установки, виконаний у вигляді логічного інвертора DD1-3, на вході якого встановлений RC-ланцюжок, виконана на резисторі R1 і конденсаторі С1 3 виходу DD1-3 сигнал надходить на інвертор DD1-4 Інвертори DD1-3 і DD1-4 служать для початкової установки при подачі харчування на пристрій Вхідний подільник-формувач виконаний у вигляді тригера на мікросхемах DD3-1 і DD3-2, що виконують роль комутатора Блок синхронізації виконаний у вигляді двох логічних інверторів на мікросхемах DD2-1 і DD2-3, причому вихід DD2-1 через RC-ланцюжок на резисторі R2 і конденсаторі С2 підключений до першого входу логічного елемента «И» на мікросхемі DD2-3, на другий вхід якого подається напруга мережі частотою 50Гц Мікросхеми DD2 і DD3 призначені для синхронізації з напругою мережі напруги перетворювача (умовно не показаний), до складу якого входить вузол квантування з часу, якій заявляється Розподільник імпульсів виконаний у вигляді лічильника-дешифратора на дев'ять виходів і реалізований на мікросхемі DD4 Дешифратор виконаний шістнадцятиканальним і реалізований на мікросхемах DD5-DD9, DD10-DD13 Формувач початкової ділянки квазісинусоїдального сигналу виконаний у вигляді логічних еле ментів DD5-1, DD5-2 і DD9-1, DD9-2, на входи яких подають чотири частотних сигнали, синфазних з частотою сіткової напруги - f=800rq і 1600Гц (прямої й інверсний сигнали), а також сигнали з виходів «0» і «7» лічильника-дешифратора DD4 Виходи DD10-DD13 приєднані до входів DD14DD17 - комутатору напівперюдів квазісинусоїдального сигналу з частотою мережі Виходи DD14-DD17 з 1-го по 16-тий подаються на бази транзисторів VT1 блоків 1-8 (умовно не показані), що входять до складу вихідних підсилювачів інвертора, що дозволяє одержати потужність вихідного квазісинусоїдального сигналу до 1 квт Пристрій працює в такий спосіб При подачі напруги харчування на пристрій відбувається початкова установка вхідного подільник-формувача на мікросхемі DD3-1 і DD3-2, що встановлює в нуль лічильник-дешифратор на мікросхемі DD4 Від синхронного помножувача частоти імпульси з частотами ^50Гц, ^800Гц, f=1600Гц надходять на входи пристрою, що заявляється, на виході якого формуються 32 імпульсу напруги, послідовно розподілених у часі Ці імпульси напруги, по черзі надходять на входи блоків 1-8 вихідних підсилювачів інвертора, які по черзі формують чергову сходинку квазісинусоїдальної напруги Крім того, важливою обставиною, що поліпшує якість напруги на виході інвертора, є те, що початкові ділянки квазісинусоїдального сигналу формуються на підвищеній частоті, тобто число сходинок на початку і наприкінці напівхвилі квазісинусоїдального сигналу значно більше, ніж у середині наПІВХВИЛІ Це дозволяє більш точно відтворити на виході інвертора синусоїдальну напругу А тому що всі частотні імпульси, подавані на пристрій, синхронізовані з частотою живильної мережі, то вихідна квазісинусоїдальна напруга також синфазна частоті живильної мережі, тобто частота і фаза вихідної квазісинусоїдальної напруги точно відповідають частоті і фазі живильної напруги мережі Таким чином, з огляду на усе вищевикладене, можна зробити висновок, що реалізація пристрою, який заявляється, дозволить виконати задачу, поставлену в дійсному винаході - розробку нової схемотехніки вузла квантування з часу інвертора квазісинусоїдальної напруги з досягненням технічного результату - поліпшення якості напруги на виході інвертора 62711 (=1600 Гц ФІГ. 1 62711 10 ДО транзисторів VT1 блоків 1-8 Фіг. 2 Комп'ютерна верстка Н Лисенко Підписне Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ДП "Український інститут промислової власності", вул Сім'ї Хохлових, 15, м Київ, 04119

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for time quantization of signals

Автори англійськоюBekirov Eskender Alimovych

Назва патенту російськоюУстройство для дискретизации сигналов по времени

Автори російськоюБекиров Эскендер Алимович

МПК / Мітки

МПК: G05F 1/56, H02M 3/335, H02M 7/00

Мітки: часом, квантування, вузол

Код посилання

<a href="https://ua.patents.su/5-62711-vuzol-kvantuvannya-za-chasom.html" target="_blank" rel="follow" title="База патентів України">Вузол квантування за часом</a>

Попередній патент: Спосіб діагностики акаріформних кліщів

Наступний патент: Спосіб розробки рудних родовищ

Випадковий патент: Склад для обробки деревини для надання їй вогнестійкості