Спосіб часового доступу до даних в пам’яті та пристрій для його реалізації

Формула / Реферат

1. Спосіб часового доступу до даних в пам'яті, до якої записуються та з якої зчитуються дані, який відрізняється тим, що разом із кожним даним при його запису в пам'ять подають часову мітку, яка позначає числове значення поточного номера такту, на якому це дане має бути зчитане із пам'яті, де під номером такту розуміють числове значення моменту часу на часовій осі або числове значення номера імпульсу тактового сигналу, або числове значення номера кроку чи етапу виконання дії, причому числові значення поточних номерів тактів, визначають відносно числових значень початкових номерів тактів, на яких починається видача даних з пам'яті, за числове значення початкового номера такту приймають довільне фіксоване числове значення номера такту, числове значення поточного номера такту формують шляхом підрахунку тактів, починаючи від числового значення початкового номера такту, тобто визначають як суму/різницю числового значення початкового номера такту та кількості підрахованих тактів, пам'ять будують таким чином, щоб забезпечити приймання та зберігання вхідних даних, а також надходження на її вихід даних, часові мітки яких співпадають з числовими значеннями поточних номерів тактів, дані записують в пам'ять та зчитують з пам'яті на довільних номерах тактів.

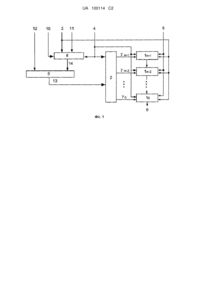

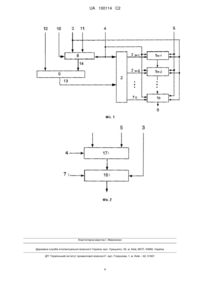

2. Пристрій пам'яті з часовим доступом містить m комірок пам'яті 1і, де і=0, 1, ... m-2, m-1, дешифратор 2, вхід 3 задання тактових імпульсів, вхід 4 запису-зчитування, вхід даних 5, вихід даних 6, виходи 7і, де і=0, 1, ... m-2, m-1, дешифратора 2, причому вхід 3 задання тактових імпульсів з'єднаний з входами синхронізації комірок пам'яті 1і, вхід 4 запису-зчитування з'єднаний з відповідними входами комірок пам'яті 1і, виходи 7і дешифратора 2 з'єднані з відповідними входами комірок пам'яті 1і, вхід даних 5 з'єднаний з входами комірок пам'яті 1і, вихід даних 6 з'єднаний з виходом комірки пам'яті 10, де кожна комірка пам'яті 1і (і=1, 2, ..., m-1) якого містить запам'ятовуючий елемент 16і, вхід дозволу запису якого з'єднаний з виходом 7і дешифратора 2, а вхід синхронізації якого з'єднаний з входом 3 задання тактових імпульсів, вихід запам'ятовуючого елемента 16і з'єднаний з виходом комірки пам'яті 1і, який відрізняється тим, що додатково містить лічильник 8, віднімач 9, вхід 10 подачі сигналу початкового встановлення, вхід 11 подачі коду початкового номера такту та вхід 12 подачі часової мітки, вихід 13 коду інтервалу очікування віднімача 9, вихід 14 коду поточного номера такту лічильника 8, причому вхід 3 задання тактових імпульсів з'єднаний з відповідним входом лічильника 8, вхід 4 запису-зчитування з'єднаний з відповідними входами лічильника 8 та керуючим входом дешифратора 2, вхід 10 подачі сигналу початкового встановлення та вхід 11 подачі коду початкового номера такту з'єднані з відповідними входами лічильника 8, вхід 12 подачі часової мітки з'єднаний з першим входом віднімача 9, другий вхід якого з'єднаний з виходом 14 лічильника 8, вихід 13 віднімача 9 з'єднаний з інформаційним входом дешифратора 2, входи комірок пам'яті 1і (і=0, 1, ..., m-2) з'єднані з виходами комірок пам'яті 1і-1 (і=1, 2, ..., m-1).

3. Пристрій за п. 2, який відрізняється тим, що кожна комірка пам'яті 1і (і=1, 2, ..., m-1) додатково містить мультиплексор 17і, причому перший вхід мультиплексора 17і (і=0, 1, ..., m-2) з'єднаний з виходом комірки пам'яті 1і+1 (і=0, 1, ..., m-2), другий вхід мультиплексора 17і (і=0, 1, ..., m-1) з'єднаний з входом даних 5, вхід керування мультиплексора 17і з'єднаний з входом 4 запису-зчитування, вихід мультиплексора 17і з'єднаний з входом запам'ятовуючого елемента 16і, вхід дозволу запису якого з'єднаний з виходом 7і дешифратора 2.

Текст

Реферат: Спосіб часового доступу до даних в пам'яті та пристрій для його реалізації належить до обчислювальної техніки і може бути використаний при побудові пристроїв пам'яті. В способі разом із кожним даним при його запису в пам'ять подають часову мітку, яка позначає числове значення поточного номера такту, на якому це дане має бути зчитане із пам'яті. Числові значення поточних номерів тактів, визначають відносно числових значень початкових номерів тактів, на яких починається видача даних з пам'яті. Числове значення поточного номера такту формують шляхом підрахунку тактів, починаючи від числового значення початкового номера такту, тобто визначають як суму/різницю числового значення початкового номера такту та кількості підрахованих тактів. Пам'ять будують таким чином, щоб забезпечити приймання та зберігання вхідних даних, а також надходження на її вихід даних, часові мітки яких співпадають з числовими значеннями поточних номерів тактів. Пристрій пам'яті з часовим доступом складається із m комірок пам'яті, дешифратора, лічильника, віднімача, входу задання тактових імпульсів, входу запису-зчитування, входу подачі сигналу початкового встановлення, входу подачі коду початкового номера такту, та входу подачі часової мітки, а також входу даних та виходу даних, причому кожна комірка пам'яті пристрою пам'яті з часовим доступом містить мультиплексор та запам'ятовуючий елемент. Технічним результатом є усунення прив'язки даного до конкретної комірки пам'яті через виключення необхідності використання адрес запису та зчитування даних. UA 100114 C2 (12) UA 100114 C2 UA 100114 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до області обчислювальної техніки і може бути використаний при побудові пристроїв пам'яті. Відомий спосіб послідовного доступу до даних в пам'яті, коли записувані в комірки пам'яті дані утворюють деяку чергу [1, стор. 181, 189-190]. Зчитування здійснюється з черги слово за словом в порядку запису або в зворотному порядку. Прямий порядок зчитування забезпечується пам'яттю FIFO з дисципліною обслуговування "перший прийшов - перший вийшов" (First In-First Out), а також в файлових і циклічних запам'ятовуючих пристроях. Обернений порядок зчитування забезпечується пам'яттю LIFO з дисципліною обслуговування "останній прийшов - перший вийшов" (Last In-First Out). Недоліком способу послідовного доступу до даних в пам'яті є значний час пошуку в пам'яті конкретної одиниці інформації. В гіршому випадку для цього може вимагатися перегляд всього об'єму даних, які записані в пам'ять. Відомий також спосіб асоціативного доступу до даних в пам'яті, відповідно до якого дані записуються в довільні вільні (звільнені) комірки і з пам'яті дане вибирається за значенням спеціальної ознаки, яка записується в комірку разом з цим даним [1, стор 182]. Як ознака може бути і значення самого даного. Недоліками способу асоціативного доступу до даних в пам'яті є необхідність двократного звернення до однієї комірки - при запису і при зчитуванні даного, а також необхідність забезпечення доступу до кожної комірки з входу та виходу пам'яті, або з об'єднаного входу/виходу пам'яті, причому при зчитуванні необхідно проводити порівняння шуканої і записаної ознак, що вимагає великих затрат на елементи доступу та сповільнює роботу пам'яті. Відомий спосіб адресного доступу до даних в пам'яті, відповідно до якого разом із кожними даними при їх записі в пам'ять та при їх зчитуванні з пам'яті подають адресу комірки пам'яті (її номер), яка ідентифікує цю комірку, з тим, щоб здійснити запис даного до цієї комірки, або його зчитування з цієї комірки [2, стор 309, 310, 331-334]. Спосіб адресного доступу до даних в пам'яті найширше використовується в сучасних комп'ютерах. Недоліки відомого способу доступу до даних - необхідність пам'ятати адреси комірок пам'яті, в яких зберігаються дані, для того, щоб при потребі ці дані можна було знайти та зчитати, та необхідність подачі адреси на адресний вхід пам'яті як при записі даного, так і при його зчитуванні. В основу винаходу поставлено задачу удосконалити спосіб доступу до даних в пам'яті шляхом усунення прив'язки даного до конкретної комірки пам'яті та виключення необхідності використання адрес запису та зчитування даних. Поставлена задача вирішується тим, що в способі часового доступу до даних в пам'яті, до якої записуються та з якої зчитуються дані, відповідно до винаходу, разом із кожними даними при їх записі в пам'ять подають часову мітку, яка позначає числове значення поточного номера такту, на якому ці дані мають бути зчитані із пам'яті, де під номером такту розуміють числове значення моменту часу на часовій осі, або числове значення номера імпульсу деякого тактового сигналу, або числове значення номера кроку чи етапу виконання деякої дії, причому числові значення поточних номерів тактів, визначають відносно числових значень початкових номерів тактів, на яких починається видача даних з пам'яті, за числове значення початкового номера такту приймають довільне фіксоване числове значення номера такту, числове значення поточного номера такту формують шляхом підрахунку тактів, починаючи від числового значення початкового номера такту, тобто визначають як суму (різницю) числового значення початкового номера такту та кількості підрахованих тактів, пам'ять будують таким чином, щоб забезпечити приймання та зберігання вхідних даних, а також надходження на її вихід даних, часові мітки яких співпадають з числовими значеннями поточних номерів тактів, дані записують в пам'ять та зчитують з пам'яті на довільних номерах тактів. Техніко-економічна ефективність запропонованого способу часового доступу до даних в пам'яті визначається тим, що, на відміну від прототипу, його реалізація дозволяє усунути прив'язку даного до конкретної комірки пам'яті через виключення необхідності використання адрес запису та зчитування даних, що виключає потребу зберігати адреси комірок, до яких записані дані, та потребу подачі адреси на адресний вхід пам'яті як при запису даного, так і при його зчитуванні, оскільки, відповідно до запропонованого способу, вимагається подача разом із кожними даними при їх записі в пам'ять лише часової мітки, яка позначає числове значення поточного номера такту, на якому ці дані мають бути зчитані із пам'яті, та побудова пам'яті таким чином, щоб забезпечити надходження на її вихід даних, часові мітки яких співпадають з числовими значеннями поточних номерів тактів. Розглянемо структуру пристрою пам'яті з часовим доступом, в якому реалізовано запропонований спосіб часового доступу до даних в пам'яті. 1 UA 100114 C2 5 10 15 20 25 30 35 40 45 50 55 Пристрій пам'яті з часовим доступом (фіг. 1), містить m комірок пам'яті 1і, де і = 0, 1, …, m-2, m-1, дешифратор 2, вхід 3 задання тактових імпульсів, вхід 4 запису-зчитування, вхід даних 5, вихід даних 6, виходи 7і, де і=0, 1, …, m-2, m-1, дешифратора 2, причому вхід 3 задання тактових імпульсів з'єднаний з входами синхронізації комірок пам'яті 1 і, вхід 4 запису-зчитування з'єднаний з відповідними входами комірок пам'яті її, виходи 7і дешифратора 2 з'єднані з відповідними входами комірок пам'яті 1і, вхід даних 5 з'єднаний з входами комірок пам'яті 1і, вихід даних 6 з'єднаний з виходом комірки пам'яті 10, та, відповідно до винаходу, додатково містить лічильник 8, віднімач 9, вхід 10 подачі сигналу початкового встановлення, вхід 11 подачі коду початкового номера такту та вхід 12 подачі часової мітки, вихід 13 коду інтервалу очікування віднімача 9, вихід 14 коду поточного номера такту лічильника 8, причому вхід 3 задання тактових імпульсів з'єднаний з відповідним входом лічильника 8, вхід 4 записузчитування з'єднаний з відповідними входами лічильника 8 та керуючим входом дешифратора 2, вхід 10 подачі сигналу початкового встановлення та вхід 11 подачі коду початкового номера такту з'єднані з відповідними входами лічильника 8, вхід 12 подачі часової мітки з'єднаний з першим входом віднімача 9, другий вхід якого з'єднаний з виходом 14 лічильника 8, вихід 13 віднімача 9 з'єднаний з інформаційним входом дешифратора 2, входи комірок пам'яті 1 2 (i=0, 1,…, m-2) з'єднані з виходами комірок пам'яті 1i (і=1, 2,…, m-1). Кожна комірка пам'яті 1i (і=1, 2,…, m-1) (фіг. 2) пристрою пам'яті з часовим доступом містить запам'ятовуючий елемент 16i, вхід дозволу запису якого з'єднаний з виходом 7i дешифратора 2, а вхід синхронізації якого з'єднаний з входом 3 задання тактових імпульсів, вихід запам'ятовуючого елемента 16і з'єднаний з виходом комірки пам'яті 1і, та, відповідно до винаходу, додатково містить мультиплексор 17і, причому перший вхід мультиплексора 17і (і=0, 1,…, m-2) з'єднаний з виходом комірки пам'яті 1і+1 (і=0, 1,…, m-2), другий вхід мультиплексора 17і (і=0, 1,…, m-1) з'єднаний з входом даних 5 пристрою пам'яті з часовим доступом, вхід керування мультиплексора 17i з'єднаний з входом 4 запису-зчитування пристрою пам'яті з часовим доступом, вихід мультиплексора 17і з'єднаний з входом запам'ятовуючого елемента 16i, вхід дозволу запису якого з'єднаний з виходом 7i дешифратора 2. Пристрій пам'яті з часовим доступом працює наступним чином. Перед початком роботи пристрою пам'яті з часовим доступом значення початкового номера такту, на якому починається видача даних з пам'яті, записують до лічильника 8 з входу 11 сигналом початкового встановлення, який надходить по входу 10. Значення поточного номера такту, рівне сумі (або різниці) значення початкового номера такту та кількості тактів зчитування даних з пам'яті, формується в лічильнику 8, вміст якого з кожним тактом зчитування збільшується (або зменшується) на 1, тобто він підраховує кількість тактів зчитування даних, починаючи від значення початкового номера такту. При цьому такти запису лічильником 8 не фіксуються, для чого на його вхід дозволу рахунку надходить сигнал запису-зчитування з входу 4, і в режимі запису забороняє рахунок. Віднімач 9 формує код інтервалу очікування, тобто різницю між кодом часової мітки, яка супроводжує кожне дане, та кодом поточного номера такту (або між кодом поточного номера такту та кодом часової мітки). Код інтервалу очікування вказує, за який час від поточного номера такту з пам'яті повинне бути зчитане це дане. В режимі запису входи всіх запам'ятовуючих елементів 16i (і=0, 1,…, m-1) через мультиплексори 17i сигналом запису-зчитування на їх керуючих входах підключені до входу даних 5. Але запис здійснюється лише до запам'ятовуючого елемента, вхід дозволу запису 7i якого має значення 1. Тому з кожним тактовим імпульсом в режимі запису записується дане до комірки пам'яті 1i, номер і якої рівний коду інтервалу очікування, який вказує, за який час від поточного номера такту з пам'яті повинне бути зчитане це дане. В режимі зчитування входи запам'ятовуючих елементів 16і (і=0, 1,…, m-2) через мультиплексори 17i сигналом запису-зчитування на їх керуючих входах підключені до виходів попередніх запам'ятовуючих елементів 16і (і=1, 2,…, m-1). При цьому запис дозволено до всіх цих запам'ятовуючих елементів, оскільки на їх входи дозволу запису 7i надходить значення 1 з виходів дешифратора 2, які в це значення встановлюються сигналом запису-зчитування на вході дешифратора 2. Тому в цьому режимі з кожним тактовим імпульсом дані перепишуться із попередніх комірок пам'яті в наступні комірки, а з комірки пам'яті 10 зчитується дане на вихід пристрою пам'яті з часовим доступом, причому номер такту зчитування співпадає з значенням, яке вказується часовою міткою. Джерела інформації:: 1. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Санкт-Петербург, 2000.-528 с. 2. Мельник А.О. Архітектура комп'ютера. - Луцьк. Волинська обласна друкарня, 2008.-470 с. 60 2 UA 100114 C2 ФОРМУЛА ВИНАХОДУ 5 10 15 20 25 30 35 40 1. Спосіб часового доступу до даних в пам'яті, до якої записуються та з якої зчитуються дані, який відрізняється тим, що разом із кожними даними при їх записі в пам'ять подають часову мітку, яка позначає числове значення поточного номера такту, на якому ці дані мають бути зчитані із пам'яті, де під номером такту розуміють числове значення моменту часу на часовій осі або числове значення номера імпульсу тактового сигналу, або числове значення номера кроку чи етапу виконання дії, причому числові значення поточних номерів тактів визначають відносно числових значень початкових номерів тактів, на яких починається видача даних з пам'яті, за числове значення початкового номера такту приймають довільне фіксоване числове значення номера такту, числове значення поточного номера такту формують шляхом підрахунку тактів, починаючи від числового значення початкового номера такту, тобто визначають як суму/різницю числового значення початкового номера такту та кількості підрахованих тактів, пам'ять будують таким чином, щоб забезпечити приймання та зберігання вхідних даних, а також надходження на її вихід даних, часові мітки яких співпадають з числовими значеннями поточних номерів тактів, дані записують в пам'ять та зчитують з пам'яті на довільних номерах тактів. 2. Пристрій пам'яті з часовим доступом містить m комірок пам'яті 1і, де і=0, 1, ..., m-2, m-1, дешифратор 2, вхід 3 задання тактових імпульсів, вхід 4 запису-зчитування, вхід даних 5, вихід даних 6, виходи 7і, де і=0, 1, ..., m-2, m-1, дешифратора 2, причому вхід 3 задання тактових імпульсів з'єднаний з входами синхронізації комірок пам'яті 1і, вхід 4 запису-зчитування з'єднаний з відповідними входами комірок пам'яті 1і, виходи 7і дешифратора 2 з'єднані з відповідними входами комірок пам'яті 1і, вхід даних 5 з'єднаний з входами комірок пам'яті 1і, вихід даних 6 з'єднаний з виходом комірки пам'яті 10, де кожна комірка пам'яті 1і (і=1, 2, ..., m-1) якого містить запам'ятовуючий елемент 16і, вхід дозволу запису якого з'єднаний з виходом 7і дешифратора 2, а вхід синхронізації якого з'єднаний з входом 3 задання тактових імпульсів, вихід запам'ятовуючого елемента 16і з'єднаний з виходом комірки пам'яті 1і, який відрізняється тим, що додатково містить лічильник 8, віднімач 9, вхід 10 подачі сигналу початкового встановлення, вхід 11 подачі коду початкового номера такту та вхід 12 подачі часової мітки, вихід 13 коду інтервалу очікування віднімача 9, вихід 14 коду поточного номера такту лічильника 8, причому вхід 3 задання тактових імпульсів з'єднаний з відповідним входом лічильника 8, вхід 4 запису-зчитування з'єднаний з відповідними входами лічильника 8 та керуючим входом дешифратора 2, вхід 10 подачі сигналу початкового встановлення та вхід 11 подачі коду початкового номера такту з'єднані з відповідними входами лічильника 8, вхід 12 подачі часової мітки з'єднаний з першим входом віднімача 9, другий вхід якого з'єднаний з виходом 14 лічильника 8, вихід 13 віднімача 9 з'єднаний з інформаційним входом дешифратора 2, входи комірок пам'яті 1і (і=0, 1, ..., m-2) з'єднані з виходами комірок пам'яті 1і-1 (і=1, 2, ..., m-1). 3. Пристрій за п. 2, який відрізняється тим, що кожна комірка пам'яті 1і (і=1, 2, ..., m-1) додатково містить мультиплексор 17і, причому перший вхід мультиплексора 17і (і=0, 1, ..., m-2) з'єднаний з виходом комірки пам'яті 1і+1 (і=0, 1, ..., m-2), другий вхід мультиплексора 17і (і=0, 1, ..., m-1) з'єднаний з входом даних 5, вхід керування мультиплексора 17і з'єднаний з входом 4 запису-зчитування, вихід мультиплексора 17і з'єднаний з входом запам'ятовуючого елемента 16і, вхід дозволу запису якого з'єднаний з виходом 7і дешифратора 2. 3 UA 100114 C2 Комп’ютерна верстка І. Мироненко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod and device for memory data time access

Автори англійськоюMelnyk Anatolii Oleksiiovych

Назва патенту російськоюСпособ временного доступа к данным в памяти и устройство для его реализации

Автори російськоюМельник Анатолий Алексеевич

МПК / Мітки

МПК: G11C 8/00, G06F 12/02

Мітки: часового, пам'яті, спосіб, пристрій, доступу, реалізації, даних

Код посилання

<a href="https://ua.patents.su/6-100114-sposib-chasovogo-dostupu-do-danikh-v-pamyati-ta-pristrijj-dlya-jjogo-realizaci.html" target="_blank" rel="follow" title="База патентів України">Спосіб часового доступу до даних в пам’яті та пристрій для його реалізації</a>

Попередній патент: Молотильний механізм та комбайн з роторним молотильним механізмом

Наступний патент: Спосіб переробки пилоподібних сольових алюміній- або глиноземвмісних шлаків

Випадковий патент: Пристрій мобільного зв'язку