Спосіб перетворення часового зсуву між двома сигналами та пристрій для його реалізації

Номер патенту: 11443

Опубліковано: 25.12.1996

Автори: Сопрунюк Петро Маркіянович, Погребенник Володимир Дмитрович

Формула / Реферат

1. Способ преобразования временного сдвига между двумя сигналами, заключающийся в параллельном интегрировании входных сигналов в течение времени, большего длительности фронтов и ожидаемой длительности между сигналами, инвертировании проинтегрированных сигналов, масштабном преобразовании по амплитуде и их интегрировании, формировании начала и конца входного временного интервала при достижении интегрируемым сигналом нулевого уровня, отличающийся тем, что, с целью расширения функциональных возможностей, осуществляют параллельное преобразование мгновенных значений входных сигналов путем отслеживания их значений до достижения максимального значения и запоминание на заданное время, а также определяют последовательность поступления входных сигналов.

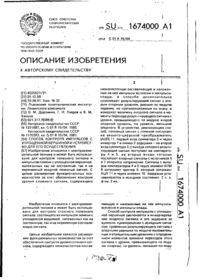

2. Устройство для преобразования временного сдвига между двумя сигналами, содержащее два идентичных канала преобразования, в состав каждого из которых входят масштабный инвертор, коммутатор, интегратор, электронный ключ и компаратор, причем вход масштабного инвертора соединен с первым входом коммутатора, второй вход которого подключен к выходу масштабного инвертора, а выход соединен с входом интегратора и первым входом электронного ключа, выходы которых подключены к первому входу компаратора, второй вход которого соединен с третьим входом электронного ключа и вторым входом канала преобразования, а выход подключен к первому выходу каналі преобразования, третий вход которого соединен с вторым входом электронного ключа, блок управления, элемент "Неравнозначность", входные шины "Вход I", "Вход 2", "Пуск" и выходную шину "Выход", которая подключена к выходу элемента "Неравнозначность", первый и второй входы которого соединены с первыми выходами соответственно первого и второго каналов преобразования, вторые входы которых подключены к первому выходу блока управления, второй выход которого соединен с третьими входами первого и второго каналов преобразования, первые входы которых подключены к шинам "Вход 1" и "Вход 2" соответственно, а вход блока управления соединен с шиной "Пуск", отличающееся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены блок для определения последовательности поступления входных сигналов и индикатор, а в каждый из каналов преобразования введен пиковый детектор, причем первый и второй входы блока для определения последовательности поступления входных сигналов соединены с вторыми выходами соответственно первого n второго каналов преобразования, а выход подключен к входу индикатора, второй выход блока управления соединен с четвертыми входами каналов преобразования, первые входы каждого из которых подключены к первым входам пиковых детекторов, выходы которых соединены с первыми входами коммутаторов и вторыми выходами каналов преобразования, четвертые входы которых подключены к вторым входам пиковых детекторов.

Текст

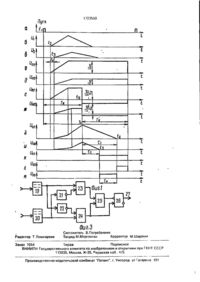

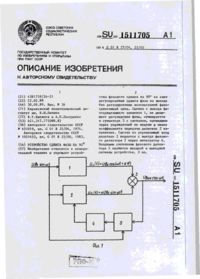

Изобретение относится к измерительной технике- Целью изобретения является расширение функциональных возможностей. Поставленная цель в способе достигается введением операций параллельного преобразования мгновенных значений входных сигналов и запоминания макси мального значения на заданное время, а также определяют последовательности поступления входных сигналов Способ заключается также в параллельном интегрировании входных сигналов, инвертировании проинтегрированных сигналов, масштабном преобразовании по амплитуде и их интегрировании, а также формировании начала и конца входного временного интервала. Цель в устройстве достигается введением устройства 17 определения последовательности поступления входных сигналов, индикатора 18 и в каждый из каналов преобразования - пиковых детекторов 5,6, Устройство также содержит два идентичных канала 1 7 преобразования, в состав которых входят масштабные инверторы 7,8, коммутаторы 9,10, интеграторы 11,12, электронные ключи 13,14 и компараторы 15,16, а также блок 3 управления, элемент "Неравнозначность" 4, входные шины "Вход 1", "Вход2", "Пуск" и выходную шину "Выход", 2 с,п.ф-лы, 3 ил. ел с ftr/ (Л о о 1723560 4 Изобретение относится к измерительнии сигналов, масштабном преобразовании ной технике и предназначено для преобпо амплитуде и их интегрировании, формиразования временного сдвига между ровании начала и конца выходного временсигнэпами в интервал времени. ного интервала при достижении Устройство для реализации способа со- 5 проинтегрированными инвертированными сигналами нулевого уровня, проводят падержит два одинаковых канала преобразораллельное преобразование мгновенных вания, включающие нормализаторы уровня значений входных сигналов путем отслежисигналов, преобразователи напряжениевания входных сигналов до достижения макток и общую часть, состоящую из формирователя, одновибратора, двух ключей, 10 симального значения и запоминания этого значения на определенное время, а затем интегрирующего конденсатора, нуль-оргапроводят параллельное интегрирование прена, двух триггеров, блока управления и устобразованных сигналов, а также определяройства для измерения интервала времени ют последовательность поступления [1]. 15 входных сигналов. Недостатками известного способа и усСпособ реализуется устройством, сотройства являются низкое быстродействие, держащим два одинаковых канала, каждый вызванное необходимостью приведения из которых содержит интегратор, электронвходных сигналов к одному уровню, и невозный ключ, компаратор, масштабный имверможность измерения временных сдвигов 20 тор и коммутатор, а также логический между одиночными сигналами. элемент "Неравнозначность" и блок управНаиболее близким к предлагаемому по ления, выход масштабного инвертора притехнической сущности способу является соединен к второму входу коммутатора, способ преобразования временного сдвига выход которого подключен к входу интеграмежду двумя сигналами, основанный на параллельном интегрировании неинвертиро- 25 тора и электронного ключа, выходы который объединены и подключены к входу компараванных входных сигналов, причем время тора, а входы компараторов обоих канало§ интегрирования входных сигналов больше присоединены к первому и второму входам длительности фронтов и ожидаемой длиэлемента "Неравнозначность", при этом тельности между сигналами, затем инвертировании входных сигналов, масштабном 30 первый выход блока управления соединен с управляющими входами коммутаторов и преобразовании по амплитуде и их интегривходами стробировзния компараторов оборовании, формировании начала и конца выих каналов, а второй его выход соединен с ход ного временного интервала при управляющими входами электронных клюдостижении проинтегрированными инвер35 чей обоих каналов, в которое дополнительтированными сигналами нулевого уровня но введены устройство для определения [2]. последовательности поступления входных Устройство для реализации способа сосигналов и индикатор, а каждый из каналов держит два одинаковых канала преобразодополнительно содержит пиковый детеквания, каждый из которых содержит 40 тор, причем к входу каждого качала подклюинтегратор, электронный ключ, компарачен вход пикового детектора, выход тор, масштабный инвертор и коммутатор, а которого присоединен к входу масштабного также логический элемент "Неравнозначинвертора и первому входу коммутатора, а ность" и блок управления [2]. второй вход блока управления соединен с Недостатком известного способа и уст45 управляющими входами пиковых детекторойства является невозможность измереров обоих каналов, входы устройства для ния временных сдвигов между одиночными определения последовательности поступсигналами треугольной или трапецеидальления входных сигналов подключены к выной формы с вершиной малой длительноходу пикового детектора каждого из сти, а также невозможность определения 50 каналов, а выход устройства присоединен к последовательности поступления входных входу индикатора. сигналов. Заявленная совокупность существенЦель изобретения - расширение функных признаков не известна ни из аналогов. циональных возможностей. ни из прототипа, позволяет достичь поставЦель достигается тем, что в способе преобразования временного сдвига меж- 55 ленную цель и, следовательно соответствует критерию "существенные ОТЛИЧИЙ". ду двумя сигналами, основанном на паралНа фиг.1 приведены временные диаглельном интегрировании сигналов, за раммы, поясняющие сущность способа; на время интегрирования сигналов, большее фиг.2 - блок-схема устройства для осущестдлительности фронтов и ожидаемой дливления способа; на фиг 3 - схема устройства тельности между сигналами, инвертирова 1723560 Ти для определения последовательности поступления входных сигналов Сущность предлагаемого способа заС) б н2 ключается в следующем т е. Входные сигналы Ui(t} и U2(t- г х ) ( (фиг.16,в), имеющие, например, треугольГ 2 = (Ти - t3) Км • ную форму, параллельно преобразовываютИнтервалы времени п и тг соответстся в сигналы трапецеидальной формы Uni(t) вуют с масштабирующим коэффициентом и Un2(t- г х ). Это осуществляется путем отслеживания входных сигналов до до- 10 Км интегральному времени существования сигналов от их начала до момента времени хл. стижения максимального значения и запоРазность этих интервалов времени г і и хч минания этого значения на заданное время соответствует с масштабным коэффициен(фиг.1г,д), Параллельно преобразованные том Км интегральному временному сдвигу сигналы интегрируются в течение времения, большего длительности их фронтов и 15 между сигналами Ги = П ~ Vi = tf>-t5 (7) ожидаемой длительности между сигналами Начало выходного интервала г и форми(фиг.1з,и) руется в момент времени ts, а его конец - в Ти момент времени Хб(фиг 1м) При одинаковых 11и1 (t)= Ki / Uni (t)dt, (1) о 20 формах входных сигналов и равных длительТи ностях их фронтов интегральный временной UM2(t)=K2 /Un2(t- r x )dt, (2) сдвиг, определенный на нулевом уровне бу0 дет давать одинаковые результаты где Uni(t), UM2(t) - напряжения, полученные Устройство для преобразования вресоответственно в результате интегрирова25 менного сдвига между двумя сигналами ния первого и второго преобразованных (фиг.2) содержит каналы 1 и 2 преобразовасигналов; ния, блок 3 управления и логический элеКі = Кг = К - коэффициент передачи мент "Неравнозначность" 4 Каналы 1 и 2 интеграторов, преобразования включают пиковые детекТи - время интегрирования; 30 торы 5 и б, масштабные инверторы 7 и 8, Гх - измеряемый временной сдвиг. коммутаторы 9 и 10, интеграторы 11 и 12, Одновременно определяют последоваэлектронные ключи 13 и 14, компараторы 15 тельность поступления входных сигналов и 16 устройство 17 определения последоваUi(t)HUa(t-r x ) тельности поступления входных сигналов и Затем инвертируют каждый из преобразованных входных сигналов и масштабиру- 35 индикатор 18 Входы пиковых детекторов 5 и 6 являютют их в одинаковое Км число раз (фиг.1е,ж) ся входами устройства Пиковый детектор 5 (3) соединен с масштабным инвертором 7, комКм мутатором 9 и входом устройства 17опредеUM2 UMH2 = (4) 40 ления последовательности поступления входных сигналов, а пиковый детектор 6 согде 1)ин1, 1!ин2 ~ напряжения, полученные единен с масштабным инвертором 8, коммупосле инвертирования и масштабного претатором 10 и вторым входом устройства 17. образования; Коммутатор 9 последовательно соединен с Ut.ii, и М 2'амплитуды входныхеигналов. 45 интегратором 11, компаратором 15 а коммутатор 10 последовательно соединен с инНапряжения иИн1 и I W интегрируют тегратором 12 и компаратором 16 Выходы далее от напряжений, полученных при инкомпараторов 15 и 16 соединены с элементегриро&ании преобразованных входных том "Неравнозначность" А, а устройство 17 сигналов до момента достижения проинтегрированных напряжений нулевого уровня 50 ~с индикатором 18 Блок 3 управления соединен одним выходом с пиковыми детекто(фиг.із.и). Интервалы времени, в течение рами 5 и 6 и электронными ключами 13 и 14, которых осуществляется интегрирование а другим выходом - с коммутаторами 9 и 10 инвертированных сигналов ІІині И UMH2. сои компараторами 15 и 16 Электронные клюответственно равны 55 чи 13 и 14 подключены к входам и выходам интеграторов 11 и 12 Т Устройство для определения последоUni(t)dt вательности поступления входных сигналов Т і = t 6 ' ХА = (5) (фиг.3} содержит компараторы 19 и 20, логин1 ческие инверторы 21 и 22 элементы И 23 и 1723560 24, элемент ИЛИ 25 и D-триггер 26. Компаратор 19 соединен с элементом И 23 и логическим инвертором 22, а компаратор 20 - с элементом И 24 и инвертором 21 Инверторы 21 и 22 соединены с вторыми входами 5 элементов И 23 и 24, входы последних подключены к элементу ИЛИ 25. Элемент И 24 соединен с входом D-триггера 26, а вход Стриггера 26 соединен с входом элемента ИЛИ 25. Выход триггера 26 подключен к 10 индикатору 18. Блок управления в настоящее время целесообразно выполнять на микропроцессорной базе, например на однокристальных микроЭВМ серии К 1816. Остальные узлы 15 устройства достаточно подробно описаны в литературе. Устройство работает следующим образом. В исходном состоянии блок 3 управле- 20 ния удерживает открытыми электронные ключи 13 и 14, вследствие чего интеграторы 11 и 12 разряжены до нулевого уровня, а также препятствует срабатыванию пиковых детекторов 5 и б и компараторов 15 и 16 25 путем подачи сигналов соответственно на управляющие входы и на выходы стробирования. Блок 3 управления осуществляет запуск устройства до момента прихода первого из входных сигналов. Этот момент 30 времени t i показан на фиг.1а Импульсом запуска блок 3 управления открывает пиковые детекторы 5 и б, закрывает электронные ключи 13 и 14 и подключает коммутаторы 9 и 10 к выходам пиковых детекторов 5 и 6. В 35 моменты t2 и t3 на входы пиковых детекторов 5 и 6 поступают соответственно входные сигналы Ui(i) и U2(t- тх) (фиг.1б,в). Производится отслеживание входных сигналов пиковыми.детекторами 5 и 6 до до- 40 стижения максимального значения и запоминания этого значения на заданное время (фиг.іг.д). Одновременно производится определение последовательности поступления входных сигналов Ui(t) и ІІ2 (t- 45 -Тх). С этой целью выходные сигналы пиковых детекторов 5 и 6 подаются на компараторы 19 и 20. Выходной сигнал компаратора 19 поступает на инвертор 22 и на первый вход логического элемента И 23, а выходной сиг- 50 нал компаратора 20 - на инвертор 21 и второй вход логического элемента И 24. На другой вход логического элемента И 23 поступает выходной сигнал инвертора 21, а на первый вход логического элемента И 24 - Е5 выходной сигнал инвертора 22. Выходные сигналы логических элементов И 23 и 24 поступают на входы логического элемента ИЛИ 25, а выходной сигнал логического эле 8 мента И 24, кроме того, поступает на D-вход D-триггерз 26, на счетный вход которого приходит выходной сигнал логического элемента ИЛИ 25. Если по первому каналу входной сигнал приходит первым, то на оыходе элемента И 23 появится логическая " 1 " , на выходе элемента М 24 - логический "0" и на выходе D-триггера - логический "0". Если по второму каналу входной сигнал приходит первым, то на выходе элемента И 23 появится логический "0", на выходе элемента И 24 логическая " 1 " и на выходе D-триггера логическая " 1 " . Одновременно производится параллельное интегрирование преобразованных сигналов интеграторами 11 и 12 с момента времени t i до момента времени ХА, обозначенного как Ти (фиг.Із,и). Время интегрирования Ти больше суммы длительности фронта входного сигнала и ожидаемой длительности между сигналами. В момент времени it блок 3 подключает коммутаторы 9 и 10 к выходам масштабных инверторов 7 и 8 (фиг 1е,ж) и разрешает срабатывание компараторов 15 и 16. Инвертированные масштабно преобразованные сигнзлы интегрируются отуровня, полученного при интегрировании неинвертированпых преобразованных сигналов, до достижения момента равенства выходных напряжений интеграторов 11 и 12 нулевому уровню (фиг 1з,и). В моменты времени ts и to на выходах компараторов 15 и 16 появляются рабочие перепады напряжения (фиг.1к.л). Масштабный коэффициент Км выбирается таким образом, чтобы моменты ts и te окончания интегрирования наступили до окончания плоской вершины преобразованного сигнала. Выходные сигналы компараторов 15 и 16 поступают на входы логического элемента "Неравнозначность" 4, нэ выходе которого получают выходной временной интервал г и (фиг.1м),соответствующий сдвигу между сигналами. Предлагаемый способ и устройство характеризуются высокой помехоустойчивостью вследствие использования для формирования временного интервала не одной точки, а целого участка входного сигнала, высоким быстродействием за счет обеспечения возможности работы с одиночными сигналами, кроме того, преобразуемый временной сдвиг не зависит от амплитуды сигналов Положительный эффект изобретении в отличие от известного заключается в расширении функциональных возможностей за счет обеспечения возможностей преобразо 1723560 ваниі временных сдвигов между сигналами с вершиной малой длительности Формула изобретения 1. Способ преобразования временного сдвига между двумя сигналами, заключаю- 5 щийся в параллельном интегрировании входных сигналов в течение времени большего длительности фронтов и ожидаемой длительности между сигналами, инвертировании проинтегрированных сигналов, мае- 10 штабном преобразовании по амплитуде и их интегрировании, формировании начала и конца входного временного интервала при достижении интегрируемым сигналом нулевого уровня, о т л и ч а ю щ и й с я тем, что, 15 с целью расширения функциональных возможностей, осуществляют параллельное преобразование мгновенных значений входных сигналов путем отслеживания их значений до достижения максимального 20 значения и запоминание па заданное время, а также определяют последовательность поступления входных сигналов 2 Устройство для преобразования временного сдвига между двумя сигналами, со- 25 держащее два идентичных канала преобразования, в состав каждого из которых входят масштабный инвертор, коммутатор, интегратор, электронный ключ и компаратор, причем вход масштабного ин- 30 верторэ соединен с первым входом коммутатора, второй вход которого подключен к выходу масштабного инвертора, а выход соединен с входом интегратора и первым входом электронного ключа, выходы которых 35 подключены к первому входу компаратора, второй вход которого соединен с третьим входом электронного ключа и вторым входом канала преобразования, а выход под ключен к первому выходу канала преобразования третий влод которого соединен с вторым входом электронного ключа блок управления элемент "Неравнозначьость", входные шины "Вход 1", "Вход 2", ' Пуск" и выходную шину "Выход", которая подключена к выходу элемента "Неравнозначность", первый и второй входы которого соединены с первыми выходами соответственно первого и второго каналов преобразования, вторые входы которых подключены к первому выходу блока управления, второй выход которого соединен с третьими входами первого и второго каналов преобразования, первые входы которых подключены к шинам "Вход 1" и "Вход 2" соответственно, э вход блока управления соединен с шиной "Пуск", о т л и ч а ю щ е е с я тем что, с целью расширения функциональных возможностей, в него дополнительно введены блок для определения последовательности поступления входных сигналов и индикатор, а в каждый из каналов преобразования введен пиковый детектор, причем первый и второй входы блока для определения последовательности поступления входных сигналов соединены с вторыми выходами соответственно первого и второго каналов преобразования, а ВЫУОД подключен к входу индикатора, второй выход блока управления соединен с четвертыми входами каналов преобразования, первые входы каждого из которых подключены к первым входам пиковых детекторов, выходы которых соединены с первыми входами коммутаторов и вторыми выходами каналов преобразования, четвертые входы которых подключены к вторым входам пиковых детекторов. 1723560 Редактор Т Лошкарева Составитель В.Погребенник Техред М.Моргеитал Корректор М Шароши Заказ 1064 Тираж Подписное ВНМИП1/1 Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб , 4/5 Производственно-издательский комбинат "Патент", г. Ужгород ул Гагарина 101

ДивитисяДодаткова інформація

Назва патенту англійськоюTransformation method for skewing beween two signals and device for its realization

Автори англійськоюPohrebennyk Volodymyr Dmytrovych, Sopruniuk Petro Markiianovych

Назва патенту російськоюСпособ преобразования временного сдвига между двумя сигналами и устройство для его реализации

Автори російськоюПогребенник Владимир Дмитриевич, Сопрунюк Петр Маркианович

МПК / Мітки

МПК: G04F 10/00

Мітки: зсуву, пристрій, сигналами, двома, спосіб, реалізації, часового, перетворення

Код посилання

<a href="https://ua.patents.su/6-11443-sposib-peretvorennya-chasovogo-zsuvu-mizh-dvoma-signalami-ta-pristrijj-dlya-jjogo-realizaci.html" target="_blank" rel="follow" title="База патентів України">Спосіб перетворення часового зсуву між двома сигналами та пристрій для його реалізації</a>

Попередній патент: Пристрій для обчищення качанів кукурудзи

Наступний патент: Кондицінований контейнер транспортного засобу

Випадковий патент: Безпілотний літальний апарат з амортизаційною пневматичною подушкою