Комбінаційний суматор

Номер патенту: 115751

Опубліковано: 11.12.2017

Автори: Грига Володимир Михайлович, Круліковський Борис Борисович, Николайчук Ярослав Миколайович, Возна Наталія Ярославівна, Давлетова Аліна Ярославівна

Формула / Реферат

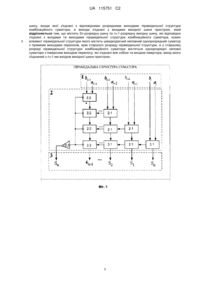

Комбінаційний суматор, який містить вхідну шину, виходи якої з'єднані з відповідними прямими входами пірамідальної структури, яка містить, з'єднані між собою прямими горизонтальними та вертикальними інформаційними зв'язками, структури однорозрядних неповних двійкових суматорів, які містять елементи І та Виключне АБО з прямими входами та виходами, вихідну шину, входи якої з'єднані з відповідними розрядними виходами пірамідальної структури комбінаційного суматора, а виходи з'єднані з входами вихідної шини пристрою, який відрізняється тим, що містить 2n-розрядну шину та n+1-розрядну вихідну шину, які відповідно з'єднані з входами та виходами пірамідальної структури комбінаційного суматора, кожен елемент пірамідальної структури якого містить швидкодіючий неповний однорозрядний суматор з прямими виходами переносів, крім старшого розряду пірамідальної структури, а у старшому розряді пірамідальної структури комбінаційного суматора містяться однорозрядні неповні суматори з інверсним виходом переносу, які з'єднані між собою та входом інвертора, вихід якого з'єднаний з n+1-им входом вихідної шини пристрою.

Текст

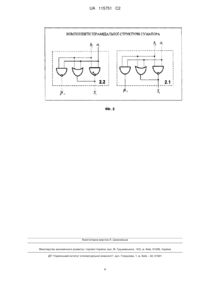

Реферат: Винахід належить до засобів обчислювальної техніки і може бути використаний як компонент швидкодіючих арифметико-логічних пристроїв та процесорів опрацювання цифрових даних. Комбінаційний суматор містить 2n-розрядну вхідну шину, на виході якої формуються прямі коди двох багаторозрядних двійкових чисел, які подаються на входи пірамідальної структури з вертикальними та горизонтальними інформаційними зв'язками між однорозрядними неповними двійковими суматорами, у старшому розряді якої містяться однорозрядні неповні суматори з інверсним виходом переносу, які з'єднані між собою та входом інвертора, вихід якого з'єднаний з n+1-им входом вихідної шини пристрою. Технічним результатом є розширення функціональних можливостей пристрою введенням 2n-розрядної вхідної шини та n+1-розрядної вихідної шини, зменшенням апаратної складності більш, ніж у 1,5 разу введенням швидкодіючих однорозрядних неповних суматорів, які містять 3 логічні елементи та підвищенням швидкодії пристрою більш ніж у 2 рази введенням однорозрядних неповних двійкових суматорів з затримкою сигналів на 1 мікротакт. UA 115751 C2 (12) UA 115751 C2 UA 115751 C2 5 10 15 20 25 30 35 40 45 50 55 60 Комбінаційний суматор належить до засобів обчислювальної техніки і може бути використаний як компонент швидкодіючих арифметико-логічних пристроїв та процесорів опрацювання цифрових даних. Відомий аналог - комбінаційний суматор [Дрозд О.В., Харченко B.C. Робоче діагностування безпечних інформаційно-керуючих систем, Харків: "ХАІ", 2012, - C. 99, рис. 4.3], який містить вхідну шину, з'єднану з відповідними входами пірамідальної структури, що містить з'єднані між собою вертикальними та горизонтальними зв'язками логічні елементи І та АБО, виходи якої з'єднані з відповідними входами вихідної шини, яка є виходом пристрою. Недоліком такого комбінаційного суматора є обмежені функціональні можливості, обумовлені тим, що такий суматор виконує додавання бітів вхідного двійкового числоімпульсного коду і представляє результат додавання у розрядно-позиційному двійковому коді. Тому такий комбінаційний суматор не забезпечує додавання двох паралельних двійкових кодів і представлення результатів додавання у коді двійкової системи числення. Відомий прототип - комбінаційний суматор [Гринберг И.П., Комбинационный сумматор //Патент RU № 2514785, Бюл. № 13, 2014], який містить 6-ти розрядну вхідну шину, виходи якої з'єднані з відповідними прямими входами пірамідальної структури, яка містить, з'єднані між собою горизонтальними та вертикальними інформаційними зв'язками, логічні елементи Виключне АБО та І", виходи якої з'єднані з відповідними входами вихідної шини, яка є виходом пристрою. Недоліками такого комбінаційного суматора є обмежені функціональні можливості, висока апаратна складність та низька швидкодія. Обмежені функціональні можливості такого суматора обумовлені чим, що відомий суматор дозволяє виконувати додавання тільки трирозрядного двійкового числа. Висока апаратна складність такого суматора обумовлена тим, що ланцюг послідовно з'єднаних входами та виходами логічних елементів Виключне АБО у старшому розряді пірамідальної структури такого суматора, кожен з яких містить не менше 4-х логічних елементів [Шило В.Л. Популярные цифрове микросхемы: Справочник. - Μ: Радио и связь, 1988 г., с. 57, рис. 1.35] для формування відповідного біта на виході старшого розряду вихідної шини пристрою. Низька швидкодія такого суматора обумовлена тим, що пірамідальна структура містить логічні елементи Виключне АБО тільки з прямими входами та прямим виходом, що потребує застосування структурної реалізації логічних елементів Виключне АБО на основі не менше 3 послідовно з'єднаних логічних елементів НІ, І-НІ та АБО-НІ [Шило В.Л. Популярные цифрове микросхемы: Справочник. - Μ: Радио и связь, 1988 г., с. 57, рис. 1.35]. В основу удосконалення комбінаційного суматора поставлена задача розширення його функціональних можливостей, зменшення апаратної складності та підвищення швидкодії шляхом додаткового введення вхідної 2n-розрядної та вихідної n+1 розрядної шини (n≥3), додатковим введенням у кожен елемент пірамідальної структури швидкодіючого однорозрядного суматора з затримкою сигналів на 1 мікротакт, який містить не більше 3 логічних елементів, з прямими виходами переносів (крім старшого розряду пірамідальної структури) та додатковим введенням у старший розряд пірамідальної структури комбінаційного суматора швидкодіючих, з затримкою сигналів на 1 мікротакт, однорозрядних двійкових суматорів з інверсним виходом переносу, виходи яких з'єднані між собою та входом додатково введеного інвертора, вихід якого додатково з'єднаний з n+1 входом вихідної шини пристрою. Поставлена задача вирішується тим, що комбінаційний суматор містить вхідну 2n розрядну шину, виходи якої з'єднані з відповідними прямими входами пірамідальної структури, яка містить, з'єднані між собою прямими горизонтальними та вертикальними інформаційними зв'язками, структури однорозрядних неповних двійкових суматорів, які містять елементи І та Виключне АБО з прямими входами та виходами, вихідну шину, входи якої з'єднані з відповідними розрядними виходами пірамідальної структури комбінаційного суматора, а виходи з'єднані з входами вихідної шини пристрою, згідно з запропонованим пристроєм, містить додатково введену 2n-розрядну шину та додатково введену n+1-розрядну вихідну шину, які відповідно додатково з'єднані з входами та виходами пірамідальної структури комбінаційного суматора, додатковим введенням у кожен елемент пірамідальної* структури швидкодіючого однорозрядного суматора з затримкою сигналів на 1 мікротакт, який містить не більше 3 логічних елементів, з прямими виходами переносів (крім старшого розряду пірамідальної структури) та додатковим введенням у старший розряд пірамідальної структури комбінаційного суматора швидкодіючих, з затримкою сигналів на 1 мікротакт, однорозрядних двійкових суматорів з інверсним виходом переносу, виходи яких з'єднані між собою та входом додатково введеного інвертора, вихід якого додатково з'єднаний з n+1 входом вихідної шини пристрою, швидкодіючого, однорозрядного неповного двійкового суматора. 1 UA 115751 C2 5 10 15 20 25 На фіг. 1 зображена структурна схема комбінаційного суматора: 1 - вхідна 2n-розрядна шина (a0b0, a1b1, a2b2,…, an-1bn-1); 2 - пірамідальна структура, яка містить: наступні типи однорозрядних неповних суматорів: 2.1-3 прямими виходами переносу (фіг. 2); 2.2 - з інверсним виходом переносу (фіг. 2); 2.3 - інвертор; 3 - вихідна шина комбінаційного суматора (S0,S1,S2,…, S n-1, Sn). Двійкові n-розрядні коди (n - ціле число ≥3) подаються на відповідні входи (a0b0, a1b1, a2b2,…, an-1bn-1) вхідної шини 1. Виходи вхідної шини 1 з'єднані з відповідними входами однорозрядних неповних суматорів 2.1, 2.2 комбінаційної структури 2. Прямі виходи суми всіх однорозрядних суматорів 2.1 та 2.2 з'єднані з відповідними входами (S0,S1,S2,…, S n-1, Sn) вихідної шини 3. Інверсні виходи переносів всіх суматорів (2.2) комбінаційної структури 2 з'єднані між собою та входом інвертора 2.3, вихід якого є Sn-им виходом вихідної шини комбінаційного суматора. Комбінаційний суматор працює наступним чином. При надходженні на вхідну шину 1 n-розрядних кодів двійкових чисел (а0, а1, а2,…, аn-1) та (b0, b1, b2,…, bn-1) на її виходах формуються двійкові коди, які надходять на відповідні входи комбінаційної структури 2. При цьому на виходах лінійки однорозрядних суматорів (2.1, 2.2) формується n-розрядний двійковий код суми вхідних кодів, який надходить на входи (S0,S1,S2,…, S n-1, Sn) вихідної шини 3, а на виходах інверсних переносів суматорів (2.2) старшого розряду комбінаційної структури 2 формується інверсний сигнал переносу, який надходить на вхід логічного елемента НІ (2.3), на виході якого формується старший біт суми Sn, що надходить на вихідну шину 3. Таким чином, у результаті запропоновано удосконалення комбінаційного суматора, у порівнянні з прототипом, досягнуто розширення функціональних можливостей комбінаційного суматора за рахунок здійснення додавання двох двійкових кодів з розрядністю n≥3. Досягнуто зменшення апаратної складності запропонованого комбінаційного суматора за рахунок зменшення числа логічних елементів у кожному однорозрядному двійковому суматорі та застосуванні одного інвертора для формування сигналу Sn-ого виходу комбінаційного суматора. Тобто число логічних елементів запропонованого n-розрядного комбінаційного 2 30 суматора складає: A C A ПC A1 (n 2) 3 1 ( A ПC - апаратна складність пірамідальної 2 структури, A 1 - апаратна складність інвертора) Наприклад, при n 4 : A C (16 2) 3 1 31 2 логічний елемент. Відповідно апаратна складність прототипу рівна: 35 40 45 2 2) 5 n (16 2) 5 4 54 логічних елементи. 2 2 Тобто, апаратна складність запропонованого комбінаційного суматора, не залежно від розрядності двійкових кодів, що додаються, зменшена більш ніж у 1,5 разу. Досягнуте збільшення швидкодії комбінаційного суматора визначається порівнянням оцінок часової складності прототипу та запропонованої структурної схеми суматора згідно з виразом КС nк , де n - розрядність вхідних кодів; к - число мікротактів затримки сигналів у найдовшому ланцюжку послідовно з'єднаних логічних елементів або вентилів комбінаційної структури. Оскільки у прототипі застосована схема ланцюга логічних елементів Виключне АБО у старшому розряді комбінаційного суматора з відомою структурою та затримкою сигналів не менше к 3v ( v - мікротакт), то загальна затримка сигналів у відомому комбінаційному суматорі у залежності від розрядності вхідних кодів n буде рівна С1 n 3 . У запропонованому комбінаційному суматорі затримка сигналів у старшому розряді комбінаційної структури рівна n+1. Тобто при n=4 підвищення швидкодії запропонованого комбінаційного 12 суматора у порівнянні з прототипом розраховується згідно з виразом: 3n n 1 і рівне: 5 2 . Технічний результат. Таким чином досягнуто розширення функціональних можливостей пристрою введенням n>3 - розрядної шини, зменшенням апаратної складності більш ніж у 7,5 разу та підвищенням швидкодії пристрою більш ніж у 2 рази. A C (n 50 ФОРМУЛА ВИНАХОДУ 55 Комбінаційний суматор, який містить вхідну шину, виходи якої з'єднані з відповідними прямими входами пірамідальної структури, яка містить, з'єднані між собою прямими горизонтальними та вертикальними інформаційними зв'язками, структури однорозрядних неповних двійкових суматорів, які містять елементи І та Виключне АБО з прямими входами та виходами, вихідну 2 UA 115751 C2 5 шину, входи якої з'єднані з відповідними розрядними виходами пірамідальної структури комбінаційного суматора, а виходи з'єднані з входами вихідної шини пристрою, який відрізняється тим, що містить 2n-розрядну шину та n+1-розрядну вихідну шину, які відповідно з'єднані з входами та виходами пірамідальної структури комбінаційного суматора, кожен елемент пірамідальної структури якого містить швидкодіючий неповний однорозрядний суматор з прямими виходами переносів, крім старшого розряду пірамідальної структури, а у старшому розряді пірамідальної структури комбінаційного суматора містяться однорозрядні неповні суматори з інверсним виходом переносу, які з'єднані між собою та входом інвертора, вихід якого з'єднаний з n+1-им входом вихідної шини пристрою. 3 UA 115751 C2 Комп’ютерна верстка Л. Ціхановська Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/501

Мітки: комбінаційний, суматор

Код посилання

<a href="https://ua.patents.su/6-115751-kombinacijjnijj-sumator.html" target="_blank" rel="follow" title="База патентів України">Комбінаційний суматор</a>

Попередній патент: 1-феніл-4-арил-5,6,7,8-тетрагідро-2,2а,8а-триазациклопента[сd]азулени, що мають протипухлинну активність

Наступний патент: Пластичне мастило

Випадковий патент: Спосіб лікування хворих з порушеннями бінокулярного і стереоскопічного зору