Суматор з прискореним переносом

Номер патенту: 117572

Опубліковано: 26.06.2017

Автори: Круліковський Борис Борисович, Грига Володимир Михайлович, Николайчук Ярослав Миколайович, Давлетова Аліна Ярославівна, Возна Наталія Ярославівна

Формула / Реферат

Суматор з прискореним переносом, що містить 2n-розрядну вхідну шину, (k=n/m) m-розрядних суматорів, на перші входи переносу яких поданий логічний "0", (k-1) m-розрядних суматорів, на перші входи переносу яких подана логічна "1", (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1-розрядну вихідну шину, в якому відповідні виходи вхідної шини з'єднано з відповідними другими інформаційними входами всіх m-розрядних суматорів з нульовими входами переносу, перші інформаційні виходи першого m-розрядного суматора з'єднано з відповідними, починаючи з нульового, розрядами вихідної шини, перші інформаційні виходи кожного m-розрядного суматора з нульовими входом переносу з'єднано з відповідними першими інформаційними входами кожного відповідного мультиплексора, перші виходи якого з'єднано з відповідними входами вихідної шини, другі інформаційні входи кожного мультиплексора з'єднано з другими виходами переносу відповідного m-розрядного суматора з нульовими входом переносу, третій прямий керуючий вхід першого мультиплексора з'єднано з другим виходом переносу першого m-розрядного суматора, другі виходи кожного мультиплексора з'єднано з третіми прямими входами кожного наступного мультиплексора, а другий вихід останнього мультиплексора з'єднано з n-м входом вихідної шини пристрою, який відрізняється тим, що додатково містить другі інформаційні входи кожного мультиплексора, які з'єднано з першими виходами кожного відповідного інкрементного m-розрядного суматора з входом переносу логічної одиниці, перший вхід якого з'єднано з другим виходом першого m-розрядного суматора, а в кожній наступній відповідній парі m-розрядних суматорів, перший вхід відповідного інкрементного m-розрядного суматора додатково з'єднано з прямим виходом попереднього мультиплексора, другі входи кожного m-розрядного інкрементного суматора додатково з'єднано з першими інформаційними m-розрядними виходами кожного відповідного m-розрядного суматора з входом переносу логічного нуля, інверсний вихід першого m-розрядного інкрементного суматора з'єднано з третім інверсним входом парафазного першого мультиплексора, третій інверсний вихід першого та кожного мультиплексора додатково з'єднано з кожним інверсним входом кожного наступного мультиплексора.

Текст

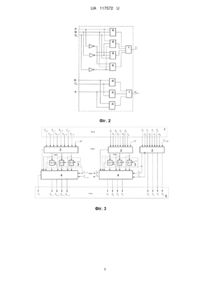

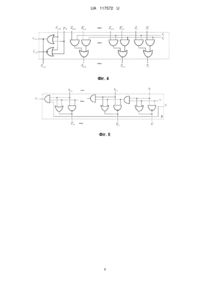

Реферат: Суматор з прискореним переносом містить 2n-розрядну вхідну шину, (k=n/m) m-розрядних суматорів, на перші входи переносу яких поданий логічний "0", (k-1) m-розрядних суматорів, на перші входи переносу яких подана логічна "1", (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1-розрядну вихідну шину. Додатково містить другі інформаційні входи кожного мультиплексора, інкрементний mрозрядний суматор, парафазний мультиплексом. UA 117572 U (12) UA 117572 U UA 117572 U 5 10 15 20 25 30 35 40 45 50 55 60 Пристрій належить до засобів обчислювальної техніки і може бути використаний як швидкодіючі компоненти арифметико-логічних пристроїв процесорів цифрового опрацювання сигналів та даних. Відомий аналог-суматор з прискореним переносом [http://phg.su/basis2/x133.HTM, с.6/6, 11.5], що містить вхідну 2n-розрядну шину, виходи якої з'єднані з відповідними входами nкомірок Брента-Кунга, виходи яких з'єднані з відповідними входами комбінаційної структури з прискореним переносом, виходи якої з'єднані з відповідними входами (n+1)-розрядної вихідної шини. Недоліком такого пристрою є велика апаратна складність, яка обумовлена наявністю великого числа компонентів, які реалізують комбінаційну структуру пристрою на логічних елементах, число яких швидко зростає при збільшенні розрядності суматора. Відомий аналог - пристрій додавання багаторозрядних двійкових чисел [Патент на корисну модель UA № 97162, Бюл. № 5, 2015], який містить першу та другу n-розрядні вхідні шини, виходи яких з'єднані з відповідними входами комбінаційної структури з прискореним переносом, виходи якої з'єднані з відповідними виходами n-розрядної вихідної шини. Недоліком такого пристрою є прискорення отримання суми двійкових чисел згідно з середньостатистичною імовірнісною характеристикою, яка залежить від випадкових значень двійкових кодів, що додаються. Прискорення операції додавання у такому пристрої може значно перевищувати оцінку часової затримки переносів τ=log2n, особливо при невеликій розрядності таких суматорів для n=16, 32, 64, що характерно для типових мікроконтролерів та універсальних процесорів персональних комп'ютерів. За найближчий аналог вибрано відомий суматор з прискореним переносом [http://phg.su/basis2/X133.HTM, с.6/8, 11.4], що містить 2n-розрядну вхідну шину, (k=n/m) mрозрядних суматорів, на перші входи переносу яких поданий логічний "0", (k-1) m-розрядних суматорів, на перші входи переносу яких подана логічна "1", (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1-розрядну вихідну шину, в якому відповідні виходи вхідної шини з'єднані з відповідними другими інформаційними входами всіх mрозрядних суматорів з нульовими та одиничними входами переносу, перші інформаційні виходи першого m-розрядного суматора з'єднані з відповідними, починаючи з нульового, розрядами вихідної шини, перші інформаційні виходи кожної пари m-розрядних суматорів з відповідними нульовими та одиничними входами переносу з'єднані з відповідними першими інформаційними входами кожного відповідного мультиплексора, перші виходи якого з'єднані з відповідними входами вихідної шини, другі інформаційні входи кожного мультиплексора з'єднані з другими виходами переносу відповідних пар m-розрядних суматорів, третій прямий керуючий вхід першого мультиплексора з'єднаний з другим виходом переносу першого m-розрядного суматора, другі виходи кожного мультиплексора з'єднані з третіми прямими входами кожного наступного мультиплексора, а другий вихід останнього мультиплексора з'єднаний з (n)-м входом вихідної шини пристрою. Недоліком такого пристрою є велика апаратна складність та низька швидкодія. Велика апаратна складність обумовлена великою апаратною складністю (k-1) m-розрядних суматорів, на входи наскрізних переносів яких подана логічна "1", та наявністю у кожному мультиплексорі двох інверторів. Оцінка апаратної складності найближчого аналогу (суматора з прискореним переносом) визначається сумарною кількістю логічних елементів у структурах m-розрядних суматорів та мультиплексорів при заданій розрядності вхідних n-розрядних двійкових кодів, які додаються, згідно з виразом: А=АC0+АС1+АМП, де АС0 - апаратна складність всіх m-розрядних суматорів з входами логічного "0"; АС1 - апаратна складність всіх m-розрядних суматорів з входами логічної "1"; АМП апаратна складність всіх (m+1)-розрядних мультиплексорів з однофазними прямими входами. Оцінка апаратної складності найближчого аналогу при розрядності вхідних двійкових кодів n=32 і 4-розрядних суматорів (m=4), отримаємо А=8AC0+7АС1+7АМП. При класичній реалізації m-розрядних суматорів на основі лінійок повних однорозрядних двійкових суматорів зі структурою, що зображена на фіг. 1 [http://phg.su/basis2/x134.HTM, с.1/6, 11.5], які містять 2 логічних елементи "виключне АБО", кожен з яких містить 4 логічні елементи [Шило В.Л. Популярные цифрове микросхемы: Справочник. - М: Радио и связь, 1988 г, с. 57, рис. 1.35], 2 логічні елементи "І" та один логічний елемент "АБО", що в сумі складає 11 логічних елементів, апаратна складність 8-ми 4-розрядних суматорів буде рівна АС0+АС1=(11×4)×(8+7)=660 логічних елементів та однофазних (m+1)-розрядних мультиплексорів, кожний розряд яких містить три логічні елементи та по два інвертори на керуючих входах [Шило 1 UA 117572 U 5 10 15 20 25 30 35 40 45 50 55 60 В.Л. Популярные цифрове микросхемы: Справочник. - М: Радио и связь, 1988 г, с. 147, рис. 1.106], що складає АМП=7×(8×3+2)=182 логічних елементи. Таким чином оцінка загальної апаратної складності відомого найближчого аналогу при застосуванні суматорів зі структурою представленою на фіг. 1 складає: А=660+182=842 логічних елементи. При реалізації m-розрядних суматорів на основі лінійок повних однорозрядних двійкових суматорів зі структурою на фіг. 2 [Шило В.Л. Популярные цифрове микросхемы: Справочник. – М.: Радио и связь, 1988 г, с. 154, рис. 1.112], які містять 12 логічних елементів їх сумарна апаратна складність складає АС0+АC1=(12×4)×(8+7)=720 логічних елементів, а з врахуванням апаратної складності аналогічних мультиплексорів, загальна апаратна складність такої схемотехнічної структури відомого найближчого аналогу буде рівна А=720+182=902 логічних елементи. Низька швидкодія такого пристрою обумовлена сумарною затримкою сигналів наскрізного переносу між m-розрядними суматорами, починаючи з другого, у кожному мультиплексорі з однофазним керуючим входом на 3 мікротакти [Шило В.Л. Популярные цифрове микросхемы: Справочник. – М.: Радио и связь, 1988 г, с. 147, рис. 1.106]. Наприклад, при розрядності пристрою n=32 біт і m=4 загальна затримка сигналів переносу у такому суматорі з прискореним переносом складає τ=7τМП+4τСМ, де τМП - затримка сигналів в однофазному 4-розрядному мультиплексорі (τМП=3υ мікротакти), який містить три послідовно з'єднаних логічних елементи (НІ→І→АБО), τСМ - затримка сигналів у першому 4-розрядному двійковому суматорі (τСМ=8υ мікротактів), при застосуванні одно-розрядних суматорів згідно структур, які зображені на фіг. 1 та фіг. 2, що складає загальну затримку сигналів у пристрої на τ=(7×3)+8=29υ. В основу корисної моделі поставлена задача зменшення апаратної складності та підвищення швидкодії суматора з прискореним переносом. Поставлена задача вирішується тим, що суматор з прискореним переносом містить 2nрозрядну вхідну шину, (k=n/m) m-розрядних суматорів, на перші входи переносу яких поданий логічний "0", (k-1) m-розрядних суматорів, на перші входи переносу яких подана логічна "1", (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1розрядну вихідну шину, в якому відповідні виходи вхідної шини з'єднано з відповідними другими інформаційними входами всіх m-розрядних суматорів з нульовими входами переносу, перші інформаційні виходи першого m-розрядного суматора з'єднано з відповідними, починаючи з нульового, розрядами вихідної шини, перші інформаційні виходи кожного m-розрядного суматора з нульовими входом переносу з'єднано з відповідними першими інформаційними входами кожного відповідного мультиплексора, перші виходи якого з'єднано з відповідними входами вихідної шини, другі інформаційні входи кожного мультиплексора з'єднано з другими виходами переносу відповідного m-розрядного суматора з нульовими входом переносу, третій прямий керуючий вхід першого мультиплексора з'єднано з другим виходом переносу першого m-розрядного суматора, другі виходи кожного мультиплексора з'єднано з третіми прямими входами кожного наступного мультиплексора, а другий вихід останнього мультиплексора з'єднано з n-м входом вихідної шини пристрою, в якому відповідно до корисної моделі додатково містить другі інформаційні входи кожного мультиплексора, які з'єднано з першими виходами кожного відповідного інкрементного m-розрядного суматора з входом переносу логічної одиниці, перший вхід якого з'єднано з другим виходом першого m-розрядного суматора, а в кожній наступній відповідній парі m-розрядних суматорів, перший вхід відповідного інкрементного m-розрядного суматора додатково з'єднано з прямим виходом попереднього мультиплексора, другі входи кожного m-розрядного інкрементного суматора додатково з'єднано з першими інформаційними m-розрядними виходами кожного відповідного m-розрядного суматора з входом переносу логічного нуля, інверсний вихід першого m-розрядного інкрементного суматора з'єднано з третім інверсним входом парафазного першого мультиплексора, третій інверсний вихід першого та кожного мультиплексора додатково з'єднано з кожним інверсним входом кожного наступного мультиплексора. Удосконалений суматор з прискореним переносом ілюструється рисунком (фіг. 3), де показано структурну схему такого n-розрядного суматора, на прикладі m=4-розрядних суматорів. Суматор з прискореним переносом містить: 1 - вхідна 2n-розрядна шина; 2-n/m, mрозрядних суматорів; 3-m-розрядний інкрементний суматор; 4-m+1-розрядний мультиплексор з парафазними керуючими входами; 5 вихідна n+1-розрядна шина. Суматор з прискореним переносом працює наступним чином: вхідні n-розрядні двійкові коди (а0b0, а1b1, a2b2, а3b3);(а4b4, a5b5, a6b6, а7b7);……(аn-4bn-4, аn-3bn-3, аn-2bn-2, аn-1bn-1) вхідної 2n 2 UA 117572 U 5 10 15 20 25 30 35 40 розрядної шини 1 одночасно надходять на відповідні перші інформаційні входи всіх mрозрядних суматорів 2 з нульовими входами переносу. Перші інформаційні виходи першого mрозрядного суматора 2 з'єднані з відповідними, починаючи з нульового, розряду входами (S0, S1, S2, S3) вихідної шини 5, а другий прямий (с 4) та третій інверсний ( c 4 ) виходи переносу першого m-розрядного суматора надходять на відповідні прямі та інверсні керуючі входи першого мультиплексора 4 (фіг. 4), вихідний прямий та інверсний сигнали якого надходять на відповідний прямий та інверсний входи наступного мультиплексора 4. Утворені вихідні коди кожного, починачи з другого, m-розрядного суматора 2 одночасно надходять на відповідні інформаційні входи відповідних мультиплексорів 4 та інформаційні входи відповідних інкрементних суматорів 3 (фіг. 5), сигнали інформаційних виходів яких надходять на відповідні m-розрядні інформаційні входи мультиплексорів 4. У результаті виконується операція додавання двох n-розрядних двійкових чисел з затримкою сигналів на 5 мікротактів у кожній парі послідовно з'єднаних m-розрядних суматорів 2 з нульовим входом переносу на основі пірамідальної структури, поданої на (фіг. 6) з реалізацією компонентів на основі однорозрядних неповних суматорів (фіг. 7) та суматорів 3 з входом логічної одиниці на основі інкрементного суматора зі структурою, поданою на (фіг. 5). Апаратна складність запропонованого суматора з прискореним переносом аналогічно розраховується за виразу: A=AC0+AC1+AМП, де AС0 - апаратна складність всіх m-розрядних пірамідальних суматорів 2 (фіг. 6) і входами логічного нуля; АC1 - апаратна складність всіх mрозрядних інкрементних суматорів 3 з входами логічної одиниці (фіг. 5); АМП - апаратна складність мультиплексора 4 з парафазними керуючими входами та виходами (фіг. 4). При n=32 і m=4, отримаємо А=8АC0+7АС1+7AМП. Апаратна складність пірамідального суматора 2: АС0=10×3+1=31. Апаратна складність інкрементного суматора 3: АC1=1+(3×3)=10. Апаратна складність мультиплексора 4: АМП=(3×4)+2=14. Таким чином оцінка загальної апаратної складності запропонованого суматора з прискореним переносом складає: А=(8×31)+(7×10)+(7×14)=416 логічних елементів. Часова складність запропонованого суматора з прискореним переносом, в якому затримка сигналів у першому 4-розрядному суматорі 2 з пірамідальною структурою (фіг. 6), в якому застосовані неповні однорозрядні суматори з затримкою сигналів переносу на 1 мікротакт (фіг. 7), а також затримкою сигналів у вихідному інверторі 2.3 (фіг. 6) складає 5 мікротактів та затримкою сигналів у мультиплексорах з парафазними входами на 2 мікротакти, загальна затримка сигналів у запропонованому суматорі при n=32 біти і m=4 буде рівна τ=(n/m1)×τМП+τСМ. Тобто, τ=(7×2)+5=19ν. Отже, зменшення апаратної запропонованого суматора з прискореним переносом по відношенню до найближчого аналогу складає 842 2 рази, а збільшення швидкодії складає 416 29 15 рази. , 19 Технічний результат. У результаті створено суматор з прискореним переносом, як засобу обчислювальної техніки та швидкодіючих компонентів арифметико-логічних пристроїв процесорів цифрового опрацювання сигналів та даних, зі зменшеною апаратною складністю у порівнянні з найближчим аналогом у 2 рази та підвищеною швидкодією у 1,5 разу. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 45 50 55 Суматор з прискореним переносом, що містить 2n-розрядну вхідну шину, (k=n/m) m-розрядних суматорів, на перші входи переносу яких поданий логічний "0", (k-1) m-розрядних суматорів, на перші входи переносу яких подана логічна "1", (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1-розрядну вихідну шину,в якому відповідні виходи вхідної шини з'єднано з відповідними другими інформаційними входами всіх m-розрядних суматорів з нульовими входами переносу, перші інформаційні виходи першого mрозрядного суматора з'єднано з відповідними, починаючи з нульового, розрядами вихідної шини, перші інформаційні виходи кожного m-розрядного суматора з нульовими входом переносу з'єднано з відповідними першими інформаційними входами кожного відповідного мультиплексора, перші виходи якого з'єднано з відповідними входами вихідної шини, другі інформаційні входи кожного мультиплексора з'єднано з другими виходами переносу відповідного m-розрядного суматора з нульовими входом переносу, третій прямий керуючий вхід першого мультиплексора з'єднано з другим виходом переносу першого m-розрядного 3 UA 117572 U 5 10 суматора, другі виходи кожного мультиплексора з'єднано з третіми прямими входами кожного наступного мультиплексора, а другий вихід останнього мультиплексора з'єднано з n-м входом вихідної шини пристрою, який відрізняється тим, що додатково містить другі інформаційні входи кожного мультиплексора, які з'єднано з першими виходами кожного відповідного інкрементного m-розрядного суматора з входом переносу логічної одиниці, перший вхід якого з'єднано з другим виходом першого m-розрядного суматора, а в кожній наступній відповідній парі m-розрядних суматорів, перший вхід відповідного інкрементного m-розрядного суматора додатково з'єднано з прямим виходом попереднього мультиплексора, другі входи кожного mрозрядного інкрементного суматора додатково з'єднано з першими інформаційними mрозрядними виходами кожного відповідного m-розрядного суматора з входом переносу логічного нуля, інверсний вихід першого m-розрядного інкрементного суматора з'єднано з третім інверсним входом парафазного першого мультиплексора, третій інверсний вихід першого та кожного мультиплексора додатково з'єднано з кожним інверсним входом кожного наступного мультиплексора. 4 UA 117572 U 5 UA 117572 U 6 UA 117572 U Комп’ютерна верстка А. Крижанівський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 7

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/38

Мітки: переносом, суматор, прискореним

Код посилання

<a href="https://ua.patents.su/9-117572-sumator-z-priskorenim-perenosom.html" target="_blank" rel="follow" title="База патентів України">Суматор з прискореним переносом</a>

Попередній патент: Дефлекторний розпилювач

Наступний патент: Інерційний запобіжний механізм для високошвидкісних приводів

Випадковий патент: Теплоізолююча оздоблювальна плита