Комбінаційний двійковий додавач

Номер патенту: 1452

Опубліковано: 25.03.1994

Автори: Кравцов Володимир Рувімович, Васіна Олена Миколаївна

Формула / Реферат

Комбинационный двоичный сумматор, содержащий m групп (m-1,..., n), причем каждая группа содержит восемь одноразрядных комбинационных двоичных сумматоров, восемь блоков формирования разрядных сигналов генерации и транзита переноса, блок формирования внутригрупповых переносов, а также блок формирования межгруппового переноса, причем входы блоков формирования разрядных сигналов генерации и транзита переноса соединены с входными сигналами слагаемых соответствующих одноразрядных сумматоров, выходы блоков формирования разрядных сигналов генерации и транзита переноса соединены с соответствующими входами соответствующих разрядов блока формирования внутригрупповых переносов, входной перенос группы соединен с входом переноса первого одноразрядного сумматора, с входом переноса блока формирования внутригрупповых переносов и с входом переноса блока формирования межгруппового переноса, входы переносов одноразрядных сумматоров, начиная со второго, соединены с выходами ускоренных переносов соответствующих разрядов блока формирования внутригрупповых переносов, выходы одноразрядных сумматоров соединены с соответствующими выходными шинами суммы сумматора, отличающийся тем, что блок формирования внутригрупповых переносов содержит одиннадцать блоков формирования внутригрупповых сигналов генерации и транзита переноса и семь блоков формирования ускоренного переноса, блок формирования межгруппового переноса содержит один блок формирования внутригрупповых сигналов генерации и транзита переноса и один блок формирования ускоренного переноса, в то время как каждый блок формирования ускоренного переноса содержит один элемент И и один элемент ИЛИ, причем первый вход элемента И соединен с входным сигналом транзита блока формирования ускоренного переноса, второй вход элемента И соединен с входным сигналом переноса блока формирования ускоренного переноса, первый вход элемента ИЛИ соединен с входным сигналом генерации блока формирования ускоренного переноса, выход элемента И соединен с вторым входом элемента ИЛИ, выход которого является выходным сигналом ускоренного переноса блока формирования ускоренного переноса, а каждый блок формирования внутригрупповых сигналов генерации и транзита переноса содержит два элемента И и один элемент ИЛИ, причем первый вход первого элемента И соединен с входным сигналом транзита первой группы входов блока формирования внутригрупповых сигналов генерации и транзита переноса, второй вход первого элемента И соединен с первым входом второго элемента И и соединен с входным сигналом транзите второй группы входов блока формирования внутригрупповых сигналов генерации и транзита, выход первого элемента И является выходным сигналом транзита блока формирования внутригрупповых сигналов генерации и транзита переноса, второй вход второго элемента И соединен с входным сигналом генерации первой группы входов блока формирования внутригрупповых сигналов генерации и транзита переноса, первый вход элемента ИЛИ соединен с входным сигналом генерации второй группы входов блока формирования внутригрупповых сигналов генерации и транзита переноса, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход которого является выходным сигналом генерации блока формирования внутригрупповых сигналов генерации и транзита, причем входы генерации и транзита первого блока формирования ускоренного переноса соединены с соответствующими входами первой группы первого блока формирования внутригрупповых сигналов генерации и транзита и являются входами генерации и транзита первого разряда блока формирования внутригрупповых переносов, выход первого блока формирования ускоренного переноса является выходом сигнала ускоренного переноса первого разряда блока формирования внутригрупповых переносов, входы генерации и транзита второй группы первого, второго, третьего и четвертого блоков формирования внутригрупповых сигналов генерации и транзита переноса являются входами генерации и транзита соответственно второго, четвертого, шестого и восьмого разрядов блока формирования внутригрупповых переносов, входы генерации и транзита первой группы второго блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы пятого блока формирования внутригрупповых сигналов генерации и транзита, переноса и являются входами генерации и транзита третьего разряда блока формирования внутригрупповых переносов, входы генерации и транзита первой группы третьего блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы девятого блоке формирования внутригрупповых сигналов генерации и транзите переноса и являются входами генерации и транзита пятого разряда блока формирования внутригрупповых переносов. входы генерации и транзита первой группы четвертого блока формирования внутригрупповых сигналов генерации и транзита соединены с соответствующими входами второй группы седьмого блока формирования внутригрупповых сигналов генерации и транзита и являются входами генерации и транзита седьмого разряда блоке формирования внутригрупповых переносов, выходы первого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами первой группы пятого и шестого блоков формирования внутригрупповых сигналов генерации и транзита и входами генерации и транзита второго блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса второго разряда блока формирования внутригрупповых переносов, выходы второго блока формирования внутригрупповых сигналов генерации и транзита переноса соединены соответственно с входами генерации и транзита второй группы шестого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы третьего блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами генерации и транзита первой группы седьмого и восьмого блоков формирования внутригрупповых сигналов генерации и транзита переноса и с входами генерации и транзита второй группы десятого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы четвертого блока формирования внутригрупповых сигналов генерации и транзита соединены соответственно с входами генерации и транзита второй группы восьмого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы пятого блока формирования внутригрупповых сигналов генерации и транзита соединены соответственно с входами генерации и транзита третьего блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса третьего разряда блока формирования внутригрупповых переносов, выходы шестого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами генерации и транзита четвертого блока формирования ускоренного переноса, с входами генерации и транзита первой группы девятого, десятого и одиннадцатого блоков формирования внутригрупповых сигналов генерации и транзита переноса и являются выходными сигналами генерации и транзита первой группы блока формирования внутригрупповых переносов, выход четвертого блока формирования ускоренного переноса является выходным сигналом ускоренного переноса четвертого разряда блока формирования внутригрупповых переносов, выходы седьмого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы одиннадцатого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы восьмого блока формирования внутригрупповых сигналов генерации и транзита переноса являются выходными сигналами генерации и транзита второй группы блока формирования внутригрупповых переносов, выходы девятого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами пятого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса пятого разряда блока формирования внутригрупповых переносов, выходы десятого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами шестого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса шестого разряда блока формирования внутригрупповых переносов, выходы одиннадцатого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами седьмого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса седьмого разряда блока формирования внутригрупповых переносов, входы переносов всех блоков формирования ускоренного переноса, входящих в блок формирования внутригрупповых переносов, соединены с входом переноса блока формирования внутригрупповых переносов, входы генерации и транзита первой группы двенадцатого блока формирования внутригрупповых сигналов генерации и транзита являются входами генерации и транзита первой группы блока формирования межгруппового переноса, которые соответственно соединены с выходными сигналами генерации и транзита первой группы блока формирования внутригрупповых переносов, входы генерации и транзита второй группы двенадцатого блока формирования внутригрупповых сигналов генерации и транзита являются входами генерации и транзита второй группы блока формирования межгруппового переноса, которые соответственно соединены с выходными сигналами генерации и транзита второй группы блока формирования внутригрупповых переносов, вход переноса восьмого блока формирования ускоренного переноса является входом переноса блока формирования межгруппового переноса, выходы двенадцатого блока формирования внутригрупповых сигналов генерации и транзита соединены с соответствующими входами восьмого блока формирования ускоренного переноса, выход которого является выходом межгруппового переноса группы.

Текст

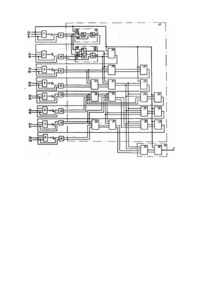

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении быстродействующих многоразрядных параллельных сумматоров в устройствах цифровой обработки сигналов. Известно устройство для формирования сквозного переноса в параллельном сумматоре [1]. Каждый 1-й разряд устройства содержит два элемента И, 1 элементов ИЛИ и (1-1) элементов НЕ. Недостатками устройства являются: большой расход оборудования при использовании его в многоразрядном сумматоре; нерегулярность структуры, неоднородность связей между разрядами, затрудняющие реализацию устройства на однотипных узлах, в том числе на БИС; отсутствие организации группового переноса, что приводит к возрастанию задержки в цепи сквозного переноса с увеличением номера разряда. Ближайшим к заявляемому по своей технической сущности является комбинационный двоичный сумматор [2], содержащий m групп, причем каждая группа сумматора содержит n блоков формирования сигналов возникновения и запрета переносов, блок формирования внутригрупповых переносов, n блоков формирования суммы, а также блок формирования межгрупповых переносов. Недостатками данного устройства являются нерегулярность структуры блока формирования межгрупповых переносов и ориентированность устройства на применение ИС определенного типа, например, выполненных по И 2Л-технологии, а именно: применение логических элементов, имеющих несколько логически равнозначных вы ходов, что обеспечивает возможность широкого разветвления выходного сигнала без промежуточных каскадов логики для его усиления; применение элементов, допускающих объединение по выходу для реализации псевдоэлементов "монтажное ИЛИ", что уменьшает число каскадов логики в цели формирования сигнала межгруппового переноса. Отсутствие указанных элементов снижает быстродействие устройства и ограничивает его область применения. Например, при критических требованиях к потребляемой мощности предпочтение имеет применение ИС, выполненных по КМОП-те хнологии. Особое внимание при этом необходимо уделить схемотехническому решению узлов, к которым предъявляются повышенные требования по быстродействию, с учетом особенностей КМОП ИС (зависимость задержки переключения логического элемента от коэффициента нагрузки, малая нагрузочная способность и большая задержка переключения многовходовых элементов). В полной мере это относится к суммирующим устройствам, так как, например, в устройствах цифровой фильтрации для сжатия сигналов операции сложения составляют около 60%. В основу изобретения поставлена задача усовершенствования комбинационного двоичного сумматора путем повышения быстродействия за счет изменения взаимосвязей устройства. При реализации устройства-прототипа и предлагаемого устройства на элементах одного типа, например, выполненных по КМОП-те хнологии, предлагаемое устройство обеспечивает выигрыш в быстродействии примерно в 1,5 раза. В конкретном случае изобретение будет использовано в арифметическом блоке спецвычислителя обработки сигналов РЛ С самолета, которая предназначена для использования природных ресурсов. В указанном арифметическом блоке 54 БИС, при проектировании которых использовано данное изобретение. Повышение быстродействия одной БИС приводит к значительному повышению производительности спецвычислителя в целом, производящем параллельную обработку больших массивов информации. Поставленная задача решается тем, что в комбинационном двоичном сумматоре, содержащем m групп (m1,...,n), причем каждая группа содержит восемь одноразрядных комбинационных двоичных сумматоров, восемь блоков формирования разрядных сигналов генерации и транзита переноса, блок формирования внутригрупповых переносов, а также блок формирования межгруппового переноса, причем входы блоков формирования разрядных сигналов генерации и транзита переноса соединены с входными сигналами слагаемых соответствующи х одноразрядных сумматоров, выходы блоков формирования разрядных сигналов генерации и транзита переноса соединены с соответствующими входами соответствующи х разрядов блока формирования внутригрупповых переносов, входной перенос группы соединен с входом переноса первого одноразрядного сумматора, с входом переноса блока формирования внутригрупповых переносов и с входом переноса блока формирования межгруппового переноса, входы переносов одноразрядных сумматоров, начиная со второго, соединены с выходами ускоренных переносов соответствующих разрядов блока формирования внутригрупповых переносов, выходы одноразрядных сумматоров соединены с соответствующими выходными шинами суммы сумматора, блок формирования внутригрупповых переносов содержит одиннадцать блоков формирования внутригрупповых сигналов генерации и транзита переноса и семь блоков формирования ускоренного переноса. блок формирования межгруппового переноса содержит один блок формирования внутригрупповых сигналов генерации и транзита переноса и один блок формирования ускоренного переноса, в то время как каждый блок формирования ускоренного переноса содержит один элемент 2И и один элемент 2ИЛИ, причем первый вход элемента 2И соединен с входным сигналом транзита блока формирования ускоренного переноса, второй вход элемента 2И соединен с входным сигналом переноса блока формирования ускоренного переноса, первый вход элемента 2ИЛИ соединен с входным сигналом генерации блока формирования ускоренного переноса, выход элемента 2И соединен с вторым входом элемента 2ИЛИ, выход которого является выходным сигналом ускоренного переноса блока формирования ускоренного переноса, а каждый блок формирования внутригрупповых сигналов генерации и транзита переноса содержит два элемента 2И и один элемент 2ИЛИ, причем первый вход первого элемента 2И соединен с входным сигналом транзита первой группы входов блока формирования внутригрупповых сигналов генерации и транзита переноса, второй вход первого элемента 2И соединен с первым входом второго элемента 2 И и соединен с входным сигналом транзита второй группы входов блока формирования внутригрупповых сигналов генерации и транзита, выход первого элемента 2И является выходным сигналом транзита блока формирования внутригрупповых сигналов генерации и транзита переноса, второй вход второго элемента 2И соединен с входным сигналом генерации первой группы входов блока формирования внутригр упповых сигналов генерации и транзита переноса, первый вход элемента 2ИЛИ соединен с входным сигналом генерации второй группы входов блока формирования внутригрупповых сигналов генерации и транзита переноса, выход второго элемента 2 И соединен с вторым входом элемента 2ИЛИ, выход которого является выходным сигналом генерации блока формирования внутригрупповых сигналов генерации и транзита, причем входы генерации и транзита первого блока формирования ускоренного переноса соединены с соответствующими входами первой группы первого блока формирования внутригрупповых сигналов генерации и транзита и являются входами генерации и транзита первого разряда блока формирования внутригрупповых переносов, выход первого блока формирования ускоренного переноса является выходом сигнала ускоренного переноса первого разряда блока формирования внутригрупповых переносов, входы генерации и транзита второй группы первого, второго, третьего и четвертого блоков формирования внутригрупповых сигналов генерации и транзита переноса являются входами генерации и транзита соответственно второго, четвертого, шестого и восьмого разрядов блока формирования внутригрупповых переносов, входы генерации и транзита первой группы второго блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы пятого блока формирования внутригрупповых сигналов генерации и транзита переноса и являются входами генерации и транзита третьего разряда блока формирования внутригрупповых переносов, входы генерации и транзита первой группы третьего блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы девятого блока формирования внутригрупповых сигналов генерации и транзита переноса и являются входами генерации и транзита пятого разряда блока формирования внутригрупповых переносов, входы генерации и транзита первой группы четвертого блока формирования внутригрупповых сигналов генерации и транзита соединены с соответствующими входами второй группы седьмого блока формирования внутригрупповых сигналов генерации и транзита и являются входами генерации и транзита седьмого разряда блока формирования внутригрупповых переносов, выходы первого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами первой группы пятого и шестого блоков формирования внутригрупповых сигналов генерации и транзита и входами генерации и транзита второго блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса второго разряда блока формирования внутригрупповых переносов, выходы второго блока формирования внутригр упповых сигналов генерации и транзита переноса соединены соответственно с входами генерации и транзита второй группы шестого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы третьего блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами генерации и транзита первой группы седьмого и восьмого блоков формирования внутригрупповых сигналов генерации и транзита переноса и с входами генерации и транзита второй группы десятого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы четвертого блока формирования внутригр упповых сигналов генерации и транзита соединены соответственно с входами генерации и транзита второй группы восьмого' блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы пятого блока формирования внутригрупповых сигналов генерации и транзита соединены соответственно с входами генерации и транзита третьего блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса третьего разряда блока формирования внутригрупповых переносов, выходы шестого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами генерации и транзита четвертого блока формирования ускоренного переноса, с входами генерации и транзита первой группы девятого, десятого и одиннадцатого блоков формирования внутригрупповых сигналов генерации и транзита переноса и являются выходными сигналами генерации и транзита первой группы блока формирования внутригрупповых переносов, выход четвертого блока формирования ускоренного переноса является выходным сигналом ускоренного переноса четвертого разряда блока формирования внутригрупповых переносов, выходы седьмого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами второй группы одиннадцатого блока формирования внутригрупповых сигналов генерации и транзита переноса, выходы восьмого блока формирования внутригрупповых сигналов генерации и транзита переноса являются выходными сигналами генерации и транзита второй группы блока формирования внутригрупповых переносов, выходы девятого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами пятого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса пятого разряда блока формирования внутригрупповых переносов, выходы десятого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами шестого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса шестого разряда блока формирования внутригрупповых переносов, выходы одиннадцатого блока формирования внутригрупповых сигналов генерации и транзита переноса соединены с соответствующими входами седьмого блока формирования ускоренного переноса, выход которого является выходным сигналом ускоренного переноса седьмого разряда блока формирования внутригрупповых переносов, входы переносов всех блоков формирования ускоренного переноса, входящих в блок формирования внутригрупповых переносов, соединены с входом переноса блока формирования внутригрупповых переносов, входы генерации и транзита первой группы двенадцатого блока формирования внутригрупповых сигналов генерации и транзита являются входами генерации и транзита первой группы блока формирования межгруппового переноса, которые соответственно соединены с выходными сигналами генерации и транзита первой группы блока формирования внутри* групповых переносов, входы генерации и транзита второй группы двенадцатого Блока формирования внутригрупповых сигналов генерации и транзита являются входами генерации и транзита второй группы блока формирования межгруппового переноса, которые соответственно соединены с выходными сигналами генерации и транзита второй группы блока формирования внутригрупповых переносов, вход переноса восьмого блока формирования ускоренного переноса является входом переноса блока формирования межгруппового переноса, выходы двенадцатого блока формирования внутригрупповых сигналов генерации и транзита соединены с соответствующими входами восьмого блока формирования ускоренного переноса, выход которого является выходом межгруппового переноса группы. Изменения во взаимосвязях элементов сумматора позволяют повысить его быстродействие. Предлагаемое устройство в отличие от устройства-прототипа позволяет формировать внутригрупповые и межгрупповые переносы на однотипных двухвходовы х элементах, уменьшить коэффициенты нагрузки для блоков формирования разрядных сигналов генерации и транзита, исключить промежуточные уровни логики при выработке ускоренных переносов, сэкономить оборудование, так как при выработке внутригр упповых и межгруппового переносов используются одни и те же элементы. На чертеже представлена функциональная схема предлагаемого устройства. Сумматор содержит m (m=1,...,n) гр упп по восемь разрядов в каждой. Каждая группа содержит восемь одноразрядных комбинационных двоичных сумматоров 1-8, восемь блоков формирования разрядных сигналов генерации и транзита переноса 9-16, блок формирования внутригрупповых переносов 17, а также блок формирования межгруппового переноса 18. Блок 17 содержит семь блоков формирования ускоренного переноса 19-25 и одиннадцать блоков формирования внутригр упповых сигналов генерации и транзита 26-36. Блок 18 содержит один блок формирования внутригрупповых сигналов генерации и транзита 37 и один блок формирования ускоренного переноса 38. Каждый из блоков формирования ускоренного переноса 19-25,38 состоит из одного элемента 2И 39 и одного элемента 2ИЛИ 40. Каждый из блоков формирования внутригрупповых сигналов генерации и транзита 26-37 содержит два элемента 2И 41, 42 и один элемент 2ИЛИ 43. В каждом из блоков 19-25, 38 первый вход элемента 39 соединен с входным сигналом транзита 45 блока, второй вход элемента 39 соединен с входным сигналом переноса 44 блока, первый вход элемента 40 соединен с входным сигналом генерации 46 блока, выход элемента 39 соединен с вторым входом элемента 40, выход которого является выходным сигналом ускоренного переноса 47 блока. В каждом из блоков 26-36, 37 первый вход элемента 41 соединен с входным сигналом транзита 48 первой группы входов блока, второй вход элемента 41 соединен с первым входом элемента 42 и соединен с входным сигналом транзита второй группы входов 50 блока, выход элемента 41 является выходным сигналом транзита 52 блока, второй вход элемента 42 соединен с входным сигналом генерации первой группы входов 49 блока, первый вход элемента 43 соединен с входным сигналом генерации второй группы 51 блока, выход элемента 42 соединен с вторым входом элемента 43, выход которого является выходным сигналом генерации 53 блока. Входы блоков 9-16 соединены с входными шинами слагаемых a1, b1,...,a 8, b8 соответствующи х одноразрядных сумматоров 1-8, выходы блоков 9-16 соединены с входами генерации и транзита соответствующи х разрядов блока 17, входной перенос группы С о соединен с входом переноса сумматора 1, с входом переноса блока 17 и с входом переноса блока 18. Входы переноса сумматоров 2-8 соединены с выходами ускоренных переносов соответствующи х разрядов блока 17. Выходы сумматоров 1-8 соединены с соответствующими выходными шинами суммы группы S1-S8. Входы генерации и транзита блока 19 соединейы с соответствующими входами первой группы блока 26 и являются входами генерации и транзита первого разряда блока 17. Выход блока 19 является выходом сигнала ускоренного переноса первого разряда блока 17. Входы генерации и транзита второй группы блоков 26, 27, 28, 29 являются соответствующими входами генерации и транзита соответственно второго, четвертого, шестого и восьмого разрядов блока 17. Входы генерации и транзита первой группы блока 27 соединены с соответствующими входами второй группы блока 30 и являются входами генерации и транзита третьего разряда блока 17. Входы генерации и транзита первой группы блока 28 соединены с соответствующими входами второй группы блока 34 и являются входами генерации и транзита пятого разряда блока 17. Входы генерации и транзита первой группы блока 29 соединены с соответствующими входами второй группы блока 32 и являются входами генерации и транзита седьмого разряда блока 17. Выходы блока 26 соединены с соответствующими входами первой группы блоков 30, 31 и входами генерации и транзита блока 20, выход которого является выходным сигналом ускоренного переноса второго разряда блока 17. Выходы блока 27 соединены соответственно с входами генерации и транзита второй группы блока 31. Выходы блока 28 соединены с соответствующими входами генерации итранзита первой группы блоков 32 и 33 и с входами генерации и транзита второй группы блока 35. Выходы блока 29 соединены соответственно с входами генерации и транзита второй группы блока 33. Выходы блока 30 соединены соответственно с входами генерации и транзита блока 21, выход которого является выходным сигналом ускоренного переноса третьего разряда блока 17. Выходы блока 31 соединены с соответствующими входами генерации и транзита блока 22, с входами генерации и транзита первой группы блоков 34, 35, 36 и являются выходными сигналами генерации и транзита первой группы блока 17. Выход блока 22 является выходным сигналом ускоренного переноса четвертого разряда блока 17. Выходы блока 32 соединены с соответствующими входами второй группы блока 26. Выходы блока 33 являются выходными сигналами генерации и транзита второй группы блока 17. Выходы блока 34 соединены с соответствующими входами блока 23, выход которого является выходным сигналом ускоренного переноса пятого разряда блоку 17. Выходы блока 35 соединены с соответствующими входами блока 24, выход которого является выходным сигналом ускоренного переноса шестого разряда блока 17. Выходы блока 36 соединены с соответствующими входами блока 25, выход которого является выходным сигналом ускоренного переноса седьмого разряда блока 17. Входы переносов блоков 19-25 соединены с входом переноса блока 17. Входы генерации и транзита первой группы блока 37 являются входами генерации и транзита первой группы блока 38, которые соответственно соединены с выходными сигналами генерации и транзита первой группы блока 17. Входы генерации и транзита второй группы блока 37 являются входами генерации и транзита второй группы блока 38, которые соответственно соединены с выходными сигналами генерации и транзита второй группы блока 17. Вход переноса блока 38 является входом переноса блока 18. Выходы блока 37 соединены с соответствующими входами блока 38, выход которого является выходом межгруппового переноса группы. Устройство реализовано в полузаказной КМОП БИС арифметического процессора, предназначенной для использования в спецвычислителе для цифровой обработки сигналов. Максимальное время суммирования 16разрядного параллельного двоичного сумматора составляет менее 180 не при задержке базового одноразрядного сумматора 30 не и базового двухвходового логического элемента И, ИЛИ - 15 не. Каждая отдельная группа сумматора работает следующим образом. По шинам слагаемых на входы блоков 9 16 поступают соответствующие разряды слагаемых. Каждый из блоков 9-16 вырабатывает разрядные сигналы генерации и транзита переноса согласно выражениям где I=1...„8 aI, bI - входные операнды разряда; gI, pI - соотве тственно, сигналы генерации и транзита переноса I-го разряда. Разрядные сигналы генерации и транзита поступают на соответствующие входы блока 17, где формируются параллельные (одновременные) переносы для каждого из одноразрядных сумматоров 2-8. Известно, что для каждого 1-го разряда должно выполняться соотношение для выходного переноса: где сI - выходной перенос из I-го разряда; cо - входной перенос младшего (первого) разряда. Для двух соседних разрядов выражение (2) имеет вид: где n=1,..,4; c2n - вы ходной перенос из старшего 2п-го разряда; c2n-2 - входной перенос младшего (2п-1)-го разряда; р2n-1, g2n-1 - соответственно сигналы транзита и генерации переноса младшего разряда: р2n, g2n - соответственно сигналы транзита и генерации переносе старшего разряда. На основании (3) определится выражение для результирующи х сигналов генерации и транзита переноса двух разрядов: Из выражений (4), (5) следует, что при организации цепи ускоренного переноса два соседних разряда эквивалентны по логике одному разряду с сигналами генерации и транзита, соответствующими (4). Блок 17 организован четырьмя каскадами блоков формирования ускоренного переноса 19-25 и формирования внутригр упповых сигналов генерации и транзита 26-36, что отражено на чертеже. Каждый из блоков 26-37 осуществляет выработку результирующи х сигналов генерации и транзита согласно (4), причем сигналы генерации и транзита младшего разряда каждой пары разрядов поступают на соответствующие входы первой группы соответствующего блока, а сигналы генерации и транзита старшего разряда - на входы второй группы. Входными сигналами генерации и транзита блоков 26-36 служат выходные сигналы соответствующи х блоков 9-16 и выходные сигналы соответствующих блоков 26-36 предыдущи х каскадов в качестве эквивалентной замены определенного числа разрядов сумматора. Каждый из блоков 19-25, 38 вырабатывает сигнал ускоренного переноса согласно (5). На входы генерации и транзита каждого блока поступают результирующие сигналы генерации и транзита всех разрядов, предшествующи х разряду, для которого формируется ускоренный перенос в данном блоке. В блоке 18 вырабатываются результирующие сигналы генерации и транзита всей группы и межгрупповой перенос. Формирование межгруппового переноса происходит следующим образом: Подставляя выражения (6), (7) в (5), приходим к выражению (2), что подтверждает работоспособность устройства. В первой группе сумматора с возрастанием номера разряда задержка в цепи формирования ускоренного переноса возрастает. Для второй и последующи х гр упп перенос, в первый разряд - это выходной перенос предыдущей гр уппы, а перенос во второй - восьмой разряды и выходной перенос группы сформируются через время, равное задержке блока формирования ускоренного переноса 38, т.к. сигналы всех блоков формирования разрядных сигналов генерации и транзита 9-16 и всех блоков формирования внутригрупповых сигналов генерации и транзита 26-37 для второй и последующи х гр упп уже выработаны. Таким образом, для каждого разряда второй и последующей гр упп предложенного сумматора организован параллельный (одновременный) перенос из предыдущей группы, соответственно одновременно в разрядах в пределах группы, начиная со второй, формируются и результирующие значение сумм. Комбинационный двоичный сумматор может быть использован при построении быстродействующи х устройств на элементах, выполненных по МОП, КМОП, БИКМОП-те хнологиям. Наиболее актуальным является использование изобретения при проектировании новых БИС, например, на ПО "Кристалл", г. Киев, причем без изменений технологического оборудования.

ДивитисяДодаткова інформація

Назва патенту англійськоюCombinatorial binary adder

Автори англійськоюVasina Olena Mykolaivna, Kravtsov Volodymyr Ruvimovych

Назва патенту російськоюКомбинационный двоичный сумматор

Автори російськоюВасина Елена Николаевна, Кравцов Владимир Рувимович

МПК / Мітки

МПК: G06F 7/50

Мітки: додавач, двійковий, комбінаційний

Код посилання

<a href="https://ua.patents.su/6-1452-kombinacijjnijj-dvijjkovijj-dodavach.html" target="_blank" rel="follow" title="База патентів України">Комбінаційний двійковий додавач</a>

Попередній патент: Метод регулювання продуктивності параллельно працюючих агрегатів синтезу аміаку

Наступний патент: Пристрій для здрібнення твердих матеріалів

Випадковий патент: Накладний вихорострумовий перетворювач для неруйнівного контролю