Спосіб аналого-цифрового перетворювання і пристрій для його виконання

Номер патенту: 1526

Опубліковано: 25.07.1994

Автори: Шевченко Валерій Андрійович, Скопюк Михайло Іванович, Сітько Сергій Пантелеймонович, Іскренко Микола Якович, Андреєв Євген Олександрович

Формула / Реферат

1. Способ аналого-цифрового преобразования, основанный на последовательном выполнении циклов интегрирования входного сигнала в течение заданного интервала времени, в каждом из которых формируют сигнал, пропорциональный интегралу от входного сигнала, начиная от первоначального уровня сигнала, меньшего нижнего заданного порогового уровня, осуществляют сравнение сформированного сигнала с заданным нижним и верхним пороговыми уровнями, формирование информационного интервала времени с длительностью, определяемой моментами равенства сформированного сигнала соответственно нижнему и верхнему пороговым уровням, и заполнение информационного интервала времени импульсами заданной частоты, восстанавливают первоначальный уровень сигнала, после чего осуществляют подсчет количества импульсов заданной частоты для всех информационных интервалов времени и определяют его усредненное значение по числу циклов интегрирования, обратную величину которого используют при формировании выходного кода, отличающийся тем, что, с целью повышения чувствительности и точности преобразования, на первом цикле интегрирования входного сигнала верхний пороговый уровень формируют путем преобразования текущего числа импульсов заданной частоты заполнения первого информационного интервала в текущий инверсный код с одновременным цифро-аналоговым преобразованием инверсного кода в аналоговый сигнал и в момент окончания первого информационного интервала запоминают значение текущего инверсного кода, а соответствующий ему аналоговый сигнал используют в качестве верхнего порогового уровня на последующих циклах интегрирования, а до формирования выходного кода усредненное значение количества подсчитанных импульсов заданной частоты уменьшают кратно запомненному в первом цикле интегрирования значению текущего инверсного кода.

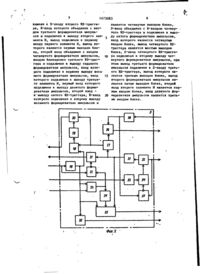

2. Устройство для аналого-цифрового преобразования, содержащее интегратор, информационный вход которого является входной шиной преобразуемого сигнала, управляющий вход подключен к первому выходу блока управления, выход подключен к первым входам первого и второго компараторов, второй вход первого компаратора является входной шиной нижнего порога сравнения, выходы первого и второго компараторов подключены соответственно к первому и второму входам блока управления, третий вход которого является управляющей входной шиной, цифровой ключ, информационный вход которого подключен к выходу генератора тактовых импульсов, выход подключен к счетному входу первого счетчика, вход обнуления которого объединен с входом обнуления второго счетчика, выходы подключены к соответствующим информационным входам накопительного регистра, выходы которого подключены к соответствующим первым информационным входам блока деления, управляющий вход объединен со счетным входом второго счетчика, выходы которого подключены к соответствующим вторым информационным входам блока деления, отличающееся тем, что, с целью повышения чувствительности и точности преобразования, в него введены блок умножения, регистр и цифро-аналоговый преобразователь, выход которого подключен к второму входу второго компаратора, входы объединены с соответствующими первыми информационными входами блока умножения и подключены к соответствующим инверсным выходам регистра, информационные входы которого объединены с соответствующими информационными входами накопительного регистра, управляющий вход подключен к второму выходу блока управления, третий выход которого подключен к управляющему входу цифрового ключа, четвертый выход - к входу обнуления первого счетчика, пятый выход - к счетному выходу второго счетчика, шестой выход - к управляющему входу блока деления, информационные выходы которого подключены к соответствующим вторым информационным входам блока умножения, управляющий вход которого подключен к выходу окончания вычислений блока деления, выход окончания вычислений подключен к четвертому входу блока управления, информационные выходы являются шиной выходного кода.

3. Устройство по п.2, отличающееся тем, что блок управления выполнен на первом - пятом RS-триггерах, первом - девятом формирователях импульсов, первом, втором и третьем элементах И, элементе ИЛИ, выход которого является вторым выходом блока, первый вход объединен с S-входом первого RS-триггера и подключен к первому выходу четвертого формирователя импульсов, второй вход подключен к выходу шестого формирователя импульсов, вход которого подключен к выходу первого RS-триггера, R-вход которого объединен с первым входом второго элемента И, R-входом третьего RS-триггера, входом второго формирователя импульсов и подключен к выходу первого формирователя импульсов, вход которого является вторым входом блока и подключен к S-входу второго RS-триггера, R-вход которого объединен с входом третьего формирователя импульсов и подключен к выходу второго элемента И, выход подключен к первому входу первого элемента И, выход которого является первым выходом блока, второй вход объединен с входом четвертого формирователя импульсов, входом блокировки третьего RS-триггера и подключен к выходу седьмого формирователя импульсов, вход которого подключен к первому выходу восьмого формирователя импульсов, вход которого подключен к выходу третьего элемента И, первый вход которого подключен к выходу девятого формирователя импульсов, второй вход - к выходу пятого RS-триггера, R-вход которого подключен к второму выходу восьмого формирователя импульсов и является четвертым выходом блока, S-вход объединен с R-входом четвертого RS-триггера и подключен к выходу пятого формирователя импульсов, вход которого является четвертым входом блока, выход четвертого RS-тригтера является шестым выходом блока, S-вход четвертого RS-триггера подключен к второму выходу четвертого формирователя импульсов, при этом выход третьего формирователя импульсов подключен к S-входу третьего RS-триггера, выход которого является третьим выходом блока, выход второго формирователя импульсов является пятым выходом блока, второй вход второго элемента И является первым входом блока, вход девятого формирователя импульсов является третьим входом блока.

Текст

союз советских СОиИАЛИСТЖЕСНИХ РЕСПУБЛИК -SU.» 1473083 А1 (50 4 Н 03 М '1/52 ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ ПРИ ГННТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4039038/24-24; 4039038/24-24 (22) 07.02,86 (46) 15.04.89. Бюл. й 14 > (75) Е.А.Андреев, Н.Я.Искренно, С.П.Ситько, М.И.Скошок И В.А.Шевченко (53) 681.325(088.8) (56) Авторское свидетельство СССР » ІО754О5, кл. Н 03 М 1/52, 1982. Авторское свидетельство СССР * 959276, кл. Н 03 М 1/52, 1981. (54) СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматизации научных экспериментов. Цель - повышение чувствительности и точности преобразования. Сущность способа заключается в многократном . за время измерения преобразовании входного сигнала во временной интер вал и нахождении его среднего значения, причем отличительным признаком является автоматический выбор верхнего порога сравнения при этом преобразовании в зависимости от величины входного сигнала. Устройство для аналого-цифрового преобразования содержит интегратор 1, блок 2 умножения, первый и второй компараторы 3, 4, блок 5 управления, генератор 6 тактовых импульсов, цифровой ключ 7, первый и второй счетчики 8, 9, накопительный регистр 10, цифроаналого-ї ' • вый (ЦАП) преобразователь 11, регистр 12, блок 13 деления, управляющую входную пику 14, входную шину 15 преобразуемого сигнала, входную шину 16 нижнего порога сравнения, выходную шину 17. При выполнении ЦАП 1I функциональным устройство может быть использовано в качестве аналого-цифрового преобразователя с не* линейной шкалой преобразования, 2 с, и 1 э.п. ф-лы, 2 ил. СО О 00 •ut. і 1 1473083 Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования аналоговых сигналов в цифровые, например сигналов, генерируемых детектором под действием рентгеновского излучения в ядерной радиоэлектронике. Цель изобретения - повышение чувствительности и точности аналого-циф- 10 рового преобразования. На фиг.1 приведена функциональная схема устройства для аналого-циф-рового преобразования; на фиг.2 - ' схема блока управления. 15 Устройство, реализующее способ аналого-цифрового преобразования^работает следующим образом. В исходном состоянии сигналом с первого выхода блока 5 управления интегратор 1 ,заблокирован, напряжение на его выходе удерживается на уровне ниже порога срабатывания первого компаратора 3, задаваемого сигналом на входной шине 16, первый и второй счетчики 8 и 9 находятся в нулевом состоянии. Код с выхода первого счетчика 8 подается на вход регистра 12, который аключен в режим записи входного кода. Инверсный двоичный код с выхода регистра 12 подается на ЦАП 11, при Устройство для аналого-цифрового помощи которого формируют выходное преобразования (фиг.1) содержит иннапряжение в соответствии с формутегратор I, блок 2 умножения, первый 20 лой и второй компараторы 3 и 4, блок 5 управления, генератор 6 тактовых импульсов, цифровой ключ 7, первый и где [N~J код на выходе первого второй счетчики 8 и 9, накопительный счетчика 8 в двоичном регистр 10, цифроаналоговый преобра25 представлении; зователь (ЦАП) II, регистр 12, блок инверсный код на выходе 13 деления, управляющую входную ширегистра 12 в двоичном п ну 14, входную шину 15 преобразуемопредставлении (в общем го сигнала, входную шину 16 нижнего порогового сравнения, выходную шину случае); 17. . 30 ЛЬ* - цена одного кванта цнфроаналогового преобразоБлок управления (фиг.2) содержит вания. . первый RS-триггер 18, первый и вто.Напряжение на выходе ЦАП 11 в рой формирователи 19 и 20 импульсов, первый элемент И 21, вто'рой RS-триг- • исходном состоянии принимает задангер 22, второй элемент И 23, третий 35 ное максимальное значение. По сигналу, поступающему по шине 14, блок 5 формирователь 24 импульсов, третий управления разрешает работу интеграи четвертый RS-триггеры 25 и 26, четтора 1 и входной ток, поступающий по вертый, пятый и шестой формирователи шине 15, Начинает заряжать емкость 27, 28 и 29 импульсов, элемент ИЛИ 30, седьмой, восьмой и девятый фор- 40 С интегратора 1. Напряжение на выходе интегратора 1 меняется в соотмировател и 31, 32 и 33 импульсов, ветствии с формулой третий элемент И 34, пятый RS-триггер 35. Способ аналого-цифрового преобра- 45 зования основан на использовании свойства расширения динамического диапазона аналого-цифрового преобразования сигналов при повыленни разрядности преобразования, обусловлен50 ного зависимостью разрядности преобразования от числа уровней квантования преобразуемого сигнала. Согласно предлагаемому способу осуществляют заданную разрядность преобразова- „ ния сигналов с нулевого нижнего значения динамического диапазона без снижения чувствительности и точности преобразования. и. где t - текущее время; і 6 к * входной ток устройства. Увеличение напряжения на выходе интегратора 1 приводит к тому, что в некоторый момент времени ti срабатывает первый компаратор 3. В этот момент времени разблокируется цифровой ключ 7 и сигналы с генератора 6 тактовых импульсов начинают поступать на счетный вход первого^1 счетчика 8. По мере заполнения первого счетчика 8 двоичный код на его выходе увеличивается, а инверсный код на выходе регистра 12 уменьшается. 3 1473083 Так как этот код поступает на ЦАП затем блок 2 умножения вычисляет ве11, то напряжение на его выходе стуличину пенчато уменьшается от исходного макп симального значения до которая с точностью до масштабного ~ техущее значение двоичнокоэффициента М соответствует среднего кода на выходе первому значению входного тока за время го счетчика 8 . 10 преобразования. Масштабный коэффиНапряжение на выходе интегратора циент М в случае, если напряжение 1 продолжает расти и в некоторый нижнего порога на шине 16 равно Q, момент времени и в ь п м сравняется с наравен пряжением U B f c u J t . При этом срабатывает второй компаратор 4. В этот мо- М - » П.. f - С мент времени t 2 блокируется цифровой где f - частота тактовых импульсов ключ 7, а регистр 12 переводится в генератора 6, режим запоминания значения двоичного Разрядность аналого-цифрового прецифрового кода [ N , 1 , который накопобразователя, реализующего предлвгален в первом счетчике 8 к моменту м •емый способ, увеличена на величину времени t a . При этом достигается слеN 1°82 ( N ( W O f - ii»in)t где (N^,,дующее равенство N,m;ч> - цифровой эквивалент разности между максимальной и минимальной длительностью первого цикла интегрирогде U ^ - напряжение верхнего поро- 25 вания-, что свидетельствует о повыга; шении чувствительности и точности - инверсный код на выходе преобразования. Предлагаемый способ регистра 12 в двоичном І и устройство могут быть использованы представлении. для получения нелинейных характерисИнтегратор 1 устанавливается в не- 30 . тик преобразования при выполнении ходное состояние, во второй счетчик цифро-аналогового преобразователя 9 записывается "І". функциональным с монотонной (выпукНачинается формирование следующелой или вогнутой) характеристикой го цикла интегрирования входного сигпреобразования• ] нала. На втором и последующих-циклах 3 5 'і интегрирования напряжение с выхода Ф о р м у л а и з о б р е т е н и я ЦАП 11 остается постоянным. Первый счетчик. 8 продолжает подсчитывать 1. Способ аналого-цифрового пре-• сигналы, проходящие через цифровой образования, основанный на последоключ 7, а второй счетчик 9 подечндо вательном выполнении циклов интегритывает количество полных циклов инрования входного сигнала в течение 1 тегрирования входного сигнала. Содерзаданного интервала времени, в кажжимое первого счетчика 8 по окончадом из которых формируют сигнал, пронии каждого цикла интегрирования пепорциональный интегралу от входного;' реписывается в накопительный регистр ^5 сигнала, начиная от первоначального 10. К моменту окончания времени преуровня сигнала, меньшего нижнего з а образования, определяемому сигналом данного порогового-уровня, осущест-' на шине 14, в накопительном регистре вляют сравнение сформированного сиг10 з аписа» код 2_{нД , во втором нала с заданным нижним и верхним посчетчике 9 записан код п числа пол- *0 роговыми уровнями, формирование информационного интервала времени с ных циклов интегрирования в течение длительностью, определяемой моментазаданного времени преобразования входми равенства сформированного сигнаного сигнала. ла соответственно нижнему и верхнеПо команде блока 5 управления блок 13 деления вычисляет величину 55 му пороговым уровням, и заполнение информационного интервала времени импульсами заданной частоты, восстанавливают первоначальный уровень сигнала, после чего осуществляют подгде IN^J 1473083 счет количества импульсов заданной деления, управляющий вход объединен частоты для всех информационных инсо счетным входом второго счетчика, тервалов времени и определяют его 'выходы которого подключены к соответусредненное значение по числу цик5 ствующим вторым информационным вхолов интегрирования, обратную величидам блока деления, о т л и ч а ю ну которого используют при формирощ е е с я тем, что, с целью повывании выходного кода, о т л н ч а ю шения чувствительности и точности ц и й с я тем, что, с целью повыпреобразования, в него введены блок шения чувствительности и точности 10 умножения, регистр и цифроаналогопреобразования, на первом цикле инвый преобразователь, выход которого тегрирования входного сигнала верхподключен к второму входу второго ; ний пороговый уровень формируют пукомпаратора, входы объединены с сооттем преобразования текущего числа имветствующими первыми информационными 1 пульсов заданной частоты заполнения 5 входами блока умножения и подключепервого информационного интервала в ны к соответствующим инверсным выхотекущий инверсный код с одновремендам регистра, информационные входы ным цифроаналоговым преобразованием которого объединены с соответствуюинверсного кода- в аналоговый сигнал щими информационными входами накопии в момент окончания первого инфор20 тельного регистра, управляющий вход мационного интервала запоминают знаподключен к второму выходу блока упчение текущего инверсного кода, а равления, третий выход которого подсоответствующий ему аналоговый сигключен к управляющему входу цифронал используют в качестве верхнего вого ключа» четвертый выход - к вхопорогового уровня на последующих цик- 25 д у обнуления первого счетчика, пялах интегрирования, а до формироватый выход - к счетному выходу второ*ния выходного кода усредненное знаго счетчика, шестой выход - к управчение количества подсчитанных импульляющему входу блока деления, инфорсов заданной частоты уменьшают кратмационные выходы которого подключены но запомненному в первом цикле интег- 30 к соответствующим вторым информационрирования значению текущего инверсным входам блока умножения, управного кода. . ляющий вход которого подключен к выходу окончания вычислений блока деле2 . Устройство для аналого-цифрония, выход окончания вычислений подвого преобразования, содержащее ин35 ключей к четвертому входу блока уптегратор, информационный вход которавления, информационные выходы яврого является входной шиной преобраляются шиной выходного кода. зуемого сигнала, управляющий вход 3 . Устройство по п . 2 , о т л и подключен х первому выходу блока упч а ю щ е е с я-тем, что блок управления, выход подключен к первым до равления выполнен на первом - пятом входам первого и второго компараRS-*-TpHrrepax» первом - девятом форторов, второй вход дервого компаратомирователях импульсов, первом, втора является входной шиной нижнего пором и третьем элементах И, элементе рога сравнения, выходы первого и второго крмпараторов подключены соответ- 45 ИЛИ, выход, которого является вторым выходом блока, первый вход объедиственно к первому и второму входам нен с S-входом первого KS-триггера блока управления, третий вход которои подключен к первому выходу четго является управляющей входной шивертого формирователя импульсов,втоной, цифровой ключ, информационный рой вход подключен к выходу шестого вход которого подключен к выходу г е 50 формирователя импульсов, вход котонератора тактовых импульсов, выход рого подключен к выходу первого RSподключен к счетному входу первого триггера, к*вход которого объединен счетчика, вход обнуления- которого с первым входом второго элемента И, объединен с входом обнуления второго R-входом третьего RS-триггера', вхосчетчика, выходы подключены к соот5 5 дом второго формирователя импульсов ветствующим информационным входам и подключен к выходу первого форминакопительного регистра, выходы корователя импульсов, вход которого торого подключены к соответствующим является вторым входом блока и подпервым информационным входам блока 8 1473083 ключей к S-входу второго RS-триггеявляется четвертым выходом €лока, ра, R-вход которого объединен с вхоS-вход объединен с R-входом четвер- • дом третьего формирователя импультого RS-триггера и подключен к выхосов и подключен к выходу второго эле- s ду пятого формирователя импульсов, мента И, выход подключен к первому вход которого является четвертым входу первого элемента И, выход ковходом блока, выход четвертого RSторого является первым выходом блотриггера является шестым выходок ка, второй вход объединен с входом блока, S-вход четвертого RS-триггечетвертого формирователя импульсов, 10 ра подключен к второму выходу четвходом блокировки третьего RS-тригвертого формирователя импульсов* при гера и подключен к выходу седьмого этом выход третьего формирователя формирователя импульсов, вход котоимпульсов подключен к S-входу третьрого подключен к первому выходу восьего RS-триггера, выход которого явмого формирователя импульсов, вход 15 ляется третьим выходом блока, выход которого подключен к выходу третьевторого формирователя импульсов явго элемента И, первый вход которого ляется пятым выходом блока, второй подключен к выходу девятого формивход второго элемента И является перрователя импульсов, второй вход вым входом блока, вход девятого форк" выходу пятого RS-триггера, R-вход 20 мирователя импульсов является третькоторого подключен к второму выходу им входом блока. восьмого формирователя импульсов и 5 28 ЗО * 29 1 \ 26 І \ і • • 71 IB 1—. е11 ? 21 • г 35 25 го Фиг:2 1 J

ДивитисяДодаткова інформація

Назва патенту англійськоюAd conversion method and device to realize it

Автори англійськоюAndreev Yevhen Oleksandrovych, Iskrenko Mykola Yakovych, Sitko Serhii Panteleimonovych, Skopiuk Mykhailo Ivanovych, Shevchenko Valerii Andriiovych

Назва патенту російськоюСпособ аналого-цифрового преобразования и устройство для его исполнения

Автори російськоюАндреев Евгений Александрович, Искренко Николай Яковлевич, Ситько Сергей Пантелеймонович, Скопюк Михаил Иванович, Шевченко Валерий Андреевич

МПК / Мітки

МПК: H03M 1/50

Мітки: спосіб, пристрій, аналого-цифрового, виконання, перетворювання

Код посилання

<a href="https://ua.patents.su/6-1526-sposib-analogo-cifrovogo-peretvoryuvannya-i-pristrijj-dlya-jjogo-vikonannya.html" target="_blank" rel="follow" title="База патентів України">Спосіб аналого-цифрового перетворювання і пристрій для його виконання</a>

Попередній патент: Штам azotobacter chroococum вніісм-20, призначений для виготовлення азотобактерину під овочеві культури

Наступний патент: Спосіб видобутку нафти з нафтового покладу

Випадковий патент: Льодогенератор, що використовує холодне повітря навколишнього середовища