Двотактний симетричний підсилювач струму

Номер патенту: 17239

Опубліковано: 15.09.2006

Автори: Решетнік Олександр Олександрович, Снігур Анатолій Васильович, Гарнага Володимир Анатолійович, Азаров Олексій Дмитрович, Лукащук Олександр Олександрович

Формула / Реферат

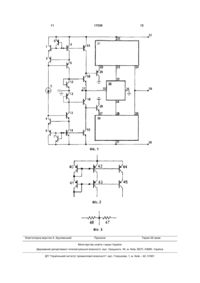

1. Двотактний симетричний підсилювач струму, який містить шість транзисторів, шини додатного та від'ємного живлення, вхідну шину, вихідну шину, шину нульового потенціалу, причому вхідну шину з'єднано з емітерами першого та другого транзисторів, бази першого та другого транзисторів з'єднано з базами і колекторами третього та четвертого транзисторів відповідно, колектори першого та другого транзисторів з'єднано з базами п'ятого та шостого транзисторів відповідно, емітери третього та четвертого транзисторів з'єднано з шиною нульового потенціалу, який відрізняється тим, що у нього введено джерело струму, дванадцять транзисторів, два відбивачі струму з двома виходами, подільник струму, причому два виходи джерела струму з'єднані з колекторами восьмого та дев'ятого, та з базами чотирнадцятого та п'ятнадцятого транзисторів відповідно, емітери восьмого та дев'ятого транзисторів з'єднано з емітерами сьомого та десятого транзисторів відповідно, бази восьмого та дев'ятого транзисторів з'єднано з емітерами чотирнадцятого та п'ятнадцятого транзисторів відповідно, і з колекторами тринадцятого та шістнадцятого транзисторів відповідно, колектори чотирнадцятого та п'ятнадцятого транзисторів з'єднано з колекторами та базами третього та четвертого транзисторів відповідно, а також з базами першого та другого транзисторів відповідно, колектори сьомого та десятого транзисторів з'єднані з шинами додатного та від'ємного живлення відповідно, бази сьомого та десятого транзисторів з'єднані з базами і колекторами одинадцятого та дванадцятого транзисторів відповідно, а також з базами тринадцятого та шістнадцятого транзисторів відповідно, а також з базами сімнадцятого та вісімнадцятого транзисторів відповідно, емітери одинадцятого, тринадцятого та сімнадцятого транзисторів з'єднані з шиною додатного живлення, емітери дванадцятого, шістнадцятого та вісімнадцятого транзисторів з'єднані з шиною від'ємного живлення, колектори сімнадцятого та вісімнадцятого транзисторів з'єднані з колекторами першого та другого транзисторів відповідно, а також з базами п'ятого та шостого транзисторів відповідно, колектори п'ятого та шостого транзисторів з'єднані з шиною нульового потенціалу, емітери п'ятого та шостого транзисторів з'єднані з входами першого та другого відбивачів струму з двома виходами відповідно, входи живлення першого та другого відбивачів струму з двома виходами з'єднано з шинами додатного та від'ємного живлення відповідно, перші виходи першого та другого відбивачів струму з двома виходами з'єднано з вихідною шиною, другі виходи першого та другого відбивачів струму з двома виходами з'єднано з першим та другим входом подільника струму відповідно, третій вхід подільника струму з'єднано з шиною нульового потенціалу, вихід подільника струму з'єднано з емітерами першого та другого транзисторів, а також з вхідною шиною.

2. Пристрій за п. 1, який відрізняється тим, що відбивач струму з двома виходами містить шість транзисторів, причому емітери дев'ятнадцятого, двадцять першого та двадцять третього транзисторів з'єднані з входом живлення відбивача струму з двома виходами, бази дев'ятнадцятого, двадцять першого та двадцять третього транзисторів об'єднані між собою а також з'єднані з колектором дев'ятнадцятого та емітером двадцятого транзисторів, колектор двадцять першого транзистора з'єднано з емітером двадцять другого транзистора, колектор двадцять третього транзистора з'єднано з емітером двадцять четвертого транзистора, бази двадцятого, двадцять другого, двадцять четвертого транзисторів об'єднані між собою а також з'єднані з колектором двадцятого транзистора та входом відбивача струму з двома виходами, колектор двадцять другого транзистора з'єднано з другим виходом відбивача струму з двома виходами, колектор двадцять четвертого транзистора з'єднано з першим виходом відбивача струму з двома виходами.

3. Пристрій за п. 1, який відрізняється тим, що подільник струму містить два резистори, причому один вивід першого резистора з'єднано з виходом подільника струму, а другий вивід першого резистора з'єднано з першим та другим входами подільника струму, а також з першим виводом другого резистора, другий вивід другого резистора з'єднано з третім входом подільника струму.

Текст

1. Двотактний симетричний підсилювач струму, який містить шість транзисторів, шини додатного та від'ємного живлення, вхідну шину, вихідну шину, шину нульового потенціалу, причому вхідну шину з'єднано з емітерами першого та другого транзисторів, бази першого та другого транзисторів з'єднано з базами і колекторами третього та четвертого транзисторів відповідно, колектори першого та другого транзисторів з'єднано з базами п'ятого та шостого транзисторів відповідно, емітери третього та четвертого транзисторів з'єднано з шиною нульового потенціалу, який відрізняється тим, що у нього введено джерело струму, дванадцять транзисторів, два відбивачі струму з двома виходами, подільник струму, причому два виходи джерела струму з'єднані з колекторами восьмого та дев'ятого, та з базами чотирнадцятого та п'ятнадцятого транзисторів відповідно, емітери восьмого та дев'ятого транзисторів з'єднано з емітерами сьомого та десятого транзисторів відповідно, бази восьмого та дев'ятого транзисторів з'єднано з емітерами чотирнадцятого та п'ятнадцятого транзисторів відповідно, і з колекторами тринадцятого та шістнадцятого транзисторів відповідно, колектори чотирнадцятого та п'ятнадцятого транзисторів з'єднано з колекторами та базами третього та четвертого транзисторів відповідно, а також з базами першого та другого транзисторів відповідно, колектори сьомого та десятого транзисторів з'єднані з шинами додатного та від'ємного живлення відповідно, бази сьомого та десятого транзисторів з'єднані з базами і колекторами одинадцятого та дванадцятого транзисторів відповідно, а також з базами тринадцятого та шістнадцятого транзисторів відповідно, а також з базами сімнадцятого та вісімнадцятого транзисторів відповідно, емітери одинадцятого, тринадцятого та сімнадцятого тран 2 (19) 1 3 17239 4 один вивід першого резистора з'єднано з виходом подільника струму, а другий вивід першого резистора з'єднано з першим та другим входами поді льника струму, а також з першим виводом другого резистора, другий вивід другого резистора з'єднано з третім входом подільника струму. Корисна модель відноситься до імпульсної техніки і може бути використана в аналого-цифрових перетворювачах і цифрових вимірювальних приладах. Відомо кероване джерело струму [Гусев В.Г., Гусев Ю.М. Электроника: Учебное пособие для вузов. - М.: Высш. школа, 1982. - 495 с., ил. Рис. 4.15 на сторінці 249.], який містить п'ятнадцять транзисторів, два діода, дві шини вхідних сигналів, шину для управління керованим джерелом струму, вихідну шину, шину нульового потенціалу, шини додатного та від'ємного живлення. Вхідний каскад зібраний по диференційній схемі на першому та другому транзисторах, бази цих транзисторів з'єднані з шинами вхідних сигналів, емітери їх об'єднані та з'єднані з керованим джерелом струму, яке виконане на третьому та четвертому транзисторах: емітери першого та другого транзисторів з'єднано з колектором третього транзистора, база якого з'єднана з колектором і базою четвертого транзистора, а також з шиною управління цим джерелом струму, емітери третього та четвертого транзисторів з'єднані з шиною від'ємного живлення. Колектор першого транзистора з'єднано з колектором п'ятого транзистора, базою дев'ятого транзистора та з анодом першого діода, база п'ятого транзистора з'єднана з базою і колектором шостого транзистора та з емітером десятого транзистора, емітери п'ятого та шостого транзисторів з'єднані з шиною додатного живлення, катод першого діода з'єднано з емітером дев'ятого транзистора та базою десятого транзистора, колектори дев'ятого та десятого транзисторів об'єднані та з'єднані з колектором дванадцятого транзистора та базою п'ятнадцятого транзистора. Колектор другого транзистора з'єднано з колектором сьомого транзистора, базою одинадцятого транзистора та з анодом другого діода, база сьомого транзистора з'єднана з базою і колектором восьмого транзистора та з емітером чотирнадцятого транзистора, емітери сьомого та восьмого транзисторів з'єднані з шиною додатного живлення, катод другого діода з'єднано з емітером одинадцятого транзистора та базою чотирнадцятого транзистора, колектори одинадцятого та чотирнадцятого транзисторів об'єднані та з'єднані з шиною виходу та з колектором п'ятнадцятого транзистора. Емітер п'ятнадцятого транзистора з'єднано з колектором та базою тринадцятого транзистора та з базою дванадцятого транзистора, емітери дванадцятого та тринадцятого транзисторів з'єднані з шиною додатного живлення. Основним недоліком цього керованого джерела струму є обмежені функціональні можливості, оскільки вхідним сигналом схеми є напруга, а також низька точність схеми через нелінійну залежність між значеннями вхідної напруги та вихідного струму. За прототип обрано двотактний підсилювач з відбивачами струму для визначення стійкої робочої точки [Push-pull amplifier with current mirrors for determining the quiescent operating point, united States Patent 3,852,678 Dec. 3, 1974], який містить шість транзисторів, два резистори, вхідну та вихідну шини, шини додатного та від'ємного живлення, шину нульового потенціалу. Вхідну шину з'єднано з емітерами першого та другого транзисторів, бази яких з'єднано з базами і колекторами третього і четвертого транзисторів відповідно, а також з першими виводами першого та другого резисторів відповідно, колектори першого та другого транзисторів з'єднано з базами п'ятого та шостого транзисторів відповідно, інші виводи першого та другого резисторів з'єднані з шинами додатного та від'ємного живлення відповідно, емітери третього та четвертого транзисторів з'єднані з шиною нульового потенціалу, емітери п'ятого та шостого транзисторів з'єднані з шинами додатного та від'ємного живлення відповідно, а їх колектори з'єднані з вихідною шиною. Недоліками прототипу є низька точність через похибку зміщення нуля, яка виникає через неідентичність параметрів п'ятого та шостого транзисторів, при цьому при нульовому вхідному сигналі складно досягнути рівності колекторних струмів п'ятого та шостого транзисторів, оскільки коефіцієнти підсилення струму β у цих транзисторів можуть значно відрізнятись. Також недоліком є обмежені функціональні можливості схеми у випадку використання резистора зворотного зв'язку, оскільки при цьому вихідним сигналом схеми вже є не струм, а напруга. В основу корисної моделі поставлено задачу створення двотактного симетричного підсилювача струму (далі - пристрій), в якому за рахунок використання способу уведення зворотного зв'язку та за рахунок введення нових елементів та зв'язків між ними зменшується як вхідний струм зміщення нуля, так і вхідна напруга зміщення нуля, що підвищує точність та дає можливість використання пристрою в АЦП з більшою швидкодією і точністю, а також у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача досягається тим, що в двотактний симетричний підсилювач струму, який містить шість транзисторів, шини додатного та від'ємного живлення, вхідну шину, вихідну шину, шину нульового потенціалу, причому вхідну шину з'єднано з емітерами першого та другого транзисторів, бази першого та другого транзисторів з'єднано з базами і колекторами третього та четвертого транзисторів відповідно, колектори першого та другого транзисторів з'єднано з базами п'ятого та шостого транзисторів відповідно, емітери третього 5 та четвертого транзисторів з'єднано з шиною нульового потенціалу, введено джерело струму, дванадцять транзисторів, два відбивачі струму з двома виходами, подільник струму, причому два виходи джерела струму з'єднані з колекторами восьмого та дев'ятого, та з базами чотирнадцятого та п'ятнадцятого транзисторів відповідно, емітери восьмого та дев'ятого транзисторів з'єднано з емітерами сьомого та десятого транзисторів відповідно, бази восьмого та дев'ятого транзисторів з'єднано з емітерами чотирнадцятого та п'ятнадцятого транзисторів відповідно, і з колекторами тринадцятого та шістнадцятого транзисторів відповідно, колектори чотирнадцятого та п'ятнадцятого транзисторів з'єднано з колекторами та базами третього та четвертого транзисторів відповідно, а також з базами першого та другого транзисторів відповідно, колектори сьомого та десятого транзисторів з'єднані з шинами додатного та від'ємного живлення відповідно, бази сьомого та десятого транзисторів з'єднані з базами і колекторами одинадцятого та дванадцятого транзисторів відповідно, а також з базами тринадцятого та шістнадцятого транзисторів відповідно, а також з базами сімнадцятого та вісімнадцятого транзисторів відповідно, емітери одинадцятого, тринадцятого та сімнадцятого транзисторів з'єднані з шиною додатного живлення, емітери дванадцятого, шістнадцятого та вісімнадцятого транзисторів з'єднані з шиною від'ємного живлення, колектори сімнадцятого та вісімнадцятого транзисторів з'єднані з колекторами першого та другого транзисторів відповідно, а також з базами п'ятого та шостого транзисторів відповідно, колектори п'ятого та шостого транзисторів з'єднані з шиною нульового потенціалу, емітери п'ятого та шостого транзисторів з'єднані з входами першого та другого відбивачів струму з двома виходами відповідно, входи живлення першого та другого відбивачів струму з двома виходами з'єднано з шинами додатного та від'ємного живлення відповідно, перші виходи першого та другого відбивачів струму з двома виходами з'єднано з вихідною шиною, другі виходи першого та другого відбивачів струму з двома виходами з'єднано з першим та другим входом подільника струму відповідно, третій вхід подільника струму з'єднано з шиною нульового потенціалу, вихід подільника струму з'єднано з емітерами першого та другого транзисторів, а також з вхідною шиною. Кожен з відбивачів струму з двома виходами містить шість транзисторів, причому емітери дев'ятнадцятого, двадцять першого та двадцять третього транзисторів з'єднані з входом живлення відбивача струму з двома виходами, бази дев'ятнадцятого, двадцять першого та двадцять третього транзисторів об'єднані між собою, а також з'єднані з колектором дев'ятнадцятого та емітером двадцятого транзисторів, колектор двадцять першого транзистора з'єднано з емітером двадцять другого транзистора, колектор двадцять третього транзистора з'єднано з емітером двадцять четвертого транзистора, бази двадцятого, двадцять другого, двадцять четвертого транзисторів об'єднані між собою а також з'єднані з колектором двадцятого транзистора та входом відбивача струму з дво 17239 6 ма виходами, колектор двадцять другого транзистора з'єднано з другим виходом відбивача струму з двома виходами, колектор двадцять четвертого транзистора з'єднано з першим виходом відбивача струму з двома виходами. Подільник струму містить два резистори, причому один вивід першого резистора з'єднано з виходом подільника струму, а другий вивід першого резистора з'єднано з першим та другим входами подільника струму, а також з першим виводом другого резистора, другий вивід другого резистора з'єднано з третім входом подільника струму. На Фіг.1 представлено принципову схему двотактного симетричного підсилювача струму, на Фіг.2 представлено принципову схему відбивача струму з двома виходами, на Фіг.3 представлено принципову схему подільника струму. Пристрій містить джерело струму 3, яке своїми виходами з'єднано з колекторами восьмого транзистора 2 та дев'ятого транзистора 4 відповідно, а також з базами чотирнадцятого транзистора 9 та п'ятнадцятого транзистора 13 відповідно, емітери восьмого транзистора 2 та дев'ятого транзистора 4 з'єднано з емітерами сьомого транзистора 1 та десятого транзистора 5 відповідно, бази восьмого транзистора 2 та дев'ятого транзистора 4 з'єднано з емітерами чотирнадцятого транзистора 9 та п'ятнадцятого транзистора 13 відповідно, а також з колекторами тринадцятого транзистора 8 та шістнадцятого транзистора 14 відповідно, бази сьомого транзистора 1 та десятого транзистора 5 з'єднано з базами та колекторами одинадцятого транзистора 6 та дванадцятого транзистора 7 відповідно, а також з базами тринадцятого транзистора 8 та шістнадцятого транзистора 14 відповідно, а також з базами сімнадцятого транзистора 15 та вісімнадцятого транзистора 19 відповідно, колектор сьомого транзистора 1, а також емітери одинадцятого транзистора 6, тринадцятого транзистора 8 та сімнадцятого транзистора 15 з'єднано з шиною додатного живлення 37, колектор десятого транзистора 5, а також емітери дванадцятого транзистора 7, шістнадцятого транзистора 14 та вісімнадцятого транзистора 19 з'єднано з шиною від'ємного живлення 39, колектори чотирнадцятого 9 та п'ятнадцятого 13 транзисторів з'єднано з колекторами та базами третього 10 та четвертого 12 транзисторів відповідно, а також з базами першого 16 та другого 18 транзисторів відповідно, емітери третього 10 та четвертого 12 транзисторів з'єднано з шиною нульового потенціалу 11, колектори сімнадцятого 15 та вісімнадцятого 19 транзисторів з'єднано з колекторами першого 16 та другого 18 транзисторів відповідно, а також з базами п'ятого 25 та шостого 26 транзисторів відповідно, емітери першого 16 та другого 18 транзисторів з'єднано з вхідною шиною 17 та виходом 32 подільника струму 36, колектори п'ятого 25 та шостого 26 транзисторів з'єднано з шиною нульового потенціалу 11, емітери п'ятого 25 та шостого 26 транзисторів з'єднано з входом 22 першого відбивача струму з двома виходами 21 та входом 27 другого відбивача струму з двома виходами 30 відповідно, вхід живлення 20 першого відбивача струму з двома виходами 21 з'єднано з шиною додатного живлен 7 ня 37, вхід живлення 31 другого відбивача струму з двома виходами 30 з'єднано з шиною від'ємного живлення 39, другий вихід 23 першого відбивача струму з двома виходами 21 з'єднано з першим входом 33 подільника струму 36, другий вихід 28 другого відбивача струму з двома виходами 30 з'єднано з другим входом 34 подільника струму 36, третій вхід 35 подільника струму 36 з'єднано з шиною нульового потенціалу 11, перший вихід 24 першого відбивача струму з двома виходами 21 та перший вихід 29 другого відбивача струму з двома виходами 30 з'єднано з вихідною шиною 38. Кожен з відбивачів струму з двома виходами 21, 30 містить шість транзисторів, причому емітери дев'ятнадцятого 40, двадцять першого 42 та двадцять третього 44 транзисторів з'єднані з входом живлення відбивача струму з двома виходами, бази дев'ятнадцятого 40, двадцять першого 42 та двадцять третього 44 транзисторів об'єднані між собою а також з'єднані з колектором дев'ятнадцятого 40 та емітером двадцятого 41 транзисторів, колектор двадцять першого транзистора 42 з'єднано з емітером двадцять другого транзистора 43, колектор двадцять третього транзистора 44 з'єднано з емітером двадцять четвертого транзистора 45, бази двадцятого 41, двадцять другого 43, двадцять четвертого 45 транзисторів об'єднані між собою а також з'єднані з колектором двадцятого транзистора 41 та входом відбивача струму з двома виходами, колектор двадцять другого транзистора 43 з'єднано з другим виходом відбивача струму з двома виходами, колектор двадцять четвертого транзистора 45 з'єднано з першим виходом відбивача струму з двома виходами. Подільник струму 36 містить два резистори, причому один вивід першого резистора 46 з'єднано з виходом подільника струму, а другий вивід першого резистора 46 з'єднано з першим та другим входами подільника струму, а також з першим виводом другого резистора 47, другий вивід другого резистора 47 з'єднано з третім входом подільника струму. Двотактний симетричний підсилювач струму працює таким чином. Нехай вхідний сигнал у вигляді струму втікає на вхідну шину 17 пристрою. Тоді другий транзистор 18 привідкривається, перший транзистор 16 призакривається. Колекторний струм другого транзистора 18 збільшується і збільшує базовий струм шостого транзистора 26, при цьому він привідкривається. Колекторний струм першого транзистора 16 зменшується, тому зменшується і струм бази п'ятого транзистора 25, що призводить до його призакривання. Збільшений емітерний струм шостого транзистора 26 подається на вхід 27 другого відбивача струму з двома виходами 30. Зменшений емітерний струм п'ятого транзистора 25 подається на вхід 22 першого відбивача струму з двома виходами 21. Перші виходи 24, 29 відбивачів струму з двома виходами 21, 30 об'єднані з вихідною шиною 38, тому з вихідної шини 38 у пристрій втікає струм, що визначається різницею емітерних струмів: шостого транзистора 26 та п'ятого транзистора 25. Другі виходи 23, 28 відбивачів струму з двома виходами 21, 30 з'єднані з першим 33 та другим 34 входами подільника 17239 8 струму 36, третій вхід 35 якого з'єднаний з шиною нульового потенціалу 11, а вихід 32 - з вхідною шиною 17 та емітерами другого транзистора 18 та першого транзистора 16, у випадку коли струм на вхідні шині 17 втікає у пристрій, подільник струму 36 частково забирає на себе цей струм. Це забезпечує від'ємний зворотній зв'язок. Нехай струм витікає з вхідної шини 17 пристрою. Тоді другий транзистор 18 призакривається, перший транзистор 16 привідкривається. Колекторний струм другого транзистора 18 зменшується і зменшує базовий струм шостого транзистора 26, при цьому він призакривається. Колекторний струм першого транзистора 16 збільшується, тому збільшується і струм бази п'ятого транзистора 25, що призводить до його привідкривання. Зменшений емітерний струм шостого транзистора 26 подається на вхід 27 другого відбивача струму з двома виходами 30. Збільшений емітерний струм п'ятого транзистора 25 подається на вхід 22 першого відбивача струму з двома виходами 21. Перші виходи 24, 29 відбивачів струму з двома виходами 21, 30 об'єднані з вихідною шиною 38, тому з пристрою у вихідну шину 38 витікає струм, що визначається різницею емітерних струмів: п'ятого транзистора 25 та шостого транзистора 11. Другі виходи 23, 28 відбивачів струму з двома виходами 21, 30 з'єднані з першим 33 та другим 34 входами подільника струму 36, третій вхід 35 якого з'єднаний з шиною нульового потенціалу 11, а вихід 32-3 вхідною шиною 17 та емітерами другого транзистора 18 та першого транзистора 16, тому у випадку коли струм на вхідні шині 17 витікає з пристрою, подільник струму 36 частково компенсує струм що витікає. Це забезпечує від'ємний зворотній зв'язок. Мінімізація похибки зміщення нуля по входу схеми у вигляді або Iвх 0 або Uвх 0 досягається таким чином. За допомогою двоярусних схем відбивачів струму, а саме побудованих на сьомому 1, одинадцятому 6, тринадцятому 8, восьмому 2, чотирнадцятому 9 транзисторах а також дванадцятому 7, десятому 5, шістнадцятому 14, дев'ятому 4, п'ятнадцятому 13 транзисторах, на третій 10 та четвертий 12 транзистори у діодному вмиканні, які є давачами струму, подаються струми відповідно І': Iк 9 1 1 p n p I n p n Ізм , а також І": Iк 13 1 1 n p n I p n p Ізм , де Iк 9 , Iк 13 - колекторні струми транзисторів 9 та 13 відповідно, Ізм - струм зміщення, який визначається джерелом струму 3. Тобто Iк 9 Iк 13 . Позначимо на Iк 13 I *зм Ізм 1 1 n p n Iк 9 p n p , струм спокою вхідного каскаду, побудованого транзисторах 16, 18 буде дорівнювати 9 17239 I *зм . Визначимо колекторні струми транзисторів 25, 10 Iспокою 26 Iк 25 та Iк 26 : Іспокою Iк 15 I * зм Іб1 I * зм Ізм / 1 Ізм 1 p n p Іспокою Iк 19 I *зм Іб 5 I *зм Ізм / 5 Ізм 1 1 n p n Iб 26 Ізм 1 n p n Iб 25 p n p Ізм n p n Ізм p n p Iк 25 Іб 25 25 Іб 25 p n p Ізм / p n p p n p Іб 26 26 Іб 26 n p n Ізм / n p n n p n Ізм , n p n Ізм , Iк 26 , p n p Ізм . Бачимо, що Ік25=Ік26=Iзм. Оскільки коефіцієнт передачі відбивачів струму дорівнює одиниці, то струми на виходах відбивачів струму з двома виходами 21, 30 дорівнюють струмам на їх входах і приблизно рівні Iзм. Оскільки струм спокою вхідних транзисторів 16, 18 дорівнює Ік9 і Ік13, то падіння напруг на базових р-n переходах Uбе16=Uбе10, a Uбе18=Uбе12. Таким чином ΔUвх мінімізується, прямуючи до нуля. Відбивачі струму з двома виходами 21, 30 працюють таким чином: струм, що витікає (втікає) зі входу призводить до падіння напруги на переході база-емітер двадцятого 41 та дев'ятнадцятого 40 транзисторів. При цьому на колекторі двадцять першого транзистора 42 формується струм, який практично дорівнює струму, що протікає через колектор дев'ятнадцятого транзистора 40, колекторний струм двадцять першого транзистора 42 втікає в емітер двадцять другого транзистора 43, включеного по каскадній схемі, і передається на колектор цього транзистора, з колектора - на другий вихід відбивача струму з двома виходами. Аналогічно на колекторі двадцять третього транзистора 44 генерується колекторний струм, який рівний колекторному струму дев'ятнадцятого транзистора 40, цей струм втікає в емітер двадцять четвертого транзистора 45, включеного по каскадній схемі, і передається на колектор цього транзистора, з колектора - на перший вихід відбивача струму з двома виходами. Подільник струму 36 працює таким чином: з других виходів 23, 28 першого 21 та другого 30 відбивачів струму з двома виходами в точці з'єднання входів 33, 34 подільника струму 36 та виходів резисторів 46, 47 отримується різницевий струм, який втікає або витікає з точки об'єднання, а саме якщо вхідний струм на вхідній шині 17 витікає з пристрою, то в точці об'єднання наявний надлишковий струм, а коли вхідний струм на вхідній шині 17 втікає у пристрій, в точку об'єднання втікає струм. Подільник струму, реалізований на резисторах 46, 47 задає, яка частина різницевого струму буде втікати (або витікати) на вихід 32, який з'єднаний з вхідною шиною 17 пристрою, а яка частина струму буде втікати (або витікати) на вихід 35, який з'єднаний з шиною нульового потенціалу 11. 11 Комп’ютерна верстка А. Крулевський 17239 Підписне 12 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюSymmetrical push-pull current amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Lukaschuk Oleksandr Oleksandrovych, Harnaha Volodymyr Anatoliiovych, Reshetnik Oleksandr Oleksandrovych

Назва патенту російськоюСимметричный двухтактныйусилитель тока

Автори російськоюАзаров Алексей Дмитриевич, Лукащук Александр Александрович, Гарнага Владимир Анатольевич, Решетник Александр Александрович

МПК / Мітки

Мітки: підсилювач, симетричний, струму, двотактний

Код посилання

<a href="https://ua.patents.su/6-17239-dvotaktnijj-simetrichnijj-pidsilyuvach-strumu.html" target="_blank" rel="follow" title="База патентів України">Двотактний симетричний підсилювач струму</a>

Попередній патент: Установка для сушіння рідких матеріалів

Наступний патент: Герметизатор устя свердловини

Випадковий патент: Завантажувальний пристрій доменної печі