Пристрій для вимірювання швидкості переміщення

Формула / Реферат

1. Устройство для измерения скорости перемещения, содержащее генератор эталонной частоты, делитель частоты и последовательно соединительные блок питания, фазовращатель, компаратор, многоканальный распределитель импульсов, многоканальный формирователь опорных импульсов, многовходовую логическую схему и блок осреднения, выход генератора эталонной частоты соединен с дополнительным входом многоканального формирователя опорных импульсов, отличающееся тем, что, с целью повышения точности измерения, в него введен формирователь импульсов стабильной амплитуды, первый и второй входы которого соединены соответственно с первым и вторым выходами многовходовой логической схемы, а выход — с входом блока осреднения, при этом выход генератора эталонной частоты соединен через делитель частоты с входом блока питания.

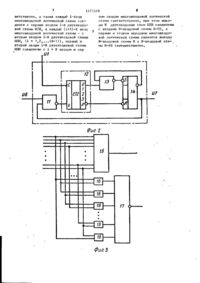

2. Устройство по п. 1, отличающееся тем, что каждый из n каналов многоканального формирователя опорных импульсов состоит из схемы ИЛИ, двоичного счетчика, схемы И и К5-триггера, причем первый вход схемы ИЛИ является информационным входом канала, второй вход соединен с прямым выходом К5-триггера и выходом канала, а выход схемы ИЛИ соединен с входом сброса двоичного счетчика, счетный вход которого является дополнительным входом канала, а первый выход соединен с первым входом схемы И, второй вход которой соединен с инверсный выходом КЗ-триггера, а выход — с установочным входом КЗ-триггера, вход сброса которого соединен с выходом переполнения двоичного счетчика.

3. Устройство по п. 1, отличающееся тем, что много-входовая логическая схема содержит N-входовую схему И, N двухвходовых схем ИЛИ и N-входовую схему И-НЕ, причем входы п каналов соединены с К входами М-входовой схемы И соответственно, а также каждый і-вход многовходовой логической схемы соединен с первым входом і-й двухвходовой схемы ИЛИ, а каждый (і+1)-й вход многовходовой логической схемы — с вторым входом і-й двухвходовой схемы ИЛИ, (і= 1, 2,... (N—1)), первый и второй входы i=N двухвходовой схемы ИЛИ соединены с і = N входом и первым входом многовходовой логической схемы соответственно, при этом выходы N двухвходовых схем ИЛИ соединены с входами М-входовой схемы И-НЕ, а первым и вторым выходами многовходо-вой логической схемы являются выходы N-входовой схемы И и N-входовой схемы И-НЕ соответственно.

Текст

Изобретение относится к измерительной технике и может найти применение в качестве датчика обратной связи по скорости в прецизионных приводах. Целью изобретения является повышение точностио Наличие в схеме устройства для измерения скорости перемещения многоканального распределителя импульсов 6, многоканального формирователя 7, многовходовой логической схемы 8 и формирователя импульсов стабильной амплитуды 9 позволяет сформировать в каждом периоде выходного сигнала фазовращателя 4 импульс с длительностью, пропорциональной модулю разности периодов питающего и выходного напряжений фазовращателя (коэффициент пропорциональности равен числу каналов), и полярностью, соответствующей знаку этой разностио На выходе блока осреднения 10 эти импульсы преобразуются в постоянное напряжение, по величине которого и судят о скорости и направлении перемещения подвижной части фазовращателяо 2 з„п.ф-лы,4 ил. .1 1571509 Изобретение относится .к измерительной технике и может быть использовано в качестве датчика обратной свя:ш по скорости в прецизионных при- , водах„ Целью изобретения является повышение точности измерения,На фиг И представлена схема устройства ДЛЯ ИЗМереНИЯ СКОРОСТИ ПЄРЄ- |0 мещения; на фиг.2 - схема одного канала многоканального формирователя опорных импульсов; на фиг.З - схема многовходовой логической схемы; на фиг,4 - временные диаграммы работы (5 для трехканального варианта устройства о Устройство для измерения скорости перемещения (фиг И ) содержит последовательно соединенные генератор 1 • 20 эталонной частоты, делитель 2 частоты, блок 3 питания, фазовращатель 4, компаратор 5, многоканальный распределитель 6 импульсов, многоканальный формирователь 7 опорных импуль_, сов, многовходовую логическую схему 8, формирователь 9 импульсов стабильной амплитуды и блок 10 соединения дополнительный вход формирователя 7 соединен также с выходом генера3 0 тора 1. Каждый канал многоканального формирователя 7 (фиг о 2) содержит схему 2ИЛИ 11, двоичный счетчик 12, схему 2И 13 и RS-триггер 14, причем первый вход схемы 2ИЛИ 11 является ^5 информационным входом канала, второй вход соединен с прямым выходом RS-триггера 14 и выходом канала, а выход схемы 2ИЛИ 11 соединен с входом сброса двоичного счетчика 12, счетныч вход которого является дополнительным входом канала, а первый выход соединен с первым входом схемы 2И 13, второй вход' которой соединен с инверсным выходом RS-триггера 14, а выход — с установочным входом этого триггера, вход сброса которого соединен с выходом переполнения счетчика 12. 1 50 Многовходозая логическая схема 8 (фиг.З) содержит N-входовую схему И 15, N двухвходовых схем ИЛИ 16 и N-вхбдовую схему И-НЕ 17, где N число каналов в устройстве. 55 Устройство работает следующим образом. Высокочастотные импульсы с генератора 1 поступают через делитель 2 на вход блока 3 питания фазовращателя и на дополнительный вход многоканального формирователя 7 опорных импульсов. Блок 3 вырабатывает питание датчика 4 в виде синусоидальных напряжений с частотой выходного сигнала делителя 2. Компаратор 5 преобразует выходной сигнал фазовращателя 4 и последовательность прямоугольных импульсов, которые блоком 6 распределяются по п каналам формирователя 7. В каждом канале по переднему фронту входных импульсов запускается схема формирования опорных импульсов. Дли- тельность опорных импульсов равна сумме п-1 периодов питающего сигнала фазовращателя 4 0 С выходов формирователя 7 опорные импульсы поступают на соответствующие входы логической схемы 8, Этот блок вырабатывает последовательность импульсов с частотой выходного сигнала фазовращателя 4 и длительностью, пропорциональной модулю разности п .периодов питающего и выходного сигналов фазовращателя 4 О При положительной разности периодов сформированная последовательность импульсов выдается с первого выхода блока 8 и поступает на прямой вход Формирователя 9 О Когда эта разность отрицательная, то последовательность импульсов выдается на инверсный вход формирователя 9 О Формирователь 9 преобразует входной сигнал а последовательность импульсов с постоянной стабильной амплитудой, с длительностью, равной длительности входных импульсов, и полярностью, соответствующей входу, на который поступает сигнал. Блок 10 выдает среднее значение сформированной блоком 9 последовательности импульсов, которое и принимается в качестве сигнала скорости перемещения. В каждом канале блока 7 формирование опорных импульсов может быть выполнено, например, по схеме, представленной на ф и г 0 2 о Схема содержит элемент ИЛИ 11 с инверсией, счетчик 12 импульсов, элемент И 13 с инверсией и RS триггер 14 о В исходном состоянии счетчик 12 и триггер 14 обнулены. С приходом запускающего импульса Ме снимается запрет со счетчика 12 по входу R и начинается подсчет высокочастотных импульсов, поступающих на вход С. Первый входной импульс своим передним 1571509 ветственно, а также каждый 1-вход многовходовои логической схемы соединен с первым входом і-й двухвходовой схемы ИЛИ, а каждый (і+1)-й вход многовходовои логической схемы - с вторым входом і-й двухвходовой схемы ИЛИ, ( і - t , 2 , . , , ( N - 1 ) ) , первый и второй входы i=N двухвходовой схемы И И соединены с і - N входом и перЛ вым входом многовходовои логической схемы соответственно, при этом выходы N двухвходовых схем И И соединены Л с входами N-входовой схемы И-НЕ, а первым и вторым выходами многовходовои логической схемы являются выходы N-входовой схемы И и N-входовой схе-, мы И-НЕ соответственно. U1 U7 фиг. 2 фиг.З 1571509 фронтом переводит выход " 0 " счетчитой выходного сигнала датчика 4 и длика 1 2 в единичное состояние 0 Вследтельностью, равной промежутку време-'^ ствие этого на выходе элемента И t3 ни между указанными опорными импульс инверсией появляется нулевой имсами. пульс, который устанавливает триггер 14 в единичное состояние. После приФормула и з о б р е т е н и я хода импульсов, количество которых соответствует требуемой длительнос1о Устройство для измерения скоти опорного импульса, на выходе Р рости перемещения, содержащее гесчетчика 12 появляется отрицательный нератор эталонной частоты, делитель импульс, сбрасывающий триггер 14 в частоты и последовательно соединенные нулевое состояние. По цепи обратной блок питания, фазовращатель, компарасвязи (триггер 14 - элемент ИЛИ 11 тор, многоканальный распределитель с инверсией) обнуляется и счетчик 12 D имцульсов, многоканальный формироваТем самым схема возвращается в исход- )5 тель опорных импульсов, многовходовую ное состояние. Формируемый опорный логическую схему и блок осреднения, импульс снимается с прямого выхода выход генератора эталонной частоты триггера 14, Далее цикл повторяется0 соединен с дополнительным входом мноЛогическая схема 8 построена в соответствии с логическими уравнениями: = х, х х ."X п» *

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for measurement of rate of displacement

Автори англійськоюYaroslavtsev Mykhailo Ivanovych

Назва патенту російськоюУстройство для определения скорости перемещения

Автори російськоюЯрославцев Михаил Иванович

МПК / Мітки

МПК: G01P 3/42

Мітки: швидкості, пристрій, переміщення, вимірювання

Код посилання

<a href="https://ua.patents.su/6-2063-pristrijj-dlya-vimiryuvannya-shvidkosti-peremishhennya.html" target="_blank" rel="follow" title="База патентів України">Пристрій для вимірювання швидкості переміщення</a>

Попередній патент: Електропневмоклапан

Наступний патент: Спосіб безвідходної переробки яблучних вичавок

Випадковий патент: Техпроцес енергозбереження в системах опалення