Пристрій для формування адрес процесора швидкого перетворення фур’є

Формула / Реферат

1. Пристрій для формування адрес процесора швидкого перетворення Фур'є, що містить перший і другий лічильники, блок постійної пам’яті, групу з N (N - максимальна розрядність адреси) мультиплексорів, перший мультиплексор, перший регістр та блок керування, тактовий вхід якого є тактовим входом пристрою, інформаційними виходами якого є виходи першого регістра, тактовий вхід якого підключений до другого виходу блока керування, перший вихід якого підключений до лічильного входу першого лічильника, j-й вихід (![]() ) якого з'єднаний з першим інформаційним входом j-го мультиплексора групи та j-м інформаційним входом першого комутатора, перший вихід першого лічильника з'єднаний з другими інформаційними входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, k-й вихід (

) якого з'єднаний з першим інформаційним входом j-го мультиплексора групи та j-м інформаційним входом першого комутатора, перший вихід першого лічильника з'єднаний з другими інформаційними входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, k-й вихід (![]() ) якого підключений до третього інформаційного входу (k-1)-гo мультиплексора групи, (N+1)-й вихід першого лічильника підключений до (N+l)-гo інформаційного входу першого комутатора, перший та (2N-2)-й виходи блока постійної пам'яті підключені до адресних входів відповідно першого та N-го мультиплексорів групи, 2m-й та (2m+1)-й виходи (

) якого підключений до третього інформаційного входу (k-1)-гo мультиплексора групи, (N+1)-й вихід першого лічильника підключений до (N+l)-гo інформаційного входу першого комутатора, перший та (2N-2)-й виходи блока постійної пам'яті підключені до адресних входів відповідно першого та N-го мультиплексорів групи, 2m-й та (2m+1)-й виходи (![]() ) блока постійної пам'яті підключені відповідно до першого та другого адресних входів (m+1)-го мультиплексора групи, адресні входи першого мультиплексора підключені до групи входів задавання довжини вибірки пристрою, який відрізняється тим, що в пристрій введені третій лічильник, другий комутатор, другий, третій і четвертий регістри, три елементи АБО, три інвертори та елемент АБО-НІ, вихід якого є виходом завершення роботи пристрою, перший вхід блока керування з'єднаний з першим входом першого елемента АБО та входом другого інвертора і є входом початку роботи пристрою, вихід першого комутатора підключений до другого входу першого елемента АБО, вихід якого підключений до входу скидання першого лічильника, та входу третього інвертора, вихід якого підключений до других входів другого та третього елементів АБО та до зворотного лічильного входу третього лічильника, виходи якого підключені до входів елемента АБО-НІ, вхід першого інвертора з'єднаний з першим входом третього елемента АБО, адресним входом другого комутатора і є входом задавання ознаки розташування даних пристрою, вихід першого інвертора підключений до першого входу другого елемента АБО, виходи другого та третього елементів АБО підключені відповідно до зворотного та прямого лічильних входів другого лічильника, вихід другого інвертора підключений до входів запису другого та третього лічильників, перші інформаційні входи другого комутатора є групою входів установлення значення "1", входи задавання довжини вибірки пристрою підключені до інформаційних входів третього лічильника та других інформаційних входів другого комутатора, виходи якого підключені до інформаційних входів другого лічильника, виходи якого підключені до адресних входів блока постійної пам'яті, вихід j-го мультиплексора групи підключений до j-го інформаційного входу першого, другого, третього та четвертого регістрів, j-ті інформаційні виходи яких з'єднані, третій, четвертий і п'ятий виходи блока керування підключені до тактових входів відповідно другого, третього та четвертого регістрів, входи дозволу читання першого, другого, третього та четвертого регістрів підключені відповідно до шостого, сьомого, восьмого та дев'ятого виходів блока керування.

) блока постійної пам'яті підключені відповідно до першого та другого адресних входів (m+1)-го мультиплексора групи, адресні входи першого мультиплексора підключені до групи входів задавання довжини вибірки пристрою, який відрізняється тим, що в пристрій введені третій лічильник, другий комутатор, другий, третій і четвертий регістри, три елементи АБО, три інвертори та елемент АБО-НІ, вихід якого є виходом завершення роботи пристрою, перший вхід блока керування з'єднаний з першим входом першого елемента АБО та входом другого інвертора і є входом початку роботи пристрою, вихід першого комутатора підключений до другого входу першого елемента АБО, вихід якого підключений до входу скидання першого лічильника, та входу третього інвертора, вихід якого підключений до других входів другого та третього елементів АБО та до зворотного лічильного входу третього лічильника, виходи якого підключені до входів елемента АБО-НІ, вхід першого інвертора з'єднаний з першим входом третього елемента АБО, адресним входом другого комутатора і є входом задавання ознаки розташування даних пристрою, вихід першого інвертора підключений до першого входу другого елемента АБО, виходи другого та третього елементів АБО підключені відповідно до зворотного та прямого лічильних входів другого лічильника, вихід другого інвертора підключений до входів запису другого та третього лічильників, перші інформаційні входи другого комутатора є групою входів установлення значення "1", входи задавання довжини вибірки пристрою підключені до інформаційних входів третього лічильника та других інформаційних входів другого комутатора, виходи якого підключені до інформаційних входів другого лічильника, виходи якого підключені до адресних входів блока постійної пам'яті, вихід j-го мультиплексора групи підключений до j-го інформаційного входу першого, другого, третього та четвертого регістрів, j-ті інформаційні виходи яких з'єднані, третій, четвертий і п'ятий виходи блока керування підключені до тактових входів відповідно другого, третього та четвертого регістрів, входи дозволу читання першого, другого, третього та четвертого регістрів підключені відповідно до шостого, сьомого, восьмого та дев'ятого виходів блока керування.

2. Пристрій за п. 1, який відрізняється тим, що блок керування містить п'ять елементів І, елемент АБО та регістр зсуву, тактовий вхід якого з'єднаний з першим входом елемента АБО і є тактовим входом блока керування, перший вхід якого підключений до входу задавання режиму роботи регістра зсуву, перші сім інформаційних входів якого підключені до входу задавання логічної одиниці пристрою, восьмий інформаційний вхід регістра зсуву підключений до входу задавання логічного нуля пристрою, перший вихід регістра зсуву підключений до перших входів першогота четвертого елементів І та є другим виходом блока керування, другий вихід регістра зсуву підключений до третього входу першого та першого входу п'ятого елементів І та є третім виходом блока керування, третій та четвертий виходи регістра зсуву підключені до перших входів відповідно другого та третього елементів І, п'ятий вихід регістра зсуву підключений до других входів першого та другого елементів І та є четвертим виходом блока керування, шостий вихід регістра зсуву підключений до четвертого входу першого та другого входу третього елементів І та є п'ятим виходом блока керування, сьомий вихід регістра зсуву підключений до другого входу четвертого елемента І, восьмий вихід регістра зсуву підключений до послідовного інформаційного входу регістра зсуву та другого входу п'ятого елемента І, виходи четвертого, п'ятого, другого та третього елементів І є відповідно шостим, сьомим, восьмим та дев'ятим виходами блока керування, вихід першого елемента І підключений до другого входу елемента АБО, вихід якого є першим виходом блока керування.

Текст

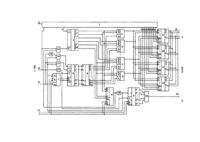

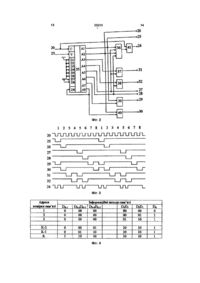

1 Пристрій для формування адрес процесора швидкого перетворення Фур'є, що містить перший і другий лічильники, блок постійної пам'яті, групу з N (N - максимальна розрядність адреси) мультиплексорів, перший мультиплексор, перший регістр та блок керування, тактовий вхід якого є тактовим входом пристрою, інформаційними виходами якого є виходи першого регістра, тактовий вхід якого підключений до другого виходу блока керування, перший вихід якого підключений до лічильного входу першого лічильника, j-й вихід ( j = 1, N) якого з'єднаний з першим інформаційним входом j-ro мультиплексора групи та J-M інформаційним входом першого комутатора, перший вихід першого лічильника з'єднаний з другими інформаційними входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, к-й вихід (к = 3,N) якого підключений до третього інформаційного входу (к-1)-го мультиплексора групи, (ІЧ+1)-й вихід першого лічильника підключений до (N+l)-ro інформаційного входу першого комутатора, перший та (2ІЧ-2)-й виходи блока постійної пам'яті підключені до адресних входів ВІДПОВІДНО першого та N-ro мультиплексорів групи, 2т-й та (2т+1)-й виходи ( т = 1,14-2) блока постійної пам'яті підключені ВІДПОВІДНО ДО першого та другого адресних входів (т+1)-го мультиплексора групи, адресні входи першого мультиплексора підключені до групи входів задавання довжини вибірки пристрою, який відрізняється тим, що в пристрій введені третій лічильник, другий комутатор, другий, третій і четвертий регістри, три елементи АБО, три інвертори та елемент АБО-НІ, вихід якого є виходом завершення роботи пристрою, перший вхід блока керування з'єднаний з першим входом першого елемента АБО та входом другого інвертора і є входом початку роботи пристрою, вихід першого комутатора підключений до другого входу першого елемента АБО, вихід якого підключений до входу скидання першого лічильника, та входу третього інвертора, вихід якого підключений до других входів другого та третього елементів АБО та до зворотного лічильного входу третього лічильника, виходи якого підключені до входів елемента АБО-НІ, вхід першого інвертора з'єднаний з першим входом третього елемента АБО, адресним входом другого комутатора і є входом задавання ознаки розташування даних пристрою, вихід першого інвертора підключений до першого входу другого елемента АБО, виходи другого та третього елементів АБО підключені ВІДПОВІДНО до зворотного та прямого лічильних входів другого лічильника, вихід другого інвертора підключений до входів запису другого та третього ЛІЧИЛЬНИКІВ, перші інформаційні входи другого комутатора є групою входів установлення значення " 1 " , входи задавання довжини вибірки пристрою підключені до інформаційних входів третього лічильника та других інформаційних входів другого комутатора, виходи якого підключені до інформаційних входів другого лічильника, виходи якого підключені до адресних входів блока постійної пам'яті, вихід j-ro мультиплексора групи підключений до j-ro інформаційного входу першого, другого, третього та четвертого регістрів, J-TI інформаційні виходи яких з'єднані, третій, четвертий і п'ятий виходи блока керування підключені до тактових входів ВІДПОВІДНО другого, третього та четвертого регістрів, входи дозволу читання першого, другого, третього та четвертого регістрів підключені ВІДПОВІДНО до шостого, сьомого, восьмого та дев'ятого виходів блока керування 2 Пристрій за п 1, який відрізняється тим, що блок керування містить п'ять елементів І, елемент АБО та регістр зсуву, тактовий вхід якого з'єднаний з першим входом елемента АБО і є тактовим входом блока керування, перший вхід якого підключений до входу задавання режиму роботи регістра зсуву, перші сім інформаційних входів якого підключені до входу задавання логічної одиниці пристрою, восьмий інформаційний вхід регістра зсуву підключений до входу задавання логічного нуля пристрою, перший вихід регістра зсуву підключений до перших входів першого та четвертого елементів І та є другим виходом блока керування, другий вихід регістра зсуву підключений дотретьо о> CO Ю 53219 го входу першого та першого входу пятого елементів І та є третім виходом блока керування, третій та четвертий виходи регістра зсуву підключені до перших входів ВІДПОВІДНО другого та третього елементів І, п'ятий вихід регістра зсуву підключений до других входів першого та другого елементів І та є четвертим виходом блока керування, шостий вихід регістра зсуву підключений до четвертого входу першого та другого входу третього елементів І та є п'ятим виходом блока керування, сьомий вихід регістра зсуву підключений до другого входу четвертого елемента І, восьмий вихід регістра зсуву підключений до послідовного інформаційного входу регістра зсуву та другого входу п'ятого елемента І, виходи четвертого, п'ятого, другого та третього елементів І є ВІДПОВІДНО шостим, сьомим, восьмим та дев'ятим виходами блока керування, вихід першого елемента І підключений до другого входу елемента АБО, вихід якого є першим виходом блока керування Винахід належить до галузі цифрової обчислювальної техніки і може бути застосований у складі процесорів швидкого перетворення Фур'є (ШПФ), що використовуються в пристроях обчислення спектрів, згорток та кореляційних функцій Відомий пристрій для формування адрес процесора ШПФ [А с СССР №1174939, кл G 06 F 15/332, 1984], що містить перший і другий лічильники, блок постійної пам'яті, групу з N (N - розрядність адреси) мультиплексорів, перший регістр та блок керування, тактовий вхід якого є тактовим входом пристрою, інформаційними виходами якого є виходи першого регістру, тактовий вхід якого підключений до другого виходу блока керування, перший вихід якого підключений до лічильного входу першого лічильника, j-й вихід 0=1,N) якого з'єднаний з першим інформаційним входом j-ro мультиплексора групи, перший вихід першого лічильника з'єднаний з другими інформаційними входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, к-й вихід (k=3,N) якого підключений до третього інформаційного входу (к-1)-го мультиплексора групи, перший та (2ІЧ-2)-й виходи блока постійної пам'яті підключені до адресних входів ВІДПОВІДНО першого та N-ro мультиплексорів групи, 2т-й та (2т+1)-й виходи (m=1,N-2) блока постійної пам'яті підключені ВІДПОВІДНО до першого та другого адресних входів (т+1)-го мультиплексора групи входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, к-й вихід (k=3,N) якого підключений до третього інформаційного входу (к-1)-го мультиплексора групи, (Ы+1)-й вихід першого лічильника підключений до (N+1)-ro інформаційного входу першого комутатора, перший та (2ІЧ-2)-й виходи блока постійної пам'яті підключені до адресних входів ВІДПОВІДНО першого та N-ro мультиплексорів групи, 2т-й та (2т+1)-й виходи (m=1,N-2) блока постійної пам'яті підключені ВІДПОВІДНО до першого та другого адресних входів (т+1)-го мультиплексора групи, адресні входи першого мультиплексора підключені до групи входів завдання довжини вибірки пристрою Недоліком даного пристрою є низька швидкодія внаслідок того, що для формування кожної адреси необхідний час, що дорівнює трьом періодам тактових імпульсів Крім того, пристрій містить складний блок модифікації адреси для можливості обробки вибірки ВІДЛІКІВ з двійковоінверсним порядком їх розташування В основу винаходу поставлено задачу створення пристрою для формування адрес процесора ШПФ, в якому за рахунок введення нових елементів та зв'язків МІЖ НИМИ досягається скорочення часу формування кожної адреси до одного періоду тактових імпульсів, внаслідок чого підвищується швидкодія пристрою, а за рахунок виключення блока модифікації адреси спрощується структура пристрою Поставлена задача досягається за рахунок того, що в пристрій для формування адрес процесора ШПФ, що містить перший і другий лічильники, блок постійної пам'яті, групу з N (N - максимальна розрядність адреси) мультиплексорів, перший мультиплексор, перший регістр та блок керування, тактовий вхід якого є тактовим входом пристрою, інформаційними виходами якого є виходи першого регістру, тактовий вхід якого підключений до другого виходу блока керування, перший вихід якого підключений до лічильного входу першого лічильника, j-й вихід Q=1 ,N) якого з'єднаний з першим інформаційним входом j-ro мультиплексора групи та J-M інформаційним входом першого комутатора, перший вихід першого лічильника з'єднаний з другими інформаційними входами всіх мультиплексорів групи, крім першого мультиплексора групи, до другого входу якого підключений другий вихід першого лічильника, k-й вихід (k=3,N) якого підключений до третього інформаційного входу (к-1) Недоліком даного пристрою є низька швидкодія та неможливість використання пристрою для адресації ВІДЛІКІВ при обробці вибірки довільної довжини, кратної двом Найбільш близьким за технічною сутністю до пропонованого є пристрій для формування адрес процесора ШПФ [А с СССР, №1499373, кл G 06 F 15/332, Бюл №29, 1989], що містить перший і другий лічильники, блок постійної пам'яті, групу з N (N - максимальна розрядність адреси) мультиплексорів, перший мультиплексор, перший регістр та блок керування, тактовий вхід якого є тактовим входом пристрою, інформаційними виходами якого є виходи першого регістру, тактовий вхід якого підключений до другого виходу блока керування, перший вихід якого підключений до лічильного входу першого лічильника, j-й вихід Q=1 ,N) якого з'єднаний з першим інформаційним входом j-ro мультиплексора групи та J-M інформаційним входом першого комутатора, перший вихід першого лічильника з'єднаний з другими інформаційними 53219 го мультиплексора групи, (ІЧ+1)-й вихід першого лічильника підключений до (N+1)-ro інформаційного входу першого комутатора, перший та (2ІЧ-2)-й виходи блока постійної пам'яті підключені до адресних входів ВІДПОВІДНО першого та N-ro мультиплексорів групи, 2т-й та (2т+1)-й виходи (m=1,N2) блока постійної пам'яті підключені ВІДПОВІДНО ДО першого та другого адресних входів (т+1)-го мультиплексора групи, адресні входи першого мультиплексора підключені до групи входів завдання довжини вибірки пристрою, додатково введені третій лічильник, другий комутатор, другий, третій і четвертий регістри, три елементи АБО, три інвертори та елемент АБО-НІ, вихід якого є виходом завершення роботи пристрою, перший вхід блока керування з'єднаний з першим входом першого елемента АБО та входом другого інвертора і є входом початку роботи пристрою, вихід першого комутатора підключений до другого входу першого елемента АБО, вихід якого підключений до входу скидання першого лічильника, та входу третього інвертора, вихід якого підключений до других входів другого та третього елементів АБО та до зворотного лічильного входу третього лічильника, виходи якого підключені до входів елемента АБОНІ, вхід першого інвертора з'єднаний з першим входом третього елемента АБО, адресним входом другого комутатора і є входом завдання ознаки розташування даних пристрою, вихід першого інвертора підключений до першого входу другого елемента АБО, виходи другого та третього елементів АБО підключені ВІДПОВІДНО до зворотного та прямого лічильних входів другого лічильника, вихід другого інвертора підключений до входів запису другого та третього ЛІЧИЛЬНИКІВ, перші інформаційні входи другого комутатора є групою входів установки значення " 1 " , входи завдання довжини вибірки пристрою підключені до інформаційних входів третього лічильника та других інформаційних входів другого комутатора, виходи якого підключені до інформаційних входів другого лічильника, виходи якого підключені до адресних входів блока постійної пам'яті, вихід j-ro мультиплексора групи підключений до j-ro інформаційного входу першого, другого, третього та четвертого регістрів, J-TI інформаційні виходи яких з'єднані, третій, четвертий і п'ятий виходи блока керування підключені до тактових входів ВІДПОВІДНО другого, третього та четвертого регістрів, входи дозволу читання першого, другого, третього та четвертого регістрів підключені ВІДПОВІДНО до шостого, сьомого, восьмого та дев'ятого виходів блока керування Блок керування містить п'ять елементів І, елемент АБО та регістр зсуву, тактовий вхід якого з'єднаний з першим входом елемента АБО і є тактовим входом блока керування, перший вхід якого підключений до входу завдання режиму роботи регістра зсуву, перші сім інформаційних входів якого підключені до входу завдання логічної одиниці пристрою, восьмий інформаційний вхід регістра зсуву підключений до входу завдання логічного нуля пристрою, перший вихід регістра зсуву підключений до перших входів першого та четвертого елементів І та є другим виходом блока керування, другий вихід регістра зсуву підключений до третього входу першого та першого входу п'ятого елементів І та є третім виходом блока керування, третій та четвертий виходи регістра зсуву підключені до перших входів ВІДПОВІДНО другого та третього елементів І, п'ятий вихід регістра зсуву підключений до других входів першого та другого елементів І та є четвертим виходом блока керування, шостий вихід регістра зсуву підключений до четвертого входу першого та другого входу третього елементів І та є п'ятим виходом блока керування, сьомий вихід регістра зсуву підключений до другого входу четвертого елемента І, восьмий вихід регістра зсуву підключений до послідовного інформаційного входу регістра зсуву та другого входу п'ятого елемента І, виходи четвертого, п'ятого, другого та третього елементів І є ВІДПОВІДНО шостим, сьомим, восьмим та дев'ятим виходами блока керування, вихід першого елемента І підключений до другого входу елемента АБО, вихід якого є першим виходом блока керування Введення в пристрій третього лічильника, другого комутатора, другого, третього та четвертого регістрів, трьох елементів АБО, трьох інверторів та елемента АБО-НІ разом з їх зв'язками дозволило скоротити до одного періоду тактових імпульсів час формування кожної адреси та спростити формування адрес при обробці вибірки ВІДЛІКІВ З ДВІЙково-шверсним порядком їх розташування, внаслідок чого підвищилась швидкодія пристрою та спростилась його структура На фіг 1 представлена функціональна схема пристрою для формування адрес процесора ШПФ, на фіг 2 - функціональна схема блока керування, на фіг 3 - часові діаграми роботи блока керування, на фіг 4 - прошивка блока постійної пам'яті пристрою Пристрій (фиг 1) містить блок 1 керування, перший, другий та третій лічильники 2-4, групу 5 мультиплексорів, перший та другий комутатори 6-7, блок 8 постійної пам'яті, перший, другий, третій та четвертий регістри 9-12, перший, другий та третій елементи АБО 13-15, перший, другий та третій інвертори 16-18, елемент АБО-НІ 19, тактовий вхід 20, вхід 21 завдання ознаки розташування даних, групу 22 входів завдання довжини вибірки, вхід 23 початку роботи пристрою та перший вхід блока 1 керування, з першого по дев'ятий виходи 24-32 блока 1 керування, інформаційні виходи 33 пристрою та вихід 34 завершення роботи пристрою Блок 1 керування (фіг 2) містить регістр 35 зсуву, з першого по п'ятий елементи 136-40 та елемент АБО 41 Тактовий вхід 20 пристрою підключений до тактового входу блока 1 керування, перший вихід 24 якого підключений до лічильного входу першого лічильника 2, з другого по п'ятий виходи 25-28 підключені до тактових входів ВІДПОВІДНО З першого по четвертий регістрів 9-12, до входів дозволу читання яких підключені ВІДПОВІДНО з шостого по дев'ятий виходи 29-32 J-й вихід 0=1,N) першого лічильника 2 з'єднаний з першим інформаційним входом j-ro мультиплексора групи 5 та J-M інформаційним входом першого комутатора 6 Перший вихід першого лічильника 2 з'єднаний з другими інформаційними входами всіх мультиплексорів групи 5, крім першого мультиплексора групи, до другого входу якого підключений другий вихід 53219 першого лічильника 2, k-й вихід (k=3,N) якого підключений до третього інформаційного входу (к-1)го мультиплексора групи 5, а (Ы+1)-й вихід підключений до (N+1)-ro інформаційного входу першого комутатора 6 Перший та (2ІЧ-2)-й виходи блока 9 постійної пам'яті підключені до адресних входів ВІДПОВІДНО першого та N-ro мультиплексорів групи 5, 2т-й та (2т+1)-й виходи (m=1,N-2) блока 9 постійної пам'яті підключені ВІДПОВІДНО ДО першого та другого адресних входів (т+1)-го мультиплексора групи 5 Входи 25 завдання довжини вибірки пристрою підключені до адресних входів першого мультиплексора 6, інформаційних входів третього лічильника 4 та других інформаційних входів другого комутатора 7, перші інформаційні входи якого є групою входів установки значення " 1 " Виходи другого комутатора 7 підключені до інформаційних входів другого лічильника 3, виходи якого підключені до адресних входів блока 8 постійної пам'яті Перший вхід 23 блока 1 керування з'єднаний з першим входом першого елемента АБО 13 та входом другого інвертора 17 і є входом початку роботи пристрою Вихід першого комутатора 6 підключений до другого входу першого елемента АБО 13, вихід якого підключений до входу скидання першого лічильника 2, та входу третього інвертора 18, вихід якого підключений до других входів другого та третього елементів АБО 14-15 та до зворотного лічильного входу третього лічильника 4, виходи якого підключені до входів елемента АБО-НІ 19, вихід якого є виходом 34 завершення роботи пристрою Вхід першого інвертора 16 з'єднаний з першим входом третього елемента АБО 15, адресним входом другого комутатора 7 і є входом 21 завдання ознаки розташування даних пристрою Вихід першого інвертора 16 підключений до першого входу другого елемента АБО 14 Виходи другого та третього елементів АБО 14-15 підключені ВІДПОВІДНО до зворотного та прямого лічильних входів другого лічильника 3 Вихід другого інвертора 17 підключений до входів запису другого та третього ЛІЧИЛЬНИКІВ 3-4 Вихід J-ГО мультиплексора групи 5 підключений до j-ro інформаційного входу першого, другого, третього та четвертого регістрів 9-12, J-TI інформаційні виходи яких з'єднані та є інформаційними виходами 33 пристрою Тактовий вхід 20 блока 1 керування підключений до тактового входу регістра 35 зсуву та першого входу елемента АБО 41 Перший вхід 23 блока 1 керування підключений до входу завдання режиму роботи регістра 35 зсуву, перші сім інформаційних входів якого підключені до входу завдання логічної одиниці пристрою, а восьмий інформаційний вхід підключений до входу завдання логічного нуля пристрою Перший вихід регістра 35 зсуву підключений до перших входів першого та четвертого елементів 136,39 та є другим виходом 25 блока 1 керування Другий вихід регістра 35 зсуву підключений до третього входу першого та першого входу п'ятого елементів 136,40 та є третім виходом 26 блока 1 керування Третій та четвертий виходи регістра 35 зсуву підключені до перших входів ВІДПОВІДНО другого та третього елементів 137,38 П'ятий вихід регістра 35 зсуву підключений до других входів першого та другого елементів 136,37 та є четвертим виходом 27 блока 1 керу 8 вання Шостий вихід регістра 35 зсуву підключений до четвертого входу першого та другого входу третього елементів 136,38 та є п'ятим виходом 28 блока 1 керування Сьомий вихід регістра 35 зсуву підключений до другого входу четвертого елемента І 39 Восьмий вихід регістра 35 зсуву підключений до послідовного інформаційного входу регістра 35 зсуву та другого входу п'ятого елемента І40 Виходи четвертого 39, п'ятого 40, другого 37 та третього 38 елементів І є ВІДПОВІДНО шостим 29, сьомим ЗО, восьмим 31 та дев'ятим 32 виходами блока 1 керування Вихід першого елемента І 36 підключений до другого входу елемента АБО 4 1 , вихід якого є першим виходом 24 блока керування Пропонований пристрій формує адреси операндів базових операцій алгоритмів ШПФ з прямим або двійково-інверсним порядком ВІДЛІКІВ вибірки довільної довжини, кратної двом Алгоритм ШПФ виконується за N=log2M (M - довжина вибірки ВІДЛІКІВ) етапів, на кожному з яких обробляється М операндів Алгоритми формування адрес операндів базових операцій в алгоритмах ШПФ з прямим та двійково-інверсним порядком ВІДЛІКІВ вибірки співпадають ВІДПОВІДНО на і-му (і=1 ,N) та (N-i+1)-My етапах Адреса операнда базової операції алгоритму ШПФ з прямим порядком ВІДЛІКІВ на і-му етапі в ДВІЙКОВІЙ формі числення визначається як ANANi AI+IAIA, А3А2, де А, (і = І, N) - значення двійкового розряду порядкового номера Р=0,М-1 операнда базової операції в межах поточного етапу алгоритму ШПФ Тобто, формування адрес операндів полягає в комутації розрядів порядкового номера операнда у ВІДПОВІДНОСТІ з номером поточного етапу алгоритму ШПФ Для формування порядкового номера операнда в межах етапу алгоритму ШПФ використовується перший (Ы+1)-розрядний лічильник 2 Номер поточного етапу алгоритму ШПФ визначається другим К~[Іод2Г\І]-розрядним лічильником 3, в який на початку роботи записується значення номера початкового етапу, котрий формується за допомогою другого комутатора 7 Комутація розрядів порядкового номера операнда виконується за допомогою блока 8 постійної пам'яті, розрядність комірок якої складає (2N-2) розряди, та групи 5 мультиплексорів Прошивка блока 8 постійної пам'яті представлена на фіг 4 Перший комутатор 6 призначений для формування ознаки завершення чергового етапу алгоритму ШПФ Третій Крозрядний лічильник 4 визначає КІЛЬКІСТЬ етапів алгоритму ШПФ, що залишились до його завершення Для забезпечення узгодженого режиму роботи процесора ШПФ, при якому під час виконання п-оі базової операції формуються адреси операндів (п1)-оі базової операції для запису результатів цієї операції в пам'ять та адреси операндів (п+1)-оі базової операції для читання операндів цієї операції з пам'яті, призначені перший, другий, третій та четвертий регістри 9-12 з тристабільними виходами В будь-який момент часу активним є лише один з них, а саме той, на який поданий сигнал дозволу читання з блока 1 керування, а виходи інших регістрів знаходяться в цей момент часу в високоімпедансному стані Запис та читання інфо 53219 10 керування присутній активний сигнал дозволу читання третього регістра 11 В четвертому такті на інформаційних виходах 33 пристрою з'являється адреса другого операнда (п-1)-оі базової операції, оскільки на дев'ятому виході 32 блока 1 керування присутній активний сигнал дозволу читання четвертого регістра 12 В п'ятому такті по спадаючому фронту сигналу 27 з четвертого виходу блока 1 керування в третій регістр 11 записується адреса першого операнда (п+1)-оі базової операції, котра з'являється на інформаційних виходах 33 пристрою, оскільки на восьмому виході 31 блока 1 керування присутній активний сигнал дозволу читання третього регістра 11 В цьому ж такті на першому виході 24 блока 1 керування формується активний сигнал, який поступає на лічильний вхід першого лічильника 2, в результаті чого на його виходах формується порядковий номер наступного операнда В шостому такті по спадаючому фронту сигналу 28 з п'ятого виходу блока 1 керування в четвертий регістр 12 записується адреса другого операнда (п+1)-оі базової операції, котра з'являється на інформаційних виходах 33 пристрою, оскільки на дев'ятому виході 32 блока 1 керування присутній активний сигнал дозволу читання четвертого регістра 12 В цьому ж такті на першому виході 24 блока 1 керування формується активний сигнал, який поступає на лічильний вхід першого лічильника 2, в результаті чого на його виходах Робота пристрою складається з послідовного формується порядковий номер наступного опевиконання циклів, кожен з яких містить ВІСІМ періранда В сьомому такті на інформаційних виходах одів тактових імпульсів (фіг 3) В першому такті по спадаючому фронту сигналу 25 з другого виходу 33 пристрою з'являється адреса першого операнблока 1 керування в перший регістр 9 записується да n-оі базової операції, оскільки на шостому виадреса першого операнда n-оі базової операції, ході 29 блока 1 керування присутній активний сигкотра з'являється на інформаційних виходах 33 нал дозволу читання першого регістра 9 В восьпристрою, оскільки на шостому виході 29 блока 1 мому такті на інформаційних виходах 33 пристрою керування присутній активний сигнал дозволу чиз'являється адреса другого операнда n-оі базової тання першого регістра 9 В цьому ж такті на пероперації, оскільки на сьомому виході ЗО блока 1 шому виході 24 блока 1 керування формується керування присутній активний сигнал дозволу чиактивний сигнал, який поступає на лічильний вхід тання другого регістра 10 першого лічильника 2, в результаті чого на його Після завершення формування першим лічивиходах формується порядковий номер наступнольником 2 всіх порядкових номерів операндів пого операнда В другому такті по спадаючому фроточного етапу алгоритму ШПФ на виході першого нту сигналу 26 з третього виходу блока 1 керуванмультиплексора 6 з'являється активний одиничний ня в другий регістр 10 записується адреса другого сигнал, який встановлює в нульовий стан перший операнда n-оі базової операції, котра з'являється лічильник 2, зменшує на одиницю значення на на інформаційних виходах 33 пристрою, оскільки виходах третього лічильника 4 та в залежності від на сьомому виході ЗО блока 1 керування присутній сигналу на вході 21 ознаки розташування даних активний сигнал дозволу читання другого регістра поступає на прямий чи зворотний лічильний вхід 10 В цьому ж такті на першому виході 24 блока 1 другого лічильника 3, формуючи на його виходах керування формується активний сигнал, який позначення номера наступного етапу алгоритму ступає на лічильний вхід першого лічильника 2, в ШПФ результаті чого на його виходах формується поПісля завершення виконання всіх етапів алгорядковий номер наступного операнда В третьому ритму ШПФ на виході елемента АБОНІ 19 з'являтакті на інформаційних виходах 33 пристрою з'явється одиничний сигнал, котрий поступає на вихід ляється адреса першого операнда (п-1)-оі базової 34 завершення роботи пристрою операції, оскільки на восьмому виході 31 блока 1 рмацм в регістри 9-12 відбувається у ВІДПОВІДНОСТІ з часовими діаграмами, приведеними на фіг З Пристрій працює наступним чином З подачею імпульсу сигналу логічної одиниці на вхід 23 початку роботи пристрою перший лічильник 2 встановлюється в нульовий стан, в третій лічильник 4 записується значення N КІЛЬКОСТІ етапів алгоритму ШПФ, а в другий лічильник 3 записується значення номера початкового етапу алгоритму ШПФ у ВІДПОВІДНОСТІ з сигналом на вході 21 завдання ознаки розташування даних при нульовому сигналі, що відповідає прямому порядку ВІДЛІКІВ вибірки, записується значення 1, а при одиничному, що відповідає двійково-інверсному порядку ВІДЛІКІВ вибірки - значення N Значення N подається на групу 22 входів завдання довжини вибірки Крім того, в регістр 35 зсуву блока 1 керування по спаду тактового імпульсу на тактовому вході 20 пристрою записується двійкове значення "01111111", оскільки на вході завдання режиму роботи регістра 35 зсуву присутній одиничний сигнал, що поступає з входу 23 пристрою Після зняття активного сигналу на вході 23 пристрою регістр 35 зсуву переходить в послідовний режим роботи, при якому по спаду тактового імпульсу на тактовому вході 20 пристрою сигнал логічного нуля з'являється послідовно на виходах регістра 35 зсуву, котрий включений як кільцевий регістр 20 J 3 3 1 2 EY X, 13 16 ГЦ R 5Г A, 10 14 Y , II IS Є = , 23 Г 21 17 +1 e n w 11 D, C EY X. 12 EY 18 5^K M 22 С 19 J T : 3 4 13 53219 14 ЗО Фіг. 2 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 20 25 26 27 28 29 ЗО 31 32 2АІГІІ L J I—I 1 І — LJ І I T Г i_n_r І-ГН—Г —LTLT" u u i_n_r —LrLr_ 1_ Фіг. 3 Адреса комірюі пам'яті 1 2 3 К-2 К-1 К Інформаційні виходи пам'яті Аі-і 0 ._0__J 0 PR-2DR-3 DR-A-S 00 00 00 00 00 00 00 00 01 00 01 10 А. 0 1 1 0 0 1 00 01 10 01 10 10 10 10 10 10 10 10 1 1 1 Фіг. 4 15 53219 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24 16

ДивитисяДодаткова інформація

Назва патенту англійськоюAddress former in a processor for fast fourier transform

Автори англійськоюVolynets Viktor Ivanovych

Назва патенту російськоюФормирователь адреса в процессоре для быстрого преобразования фурье

Автори російськоюВолынец Виктор Иванович

МПК / Мітки

МПК: G06F 17/14

Мітки: формування, процесора, фур'є, пристрій, перетворення, адрес, швидкого

Код посилання

<a href="https://ua.patents.su/8-53219-pristrijj-dlya-formuvannya-adres-procesora-shvidkogo-peretvorennya-fureh.html" target="_blank" rel="follow" title="База патентів України">Пристрій для формування адрес процесора швидкого перетворення фур’є</a>

Попередній патент: Арифметичний пристрій для виконання швидкого перетворення хартлі-фур’є

Наступний патент: Пристрій для автоматичної настройки реактора для гасіння дуги

Випадковий патент: Четвертинні солі 1-[4-(1,1,3,3-тетраметилбутил)феноксі-1-етоксі]-3-(n-алкілдіалкіламіно)-2-пропанолу