Пристрій для моделювання оцінки надійності програмного забезпечення

Номер патенту: 59960

Опубліковано: 15.09.2003

Автори: Бунчук Олександр Олексійович, Мірошниченко Олег Григорович, Зеленков Олександр Аврамович

Формула / Реферат

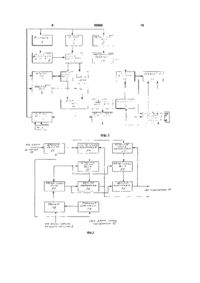

1. Пристрій для моделювання оцінки надійності програмного забезпечення, який містить перший регістр, генератор випадкових сигналів, перший, другий, третій та четвертий постійні запам'ятовуючі пристрої (ПЗП), першу та другу схеми порівняння, формувач, першу та другу схеми збігу, елемент АБО, блок задання константи, накопичуючий суматор, блок ділення, лічильник та індикатор, причому вихід першого ПЗП підключений до першого входу першої схеми порівняння, другий вхід якої з'єднаний з виходом генератора випадкових сигналів, а перший вихід з'єднаний з першим входом першої схеми збігу, другий вхід якої підключено до виходу другого ПЗП, другий вихід першої схеми порівняння підключено до другого входу другої схеми збігу, перший вхід якої з'єднаний з виходом третього ПЗП, адресний вхід якого з'єднаний з відповідними адресними входами першого, другого та четвертого ПЗП, із входом формувача і підключений до виходу першого регістра, інформаційний вхід якого з'єднаний з першим входом другої схеми порівняння і з виходом елемента АБО, перший і другий входи якого підключені до виходів відповідно першої та другої схеми збігу, вхід запуску першого регістра є входом пристрою, а вхід скидання першого регістра з`єднаний із входом скидання лічильника і підключений до виходу другої схеми порівняння, другий вхід якої підключено до виходу блока задання константи, вихід лічильника підключений до першого входу блока ділення, вихід якого з'єднаний із першим входом індикатора, а другий вхід підключено до виходу накопичуючого суматора, вхід якого з'єднаний з виходом четвертого ПЗП, який відрізняється тим, що в нього додатково введений блок виділення максимальної та мінімальної ймовірностей, перший вхід якого з'єднаний із виходом другої схеми порівняння, другий вхід підключений до входу запуску першого регістра, а інформаційний вхід з'єднаний із виходом блока ділення, перший і другий виходи блока підключені відповідно до другого і третього входів індикатора.

2. Пристрій за п.1, який відрізняється тим, що блок виділення максимальної і мінімальної ймовірностей містить тригер, третю, четверту та п'яту схеми збігу, другий регістр, третю та четверту схеми порівняння, регістр максимуму та регістр мінімуму і елемент затримки, вхід якого є першим входом блока виділення максимальної і мінімальної ймовірностей і підключений до першого входу другого регістра, а вихід з'єднаний із другим входом тригера, перший вхід якого є другим входом блока виділення максимальної і мінімальної ймовірностей, а вихід підключений до першого входу третьої схеми збігу, другий вхід якої об'єднаний з першими входами четвертої та п'ятої схем збігу, третьої та четвертої схем порівняння і підключений до виходу другого регістра, інформаційний вхід якого є інформаційним входом блока виділення максимальної та мінімальної ймовірностей, вихід третьої схеми збігу підключений до перших входів відповідно регістрів максимуму і мінімуму, другі входи яких підключені відповідно до виходів четвертої і п'ятої схем збігу, другі входи яких з'єднані відповідно з виходами третьої і четвертої схем порівняння, другі входи яких підключені відповідно до виходів регістрів максимуму і мінімуму і є другим і третім виходами блока виділення максимальної і мінімальної ймовірностей.

Текст

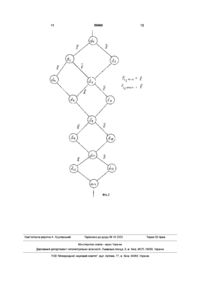

1 Пристрій для моделювання оцінки надійності програмного забезпечення, який містить перший регістр, генератор випадкових сигналів, перший, другий, третій та четвертий ПОСТІЙНІ запам'ятовуючі пристрої (ПЗП), першу та другу схеми порівняння, формувач, першу та другу схеми збігу, елемент АБО, блок задания константи, накопичуючий суматор, блок ділення, лічильник та індикатор, причому вихід першого ПЗП підключений до першого входу першої схеми порівняння, другий вхід якої з'єднаний з виходом генератора випадкових сигналів, а перший вихід з'єднаний з першим входом першої схеми збігу, другий вхід якої підключено до виходу другого ПЗП, другий вихід першої схеми порівняння підключено до другого входу другої схеми збігу, перший вхід якої з'єднаний з виходом третього ПЗП, адресний вхід якого з'єднаний з ВІДПОВІДНИМИ адресними входами першого, другого та четвертого ПЗП, із входом формувача і підключений до виходу першого регістра, інформаційний вхід якого з'єднаний з першим входом другої схеми порівняння і з виходом елемента АБО, перший і другий входи якого підключені до виходів ВІДПОВІДНО першої та другої схеми збігу, вхід запуску першого регістра є входом пристрою, а вхід скидання першого регістра з'єднаний із входом скидання лічильника і підключений до виходу другої схеми порівняння, другий вхід якої підключено до виходу блока задания константи, вихід лічильника підключений до першого входу блока Винахід відноситься до галузі автоматики та обчислювальної техніки і призначений для моделювання характеристик надійності програмного забезпечення ВІДМОВОСТІЙКИХ обчислювальних ділення, вихід якого з єднаний із першим входом індикатора, а другий вхід підключено до виходу накопичуючого суматора, вхід якого з'єднаний з виходом четвертого ПЗП, який відрізняється тим, що в нього додатково введений блок виділення максимальної та мінімальної ймовірностей, перший вхід якого з'єднаний із виходом другої схеми порівняння, другий вхід підключений до входу запуску першого регістра, а інформаційний вхід з'єднаний із виходом блока ділення, перший і другий виходи блока підключені ВІДПОВІДНО ДО другого і третього входів індикатора 2 Пристрій за п 1 , який відрізняється тим, що блок виділення максимальної і мінімальної ймовірностей містить тригер, третю, четверту та п'яту схеми збігу, другий регістр, третю та четверту схеми порівняння, регістр максимуму та регістр мінімуму і елемент затримки, вхід якого є першим входом блока виділення максимальної і мінімальної ймовірностей і підключений до першого входу другого регістра, а вихід з'єднаний із другим входом тригера, перший вхід якого є другим входом блока виділення максимальної і мінімальної ймовірностей, а вихід підключений до першого входу третьої схеми збігу, другий вхід якої об'єднаний з першими входами четвертої та п'ятої схем збігу, третьої та четвертої схем порівняння і підключений до виходу другого регістра, інформаційний вхід якого є інформаційним входом блока виділення максимальної та мінімальної ймовірностей, вихід третьої схеми збігу підключений до перших входів ВІДПОВІДНО регістрів максимуму і мінімуму, другі входи яких підключені ВІДПОВІДНО до виходів четвертої і п'ятої схем збігу, другі входи яких з'єднані ВІДПОВІДНО з виходами третьої і четвертої схем порівняння, другі входи яких підключені ВІДПОВІДНО до виходів регістрів максимуму і мінімуму і є другим і третім виходами блока виділення максимальної і мінімальної ймовірностей систем Відомий пристрій для моделювання імовірнісного графа, що містить перший та другий регістри, перший, другий та третій ПОСТІЙНІ запам'ятовуючі о (О о> ю 59960 пристрої, формувач, першу, другу та третю схеми порівняння, перший та другий генератори випадкових сигналів, першу та другу схеми збігу, перший та другий елементи АБО, лічильний об'єму моделювання, реверсивний лічильник, перший та другий накопичуючи суматори, перший та другий блоки задання константи, перший та другий блоки ділення та індикатор [1] Цей пристрій дозволяє моделювати статистичні характеристики процесу автоматичного відновлення за допомогою імовірнісного графа Недоліком пристрою є те, що він не дозволяє визначити характеристики надійності програмних засобів ВІДМОВОСТІЙКИХ обчислювальних систем Відомий пристрій для моделювання оцінки надійності програмних засобів, що містить перший регістр, генератор випадкових сигналів, перший, другий, третій та четвертий ПОСТІЙНІ запам'ятовуючі пристрої, першу та другу схеми порівняння, формувач, першу та другу схеми збігу, елемент АБО, блок задання константи, накопичуючий суматор, блок ділення, лічильник та індикатор [2] Цей пристрій дозволяє моделювати статистичні характеристики надійності програмних засобів Недоліком пристрою є те, що він не дозволяє визначити максимальну та мінімальну імовірності безвідмовного виконання програми, які мають велике значення при проектуванні програмного забезпечення ВІДМОВОСТІЙКИХ обчислювальних систем високої відповідальності В основу винаходу поставлена задача вдосконалення пристрою для моделювання статистичних характеристик надійності програмного забезпечення ВІДМОВОСТІЙКОІ обчислювальної системи за допомогою імовірнісного графа, в якому за рахунок багаторазового проходження різних маршрутів графа визначається не тільки середня імовірність безвідмовного виконання програми, а й максимальна і мінімальна імовірності, які відповідають "найважчому" і "найлегшому" маршрутам і можуть бути реалізовані імовірнісним графом, що розширює його функціональні можливості Поставлена задача вирішується тим, що до пристрою, який містить перший регістр, генератор випадкових сигналів, перший, другий, третій та четвертий ПОСТІЙНІ запам'ятовуючі пристрої, першу та другу схеми порівняння, формувач, першу та другу схеми збігу, елемент АБО, блок завдання константи, накопичуючий суматор, блок ділення, лічильник та індикатор, причому вихід першого запам'ятовуючого пристрою (ПЗП) підключений до першого входу першої схеми порівняння, другий вхід якої з'єднаний з виходом генератора випадкових сигналів, а перший вихід з'єднаний з першим входом першої схеми збігу, другий вхід якої підключено до виходу другого ПЗП, другий вихід першої схеми порівняння підключено до другого входу другої схеми збігу, перший вхід якої з'єднаний з виходом третього ПЗП, адресний вхід якого з'єднаний з ВІДПОВІДНИМИ адресними входами першого, другого та четвертого ПЗП, із входом формувача і підключений до виходу першого регістра, інформаційний вхід якого з'єднаний з першим входом другої схеми порівняння і з виходом елемента АБО, перший і другий входи якого підключені до виходів ВІДПОВІДНО першої та другої 4 схеми збігу, вхід запуску першого регістра є входом пристрою, а вхід скидання першого регістра з'єднаний із входом скидання лічильника і підключений до виходу другої схеми порівняння, другий вхід якої підключено до виходу блока задання константи, вихід лічильника підключений до першого входу блока ділення, вихід якого з'єднаний із першим входом індикатора, а другий вхід підключено до виходу накопичуючого суматора, вхід якого з'єднаний з виходом четвертого ПЗП у ВІДПОВІДНОСТІ з винаходом додатково введений блок виділення максимальної та мінімальної ймовірностей, перший вхід якого з'єднаний із виходом другої схеми порівняння, другий вхід підключено до входу запуску першого регістра, а інформаційний вхід з'єднаний із виходом блока ділення, перший і другий виходи блока підключені ВІДПОВІДНО ДО другого і третього входів індикатора, блок виділення максимальної і мінімальної ймовірностей містить тригер, третю, четверту та п'яту схеми збігу, другій регістр, третю та четверту схеми порівняння, регістр максимуму та регістр мінімуму і елемент затримки, вхід якого є першим входом блока виділення максимальної і мінімальної ймовірностей і підключений до першого входу другого регістра, а вихід з'єднаний із другим входом тригера, перший вхід якого є другим входом блока виділення максимальної і мінімальної ймовірностей, а вихід підключено до першого входу третьої схеми збігу, другий вхід якої об'єднаний з першими входами четвертої та п'ятої схем збігу, третьої та четвертої схем порівняння і підключений до виходу другого регістра, інформаційний вхід якого є інформаційним входом блока виділення максимальної та мінімальної ймовірностей, вихід третьої схеми збігу підключений до перших входів ВІДПОВІДНО регістрів максимуму і мінімуму, другі входи яких підключені ВІДПОВІДНО до виходів четвертої і п'ятої схем збігу, другі входи яких з'єднані ВІДПОВІДНО З виходами третьої і четвертої схем порівняння, другі входи яких підключені ВІДПОВІДНО до виходів регістрів максимуму і мінімуму і є другим і третім виходами блока виділення максимальної і мінімальної ймовірностей На фіг 1 показано блок-схему пристрою, на фіг 2 показано структурну схему блока виділення максимальної і мінімальної ймовірностей, а на фіг 3 наведено приклад імовірного графа програми Пристрій для моделювання оцінки надійності програмного забезпечення містить перший регістр 1 вихід якого з'єднаний з адресними входами ВІДПОВІДНО першого 2, другого 3, третього 4, четвертого 5, ПЗП і з входом формувача 6 Вихід першого ПЗП 2 з'єднаний з першим входом першої схеми порівняння 7, другий вхід якої підключено до виходу генератора випадкових сигналів 8, вхід якого підключений до виходу формувача 6 Перший і другий виходи першої схеми порівняння 7 підключені ВІДПОВІДНО до першого і другого входів першої 9 і другої 10 схем збігу Другий вхід першої схеми збігу 9 підключений до виходу другого ПЗП З, а перший вхід другої схеми збігу 10 підключений до виходу третього ПЗП 4 Виходи першої 9 і другої 10 схем збігу підключені ВІДПОВІДНО до першого і другого входів елемента АБО 11, вихід якого 59960 підключений до першого входу другої схеми порівняння 12 і інформаційного входу першого регістра 1, вхід скидання якого з'єднаний із входом лічильника 13 та першим входом блока виділення максимальної та мінімальної ймовірностей і підключений до виходу другої схеми порівняння 12, другий вхід якої підключено до виходу блока задания константи 15 Вхід запуску першого регістра 1 з'єднаний із другим входом блока виділення максимальної і мінімальної ймовірностей і є входом пристрою Інформаційний вхід накопичуючого суматора 14 підключено до виходу четвертого ПЗП 5, а вихід з'єднаний з першим входом блока 16 ділення Другий вхід якого підключений до виходу лічильника 13, а вихід підключений до першого входу індикатора 17 і до інформаційного входу блока 18 виділення максимальної і мінімальної ймовірностей, перший і другий виходи якого підключені ВІДПОВІДНО до другого і третього входів індикатора 17 Перший вхід тригера 19 з'єднаний із виходом другої схеми порівняння 12, а вихід підключено до першого входу третьої 20 схеми збігу, другий вхід якої з'єднаний із виходом другого регістра 21 і підключений до перших входів четвертої 22, п'ятої 23 схеми збігу та третьої 24 і четвертої 25 схем порівняння Вихід третьої схеми збігу 20 підключено до перших входів регістра максимуму 26 і регістра мінімуму 27, виходи яких з'єднані із другими входами ВІДПОВІДНО третьої 24 і четвертої 25 схем порівняння і підключені ВІДПОВІДНО до другого та третього входів індикатора 17 Виходи третьої 24 і четвертої 25 схем порівняння підключені до других входів четвертої 22 і п'ятої 23 схем збігу ВІДПОВІДНО, виходи яких підключені ВІДПОВІДНО до других входів регістра максимуму 26 і регістра мінімуму 27 Вихід елемента затримки 28 підключений до другого входу тригера 19, а вхід є першим входом блока 18 виділення максимальної і мінімальної ймовірностей і підключений до першого входу другого регістра 2 1 , інформаційний вхід якого є інформаційним входом блока 18 виділення максимальної і мінімальної ймовірностей Принцип роботи пристрою такий Програмний модуль з програмного забезпечення ВІДМОВОСТІЙКОІ обчислювальної системи може бути поданий графовою моделлю програми При моделюванні обчислювального процесу за такою моделлю передбачається надання кожній вершині графа деякого значення, наприклад, елементарного показника d,, що дорівнює логарифму ймовірності правильної роботи операторів, пов'язаних з даною вершиною Динаміка функціонування програми визначається вибором визначеного маршруту на графі Цей вибір обумовлюється сукупністю реалізацій передач керування в логічних вершинах, які зв'язані з випадковим процесом надходження на вхід програми різних векторів вхідних даних, що приводить до випадкового вибору маршрутів на графі Вибір маршрутів залежить від значення транзитивних ймовірностей переходів P., від І-І до J-I вершини графа, якими навантажуються дуги графа Очевидно, що окремий маршрут алізується з деякою імовірністю L ре P(L)= П R, L а середня оцінка ймовірності відмови може бути визначена як = s { p ( L ) x S d. тому що параметр надійності Q є дискретною випадковою величиною і його середнє значення визначається на множині реалізацій як середнє по імовірності Але для багаторозгалужених графових моделей, які мають багато логічних вершин (вершин з двома виходами), КІЛЬКІСТЬ МОЖЛИВИХ маршрутів різко зростає Наприклад, якщо граф має 20 логічних вершин, то при певних умовах КІЛЬКІСТЬ маршрутів досягає ^ ~ |и В таких випадках оцінку надійності функціонування програми можна одержати тільки за допомогою імітаційного моделювання КІЛЬКІСТЬ реалізацій маршрутів визначає об'єм моделювання М Тоді Q= Ed, leL М а внесок маршрутів в оцінку Q буде пропорційним ймовірності їх реалізацій У багатьох випадках важливими показниками є максимальна Q m a x і мінімальна Qmm ймовірності відмови програми, які можуть бути реалізовані на множині маршрутів Qr = maxQ., Q m i n = m m Q , На фіг 3 показані один з можливих варіантів імовірнісного графа програми Блоки 1 - 12, що показані на фіг 1, визначають ту чи іншу реалізацію маршруту на імовірнісному графі Генератор випадкових сигналів 8 формує реалізацію неперервної випадкової величини, яка має рівномірний розподіл на інтервалі [0, 1] В першому ПЗП зберігаються значення ймовірностей переходів у ВІДПОВІДНОСТІ з послідовними номерами вершин графа Наприклад, у першій комірці, яка відповідає вершині Zi (номер вершини - 1) записане число, яке дорівнює найменшому значенню ймовірності переходу (Р12 чи Різ), у другій комірці ПЗП 2 записане значення Р24, або Р25, У четвертій комірці (відповідає четвертій вершині) записується одиниця і т д У другому ПЗП 3 записується найменший номер вершини графа, яка пов'язана з поточною вершиною, а у третьому ПЗП 4 записується номер другої вершини, що зав'язана з поточною (при відсутності такої вершини записується 0) Нехай, наприклад, на виході першого регістра 1 встановлено КОД ПОТОЧНОЇ ВерШИНИ Zs (П'ЯТЬ), а Рбб < Рб7 Тоді на виході першого ПЗП 2 буде значення Рбб, на виході другого ПЗП 3 - номер 6, а на виході третього ПЗП 4 - номер 7, тобто номера вершин, які пов'язані з поточною вершиною під номером 5 У четвертому ПЗП 5 записується значення показників вершин d b імовірнісного графа Таким чином, в чотирьох ПЗП кодується конкретна реалізація імовірнісного графа Пристрій працює таким чином При надходженні сигналу запуску на вхід запуску першого регістра 1 на його виході встановлю 59960 ється код першої вершини графа Zi (одиниця), який надходячи на адресні входи усіх ПЗП встановлює на виходах ВІДПОВІДНО значення ймовірності Ріг(при умові, що Рі2< Різ), код числа 2 (ПЗП 3), код числа З (ПЗП 4), а також значення d, для першої вершини (ПЗП 5) Крім того, сигнал з виходу регістра 1 за допомогою формувача 6 запускає генератор випадкових сигналів 8, на виході якого одержується випадкове число г, з інтервалу [0, 1] Якщо г,

ДивитисяДодаткова інформація

Назва патенту англійськоюSimulator for estimating the reliability of software

Автори англійськоюZelenkov Oleksandr Avramovych

Назва патенту російськоюМоделирующее устройство для оценки надежности программного обеспечения

Автори російськоюЗеленков Александр Аврамович

МПК / Мітки

МПК: G06G 7/48

Мітки: забезпечення, програмного, пристрій, надійності, моделювання, оцінки

Код посилання

<a href="https://ua.patents.su/6-59960-pristrijj-dlya-modelyuvannya-ocinki-nadijjnosti-programnogo-zabezpechennya.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання оцінки надійності програмного забезпечення</a>

Попередній патент: Реактивний двигун

Наступний патент: Спосіб сорбційно-спектроскопічного визначення стануму (iv)

Випадковий патент: Сталь для сталевих труб (варіанти)