Формувач періодичної послідовності імпульсів з перенастроюваною тривалістю і фіксованим періодом

Номер патенту: 66752

Опубліковано: 10.01.2012

Автори: Харченко Вячеслав Сергійович, Коробков Микола Григорович, Рубанов Василь Григорович, Коробкова Олена Миколаївна

Формула / Реферат

Формувач періодичної послідовності імпульсів з перенастроюваною тривалістю і фіксованим періодом, який містить два лічильники, кожен з яких має вхід подачі імпульсів синхронізації, входи паралельного завантаження, вхід асинхронної установки у нульовий стан; ланцюжок, що складається з послідовно з'єднаних резистора і конденсатора; інвертор; стартостопний пристрій, який містить синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І; тривходовий елемент АБО, при цьому загальна точка послідовно сполучених резистора і конденсатора з'єднана з інформаційним входом D-тригера, з одним входом першого та другого двовходових елементів І; вихід першого двовходового елемента І сполучений зі входом асинхронної установки D-тригера в нульовий стан; другий вхід другого елемента І сполучений з виходом тривходового елемента АБО, один з входів якого поєднаний з виходом D-тригера; вихід другого елемента І з'єднаний з входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, утворюючи вхід формувача - вхід подачі періодичної послідовності імпульсів з виходу зовнішнього генератора; входи паралельного завантаження першого лічильника з'єднані з відповідними входами паралельного завантаження другого лічильника, утворюючи входи налагодження формувача на задані часові параметри вихідної послідовності імпульсів, який відрізняється тим, що замість типових двійкових лічильників в нього введено лічильники, кожен із яких виконано на зсувних регістрах, які мають два входи послідовного внесення і два входи налагоджування на заданий режим, за схемою генератора послідовності максимальної тривалості, тобто має двовходовий елемент інверсії складання за модулем два, перші входи яких з'єднано з виходами молодшого (нульового) розряду регістрів, а другі входи з'єднано з виходами старшого (третього) розряду, при цьому вихід першого елемента з'єднано зі входом послідовного внесення зі зсувом у бік молодших розрядів першого регістра, вихід другого елемента з'єднано зі входом послідовного внесення зі зсувом у бік старших розрядів другого регістра; перший і другий чотиривходові елементи АБО; третій двовходовий елемент інверсії складання за модулем два; двовходовий елемент АБО-НІ, при цьому виходи першого регістра з'єднано зі входами першого чотиривходового елемента АБО, вихід якого утворює перший вихід формувача, який з'єднано з першим входом елемента АБО-НІ, вихід якого утворює другий вихід формувача, з другим входом тривходового елемента АБО і з першим входом третього двовходового елемента інверсії складання за модулем два, вихід якого з'єднано з першими входами налагоджування на заданий режим першого регістра і другого регістра; другий вхід третього елемента інверсії складання за модулем два з'єднано з виходом другого чотиривходового елемента АБО, третім входом тривходового елемента АБО і входом інвертора, вихід якого з'єднано з нульовим входом налагоджування на заданий режим першого регістра; нульовий вхід налагоджування на заданий режим другого регістра з'єднано з рівнем логічної одиниці.

Текст

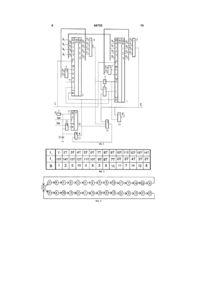

Формувач періодичної послідовності імпульсів з перенастроюваною тривалістю і фіксованим періодом, який містить два лічильники, кожен з яких має вхід подачі імпульсів синхронізації, входи паралельного завантаження, вхід асинхронної установки у нульовий стан; ланцюжок, що складається з послідовно з'єднаних резистора і конденсатора; інвертор; стартостопний пристрій, який містить синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І; тривходовий елемент АБО, при цьому загальна точка послідовно сполучених резистора і конденсатора з'єднана з інформаційним входом Dтригера, з одним входом першого та другого двовходових елементів І; вихід першого двовходового елемента І сполучений зі входом асинхронної установки D-тригера в нульовий стан; другий вхід другого елемента І сполучений з виходом тривходового елемента АБО, один з входів якого поєднаний з виходом D-тригера; вихід другого елемента І з'єднаний з входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, утворюючи вхід формувача - вхід подачі періодичної послідовності імпульсів з виходу зовнішнього генератора; входи паралельного завантаження першого лічильника з'єднані з відповідними входами паралельного завантаження другого лічильника, утво U 2 (19) 1 3 66752 4 часові параметри яких визначаються часовими нхронний D-тригер зі входом асинхронної установпараметрами імпульсів, що подаються на вхід (Таки у нульовий стан, перший і другий двовходові ктовий генератор. Авторське свідоцтво СРСР № елементи І; тривходовий елемент АБО, при цьому 307502. - Бюлетень винаходів. № 20, 1971; Тактозагальна точка послідовно сполучених резистора і вий генератор. Авторське свідоцтво СРСР № конденсатора з'єднана з інформаційним входом D354544. - Бюлетень винаходів. № 30, 1972). тригера, з одним входом першого та другого двовНедолік відомих пристроїв - обмежені функціходового елемента І; вихід першого двовходового ональні можливості, обумовлені налагоджуванням елемента І сполучений зі входом асинхронної на фіксований режим часових параметрів вихідних установки D-тригера в нульовий стан; другий вхід імпульсів. другого елемента І сполучений з виходом тривхоНайбільш близьким за технічною суттю і редового елемента АБО, один з входів якого поєдназультатом, що досягається, є формувач періодичний з виходом D-тригера; вихід другого елемента І ної послідовності імпульсів з перенастроюваною з'єднаний з входами асинхронної установки лічитривалістю і фіксованим періодом (патент України льників у нульовий стан; тактові входи першого та на корисну модель № 53542, бюл. № 19, 2010), другого лічильників сполучені між собою, утворюякий містить два лічильники, кожен з яких має вхід ючи вхід формувача - вхід подачі періодичної посподачі імпульсів синхронізації, входи паралельнолідовності імпульсів з виходу зовнішнього генераго завантаження, вхід асинхронної установки у тора; входи паралельного завантаження першого нульовий стан; ланцюжок, що складається з послілічильника з'єднано з відповідними входами парадовно з'єднаних резистора і конденсатора; інверлельного завантаження другого лічильника, утвотор; стартостопний пристрій, якій містить синхронрюючи входи налагодження формувача на задані ний D-тригер зі входом асинхронної установки у часові параметри вихідної послідовності імпульсів, нульовий стан, перший і другий двовходові елемевідповідно до корисної моделі, замість типових нти І; тривходовий елемент АБО, при цьому загадвійкових лічильників введено лічильники, кожен із льна точка послідовно сполучених резистора і яких виконано на зсувних регістрах, яки мають два конденсатора з'єднана з інформаційним входом Dвходи послідовного внесення і два входи налаготригера, з одним входом першого та другого двовджування на заданий режим, за схемою генератоходового елемента І; вихід першого двовходового ра послідовності максимальної тривалості, тобто елемента І сполучений зі входом асинхронної має двовходовий елемент інверсії складання за установки D-тригера в нульовий стан; другий вхід модулем два, першої входи яких з'єднано з виходругого елемента І сполучений з виходом тривходами молодшого (нульового) розряду регістрів, а дового елемента АБО, один з входів якого поєднадругої входи з'єднано з виходами старшого (трений з виходом D-тригера; вихід другого елемента І тього) розряду, при цьому, вихід першого елеменз'єднаний з входами асинхронної установки лічита з'єднано зі входом послідовного внесення зі льників у нульовий стан; тактові входи першого та зсувом у бік молодших розрядів першого регістра, другого лічильників сполучені між собою, утворювихід другого елемента з'єднано зі входом посліючи вхід формувача - вхід подачі періодичної посдовного внесення зі зсувом у бік старших розрядів лідовності імпульсів з виходу зовнішнього генерадругого регістра; перший і другий чотиривходові тора; входи паралельного завантаження першого елементи АБО; третій двовходовий елемент інвелічильника з'єднано з відповідними входами парарсії складання за модулем два; двовходовий елелельного завантаження другого лічильника, утвомент АБО-НІ, при цьому, виходи першого регістру рюючи входи налагодження формувача на задані з'єднано зі входами першого чотирьох входового часові параметри вихідної послідовності імпульсів. елемента АБО, вихід якого утворює перший вихід Недолік відомого пристрою - низька швидкоформувача, який з'єднано з першим входом еледія, зумовлена використанням типових двійкових мента АБО-НІ, вихід якого утворює другий вихід лічильників, складність і швидкодія яких знахоформувача, з другим входом тривходового елемедяться в протидії, що особо проявляється при збінта АБО і з першим входом третього двовходового льшенні діапазону перестройки, тобто кількості елемента інверсії складання за модулем два, вирозрядів, покриваючих заданий діапазон перехід якого з'єднано з першими входами налагоджустройки. вання на заданий режим першого регістра і другоВ основу корисної моделі поставлено завданго регістрів; другий вхід третього елемента інверсії ня удосконалення формувача періодичної посліскладання за модулем два з'єднано з виходом довності імпульсів з перенастроюваною тривалісдругого чотирьох входового елемента АБО, третім тю і фіксованим періодом шляхом введення входом тривходового елемента АБО і входом іннового складу елементів і нової організації взаємвертора, вихід якого з'єднано з нульовим входом них з'єднань між ними, забезпечує незалежність налагоджування на заданий режим першого регісвстановлення від кількості розрядів. тра; нульовий вхід налагоджування на заданий Поставлене завдання вирішується тим, що в режим другого регістру з'єднано з рівнем логічної формувач періодичної послідовності імпульсів з одиниці. перенастроюваною тривалістю і фіксованим періЗаявлений формувач має новий склад елемеодом, який містить два лічильники, кожен з яких нтів і нову організацію взаємозв'язків між ними, має вхід подачі імпульсів синхронізації, входи патобто містить нову сукупність ознак, які забезпералельного завантаження, вхід асинхронної устачують нові технічні властивості. новки у нульовий стан; ланцюжок, що складається Технічний результат, як наслідок цих властиз послідовно з'єднаних резистора і конденсатора; востей - більш висока швидкодія, зумовлена незаінвертор; стартостопний пристрій, якій містить силежністю встановлення від кількості розрядів. 5 66752 6 На фіг. 1 приведена схема формувача. Працює формувач в наступній послідовності. Формувач містить: два зсувних регістра 1, 2, Наявність ланцюжка, що складається із поєдкожен з яких має вхід подачі тактових імпульсів С, наних послідовно резистора 9 і конденсатора 10, входи паралельного завантаження D0-D3, входи підключеного до шини живлячої напруги +Е, при послідовного внесення DS0, DS3, входи налаговключенні джерела живлення протягом деякого джування на заданий режим М0, М1, вхід асинхпроміжку часу формує рівень логічного нуля на ронної установки в нульовий стан R, виходи Q0-Q3; входах елементів 12 та 13, забезпечуючи формуперший, другий і третій двовходові елементи інвевання рівня логічного нуля на їхніх виходах, приєрсії складання за модулем два 3, 4, 8, при цьому, днаних до входів R асинхронної установки в нуперші входи елементів 3, 4 з'єднано з виходами льовий стан відповідно D-тригера 11 і регістрів 1, молодшого (Q0) розряду регістрів, а другі входи 2. Після закінчення перехідного процесу, пов'язаз'єднано з виходами старшого (Q3) розряду, при ного з включенням джерела живлення D-тригер 11 цьому, вихід елемента 3 з'єднано зі входом посліі обоє регістри переходять у нульовий стан, фордовного внесення зі зсувом у бік молодших розрямуючи рівень логічного нуля відповідно на виході дів (DS3) регістра 1, вихід другого елемента з'єдQ тригера 11 і на виходах Q0-Q3 регістрів, що веде нано зі входом послідовного внесення зі зсувом у до формування рівня логічного нуля на виходах бік старших розрядів (DS0) регістра 2; перший і елементів АБО 5, 6 і елемента АБО 14, вихід якого другий чотиривходові елементи АБО 5, 6; інвертор з'єднаний зі входом елемента І 13, що забезпечує 7; ланцюжок, що складається з послідовно з'єднапідтвердження (блокування) рівня логічного нуля них резистора 9 і конденсатора 10; стартостопний на його виході, і по закінченню перехідного процепристрій, якій містить синхронний D-тригер 11 зі су, пов'язаного із зарядом конденсатора 6, що завходом асинхронної установки у нульовий стан R, безпечує рівень логічного нуля на входах R асинхперший і другий двовходові елементи І 12, 13; ронної установки регістрів 1 2 у нульовий стан. тривходовий елемент АБО 14, двовходовий елеОскільки режим асинхронної установки регістрів у менти АБО-НІ 15. Тактові входи С регістрів 1, 2 нульовий стан має пріоритет по відношенню до сполучені між собою, утворюючи вхід формувача всіх останніх режимів, то до тих пор поки на вході С - вхід подачі періодичної послідовності імпульсів елемента 13 (а отже і на його виході) зберігатиз виходу зовнішнього генератора. Входи паралеметься рівень логічного нуля, нульовий стан регісльного завантаження D0-D3 регістра 1 з'єднано з трів залишатиметься незмінним. відповідними входами паралельного завантаженПід час вступу імпульсу запуску (Start) на такня D0-D3 регістра 2, утворюючи входи b0-b3 налатовий вхід С тригера 11 по його фронту тригер годження формувача на задані часові параметри переходить в одиничний стан (Q=1), формуючи вихідної послідовності імпульсів. рівень логічної одиниці на виході елемента АБО Загальна точка послідовно сполучених резис14, а отже на вході та виході елемента І 13, що тора 9 і конденсатора 10 з'єднана з інформаційним забезпечує рівень логічної одиниці на входах R входом D-тригера 11, з одним входом двовходових регістрів 1,2, знімаючи блокування, у результаті елементів І 12, 13; другий вхід елемента І 12 утвочого нульове значення сигналу з виходів Р1, Р2 рює вхід подачі імпульсів зупинки (Stop) формуелементів АБО 5, 6, яке поступає на входи елемевання вихідних імпульсів, вихід першого двовхонту 8, формуючи на його виході, тобто на входах дового елемента І 12 сполучений зі входом R М1 регістрів 1, 2 рівень логічної одиниці, на входах асинхронної установки D-тригера 11 у нульовий М0 регістрів 1, 2 також рівень логічної одиниці, що стан; другий вхід елемента 113, який сполучений з забезпечує режим паралельного завантаження. виходом тривходового елемента АБО 14, один з Під час вступу першого (після закінчення певходів якого поєднаний з виходом D-тригера 11; рехідного процесу, пов'язаного із зняттям блокувихід елемента І 13 з'єднаний зі входами R асинхвання) тактового імпульсу С по його фронту відбуронної установки регістрів 1, 2 у нульовий стан. вається Тактовий вхід С тригера 11 утворює вхід подачі паралельне завантаження регістрів 1, 2 знаімпульсів запуску (Start) формування вихідних імченнями сигналів, що подаються на відповідні пульсів. входи D0-D3, тобто регістри 1, 2 переходять у стан Виходи Q0-Q3 регістру 1 з'єднано зі входами В. чотирьох входового елемента АБО 5, вихід якого В результаті цього переходу сигнал на вихоутворює перший вихід формувача F1, з'єднано зі дах елементів АБО 5, 6 дорівнює рівню логічної першим входом елемента АБО-НІ 15, вихід якого одиниці, що веде до формування одиничного сигутворює другий вихід F2 формувача, з другим вхоналу на вході інвертора 7, тобто нульового сигнадом тривходового елемента АБО 14 і з першим лу на вході М0 регістру 1, одиничне значення сигвходом третього двовходового елемента інверсії налу на входах М0, М1 регістра 2 залишається складання за модулем два 8, вихід якого з'єднано незмінним, тобто, режим завантаження регістра 2 зі входами М1 налагоджування на заданий режим залишатися незмінним, а регістр 1 переходить у регістрів 1, 2; другий вхід елемента 8 інверсії режим зсуву у бік молодших розрядів. складання за модулем два з'єднано з виходом Під час вступу подальших тактових імпульсів, чотирьох входового елемента АБО 6, третім вхозміст регістра 1 зміняється відповідно з алгоритдом тривходового елемента АБО 14 і входом інмом функціонування генератора послідовності вертора 7, вихід якого з'єднано зі входом М0 наламаксимальної тривалості зі зсувом у бік молодших годжування на заданий режим регістра 1; вхід М0 розрядів, а стан регістра 2 залишатися рівним В, налагоджування на заданий режим регістру 2 з'єддо тих пор, поки зміст регістра 1 не стане рівним 0. нано з рівнем логічної одиниці. В результаті цього переходу регістр 1 перейде в 7 66752 8 режим зберігання, а регістр 2 - у режим зсуву у бік обумовлюючи рівень логічної одиниці на його вистарших розрядів. ході, приєднаного до входу елемента І 13. ОскільПід час вступу подальших тактових імпульсів, ки на другому вході цього елемента також рівень зміст регістра 1 буде залишатися незмінним (рівлогічної одиниці, визначуваний напругою на конним 0), а стан регістра 2 буде зміняться відповідно денсаторі 10, який зарядився при включенні джез алгоритмом функціонування генератора послідорела живлення, то на виході елемента І 13, а отже, вності максимальної тривалості зі зсувом у бік і на входах R обох регістрів буде рівень логічної старших розрядів, до тих пор, поки зміст регістра 2 одиниці. Звідси витікає, що у момент вступу імпуне стане рівним 0, тобто формувач повернеться у льсу припинення генерації не станеться, обумоввихідний стан. Надалі всі процеси повторюються. люючи тим самим запобігання спотворенню Таким чином, після закінчення перехідного останнього імпульсу у вихідній послідовності. І процесу, пов'язаного із зняттям блокування, під тільки зі вступом подальших імпульсів, коли відбучас вступу на вхід С формувача періодичної посватиметься перехід регістрів 1, 2 у нульовий стан, лідовності імпульсів з періодом Т на виходах елена виході елемента АБО 14 буде сформований ментів АБО 5 і АБО-НІ 15 генерується послідоврівень логічного 0, обумовлюючи рівень 0 на вході ність імпульсів з фіксованим періодом, рівним 16Т, та виході елемента І 13, що приведе до блокувантривалість імпульсу і тривалість паузи яких заленя нульового стану регістрів 1, 2, тобто до припижать (фіг. 2) від значення управляючого двійкового нення процесу генерації. Зі вступом наступного слова В, при цьому, tи2=tп1-Т, tп2=tи1+Т, імпульсу запуску усі процеси повторюються. tи1+tп1=tи2+tп2=16T. На фіг. 3 приведений граф переходів формуЗупинка процесу формування вихідної послівача, що складається з двох кілець (верхнє кільце довності імпульсів здійснюється подачею імпуль- граф переходів регістра 2, нижнє кільце - граф су, відповідного рівню логічного нуля, на вхід зупипереходів регістра 1 із загальною вершиною, віднки (Stop), що формує активний рівень сигналу на повідною їх нульовому стану, а на фіг. 4 - епюри, вході R асинхронної установки D-тригера 5, що що ілюструють роботу для варіанту налагодження призводить до переходу його у нульовий стан В=9, визначаючого часові параметри вихідної пе(Q=0). Імпульс Stop, як правило, асинхронний по ріодичної послідовності імпульсів - tи1=6T, tп1=10Т і, відношенню до імпульсів зовнішнього генератора і відповідно, tи2=tп1-Т=9Т, tп2=tи1+Т=7Т, до стану регістрів 1, 2. tи1+tп1=tи2+tп2=16Т. Якщо у момент вступу тактового імпульсу обоє Пропонований пристрій, який, на відміну від регістри знаходитиметься у нульовому стані, то відомого, містить два лічильника, виконаних на при переході D-тригера 5 у нульовий стан на вхозсувних регістрах за схемою генератора послідовдах елемента АБО 14 і його виході буде сформоності максимальної тривалості, що дозволило звеваний рівень логічного 0, обумовлюючи рівень сти час переходу формувача з одного стану в друлогічного нуля на вході та виході елемента І 13, гий до мінімально можливого значення, яке що призведе до блокування нульового стану обох визначається часом передачі сигналу проміж сусірегістрів, а отже, до припинення процесу генерації. дніми розрядами регістра без додаткових міжрозЯкщо у момент вступу регістр 1 або регістр 2 рядних логічних елементів незалежно від кількості (або обоє) знаходитиметься у стані, відмінному від розрядів, тобто забезпечило підвищення швидкодії нульового, яке характеризується рівнем логічної формувача до максимально можливого, яка виодиниці на виході відповідного елемента АБО 5 значається використованою елементною базою. (АБО 6) з'єднаного зі входами елемента АБО 14, 9 66752 10 11 Комп’ютерна верстка Л. Купенко 66752 Підписне 12 Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюMeander-type pulse sequence shaper with adjustable pulse length and fixed period

Автори англійськоюKorobkov Mykola Hryhorovych, Korobkova Olena Mykolaivna, Rubanov Vasyl Hryhorovych, Kharchenko Viacheslav Serhiiovych

Назва патенту російськоюФормирователь периодической последовательности импульсов с перестраиваемой длительностью и фиксированным периодом

Автори російськоюКоробков Николай Григорьевич, Коробкова Елена Николаевна, Рубанов Василий Григорьевич, Харченко Вячеслав Сергеевич

МПК / Мітки

МПК: H03K 3/78

Мітки: тривалістю, перенастроюваною, формувач, фіксованим, імпульсів, послідовності, періодом, періодичної

Код посилання

<a href="https://ua.patents.su/6-66752-formuvach-periodichno-poslidovnosti-impulsiv-z-perenastroyuvanoyu-trivalistyu-i-fiksovanim-periodom.html" target="_blank" rel="follow" title="База патентів України">Формувач періодичної послідовності імпульсів з перенастроюваною тривалістю і фіксованим періодом</a>

Попередній патент: Формувач послідовності імпульсів типу меандр з перенастроюваною тривалістю

Наступний патент: Автоматизована гравіметрична система з високоточним виставленням осі чутливості гравіметра

Випадковий патент: Спосіб лікування шкірно-м'язових ран та подолання дефіциту донорських ресурсів шкіри