Перетворювач двійкового коду в однополярні оборотні коди

Номер патенту: 72952

Опубліковано: 10.09.2012

Автори: Рудаков Костянтин Сергійович, Лукашенко Володимир Андрійович, Лукашенко Дмитро Андрійович, Лукашенко Андрій Германович, Лукашенко Валентина Максимівна, Вербицький Олександр Сергійович, Міценко Сергій Анатолійович

Формула / Реферат

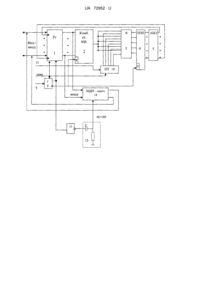

Перетворювач двійкового коду в однополярні оборотні коди, що містить регістр входу, який виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістра з'єднані з входами пристрою, постійного запам'ятовуючого пристрою (ПЗП), виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістра входу, керуючий вхід регістра входу з'єднаний з прямим виходом керуючого тригера, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, вхід керуючого тригера з'єднаний з першим керуючим входом пристрою, вхід "скид" регістра входу з'єднаний з входом пристрою "скид", входи комбінаційної схеми адреси з'єднані з відповідними виходами регістра входу, а керуючий вхід комбінаційної схеми адреси з'єднаний з інверсним виходом керуючого тригера, вихід комбінаційної схеми адреси з'єднаний з інформаційними входами блока вентилів, виходи якого з'єднані з відповідними входами постійно запам'ятовуючого пристрою, а керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з другим керуючим входом пристрою, входи "скид" керуючого пристрою та керуючого тригера з'єднані з входами "скид" пристрою, який відрізняється тим, що прямий вихід тригера з'єднаний з входом додатково введеного інвертора, вихід якого підключений до входу введеного диференціюючого ланцюга, вихід якого підключений до керуючого входу введеного блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра, а інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами вхідного регістра і є "входом/виходом" перетворювача.

Текст

Реферат: Перетворювач двійкового коду в однополярні оборотні коди містить регістр входу, постійний запам'ятовуючий пристрій, блок елементів АБО, керуючий тригер, комбінаційну схему адреси, блок вентилів, інвертор, диференціюючий ланцюг, блок МДП-ключів. UA 72952 U (54) ПЕРЕТВОРЮВАЧ ДВІЙКОВОГО КОДУ В ОДНОПОЛЯРНІ ОБОРОТНІ КОДИ UA 72952 U UA 72952 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначається для використання в інформаційних обчислювальних системах, в дискретних перетворювачах координат, у системах з функціональними перетворювачами дискретної інформації. Перетворювач двійкового коду, що вміщує регістр входу, який виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістра з'єднані з входами пристрою, постійний запам'ятовуючий пристрій (ПЗП), виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістра входу, виходи якого з'єднані з виходами пристрою, керуючий вхід регістра входу з'єднаний з прямим виходом керуючого тригера, а інверсний вихід тригера з'єднаний з керуючим входом ПЗП, вхід керуючого тригера з'єднаний з першим керуючим входом пристрою, вхід «скид» регістра входу з'єднаний з входом пристрою «скид» [1]. Недоліком даного перетворювача є складність формування для ключової двійкової комбінації послідовного набору однополярних оборотних кодів з n розрядністю 3, 5, 7, 11, 13. Найближчим аналогом до запропонованого пристрою є перетворювач двійкового коду в однополярні оборотні коди [2], який містить регістр входу, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістра з'єднані з входами пристрою, ПЗП, виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістра входу, керуючий вхід регістра входу з'єднаний з прямим виходом керуючого тригера, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, вхід керуючого тригера з'єднаний з першим керуючим входом пристрою, вхід «скид» регістра входу з'єднаний з входом пристрою «скид», входи комбінаційної схеми адреси з'єднані з відповідними виходами регістра входу, а керуючий вхід комбінаційної схеми адреси з'єднаний з інверсним виходом тригера, вихід комбінаційної схеми адреси з'єднаний з інформаційними входами блока вентилів, виходи якого з'єднані з відповідними входами ПЗП, а керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з другим керуючим входом пристрою, входи «скид» керуючого пристрою та керуючого тригера з'єднані з входами «скид» пристрою. Недоліком даного перетворювача є низька надійність. В основу корисної моделі поставлено задачу підвищення надійності шляхом схемотехнічного вирішення. Поставлена задача вирішується тим, що у перетворювач додатково введено кодові шини "вхід/вихід", які з'єднані з кодовими інформаційними входами регістра входу, та з виходами блока МДП-ключів, входи якого підключено до відповідних виходів регістра входу, а керуючий вхід підключений до виходу диференціюючого ланцюга, вхід якого підключений до виходу інвертора, вхід якого підключений до прямого виходу керуючого тригера, забезпечено зменшення кількості контактів, зумовлену об'єднанням шин входів та виходів, по яким інформація вхідна та вихідна з'являється роздільно у часі, завдяки запропонованому рішенню для всіх ознак, які вказані у частині формули корисної моделі, що відрізняється, і виявляють в процесі взаємодії характерні їм відомі властивості, що дають кожен із них окремо відомий позитивний ефект. Отже, забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю вказаних ознак, що задовольняє критерій «суттєві відмінності». На кресленні зображена структурна схема перетворювача двійкового коду в однополярні оборотні коди. Перетворювач двійкового коду в однополярні оборотні коди містить регістр входу 1, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістра 1 з'єднані з входами пристрою, постійного запам'ятовуючого пристрою (ПЗП), а виходи з'єднані з відповідними входами комбінаційної схеми адреси 2, блок вентилів 3, інформаційні входи якого з'єднані з виходом комбінаційної схеми адреси 2, а його виходи з'єднані з відповідними входами ПЗП 4, виходи якого з'єднані через блок елементів АБО 5 з відповідними лічильними входами регістра входу 1, керуючий вхід регістра входу 1 з'єднаний з прямим виходом керуючого тригера 6, а інверсний вихід керуючого тригера 6 з'єднаний з керуючим входом 7 ПЗП 4 та з дозволяючим входом 8 комбінаційної схеми адреси 2, вхід керуючого тригера 6 з'єднаний з першим керуючим входом 9 пристрою. Керуючі входи блока вентилів 3 з'єднані з відповідними виходами керуючого пристрою 10, вхід якого з'єднаний з керуючим входом 11 пристрою, вхід «скид» пристрою з'єднаний з входами «скид» регістра входу 1, керуючого тригера 6, керуючого пристрою 10, крім того прямий вихід тригера 6 з'єднаний з входом додатково введеного інвертора 12, вихід якого підключений до входу диференціюючого ланцюга 13, вихід якого підключений до керуючого входу блока МДП - ключів 14, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра 1, інформаційні виходи блока МДП-ключів 14 з'єднані з 1 UA 72952 U 5 інформаційними входами вхідного регістра 1 і є «входом/виходом» перетворювача двійкового коду в однополярні коди. При проектуванні перетворювачів двійкового коду в однополярні оборотні коди, на ряду з традиційними етапами розробки включаються наступні: - заздалегідь складається таблиця перетворення вхідної двійкової кодової комбінації та відповідних коректуючих констант до неї, по яким будується ПЗП та група елементів АБО; - значення кодових констант для коректування відповідної двійкової кодової послідовності визначаються за формулою A Bi i 10 15 , (1) де А - вхідна кодова послідовність; Ві - вихідна кодова послідовність; Δі - коригуюча константа. З формули (1) видно, що завдяки властивості операції додавання по mod 2 вихідна кодова послідовність Ві визначається Bi A i , (2) а зворотна вхідна кодова послідовність відповідно A i Bi 20 25 30 35 40 . (3) Враховуючи, що для формування А, В використовуються однакові константи Δ і та порозрядне перетворення (підтверджує аналіз формул (1), (2), (3)), тоді для зменшення загального об'єму пам'яті рекомендується: - по-перше, вхідний двійковий код та вихідний код перетворювача представляти однаковою розрядністю; - по-друге, коди розбивати на відповідні тетради [2]; - константи представляти чотирирозрядними кодами, які є результатами додавання по mod 2 відповідних тетрад для обох зазначених кодових послідовностей. Наприклад, нехай для перетворення 16 розрядна вхідна двійкова кодова послідовність має вигляд: А - 0001100001001110, а відповідні вихідні n - розрядні кодові послідовності однополярних кодів Ві: В3 - 110; В5 - 11101; В7 - 1110010; В11 - 11100010010; В13 - 111100110101. Згідно із зазначеними вище рекомендаціями, відповідні кодові послідовності, які представляються однаковою розрядністю та розбиті на тетради, мають наступний вигляд А - 0001_1000_0100_1110 В3 - 0000000000000110; - 0000_0000_0000_0110; В5 - 0000000000011101; - 0000_0000_0001_1101; В7 - 0000000001110010; - 0000_0000_0111_0010; В11 - 0000011100010010; - 0000_0111_0001_0010; В13 - 0000111100110101; - 0000_1111_0011_0101. Для кожної тетради в таблиці наведені значення коректуючих констант, що визначалися за формулою (1). Таблиця Тетради Значення тетрад кодових констант відповідної двійкової кодової послідовності код А1 код А2 код А3 код А4 0001 1000 0100 1110 код Δі Δ1_3 Δ2_3 Δ3_3 Δ4_3 константи для В3 код Δі константи для В5 код Δі константи для В7 код Δі константи для В11 код Δі константи для В13 0001 Δ1_5 0001 Δ1_7 0001 Δ1_11 0001 Δ1_13 0001 1000 Δ2_5 1000 Δ2_7 1000 Δ2_11 1111 Δ2_13 0111 0100 Δ3_5 0101 Δ3_7 0011 Δ3_11 0101 Δ3_13 0111 1000 Δ4_5 0011 Δ4_7 1100 Δ4_11 1100 Δ4_13 1011 де і=1 - старша тетрада; і=2, і=3 середні тетради, і=4 - молодша тетрада; j - номер, який відповідає перетвореному коду. 2 UA 72952 U 5 10 15 20 25 30 35 40 45 50 55 60 Надійність перетворювачів, які створюються у вигляді інтегральних мікросхем підвищується тому, що інтенсивність відмов λ контактних вузлів всередині схеми на три, ..., чотири порядки менші в порівнянні з формуванням зовнішніх контактних вузлів. Відомо [2], що основними причинами відмови приладів при зборці кристалів в корпус та установці на друковану плату є недостатня механічна міцність контактів, мала адгезія виводів до контактної площадки і останньої до підложи, деградації контактного опору через взаємної дифузії металів з утворенням інтерметалевих фаз і пустот, або прихованого технологічного дефекту. Під контактним вузлом приймається система: струмоведуча площина металізації термокомпресія - провідник - контактний вивід корпусу - міжз'єднання до струмоведучої площадки друкованої плати. Припустимо, інтенсивність відмов кожного контактного вузла при операціях: -6 - термокомпресія провідника до металізованої площадки дорівнює λ 1=10 , -6 - термокомпресія провідника до контакту площини корпусу дорівнює λ2=10 , -6 - контакт виводів корпусу IС до друкованої плати дорівнює λ3=10 . Тоді загальна інтенсивність відмови одного контактного вузла дорівнює -6 -6 -6 -6 λ з=λ1+λ2+λ3=10 +10 +10 =3·10 . Наприклад, у перетворювачах при обробці інформаційних операндів з розрядністю 32 загальна інтенсивність відмов контактних вузлів дорівнює -6 -6 2·32·λ3=32·3·10 =192·10 . Тоді середній час безвідмовної роботи Тр перетворювача дорівнює Tр=(1/Σλi). (1) Припустимо, що для перетворювачів з числом контактних вузлів 32 інтенсивність відмови -6 пристрою - найближчого аналога дорівнює λзпр=192·10 , а перетворювача двійкового коду в однополярні коди з розробленою новою схемотехнікою - зменшується число контактних вузлів в 2 рази, тоді -6 λз вин=(192/2)·10 , тобто за рахунок зменшення кількості контактних вузлів інтенсивність відмови пристрою зменшується в 2 рази. Причому порівняння проводиться при ідентичних умовах формування елементів конструкції, технології виготовлення перетворювачів і мають однакову інтенсивність відмови. Це забезпечує збільшення середнього часу безвідмовної роботи перетворювача двійкового коду в однополярні коди, відповідно [2] в Тр вин/Тр пр=(1/Σλi)вин/(1/Σλi)пр рази, (2) де Тр пр - середній час безвідмовної роботи перетворювача-прототипу; Тр вин - середній час безвідмовної роботи перетворювача двійкового коду в однополярні коди з розробленою новою схемотехнічною реалізацією. Тоді для наведеного прикладу середній час безвідмовної роботи збільшується в -6 -6 Твин/Тпр=192·10 /(192/2)·10 =2 рази. Отже, зменшення кількості контактних вузлів (припустимо) в 2 рази при збереженні паралельної обробки операндів високої точності зменшується середній час безвідмовної роботи в 2 рази. Перетворювач двійкового коду в однополярні оборотні коди працює таким чином. Перед перетворенням вхідного двійкового коду, що надходить на вхід пристрою, імпульсом «скид» пристрою установлюються в початковий стан регістр 1, тригер 6, керуючий пристрій 10. Імпульс запуску 9 надходить на лічильний вхід тригера 6 й на виході регістра 1 встановлюється вхідна кодова послідовність інформації. Дозволяючі входи 7, 8 ПЗП та комбінаційної схеми адреси 2 з'єднані з інверсним виходом тригера 6 відповідно. При надходженні керуючого імпульсу 11 на вхід керуючого пристрою (КП) 10, на відповідному виході якого з'являється імпульс, який дозволить імпульсу з виходу комбінаційної схеми адреси 2 пройти через блок вентилів 3 й зчитати із ПЗП 4 код значення відповідної коректуючої константи, який через блок елементів АБО 5 надходить на відповідні лічильні входи регістра 1. Під дією одиниць коду константи відбувається перекидання станів тригерів регістра 1 в інший стан, тобто відбувається сумування по mod 2 вхідного двійкового коду та відповідного коду коректуючої константи й на виході регістра 1 з'являється відповідний однополярний оборотний код, який надходить на інформаційні входи блока МДП-ключів 14, інформаційний код з'явиться на виході блока МДПключів 14 після надходження керуючого сигналу a(t+At) з прямого виходу керуючого тригера 6 через інвертор 12 і диференціюючого вузла 13. Отже, перевагою перетворювача двійкового коду в однополярні оборотні коди є збільшення надійності в 2 рази. 3 UA 72952 U Література: 1. А. С. № 781806, МПК G06F 5/02. 2. Патент № 44833 Перетворювач двійкового коду в однополярні оборотні коди, МПК G06F 5/00 Лукашенко В.М. та інші. 5 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 20 25 Перетворювач двійкового коду в однополярні оборотні коди, що містить регістр входу, який виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістра з'єднані з входами пристрою, постійного запам'ятовуючого пристрою (ПЗП), виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістра входу, керуючий вхід регістра входу з'єднаний з прямим виходом керуючого тригера, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, вхід керуючого тригера з'єднаний з першим керуючим входом пристрою, вхід "скид" регістра входу з'єднаний з входом пристрою "скид", входи комбінаційної схеми адреси з'єднані з відповідними виходами регістра входу, а керуючий вхід комбінаційної схеми адреси з'єднаний з інверсним виходом керуючого тригера, вихід комбінаційної схеми адреси з'єднаний з інформаційними входами блока вентилів, виходи якого з'єднані з відповідними входами постійно запам'ятовуючого пристрою, а керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з другим керуючим входом пристрою, входи "скид" керуючого пристрою та керуючого тригера з'єднані з входами "скид" пристрою, який відрізняється тим, що прямий вихід тригера з'єднаний з входом додатково введеного інвертора, вихід якого підключений до входу введеного диференціюючого ланцюга, вихід якого підключений до керуючого входу введеного блока МДПключів, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра, а інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами вхідного регістра і є "входом/виходом" перетворювача. Комп’ютерна верстка І. Скворцова Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюConverter of binary code to unipolar inverse codes

Автори англійськоюLukashenko Andrii Hermanovych, Lukashenko Valentyna Maksymivna, Rudakov Kostiantyn Serhiiovych, Lukashenko Dmytro Andriiovych, Verbickiy Oleksandr Sergiyovich, Lukashenko Volodymyr Andriiovych, Lukashenko Volodymyr Andriiovych

Назва патенту російськоюПреобразователь двоичного кода в однополярные оборотные коды

Автори російськоюЛукашенко Андрей Германович, Лукашенко Валентина Максимовна, Рудаков Константин Сергеевич, Лукашенко Дмитрий Андреевич, Вербицкий Александр Сергеевич, Лукашенко Владимир Андреевич, Лукашенко Владимир Андреевич

МПК / Мітки

МПК: G06F 5/00

Мітки: двійкового, перетворювач, оборотні, коду, однополярні, коді

Код посилання

<a href="https://ua.patents.su/6-72952-peretvoryuvach-dvijjkovogo-kodu-v-odnopolyarni-oborotni-kodi.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійкового коду в однополярні оборотні коди</a>

Попередній патент: Спосіб визначення наночастинок в повітрі робочої зони

Наступний патент: Пасовий привід

Випадковий патент: Установка для дослідження гнучких тягових органів транспортерів і передач