Перетворювач коду фібоначі в двійковий код

Номер патенту: 58165

Опубліковано: 15.07.2003

Автори: Макаренко Ганна Миколаївна, Купрейчик Ірина Валеріївна, Какурін Микола Яковлевич

Формула / Реферат

Перетворювач коду Фібоначі в двійковий код, який складається з генератора імпульсів, групи n тригерів стану, багатоканального формувача еквівалентів, першого, другого і третього комбінаційних суматорів першого і другого ступеня, накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з відповідними другими входами комбінаційного двійкового суматора, перші входи якого з'єднані з відповідними виходами третього комбінаційного суматора другого ступеня, входи першого і другого доданку якого з'єднані з відповідними виходами першого і другого комбінаційних суматорів першого ступеня, виходи комбінаційного двійкового суматора з'єднані з відповідними входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, прямий вихід якого з'єднаний з входами синхронізації всіх тригерів стану, виходи яких з'єднано з відповідними входами формувача еквівалентів, який відрізняється тим, що виходи формувачів сусідніх каналів з'єднано з відповідними входами першого і другого доданку комбінаційних суматорів першого ступеня, входи тригерів стану є відповідними входами перетворювача.

Текст

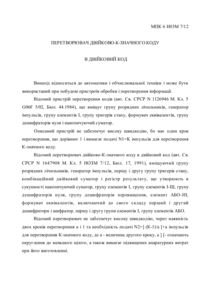

Перетворювач коду Фібоначі в двійковий код, який складається з генератора імпульсів, групи п тригерів стану, багатоканального формувача еквівалентів, першого, другого і третього комбінаційних суматорів першого і другого ступеня, накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційного двійкового суматора, перші входи Винахід стосується автоматики і обчислювальної техніки і може бути використаний при побудові пристроїв обробки і перетворення інформації Відомий перетворювач р-коду Фібоначі в двійковий код (авт св СРСР №662932 М Кл 2 G06F5/02, Бюл 18, 1979) вміщує п-розрядний регістр для збереження р-коду Фібоначі, L комутаторів групи розрядів, розподільник імпульсів для управління процесом перетворення та двійковий накопичувальний суматор для послідовного накопичення двійкових еквівалентів Такий перетворювач не забезпечує достатньо високої швидкодії тому, що максимальна КІЛЬКІСТЬ тактів перетворення р-коду Фібоначі дорівнює р+1 і-макс а також має великі апаратні ви трати тому, що КІЛЬКІСТЬ І_ комутаторів групи розрядів знаходиться з нерівності 2 L + 1 >cpp(n), де cp(n) n - по порядку число р-коду Фібоначі, р-число, що характеризує конкретну множину чисел р-коду Фібоначі Найбільш близьким по сукупності ознак щодо заявленого є перетворювач двійково-К-значного коду в двійковий код (Патент України №44423А якого з єднані з ВІДПОВІДНИМИ виходами третього комбінаційного суматора другого ступеня, входи першого і другого доданку якого з'єднані з ВІДПОВІДНИМИ виходами першого і другого комбінаційних суматорів першого ступеня, виходи комбінаційного двійкового суматора з'єднані з ВІДПОВІДНИМИ входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, прямий вихід якого з'єднаний з входами синхронізації всіх тригерів стану, виходи яких з'єднано з ВІДПОВІДНИМИ входами формувача еквівалентів, який відрізняється тим, що виходи формувачів сусідніх каналів з'єднано з ВІДПОВІДНИМИ входами першого і другого доданку комбінаційних суматорів першого ступеня, входи тригерів стану є ВІДПОВІДНИМИ входами перетворювача МПК7Н03М7/12, Бюл №2, 2002), вміщуючий групу з п розрядних регістрів зсуву, де п - розрядність коду, що перетворюється, генератор імпульсів, групу з n-тригерів стану, комбінаційний двійковий суматор і регістр результату, що створюють в сукупності накопичувальний суматор, перший, другий і третій комбінаційні суматори першого і другого ступеня, багатоканальний формувач еквівалентів, який містить у кожному каналі шифратор, підсумовувальний лічильник імпульсів та комбінаційний зсувач Описаний перетворювач не забезпечує достатньо високої швидкодії через необхідність подачі N2=4 імпульсів для перетворення коду і має великі апаратні витрати внаслідок того, що в кожному каналі формувача еквівалентів містяться шифратор, підсумовувальний лічильник імпульсів та комбінаційний зсувач, а для збереження двійково-Кзначного коду перетворювач повинен мати п розрядних регістрів зсуву В основу винаходу поставлена задача створення такого перетворювача р-коду Фібоначі в двійковий код, в якому нове схемне рішення дозволило б при збільшенні швидкодії істотно зменшити його апаратні витрати ю (О 00 ю 58165 Такий технічний результат може бути досягнувиходи комбінаційного двійкового суматора 4 в тий, якщо в перетворювачі коду Фібоначі в двійконакопичувальному суматорі 6 з'єднані з ВІДПОВІДвий код, який складається з генератора імпульсів, НИМИ входами регістра результату 5, синхровхід групи з п тригерів стану, багатоканального формуякого з'єднано з прямим затриманим виходом ПЗ вача еквівалентів, кожний канал якого містить шигенератора імпульсів 1, прямий вихід П якого з'єдфратор, з першого, другого і третього комбінаційнано з входами синхронізації усіх тригерів стану них суматорів першого і другого ступеня, 2i-2s, виходи яких з'єднано з ВІДПОВІДНИМИ входанакопичувального суматора, виконаного з комбіми формувача еквівалентів З1-З4, виходи формунаційного двійкового суматора та регістра резульвачів З1-З4 сусідніх каналів з'єднано з ВІДПОВІДНИМИ тату, виходи якого є виходами перетворювача і входами першого і другого доданку в комбінаційз'єднані з ВІДПОВІДНИМИ другими входами комбінаних суматорах 7і і 7 2 першого ступеня, входи триційного двійкового суматора, перші входи якого герів стану 2i-2s є ВІДПОВІДНИМИ входами перетвоз'єднані з ВІДПОВІДНИМИ виходами третього комбірювача наційного суматора другого ступеня, входи першоЛанцюги ініціювання та скидання на кресленні го і другого доданку якого з'єднані з ВІДПОВІДНИМИ не наведені виходами першого і другого комбінаційних суматоПристрій працює слідуючим чином рів першого ступеня, виходи комбінаційного двійЯкщо в конкретному випадку п=8, р=1, І_=4, то кового суматора в накопичувальному суматорі діапазон зміни вхідного коду знаходиться від 0 до з'єднані з ВІДПОВІДНИМИ входами регістра резульі=8 тату, синхровхід якого з'єднаний з прямим затри^ W , -С, = 5 4 ю . бо вага W, і-го розряду 1-коду маним виходом генератора імпульсів, прямий ви1=1 хід якого з'єднаний з входами синхронізації всіх (р=1) Фібоначі дорівнює W i = W 2 = 1 , W 3 = 2 , W 4 =3, тригерів стану, виходи яких з'єднано з ВІДПОВІДНИW5=5, W6=8, W7=13, W8=21 МИ входами шифраторів в каналах формувача В перетворювачі коду Фібоначі в двійковий еквівалентів, ВІДПОВІДНО ДО винаходу, виходи шикод, в каналах формувачі З1-З4 еквівалентів, реаліфраторів сусідніх каналів з'єднані з ВІДПОВІДНИМИ зують ВІДПОВІДНО функції (1)-(4) входами першого і другого доданку комбінаційних Si=W 2 C 2 +WiCi (1) суматорів першого ступеня, входи тригерів стану є S2=W4C4+W3C3 (2) ВІДПОВІДНИМИ входами перетворювача S3=W6C6+W5C5 (3) S^WsCs+WyC? (4) Таким чином, завдяки новим зв'язкам між де C-i-Cs - значення (0 або 1) тригерів стану 1\елементами схеми створено перетворювач у новій 28 якості, що дозволяє підвищити швидкодію переПеретворення війкових кодів (Сі,С2), (Сз,С4), творення з чотирьох тактів до одного та істотно (Сб.Сє), (C7,Cs), що можуть приймати в кожній парі зменшити його апаратні витрати чотири значення 00, 01, 10, 11 виконується в ВІДНа фігурі зображена структурна схема переПОВІДНОСТІ з законом функціонування формувача творювача коду Фібоначі в двійковий код для р=1, еквівалентів З1-З4 (див таблицю) п=8 Перетворення коду Фібоначі відбувається за Перетворювач містить генератор імпульсів 1, один такт Формувачі еквівалентів З4-З1 за допомовміщуючий прямий П та прямий затриманий ПЗ гою шифраторів перетворюють ДВІЙКОВІ КОДИ тривиходи, групу п тригерів стану 2i-2s, багатоканальгерів стану (С8 С7), (С6 С5), (С4 С3), (С2 Сі) в ДВІЙний (І_=4) формувач З1-З4 еквівалентів, виконаний КОВІЙ код складової еквіваленту Ує-Уі згідно з шифратора, комбінаційний двійковий суматор 4 таблиці та регістр результату 5, що створюють в сукупності Складові еквівалентів, що з'являться на вихонакопичувальний суматор 6, перший 7і другий 7 2 дах першого та другого формувачів еквівалентів Зі та третій 8 комбінаційні суматори першого і другоі 3 2 третього та четвертого формувачів еквіваленго ступеня тів Зз і З4 будуть підсумовані ВІДПОВІДНО першим 7і Виходи регістра результату 5 є виходами пета другим 7 2 комбінаційними суматорами першого ретворювача і з'єднані з ВІДПОВІДНИМИ другими ступеня входами комбінаційного двійкового суматора 4, За допомогою комбінаційного суматора 8 друперші входи якого з'єднані з ВІДПОВІДНИМИ виходагого ступеня суми еквівалентів з виходів суматорів ми третього комбінаційного суматора 8 другого 7і та 7 2 будуть складені та надійдуть на перші ступеня, входи першого і другого доданку якого входи комбінаційного двійкового суматора 4 в наз'єднані з ВІДПОВІДНИМИ виходами першого 7і і друкопичувальному суматорі 6 гого 7г комбінаційних суматорів першого ступеня, Таблиця С6С5 С4СЗ о о о о о о о о о о о о о о о о о о о о С2С1 00 01 10 11 00 Десятковий Двійковий КОД еквіваленту Значення код еквіваленвихідних розрядів ту S10 У6У5 У4 Уз У2 Уі 0 0000 1 0001 1 0001 2 0010 0 0000 о о о о о о о о о о С8С7 о о о о о о о о о о Значення Розрядів 58165 Продовження таблиці Значення Розрядів С6С5 00 00 00 00 01 10 11 00 00 00 00 С4СЗ 01 10 11 00 00 00 00 00 00 00 00 С2С1 ooooooooooo ooooooooooo С8С7 00 00 00 00 00 00 00 00 01 10 11 В першому ж такті накоплена сума еквівалентів буде складена з початковою накопленою сумою еквівалентів, яка дорівнює нулю Тригери стану 2s-2i та регістр результату 5 перед початком перетворення коду Фібоначі в двійковий код потрібно обнулити Запис коду Фібоначі в тригери стану 2s-2i виконується перепадом 0-1 прямого імпульсу з виходу П генератора імпульсів 1, запис накопиченої суми еквівалентів в регістр 5 накопичувального суматора 6 виконується перепадом 1-0 імпульсу з прямого затриманого виходу ПЗ генератора 1 Розглянемо роботу пристрою на наступному прикладі Нехай необхідно перетворити вхідний восьмирозрядний 1-код Фібоначі (р-1) Ао=10001010=25ю, який знаходиться в тригерах стану 2s-2i ВІДПОВІДНО Формувач еквівалентів З1-З4 реалізують в нашому прикладі функції (5)-(8) Si=1 С 2 +1 Сі (5) S 2 =3 C4+2 Сз (6) S 3 =8 С 6 +5 С 5 (7) S4 = 2 1 C 8 + 1 3 C 7 (8) Після ПОЯВИ першого імпульсу з виходу Пгенератора імпульсів 1 перепадом 0-1 відбудеться запис вхідного коду Фібоначі Ао=10001010 в тригери стану 2s-2i які перед початком перетворення були обнулені В результаті відбудеться зміна стану тригерів С 2 Сі з 00 на 10, С 4 С 3 з 00 на 10, С 8 С 7 з 00 на 10 Стан тригерів СєСб залишиться тим же 00 В результаті цього коди тригерів стану 2s-2i надійдуть на входи формувачів 3 4 -3і CsC7=10 на входи формувача 3 4 , СєСб=00 на входи формувача Зз, С 4 Сз=10 на входи формувача 3 2 , С 2 Сі=10 на входи формувача Зі і далі перетворяться, згідно таблиці, на складові еквівалентів S 4 = 2 1 I O = 0 1 0 1 0 1 2 , Десятковий Двійковий КОД еквіваленту Значення код еквіваленвихідних розрядів ту S10 У6У5 У 4 Уз У 2 Уі 2 00 0010 3 00 0011 5 00 0101 0 00 0000 5 00 0101 8 00 1000 13 00 1101 0 00 0000 13 00 1101 21 01 0101 34 10 0010 S 3 = 0 i o = 0 0 0 0 0 0 2 , S 2 = 3 i o = 0 0 0 0 1 1 2 , S i = 1 io=0000012 Комбінаційний двійковий суматор першого ступеня 7 2 в результаті додавання складових еквівалентів S 4 та S3 видасть на своїх виходах двійковий код числа S 4 +S3=21 ю+0ю=010101 2 , що надійде на входи другого доданку третього комбінаційного суматора 8 другого ступеня В результаті додавання складових еквівалентів S 2 і S i перший комбінаційний суматор першого ступеня 7і видасть на своїх виходах двійковий код числа S 2 +Si=3io+1io-4io=000100 2 , що надійде на входи першого доданку третього комбінаційного суматора 8 другого ступеня В результаті додавання складових еквівалентів 4 ю = 0 0 0 1 0 0 2 т а 21ю=010101 2 двійковий код числа 21 іо+4іо=25ю=011001 2 з'явиться на виходах третього комбінаційного суматора 8 другого ступеня і надійде також на перші входи комбінаційного двійкового суматора 4 в накопичувальному суматорі 6 Після приходу прямого затриманого імпульсу ПЗ перепадом 1-0 в регістр 5 буде записаний результат складання числа 25ю=011001 2 з початковою накопленою сумою еквівалентів, що дорівнює нулю В результаті число 25ю=011001 2 з'явиться на виходах регістра 5 і на виходах перетворювача кодів На цьому процес перетворення коду Фібоначі в двійковий код закінчується Перед кожним наступним перетворенням необхідно обновити регістр 5 результату Пристрій може буде використаний для перетворення р-коду Фібоначі представленого як в мінімальній, так і в не мінімальній формі Швидкодія пристрою, що пропонується, не залежить від розрядності перетворюваного коду Фібоначі і не перевищує одного такту 58165 Комп'ютерна верстка О Воробей Підписано до друку 05 08 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюFibonacci-to-binary code converter

Автори англійськоюKachurin Mykola Yakovych, Makarenko Hanna Mykolaivna

Назва патенту російськоюПреобразователь кода фибоначчи в двоичный код

Автори російськоюКачурин Николай Яковлевич, Макаренко Анна Николаевна

МПК / Мітки

МПК: H03M 7/02

Мітки: коду, перетворювач, код, двійковий, фібоначі

Код посилання

<a href="https://ua.patents.su/4-58165-peretvoryuvach-kodu-fibonachi-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач коду фібоначі в двійковий код</a>

Попередній патент: Спосіб лікування рецидивів плоскоклітинного раку анальної області

Наступний патент: Спосіб профілактики утробної гіпоксії плода та лікування нейро-циркуляторної астенії у вагітних жінок

Випадковий патент: Спосіб передпосівного обробітку грунту