Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями

Номер патенту: 91894

Опубліковано: 25.07.2014

Автори: Горбенко Іван Дмитрович, Горбенко Юрій Іванович, Краснобаєв Віктор Анатолійович, Замула Олександр Андрійович, Янко Аліна Сергіївна

Формула / Реферат

Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями, що містить перший, другий і третій суматори, перший, другий і третій регістри, при цьому, перший (шина подачі значення позиційного двійкового коду) вхід пристрою підключено до першого входу першого регістра, перший вихід якого підключено до першого входу першого суматора, а також до перших входів другого та третього регістрів, а перший вихід першого суматора підключено до другого входу першого регістра, перший вихід другого суматора підключено до другого входу другого регістра, вихід якого підключено до першого (шина результату перетворення позиційного двійкового коду у лишок за першим модулем) виходу пристрою, а також до першого входу другого суматора, перший вихід третього суматора підключено до другого входу третього регістра, вихід якого підключено до другого (шина результату перетворення позиційного двійкового коду у лишок за другим модулем) виходу пристрою, а також до першого входу третього суматора, який відрізняється тим, що в нього введені перший, другий, третій, четвертий і п'ятий елементи І, тригер і блок множення, при цьому, другий (шина подачі значення першого модуля) вхід пристрою підключено до першого входу блока множення, вихід якого підключено до другого входу першого суматора, другий вхід пристрою підключено також до другого входу другого суматора, третій (шина подачі значення другого модуля) вхід пристрою підключено до другого входу блока множення, а також до другого входу третього суматора, четвертий (тактовий) вхід пристрою підключено до перших входів першого та другого елементів І, до других входів яких підключено другий вихід першого суматора, вихід першого елемента І підключено до третього входу першого регістра, а вихід другого елемента І підключено до першого входу третього елемента І і до входу тригера, вихід якого підключено до другого входу третього елемента І, а також до третіх входів другого та третього регістрів, вихід третього елемента І підключено до перших входів четвертого та п'ятого елементів І, до других входів яких підключено відповідно другі виходи другого та третього суматорів, виходи четвертого та п'ятого елементів І підключено до четвертих входів відповідно другого та третього регістрів.

Текст

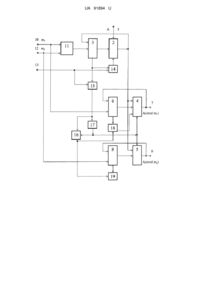

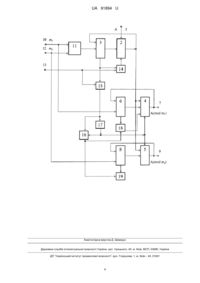

Реферат: Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями містить суматори, регістри, при цьому входи і виходи пристрою, елементи І, тригер і блок множення. UA 91894 U (54) ПРИСТРІЙ ДЛЯ ПЕРЕТВОРЕННЯ ПОЗИЦІЙНОГО ДВІЙКОВОГО КОДУ У ЛИШКИ ЗА ДВОМА ДОВІЛЬНИМИ МОДУЛЯМИ UA 91894 U UA 91894 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель (пристрій) належить до області автоматики та обчислювальної техніки і може бути використано у системах і засобах обробки цифрової інформації, що функціонують у непозиційній системі числення класу лишків (КЛ). Відомий пристрій (аналог), що застосовується для перетворення позиційного двійкового коду А у лишок за довільним модулем mi, КЛ (а.с. СССР № 864278, МПК G 06 F 5/02, 1978 р.). Пристрій містить блок множення, блок порівняння, регістри, комбінаційний суматор елементи І та АБО. Недолік аналогу - низькі функціональні можливості пристрою. Відомий пристрій (аналог), що застосовується для перетворення позиційного двійкового коду А у лишок за довільним модулем mi, КЛ (а.с. СССР № 1084798, МПК G 06 F 11/08, 1978 р.). Пристрій-аналог містить блоки множення, блок порівняння, регістри, комбінаційний суматор елементи І та АБО. Недолік аналога - низькі функціональні можливості пристрою. Відомий пристрій (аналог), що застосовується для перетворення позиційного двійкового коду А у лишок за довільним модулем mi, КЛ (а.с. СССР № 1185339, МПК G 06 F 5/02, 1985 р.). Аналог містить блок порівняння, вхідний та вихідний регістри, суматор елементи І та АБО, прийомні регістри. Недолік аналога - низькі функціональні можливості пристрою. Відомий пристрій (аналог), що застосовується для перетворення позиційного двійкового коду А у лишок за довільним модулем mі, КЛ (а.с. СССР № 1105895, МПК G 06 F 11/08, 1983 р.). Пристрій для перетворення позиційного двійкового коду у лишок за довільним модулем mi, містить лічильник, до першого входу якого підключено перший (установчий) вхід пристрою, блок порівняння та перший елемент І, причому перший вхід першого елемента І є другим (тактовим) входом пристрою, вихід першого елемента І підключено до другого (рахункового) входу лічильника, перший вхід блока порівняння є входом подачі значення модуля mi. Недолік аналога - низькі функціональні можливості пристрою. Найбільш близьким за технічною суттю до запропонованої корисної моделі є пристрій за а.с. СССР № 396688, МПК G 06 F 11/08, 1971 р.). Пристрій містить перший, другий і третій суматори, , перший, другий і третій регістри, при цьому перший (шина подачі значення позиційного двійкового коду) вхід пристрою підключено до першого входу першого регістру, пёрший вихід якого підключено до першого входу першого суматора, а також до перших входів другого та третього регістрів, а перший вихід першого суматора підключено до другого входу першого регістра, перший вихід другого суматора підключено до другого входу другого регістра, вихід якого підключено до першого (шина результату перетворення позиційного двійкового коду у лишок за першим модулем) виходу пристрою, а також до першого входу другого суматора, перший вихід третього суматора підключено до другого входу третього регістра, вихід якого підключено до другого (шина результату перетворення позиційного двійкового коду у лишок за другим модулем) виходу пристрою, а також до першого входу третього суматора. Недолік найбільш близького аналога - низькі функціональні можливості пристрою. В основу запропонованої корисної моделі поставлена задача розширити функціональні можливості пристрою за рахунок перетворення позиційного двійкового коду А у лишки за двома m1 і m2 довільними модулями КЛ. Поставлена задача вирішується тим, що у пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями, що містить перший, другий і третій суматори, перший, другий і третій регістри, при цьому перший (шина подачі значення позиційного двійкового коду) вхід пристрою підключено до першого входу першого регістра, перший вихід якого підключено до першого входу першого суматора, а також до перших входів другого та третього регістрів, а перший вихід першого суматора підключено до другого входу першого регістра, перший вихід другого суматора підключено до другого входу другого регістра, вихід якого підключено до першого (шина результату перетворення позиційного двійкового коду у лишок за першим модулем) виходу пристрою, а також до першого входу другого суматора, перший вихід третього суматора підключено до другого входу третього регістра, вихід якого підключено до другого (шина результату перетворення позиційного двійкового коду у лишок за другим модулем) виходу пристрою, а також до першого входу третього суматора, згідно з корисною моделлю, додатково введено перший, другий, третій, четвертий і п'ятий елементи І, тригер і блок множення, при цьому другий (шина подачі значення першого модуля) вхід пристрою підключено до першого входу блока множення, вихід якого підключено до другого входу першого суматора, другий вхід пристрою підключено також до другого входу другого суматора, третій (шина подачі значення другого модуля) вхід пристрою підключено до другого входу блока множення, а також до другого входу третього суматора, четвертий (тактовий) вхід 1 UA 91894 U 5 10 15 20 25 30 35 40 45 50 55 60 пристрою підключено до перших входів першого та другого елементів І, до других входів яких підключено другий вихід першого суматора, вихід першого елемента І підключено до третього входу першого регістру, а вихід другого елемента І підключено до першого входу третього елемента І і до входу тригера, вихід якого підключено до другого входу третього елемента І, а також до третіх входів другого та третього регістрів, вихід третього елемента І підключено до перших входів четвертого та п'ятого елементів І, до других входів яких підключено відповідно другі виходи другого та третього суматорів, виходи четвертого та п'ятого елементів І підключено до четвертих входів відповідно другого та третього регістрів. Введення вказаних ознак дозволяє розширити функціональні можливості пристрою за рахунок перетворення позиційного двійкового коду А у лишки за двома m1 і m2 довільними модулями КЛ. На кресленні представлена блок-схема корисної моделі. Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями містить: 1 - перший (шина подачі значення позиційного двійкового коду А) вхід пристрою; 2 - перший регістр; 3 - перший суматор; 4 - другий регістр; 5 - третій регістр; 6 другий суматор; 7 - перший (шина результату перетворення позиційного двійкового коду у лишок за першим m1 модулем) вихід пристрою; 8 - третій суматор; 9 - другий (шина результату перетворення позиційного двійкового коду у лишок за другим m2 модулем) вихід пристрою; 10 другий (шина подачі значення першого m1 модуля) вхід пристрою; 11 - блок множення; 12 третій (шина подачі значення другого m2 модуля) вхід пристрою; 13 - четвертий (тактовий) вхід пристрою; 14, 15 і 16 - перший, другий і третій елементи І; 17 - тригер; 18, 19 - четвертий і п'ятий елементи І. Перший 1 (шина подачі значення позиційного двійкового коду А) вхід пристрою підключено до першого входу першого регістра 2, перший вихід якого підключено до першого входу першого 3 суматора, а також до перших входів другого 4 та третього 5 регістрів, а перший вихід першого 3 суматора підключено до другого входу першого 2 регістру, перший вихід другого 6 суматора підключено до другого входу другого 4 регістра, вихід 7 якого підключено до першого (шина результату перетворення позиційного двійкового коду у лишок за першим m1 модулем) виходу пристрою, а також до першого входу другого 6 суматора, перший вихід третього 8 суматора підключено до другого входу третього 5 регістру, вихід 9 якого підключено до другого (шина результату перетворення позиційного двійкового коду у лишок за другим m2 модулем) виходу пристрою, а також до першого входу третього 8 суматора, другий 10 (шина подачі значення першого m1 модуля) вхід пристрою підключено до першого входу блоку 11 множення, вихід якого підключено до другого входу першого 3 суматора, другий 10 вхід пристрою підключено також до другого входу другого 6 суматора, третій 12 (шина подачі значення другого m2 модуля) вхід пристрою підключено до другого входу блоку 11 множення, а також до другого входу третього 8 суматора, четвертий 13 (тактовий) вхід пристрою підключено до перших входів першого 14 та другого 15 елементів І, до других входів яких підключено другий вихід першого 3 суматора, вихід першого 14 елемента І підключено до третього входу першого 2 регістра, а вихід другого 15 елемента І підключено до першого входу третього 16 елемента І і до входу тригера 17, вихід якого підключено до другого входу третього 16 елемента І, а також до третіх входів другого 4 та третього 5 регістрів, вихід третього 16 елемента 1 підключено до перших входів четвертого 18 та п'ятого 19 елементів I, до других входів яких підключено відповідно другі виходи другого 6 та третього 8 суматорів, виходи четвертого 18 та п'ятого 19 елементів І підключено до четвертих входів відповідно другого 4 та третього 5 регістрів. Пристрій працює наступним чином. У початковому стані за входом 1 пристрою на перший регістр 2 записується число А. На другому вході 10 і третьому вході 12 пристрою виставлені коди m1 і m2 першого і другого модулів. Тригер 17, другий суматор 6 і третій суматор 8 знаходяться в нульовому стані. При подачі тактових імпульсів відбувається віднімання з числа А добутку модулів. При позитивній різниці на виході першого суматора 3 присутній одиничний сигнал, який пропускає тактовий імпульс через перший елемент І 14 і записує на перший регістр 2 результат віднімання по першому інформаційного входу. Віднімання продовжується до тих пір, поки різниця не буде негативною. У цей момент на виході переповнення першого суматора 3 формується нульовий сигнал, який закриває перший елемент І 14 і на першому регістрі 2 залишається колишній результат. Нехай тактові імпульси починають проходити через другий елемент І 15. Перший імпульс з виходу другого елемента I 15 встановлює в одиничний стан тригер 17, сигнал з прямого виходу якого записує на другий регістр 4 і третій регістр 5 лишок з виходу першого регістра 2. За наступними імпульсам з виходу другого елемента І 15, які починають проходити через третій елемент І 16, відбувається віднімання з вмісту другого регістру 4 і третього регістру 2 UA 91894 U 5 10 5 кодів першого m1 і другого m2 модулів відповідно. Управління відніманням здійснюється сигналами переповнення другого 6 і третього 8 суматорів. Коли вміст другого регістра 4 стає меншим, ніж значення першого m1 модуля, вихід переповнення суматора 6 забороняє зміну коду на другому регістрі 4 і його вміст може використовуватися як лишок по першому m1 модулю. Аналогічно, вихід переповнення третього суматора 8 визначає момент формування на третьому регістрі 5 лишку за другим m2 модулем. Таким чином запропонований пристрій дозволяє розширити функціональні можливості пристрою за рахунок перетворення позиційного двійкового коду А у лишки за двома m1 і m2 довільними модулями КЛ. Це підвищує загальну ефективність використання непозиційних кодових структур у системах та засобах, що функціонують у класі лишків. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 15 20 25 30 35 Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями, що містить перший, другий і третій суматори, перший, другий і третій регістри, при цьому, перший (шина подачі значення позиційного двійкового коду) вхід пристрою підключено до першого входу першого регістра, перший вихід якого підключено до першого входу першого суматора, а також до перших входів другого та третього регістрів, а перший вихід першого суматора підключено до другого входу першого регістра, перший вихід другого суматора підключено до другого входу другого регістра, вихід якого підключено до першого (шина результату перетворення позиційного двійкового коду у лишок за першим модулем) виходу пристрою, а також до першого входу другого суматора, перший вихід третього суматора підключено до другого входу третього регістра, вихід якого підключено до другого (шина результату перетворення позиційного двійкового коду у лишок за другим модулем) виходу пристрою, а також до першого входу третього суматора, який відрізняється тим, що в нього введені перший, другий, третій, четвертий і п'ятий елементи І, тригер і блок множення, при цьому, другий (шина подачі значення першого модуля) вхід пристрою підключено до першого входу блока множення, вихід якого підключено до другого входу першого суматора, другий вхід пристрою підключено також до другого входу другого суматора, третій (шина подачі значення другого модуля) вхід пристрою підключено до другого входу блока множення, а також до другого входу третього суматора, четвертий (тактовий) вхід пристрою підключено до перших входів першого та другого елементів І, до других входів яких підключено другий вихід першого суматора, вихід першого елемента І підключено до третього входу першого регістра, а вихід другого елемента І підключено до першого входу третього елемента І і до входу тригера, вихід якого підключено до другого входу третього елемента І, а також до третіх входів другого та третього регістрів, вихід третього елемента І підключено до перших входів четвертого та п'ятого елементів І, до других входів яких підключено відповідно другі виходи другого та третього суматорів, виходи четвертого та п'ятого елементів І підключено до четвертих входів відповідно другого та третього регістрів. 3 UA 91894 U Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюHorbenko Ivan Dmytrovych, Krasnobaiev Viktor Anatoliiovych, Zamula Oleksandr Andriiovych, Horbenko Yurii Ivanovych

Автори російськоюГорбенко Иван Дмитриевич, Краснобаев Виктор Анатольевич, Замула Александр Андреевич, Горбенко Юрий Иванович

МПК / Мітки

МПК: G06F 5/00

Мітки: довільними, двійкового, коду, пристрій, позиційного, перетворення, модулями, лишки, двома

Код посилання

<a href="https://ua.patents.su/6-91894-pristrijj-dlya-peretvorennya-pozicijjnogo-dvijjkovogo-kodu-u-lishki-za-dvoma-dovilnimi-modulyami.html" target="_blank" rel="follow" title="База патентів України">Пристрій для перетворення позиційного двійкового коду у лишки за двома довільними модулями</a>

Попередній патент: Пристрій для просочення довгомірного скловолокнистого матеріалу

Наступний патент: Спосіб комбінованої терапії вперше діагностованого деструктивного туберкульозу легень з бактеріовиділенням і хронічного обструктивного захворювання легень

Випадковий патент: Швидкодіючий реверсивний індукційно-динамічний привід комутаційного апарата