Модуль пристрою для відтворення зображення на великому екрані

Номер патенту: 14808

Опубліковано: 18.02.1997

Автори: Бойван Анатолій Васильович, Дорощенков Генадій Дмитрович, Кожем'яко Володимир Прокопович

Формула / Реферат

1. Модуль устройства для воспроизведения изображения на большом экране, содержащий два блока памяти и блок отображения в виде матрицы, анодные и катодные входы которой подключены соответственно к выходам блока анодной и блока катодной развертки, отличающийся тем, что он дополнительно содержит два контроллера блоков памяти, коммутатор - мультиплексор и блок тактовых и управляющих сигналов, тактовый выход которого подключен к тактовым входам чтения блока катодной развертки, первого и второго контроллеров блоков памяти, первый выход управления - к входу управления первого контроллера блока памяти и первому входу управления коммутатора - мультиплексора, второй выход управления - к входу управления второго контроллера блока памяти, третий и четвертый выходы управления - ко второму и третьему входам управления коммутатора -мультиплексора, пятый выход управления -к первому входу управления блока катодной развертки, шестой выход управления - к первому входу управления блока анодной развертки, седьмой выходу правления - ко вторым входам управления блока катодной и блока анодной развертки, восьмой выход управления - к третьим входам управления блока катодной и блока анодной развертки, выход обратной связи которого подключен к первому входу управления блока тактовых и управляющих сигналов, второй вход управления которого подключен к выходу обратной связи первого контроллера блока памяти, третий - к выходу обратной связи второго контроллера блока памяти, вход кадровой синхронизации которого объединен с входами кадровой синхронизации первого контроллера блока памяти, блока тактовых и управляющих сигналов, блока анодной развертки и являются входом кадровой синхронизации модуля, входом строчной синхронизации которого являются объединенные входы строчной синхронизации первого и второго контроллеров блоков памяти, объединенные тактовые входы записи которых являются входом тактовой синхронизации модуля, информационными входами которого являются информационные входы коммутатора - мультиплексора, информационные выходы которого подключены соответственно к информационным входам блока катодной развертки, а его первая и вторая группы промежуточных входов - выходов - к соответствующим входам - выходам первого и второго блоков памяти, соответственно, адресные и управляющие входы которых подключены к соответствующим выходам соответственно первого и второго контроллеров памяти.

2. Устройство по п.1, отличающееся тем, что блок тактовых и управляющих сигналов (БТУС) содержит тактовый генератор, выход которого подключен к тактовому воду первого триггера и первому входу первой схемы И, выход которой является тактовым выходом БТУС, второй вход подключен к прямому выходу первого триггера, вход R сброса которого подключен к инверсному выходу второго триггера, вход R сброса которого подключен к выходу первой схемы ИЛИ, вход S установки в единичное состояние - к выходу второй схемы ИЛИ, первый вход которой подключен к счетному входу третьего триггера, к входу R сброса первого счетчика и является входом кадровой синхронизации БТУС, второй вход объединен с первым входом третьей схемы ИЛИ, первым входом второй схемы И и тактовым входом четвертого триггера и подключен к выходу первого формирователя импульсов, вход которого подключен к выходу третьей схемы И, первый вход которой подключен к выходу схемы сравнения кодов, второй вход - к выходу задающего генератора и счетному входу второго счетчика, выходы младших разрядов которого через четвертую схему И подключены ко входу равенства кодов схемы сравнения кодов, выходы четырех старших разрядов - к соответствующим входам первого числа схемы сравнения кодов, входы второго числа которой подключены к соответствующим четырем выходам дешифратора, первый и второй входы которого подключены соответственно к первому и второму выходам первого счетчика, третий выход которого подключен ко второму входу третьей схемы ИЛИ и входу R сброса четвертого триггера, прямой выход которого подключен ко второму входу второй схемы И, выход которой является шестым выходом управления БТУС, первым и вторым выходами управления которого являются прямой и инверсный выходы третьего триггера, третьим и четвертым - первый и второй выходы первого счетчика, пятым - выход первого формирователя импульсов, который через первую схему задержки подключен ко входу второго формирователя импульсов, седьмым - выход второго формирователя импульсов, который через вторую схему задержки подключен к тактовому входу пятого триггера, вход R сброса которого объединен со входом R сброса второго счетчика и подключен к выходу третьей схемы ИЛИ, прямой выход является восьмым выходом управления БТУС, первым входом управления которого является счетный вход первого счетчика, а вторым и третьим входами управления - входы первой схемы ИЛИ.

3. Устройство по п.1, отличающееся тем, что контроллер блока памяти (КБП) содержит инвертор, вход которого является входом управления КБП и объединен с первыми входами первой, второй, третьей и четвертой схем И и первым входом схемы И-НЕ, второй вход которой объединен со вторым входом четвертой схемы И, является тактовым входом записи КБП и подключен к входу первой схемы задержки, выход которой подключен ко второму входу первой схемы задержки, выход которой подключен ко второму входу первой схемы И, выход которой подключен к первому входу первой схемы ИЛИ, выход которой подключен к счетному входу первого двоичного счетчика, второй вход является выходом обратной связи КБП и подключен к выходу пятой схемы И, первый вход которой подключен к выходу перенос второго двоичного счетчика, второй вход - к выходу инвертора и первому входу шестой схемы И и первому входу седьмой схемы И, выход которой подключен к первым входам первой, второй, третьей и четвертой схем ИЛИ-НЕ, выходы которых совместно с выходом схемы И-НЕ являются управляющими выходами КБП, вторые входы подключены к соответствующим выходам дешифратора, управляющий вход которого подключен к выходу четвертой схемы И, первый и второй адресные входы -соответственно к выходам седьмого разряда первого и второго двоичных счетчиков, выходы с первого по шестой разрядов которых являются адресными выходами КБП, входом кадровой синхронизации которого являются вход сброса R второго двоичного счетчика, объединенный с первым входом второй схемы ИЛИ, выход которой подключен к входу R сброса первого двоичного счетчика, второй вход - к выходу второй схемы И, второй вход которой является входом строчной синхронизации КБП и подключен ко второму входу третьей схемы И, выход которой подключен к первому входу третьей схемы ИЛИ, выход которой подключен к счетному входу второго двоичного счетчика, второй вход - к выходу шестой схемы И, второй вход которой подключен к выходу второй схемы задержки, вход которой объединен со вторым входом седьмой схемы И и является тактовым входом чтения КБП.

4. Устройство по п.1, отличающееся тем, что коммутатор-мультиплексор содержит три группы коммутаторов и мультиплексоров по четыре коммутатора и мультиплексора в каждой группе, причем управляющие входы всех коммутаторов и входы управления старшего (третьего) разряда всех мультиплексоров объединены и являются первым входом коммутатора - мультиплексора, вторым и третьим входами управления которого являются объединенные входы управления первого и второго разрядов всех мультиплексоров.

5. Устройство по п.4, отличающееся тем, что восемь выходов каждого коммутатора подключены к восьми входам соответствующего мультиплексора, выходы двенадцати мультиплексоров образуют двенадцать информационных выходов коммутатора - мультиплексора, две группы по 48 промежуточных входов - выходов которого образуют выходы 12 - и коммутаторов, причем первую группу образуют первые четыре выхода каждого коммутатора, а три группы по 4 информационных входа коммутатора-мультиплексора образуют информационные входы трех групп коммутаторов, внутри которых информационные входы коммутаторов объединены поразрядно.

Текст

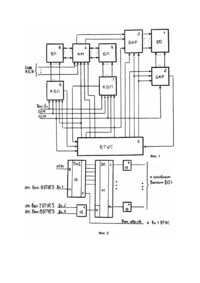

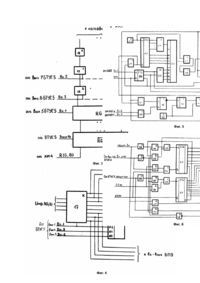

Изобретение относится к электронной технике, а именно к системам отображения информации и может быть применено в телевидении, рекламных устройствах, системах управления и пр. Наиболее близким по технической сущности к заявляемому является модуль устройства для воспроизведения изображения на большом экране, содержащий блок отображения, два блока памяти, блок анодной развертки (блок развертки) и блок катодной развертки (блок выходных регистров). Данный модуль применен в системе воспроизведения изображения логико-временного типа. Технические характеристики модуля: Недостатками этого устройства являются: - сложность технической реализации, т.к. кроме имеющихся в устройстве двух блоков памяти, элементы изображения должны обладать памятью; - невысокая технологичность, т.к. блок отображения выполняется из дискретных элементов - лампы накаливания, тиристоров и т.д.; низкая разрешающая способность, ограниченная применением дискретных элементов изображения; - невозможность воспроизведения полного телевизионного кадра (из-за асинхронности системы записи и чтения часть информации ТВ кадра теряется). Задачей изобретения является упрощение технической реализации, повышение технологичности и разрешающей способности модуля устройства для воспроизведения изображения на большом экране, а также воспроизведение полного цветного телевизионного кадра стандартного телевидения и кадра телевидения с повышенным числом строк при наборе большого экрана соответствующего формата. Поставленная задача решается тем, что в модуль устройства для воспроизведения изображения на большом экране, содержащий два блока памяти и блок отображения в виде матрицы, анодные и катодные входы которой подключены соответственно к входам блока анодной и блока катодной разверток, согласно изобретению, дополнительно введены два контроллера блоков памяти, коммутатор-мультиплексор и блок тактовых и управляющих сигналов, выходы которого подключены: тактовый - к тактовым входам чтения блока катодной развертки, первого и второго контроллеров блоков памяти, первый управления - к входу управления первого контроллера блока памяти и первому входу управления коммутатора - мультиплексора, второй управления - к входу управления второго контроллера блока памяти, третий и четвертый управления - ко второму и третьему входам управления коммутатора-мультиплексора, пятый управления - к первому входу управления блока катодной развертки, шестой управления - к первому входу управления блока анодной развертки, седьмой управления - ко вторым входам управления блока катодной и блока анодной развертки, восьмой управления - к третьим входам управления блока катодной и блока анодной развертки, выход обратной связи которого подключен к первому входу управления блока тактовых и управляющих сигналов, второй вход управления которого подключен к выходу обратной связи первого контроллера блока памяти, третий - к выходу обратной связи второго контроллера блока памяти, вход кадровой синхронизации которого объединен с входами кадровой синхронизации первого контроллера блока памяти, блока тактовых и управляющих сигналов, блока анодной развертки и являются входом кадровой синхронизации модуля, входом строчной синхронизации которого являются объединенные входы строчной синхронизации первого и второго контроллеров блоков памяти, объединенные тактовые входы записи которых являются входом тактовой синхронизации модуля, информационными входами которого являются информационные входы коммутаторов-мультиплексора, информационные выходы которого подключены соответственно к информационным входам блока катодной развертки, а его первая и вторая группы промежуточных входов-выходов к соответствующим входам-выходам первого и второго блоков памяти соответственно адресные и управляющие входы которых подключены к соответствующим выходам соответственно первого и второго контроллеров блока памяти. Блок тактовых и управляющих сигналов (БТУС) содержит тактовый генератор, выход которого подключен к тактовому входу первого триггера и первому входу первой схемы И, выход которой является тактовым выходом БТУС, второй вход подключен к прямому выходу первого триггера, вход сброса которого подключен к инверсному выходу второго триггера, вход сброса которого подключен к выходу первой схемы ИЛИ, вход установки в единичное состояние - к выходу второй схемы ИЛИ, первый вход которой подключен к счетному входу третьего триггера, к входу сброса первого счетчика и является входом кадровой синхронизации БТУС, второй вход объединен с первым входом третьей схемы ИЛИ, первым входом второй схемы И и тактовым входом четвертого триггера и подключен к выходу первого формирователя импульсов, вход которого подключен к выходу третьей схемы И, первый вход которой подключен к выходу схемы сравнения кодов, второй вход - к выходу задающего генератора и счетному входу второго счетчика, выходы младших разрядов которого через четвертую схему И подключены ко входу равенства кодов схемы сравнения кодов, выходы четырех старших разрядов - к соответствующим входам первого числа схемы сравнения кодов, входы второго числа подключены к соответствующим четырем выходам дешифратора, первый и второй входы которого подключены соответственно к первому и второму выходам первого счетчика, третий выход которого подключен ко второму входу третьей схемы ИЛИ и входу сброса четвертого триггера, прямой выход которого подключен ко второму входу второй схемы И, выход которой является шестым выходом управления БТУС, первым и вторым выходами управления которого являются прямой и инверсный выходы третьего триггера, третьим и четвертым - первый и второй выходы первого счетчика, пятым - выход первого формирователя импульсов, который через первую схему задержки подключен ко входу второго формирователя импульсов, седьмым - выход второго формирователя импульсов, который через вторую схему задержки подключен к тактовому входу пятого триггера, вход сброса которого объединен со входом сброса второго счетчика и подключен к выходу третьей схемы ИЛИ, прямой выход - является восьмым выходом управления БТУС, первым входом управления которого является счетный вход первого счетчика, а вторым и третьим входами управления - входы первой схемы ИЛИ. Контроллер блока памяти (КБП) содержит инвертор, вход которого является входом управления КБП и объединен с первыми входами первой, второй, третьей и четвертой схем И и первым входом схемы И-НЕ, второй вход которой объединен со вторым входом четвертой схемы И, является тактовым входом записи КБП и подключен к входу первой схемы задержки, выход которой подключен ко второму входу первой схемы И, выход которой подключен к первому входу первой схемы ИЛИ, выход которой подключен к счетному входу первого двоичного счетчика, второй вход является выходом обратной связи КБП и подключен к выходу пятой схемы И, первый вход которой подключен к выходу перенос второго двоичного счетчика, второй вход - к выходу инвертора и первому входу шестой схемы И и первому входу седьмой схемы И, выход которой подключен к первым входам первой, второй, третьей и четвертой схем ИЛИ-НЕ, выходы которых совместно с выходом схемы И-НЕ являются управляющими входами КБП, вторые входы подключены к соответствующим выходам дешифратора, управляющий вход которого подключен к выходу четвертой схемы И, первый и второй адресные входы - соответственно к выходам седьмого разряда первого и второго двоичных счетчиков выходы с первого по шестой разрядов которых являются адресными выходами КБП, входом кадровой синхронизации которого является вход сброса второго двоичного счетчика объединенный с первым входом второй схемы ИЛИ, выход которой подключен к выходу сброса первого двоичного счетчика, второй вход к выходу второй схемы И, второй вход которой является входом строчной синхронизации КБП и подключен ко второму входу третьей схемы И, выход которой подключен к первому входу третьей схемы ИЛИ, выход которой подключен к счетному входу второго двоичного счетчика, второй вход - к выходу шестой схемы И, второй вход которой подключен к выходу второй схемы задержки, вход которой объединен со вторым входом седьмой схемы И и является тактовым входом чтения КБП. Коммутатор-мультиплексор содержит три группы по четыре коммутатора и мультиплексора в каждой. Три входа управления образуются: первый - входом управления коммутаторов и первым входом управления мультиплексоров, второй и третий - вторым и третьим входами управления мультиплексоров. Информационные входы образуют информационные входы трех групп коммутаторов, информационные выходы - выходы мультиплексоров, промежуточные входы-выходы выходы коммутаторов, подключенные к входам мультиплексоров. Данные существенные признаки позволяют на большом экране, набираемом из модулей, воспроизвести полный телевизионный кадр, а также упростить техническую реализацию модуля (в блоке отображения не требуется элементов изображения с памятью), повысить технологичность и разрешающую способность модуля. На фиг.1 представлена схема электрическая структурная модуля устройства для воспроизведения изображения на большом экране; на фиг.2 - схема электрическая структурная блока анодной развертки; на фиг.3 -схема электрическая структурная части (одна группа из 12) блока катодной развертки; на фиг.4 - схема электрическая структурная части (одна группа из 12) коммутаторамультиплексора; на фиг.5 - схема электрическая структурная блока тактовых и управляющих сигналов; на фиг.6 - схема электрическая структурная контроллера блока памяти. Модуль устройства для воспроизведения изображения на большом экране (фиг.1) содержит: блок отображения 1 (БО), 64 анодных входа которого подключены к соответствующим выходам блока анодной развертки 2 (БАР), а 768 катодных входов - к соответствующим выходам блока катодной развертки 3 (БКР), 12 информационных входов которого подключены к соответствующим выходам коммутатора-мультиплексора 4 (КМ). Выход обратной связи БАР2 подключен к первому входу блока тактовых и управляющих сигналов 5 (БТУС), ко второму и третьему входам которого подключены соответственно выходы обратной связи первого 6 и второго 7 контроллеров блоков памяти (КБП). Вход кадровой синхронизации БАР2 объединен с аналогичными входами БТУС5, КБП6, КБП7 и является входом кадровой синхронизации модуля (КСМ). Тактовый выход БТУС5 (такт Чт) подключен к тактовым входам чтения КБП6, КБП7 и БКР3. Первый выходу управления БТУС5 (Вых.1) подключен ко входу управления КБП6 и первому входу управления КМ4, второй (Вых.2) - ко входу управления КБП7, третий и четвертый (вых.3 и Вых.4) - ко второму и третьему входам управления КМ4 соответственно, пятый 4 к первому входу управления БКР3, шестой - к первому входу управления БАР2, седьмой и восьмой - ко второму и третьему входам управления БКР3, БАР2. Тактовые входы записи КБП6 и 7 объединены и являются входом тактовой синхронизации модуля по записи (Такт Зп.). Входы строчной синхронизации КБП6 и 7 объединены и являются входом строчной синхронизации модуля (ССМ). 12 информационных входов КМ4 являются информационными входами модуля 96 промежуточных входов-выходов КМ4 подключены соответственно к 48 входамвыходам первого 8 и 48 входам-выходам второго 9 блоков памяти (БП). Адресные и управляющие входы БП8 и 9 подключены к соответствующим выходам КБП 6 и 7. БО1 состоит из 4 - х панелей типа "Плутон-3". Каждая панель содержит 64 ´ 64 газоразрядных пикселей по 3 ячейки, излучающих 6 красной зеленой синей областях спектра. Каждый пиксель имеет общий анод и три катода. Аноды пикселей внутри панели объединены по колонкам, а катоды - построчно. Т.е. каждая панель имеет 64 анодных и 192 катодных выхода. Внутри БО1 анодные входы панелей соответственно запараллелены, т.е. БО1 имеет 64 анодных и 192 ´ 4 = 768 катодных входа. БАР2 (фиг.2) содержит: двоичный шестиразрядный счетчик 10, вход "+1" которого является первым входом управления, вход входом кадровой синхронизации, а выход "перенос" - выходом обратной связи БАР2. Шесть выходов счетчика 10 подключены к соответствующим входам дешифратора 11, тактовый вход которого подключен к выходу схемы ИЛИ 12, входы которой являются вторым и третьим входами управления БАР2. Выходы дешифратора 11 подключены к соответствующим анодным ключам 13, выходы которых образуют 64 анодных выхода БАР2. БКР3 (фиг.3) содержит: двенадцать сдвиговых регистров 14 на 64 разряда (на фиг.3 представлена одна из 12 частей БКР3), последовательные информационные входы которых образуют 12 информационных входов БКР3, т.е. каждой панели БО1 соответствует по 3 регистра 14 (а также и других частей схемы представленных на фиг.3), которые в свою очередь принимают информацию в красном зеленом и синем цветах. Тактовые входы регистров 14 объединены и являются тактовым входом чтения БКРЗ (Такт Чт.), а выходы подключены к соответствующим входам соответствующих параллельных регистров 15. Тактовые входы регистров 15 объединены и являются первым входом управления (Вх.1) БКР3, а выходы подключены к первым входам соответствующих схем И 16, вторые входы которых объединены и являются третьим входом управления (Вх.3) БКР3. Выходы схем И 16 подключены к первым входам соответствующих схем ИЛИ 17, вторые входы которых объединены и являются вторым входом управления (Вх.2) БКР3. Выходы схем ИЛИ 17 подключены к входам соответствующих катодных ключей 18, выходы которых образуют 768 катодных выхода БКР3 (на фиг.3 изображено 64 катодных ключа и 64 катодных выхода БКР3, что соответствует одному из 12 - и регистру 14). КМ4 (фиг.4) содержит: по 12 коммутаторов 19 и мультиплексоров 20. (На фиг.4 представлена одна группа из одного коммутатора 19 и мультиплексора 20, остальные группы включены аналогично). Информационные входы коммутаторов 19 соответствующих одноименным цветам объединены поразрядно, т.е. КМ4 имеет по 4 информационных входа по красному зеленому и синему цветам, всего 12 информационных входа Выходы коммутаторов 19 подключены к соответствующим входам соответствующих мультиплексоров 20 и кроме того являются входами-выходами КМ4. Всего КМ4 имеет 96 входов-выходов по 12 от каждого коммутатора 19, которые разделены на 2 группы по 48 входоввыходов соответственно для БЛ8 и БП9. Управляющие входы коммутаторов 19 и входы управления старшего (третьего) разряда мультиплексоров 20 объединены и являются первым входом управления (Вх.1) КМ4. Входы управления первого и второго разрядов мультиплексоров 20 соответственно объединены и являются вторым и третьим входами управления (Вх.2 и вх.3) КМ4. Выходы 12 - и мультиплексоров 20 являются информационными выходами КМ4 (12 выходов). БТУС5 (фиг.5) содержит: генератор 21 длительности цикла, выход которого подключен ко входу "+1" счетчика 22 длительности цикла и к первому входу схемы И 23. Выходы младших разрядов счетчика 22 подключены к входам схемы И 24, а выходы последних четырех старших разрядов - к входам первого четырехразрядного числа схемы сравнения 25, выход которой подключен ко второму входу схемы И 23. Вход сброса счетчика 22 объединен с входом сброса триггера 26 и подключен к выходу схемы ИЛИ 27. Выход схемы И 23 подключен ко входу формирователя 28. Выход схемы И24 подключен ко входу равенства первого и второго числа схемы сравнения 25. Четыре входа второго четырехразрядного числа схемы сравнения 25 подключены к выходам дешифраторе 29. Прямой выход триггера 16 является восьмым выходом управления (Вых.8) БТУС5. Вход управления триггера 26 (на схеме не показан) подключен к шине "лог.1", а тактовый вход подключен к выходу задержки 30. Первый вход схемы ИЛИ 27 объединен с первым входом схемы ИЛИ 31, первым входом схемы И 32, тактовым входом триггера 33, входом задержки 34 и подключен к выходу формирователя 28, который кроме того является пятым выходом управления (Вых.5) БТУС5. Второй вход схемы ИЛИ 27 объединен с входом сброса триггера 33 и подключен к выходу третьего разряда счетчика 35. Два входа дешифратора 29 подключены соответствен но к выходам первого и второго разрядов триггера 35 и является третьим и четвертым выходами управления (Вых.3 и вых.4) БТУС5. Вход задержки 30 подключен к выходу формирователя 36 и является седьмым выходом управления (Выход 7) БТУС 5. Второй вход схемы ИЛИ 31 объединен со входом сброса триггера 35, счетным входом "+1" триггера 37 и является входом КСМ БТУС 5. Выход схемы ИЛИ31 подключен ко входу установки в состояние "лог.1". триггера 38. Выход схемы И 32 является шестым выходом управления (Вых.6) БТУС5, а второй вход подключен к прямому выходу триггера 33, вход управления которого подключен к шине "лог.1" (на схеме не показан). Выход задержки 34 подключен к входу формирователя 36. Счетный вход "+1" счетчика 35 является первым входом управления (Вх.1) БТУС5. Прямой и инверсный выходы триггера 37 являются соответственно первым и вторым выходами управления (Вых.1 и вых.2) БТУС 5. Вход сброса триггера 38 подключен к выходу схемы ИЛИ, а инверсный выход к входу сброса триггера 40. Первый и второй входы схемы ИЛИ 39 являются соответственно вторым и третьим входами управления (Вх.2 и вх.3) БТУС 5. Прямой выход триггера 40 подключен к первому входу схемы И 41, тактовый вход объединен со вторым входом схемы И 41 и подключен к выходу тактового генератора 42, вход управления подключен к шине "лог.1" (на схеме не показан). Выход схемы И 41 является тактовым выходом чтения (Такт Чт.) БТУС 5. КБП6 (7) (фиг.6) содержит: инвертор 43, вход которого является входом управления КБП6(7), и объединен со вторыми входами схем И 44, 45, 46, 47 и первым входом схемы И-НЕ 48. Выход инвертора 43 подключен ко вторым входам схем И 49, 50, 51. Первый вход схемы И 44 подключен к выходу задержки 52, а выход - к первому входу схемы ИЛИ 53. Первый вход схемы И 45 объединен с первым входом схемы И 46, является входом строчной синхронизации КБП6(7) (ССМ), а выход подключен к первому входу схемы ИЛИ 54. Выход схемы И 46 подключен ко второму входу схемы ИЛИ 55. Первый вход схемы И 47 является тактовым уходом записи КБП6(7) (Такт Зп) и объединен с входом задержки 52 и вторым входом схемы И-НЕ 48, а выход подключен к тактовому входу дешифратора 56. Выход схемы И-НЕ 48 является первым выходом управления КБП6(7). Первый вход схемы И 49 подключен к выходу перенос адресного счетчика 57, а выход - ко второму входу схемы ИЛИ 53 и является выходом обратной связи КБП6(7). Первый вход схемы И50 подключен к выходу задержки 58, а выход - к первому входу схемы ИЛИ 55. Первый вход схемы И 51 объединен с входом задержки 58 и является тактовым входом чтения (Такт Чт.) КБП 6(7), а выход подключен ко вторым входам схем ИЛИ-НЕ 59, 60, 61, 62. Выход схемы ИЛИ 53 подключен к счетному входу "+1" адресного счетчика 63. Второй вход схемы ИЛИ 54 объединен со входом сброса счетчика 57, и является входом кадровой синхронизации (КСМ) КБП6(7), а выход подключен ко входу сброса счетчика 63. Выход схемы ИЛИ 55 подключен к счетному входу "+1" счетчика 57. Первый и второй информационные входы дешифратора 56 подключены к выходам седьмого разряда счетчиков 63 и 57 соответственно. Выходы дешифратора 56 подключены к первым входам соответствующих схем ИЛИ-НЕ 59, 60, 61, 62. Шесть выходов шести разрядов счетчика 57 и шесть выходов шести разрядов счетчика 63 являются адресными выходами (12 выходов) КБП6(7). Выходы схем ИЛИ-НЕ 59, 60, 61, 62 являются вторым, третьим четвертым и пятым выходами управления КБП6(7). БП8 состоит, например, из 12 - и микросхем типа (КМ 132 РУ12 А (зарубежный аналог Данная микросхема имеет объем памяти что обеспечивает хранение информации одного цвета газоразрядной панели 64 ´ 64 точки с 16 - ю градациями яркости в виде двоичного 4 - х разрядного кода. Таким образом, каждой панели БО1 для каждой цветовой составляющей соответствует одна микросхема БП8 и одна микросхема БП9. Входы-выходы каждой микросхемы подключены к соответствующим входам-выходам КМ4, а точнее к выходам соответствующих коммутаторов 19. Адресные входы всех микросхем БП8 и БП9 соответствующим образом запараллелены и подключены к адресным выходам соответственно КБП6 и КБП7. Входы "запись/чтения" всех микросхем БП8 и БП9 объединены и подключены к соответствующему выходу управления соответственно КБП6 и КБП7, а конкретно к выходу схемы И-НЕ 48. Входы "выбор кристалла" микросхем БП8 и БП9 объединены по тройкам соответствующим панелям БО1 и подключены к соответствующим выходам управления соответственно КБП6 и КБЛ7. Например, входы "выбор кристалла" микросхем цвета БП8 соответствующие первой панели БО1 объединены и подключены к первому выходу управления КБП6, а конкретно к выходу схемы ИЛИ-НЕ 59 и т.д. Работа устройства. Модуль устройства для воспроизведения изображения позволяет отобразить полутоновую цветную информацию телевизионного типа с 16 - ю градациями яркости по каждой цветовой составляющей. Информация поступает в модуль на информационные входы КМ4 в виде 4 - х разрядного двоичного кода по каждой цветовой составляющей, т.е. 4 разряда - информация о красном цвете 4 - о зеленом и 4 - о синем Данная информация тактирована сигналом "Такт Зп" поступающим на КБП6 и 7. Кроме того в модуль поступают сигналы строчной и кадровой синхронизации ССМ и КСМ. Сигнал КСМ кроме сброса соответствующих счетчиков модуля в исходное состояние переключает также БП8 и 9 из режима записи информации в режим чтения, точнее один из БП находится в состоянии записи информации, а другой в это время в состоянии чтения. По приходу сигнала КСМ происходит смена режима записи на режим чтения в одном из БП и наоборот режима чтения на режим записи в другом БП. Конкретно управляющим элементом является триггер 37 БТУС5, на счетный вход "+1" которого поступает сигнал КСМ. С прямого и инверсного выходов триггера 37 снимается "лог.1" и "лог.0" поступающие на вход управления КБП6 и 7. Очевидно, что с приходом каждого КСМ уровень "лог.1" снимаемой, например, с прямого или инверсного выхода меняется на уровень "лог.0" и наоборот. Уровень "лог.1" на входе управления КБП задает режим записи соответствующего БП и наоборот уровень "лог.0" - режим чтения информации. Рассмотрим подробнее режим записи информации, например в БП8. После прихода очередного КСМ триггер 37 установился в такое состояние, что на его прямом выходе (Вых.1) уровень "лог.1", определяющий режим записи информации в БП8. Данный уровень поступает на вход управления (вх.упр.) КБП6, конкретно на один из входов схем И 44 - 47, схемы И-НЕ 48 и на вход инвертора 43, на выходе которого при этом появляется уровень "лог.0". Уровень "лог.0" с выхода инвертора 43 "блокирует" схемы И 49, 50, 51. Т.к. на одном из входов схем И 44 - 48 присутствует уровень "лог.1", то состояние выходов данных схем определяет сигнал поступающий на другой из входов. Сигнал "Такт Зп" через задержку 52, схему И 44 и схему ИЛИ 53 поступает на счетный вход "+1" счетчика 63. С приходом каждого тактового импульса счетчик 63 увеличивает свое состояние на 1, осуществляя таким образом пересчет младших 6 - й разрядов кристаллов памяти БП8. Синхронизирует работу счетчика 63 строчный (ССМ) и кадровый (КСМ) сигналы поступающие через схему И 45 и схему ИЛИ 54 на вход сброса данного счетчика. Пересчет старших 6 - й разрядов микросхем БП8 осуществляет счетчик 57 по приходу каждого ССМ через схему И 46, ИЛИ 55 на счетный вход "+1". Синхронизирует работу счетчика 57 сигнал КСМ поступающий на вход сброса . В исходном состоянии (по приходу КСМ) счетчики 57 и 63 находятся в состоянии "0" на всех выходах. Как видно из фиг.6 это 7 - й разрядные счетчики. Седьмые разряды счетчиков 57 и 63 используются для выбора микросхем БП8, в которые будет произведена запись информации. Как уже отмечалось БО1 состоит из 4 - х панелей. Каждой панели в БП8 и 9 соответствует по 3 микросхемы для записи-чтения информации и цветов. В исходном состоянии 7 - е разряды счетчиков 57 и 63 находятся в состоянии "лог.0", поэтому дешифратор 56 с приходом на управляющий вход сигнала со схемы И 47, вырабатывает управляющий сигнал на своем первом выходе. Данный сигнал через схему ИЛИНЕ 59 поступает на вход "выбор кристалла" соответствующих 3 - х микросхем БП8. Синхронно в это время схема И-НЕ 48 вырабатывает сигнал "записи" поступающий на вход "запись/чтение" всех микросхем БП8, однако запись информации будет происходить только в те 3 микросхемы, которые выбраны дешифратором 56, т.к. только на первом его выходе присутствует необходимый для записи сигнал. Уровень "лог.1" с прямого выхода триггера 37 поступает кроме того на КМ4, а конкретно на вход управления всех коммутаторов 19. При поступлении данного уровня на вход управления коммутатора 19 "открыты" для входной информации первые четыре выхода, а вторые четыре выхода "закрыты". Таким образом на соответствующие микросхемы синхронно с сигналом "такт Зп" поступает параллельный 4 - х разрядный код яркости ячеек соответствующей панели. Запись информации в БП8 ведется построчно, т.е. счетчик 63 производит перебор 64 пикселей панелей БО1, после чего на его 7 - ом выходе появляется уровень "лог.1", который поступая на дешифратор 56 "выбирает" для записи информации следующие 3 микросхемы т.к. "рабочим" становится второй выход дешифратора 56 и схема ИЛИ-НЕ 60. Таким образом первая строка информации, содержащая 128 12 - и разрядных слов (по 4 разряда на каждый цвет) будет записана в первые 64 ячейки микросхем соответствующих 1 - ий 2 - й панелям БО1. После чего счетчик 63 приходит в исходное состояние, а на счетчик 57 приходит сигнал ССМ, переводя его в состояние выбора второй строки микросхем для записи информации. После заполнения информацией микросхем, соответствующих 1 - й и 2 - й панелям БО1, на 7 - м выходе счетчика 57 появляется уровень "лог.1", что в комбинации с уровнями "лог.0" и "лог.1" на 7 - м выходе счетчика 63 выбирает "рабочими" 3 и 4 выходы дешифратора 56 и запись информации будет происходить в микросхемы БП6 соответствующие 3 - ей и 4 - ой панелям БО1, после заполнения которых по приходу следующего КСМ описанный процесс повторится для аналогичной схемы БП9 и КБП 7, т.е. триггер 37 установится в состояние при котором на его прямом выходе уровень "лог.0", а на инверсном - "лог.1". Коммутаторы 19 при этом переходят в состояние при котором первые четыре выхода "закрыты", а вторые четыре выхода "открыты" для прохождения информации и запись информации аналогично будет проведена в микросхемы БП9. В это время микросхемы БП8 находятся в режиме чтения информации. Чтение информации из БП происходит в другой последовательности нежели была произведена запись, а именно, не построчно, а по колонкам. Это связано конкретной конструкцией панелей БО1, у которой аноды объединены по колонкам. Перед рассмотрением режима чтения объясним каким образом ячейки БО1 воспроизводят полутоновое изображение. Период возбуждения ячеек должен быть не более (кадровая частота 50Гц), чтобы исключить мелькания, поэтому максимальное время возбуждения ячейки составит т.к. в данном устройстве ячейки возбуждаются одновременной для всей колонки панели, а число колонок 64. Примем за максимальное время возбуждения ячейки При воспроизведении 16 градаций (включая и нулевую) минимальное время возбуждения ячейки составит: При системе кодирования яркостного сигнала длительности полей возбуждения ячеек составят: что в сумме составляет Таким образом при нулевой градации яркости (код 0000) ячейки вообще не включаются (не возбуждаются), при 1 - й - включаются ячейки закодированные 0001 на время при 2 - й ячейки закодированные 0010 на время при 3 - й - ячейки закодированные 0011 на время 20,8 и и т.д. при 10 - й градации яркости включаются ячейки закодированные 1111 на время 20,8; 41,6; 83,2; 166,4 т.е. на все время отведенное для колонки 312. Необходимые длительности формируются БТУС5 следующим образом: КСМ поступая на вход сброса счетчика 35 "обнуляет" его, при этом на его выходах устанавливаются уровни "лог.0". Первые два выхода счетчика 35 кодом 00 определяют длительность поля возбуждения ячеек в Код 00 поступая на входы дешифратора 29 устанавливает уровень "лог.1" на первом выходе дешифратора 29 и первом входе схемы сравнения 25. Генератор 21, частота которого подобрана соответствующим образом, счетчик 22, схема И 24 выработают сигналы уровня "лог.1", которые появятся на первом входе и выходе через время равное длительности первого поля, при этом на выходе схемы сравнения 25 появится сигнал с уровнем "лог.1", который через схему И 23 запускает формирователь 28. Формирователь 28 вырабатывает сигнал "перенос", который через схему ИЛИ 27 обнуляет счетчик 22, триггер 26, а также непосредственно устанавливает триггер 33 в единичное состояние. Кроме того сигнал "перенос" появляется на вых.5 БТУС5, который поступает на Вх.1 регистра 15 осуществляет перезапись информации накопленной к этому времени в сдвиговом регистре 14 в регистр 15. Через задержку 34 сигнал перенос поступает на формирователь 36, который формирует сигнал "инициализация", назначение которого рассмотрим ниже, и через задержку 30 устанавливает триггер 26 в единичное состояние, выход которого есть вых.8 БТУС5 и на котором формируется сигнал "управление разрядом". После окончания сигнала "перенос" генератора 21, счетчик 22, схема И 24 и схема сравнения 25 "отрабатывают" следующий цикл первой длительности первого поля. Как видно из схемы, первый после КСМ6 сигнал "перенос" на Вых.6 БТУС5 не появится, т.к. схема И 32 была блокирована триггером 33, поэтому счетчик 10 остается в нулевом состоянии (обнулен сигналом КСМ (и дешифратор 11 подготовлен к появлению сигналов на первом выходе, которые появятся на нем синхронно с поступлением сигналов на входе На вход через схему ИЛИ 12 последовательно поступят сигналы "инициализация" и "управление разрядом", которые с первого выхода дешифратора 11 через ключ 13 поступят на первый анодный вход панелей БО1. Чтение информации происходит одновременно из всех микросхем БП8, т.к. в данном режиме уровень "лог.0" на входе управления КБП6 через инвертор 43, схему И 51 "разрешает" прохождение на объединенные входы схем ИЛИ-НЕ 59 - 62 сигнала Такт Чт, который поступает на вход "выбор кристалла" всех микросхем БП8. В это время уровень "лог.0" на втором входе схемы И-НЕ 48 вызывает появление на ее выходе уровня "лог.1", который поступая на вход "запись-чтение" всех микросхем БП8 определяет режим чтения информации из БП8. По сигналу Такт Чт, который через задержку 58, схему И 50, ИЛИ 55 поступает на счетный вход "+1" счетчика 57, происходит перебор колонок микросхем БП8. После считывания информации из последней 64 ячейки колонки микросхем БП8 на выходе переноса счетчика 57 появляется импульс, который через схему И 49, ИЛИ 53 поступает на счетный вход "+1" счетчика 63 переводя его в состояние выбора следующей колонки микросхем БП8. Одновременно данный сигнал, являясь сигналом обратной связи КБП6 (7) поступает на вход управления 2(3) БТУС5, где через схему ИЛИ 39 поступает на вход сброса триггера 38 и устанавливает его в "нулевое" состояние. Уровень "лог.1" на инверсном выходе данного триггера, поступая на вход сброса триггера 40 вызывает появление на его выходе уровня "лог.0" который поступая на вход схемы И 41 "блокирует" прохождение сигнала Такт Чт на соответствующий выход БТУС5. Считывание информации следующей колонки из БП8 произойдет после прихода соответствующего сигнала через схему ИЛИ 31 на вход триггера 38. При этом на инверсном выходе триггера 38 появится уровень "лог.0", который "разблокирует" триггер 40. Первый импульс генератора 42, поступая на тактовый вход триггера 40 установит его в состояние "лог. 1". Данный уровень поступает на вход схемы И 41 и "разрешает" прохождение сигнала Такт Чт на соответствующий выход БТУС5 и процесс считывания информации повторится для следующей колонки микросхем 6П8. Считываемая информация поступает на соответствующие входы мультиплексоров 20, но на выходах появится только информация соответствующая первому разряду кода яркости, т.к. на входах управления присутствует код первого поля поступающий со счетчика 35. Вход мультиплексоров 20 определяет, как уже указывалось, считывание информации либо с БП8, либо в БП9. В цикле первого поля на выходы мультиплексоров 20 "пройдет" информация о яркости ячеек, длительность возбуждения которых должна быть т.е. информация первого разряда яркостного кода. Данная информация поступает в соответствующие сдвиговые регистры 14 и накапливается в них путем сдвига с частотой Такт Чт, после чего при поступлении сигнала, "перенос" перезаписывается в регистр 15, а в сдвиговый регистр 14 поступает информация следующей колонки. Информация на выходе регистра 15 в виде уровней "лог.1" и "лог.0" определяет какие ячейки в колонке должны возбудиться на время сигнала "управления разрядом" поступающим на Вх.3 БКР3. Естественно, что возбудятся только ячейки соответствующие информации с уровнем "лог.1", т.е. на катодные входы сигнал "управление разрядом" поступает через схемы И 16. Независимо от того должна ячейка возбудиться в данном поле или нет, на ее катодные входы поступит сигнал "инициализация" через схемы ИЛИ 17 и ключи 18. Длительность данного сигнала составляет не более трети сигнала "управление разрядом" младшего поли. Сигнал "инициализация" играет роль подготовительного для устойчивого включения ячеек в рабочем цикле, чтобы не было большой задержки при возбуждении ячеек, которые в прошлом кадре имели нулевую градацию яркости. После воспроизведения информации первого поля, т.е. после пересчета 64 - х строк на выходе "перенос" счетчика 10 появляется импульс, который поступая на счетный вход "+1" счетчика 35 переводит его в состояние 01. Описанный процесс повторится с длительностью поля возбуждения и т.д. После воспроизведения информации 64 - й строки последнего поля на выходе третьего разряда счетчика 35 появится сигнал с уровнем "лог.1"; который обнуляет триггер 33 и через схему ИЛИ 27 "блокирует" счетчик 22 до прихода кадрового синхроимпульса, который поступив на вход сброса счетчика 35 "разблокирует" счетчик 22. Описанный процесс чтения и воспроизведения изображения повторится. Заявляемый модуль предназначен для набора больших экранов путем стыковки панелей 60 в матрицы соответствующего формата. Кроме того, модуль, имея информационную емкость 128 ´ 128 цветовых пикселей, может быть использован и как отдельное устройство для воспроизведения изображения, знакографической и текстовой информации ограниченного формата. При осуществлении изобретения может быть получен модуль со следующими характеристиками:

ДивитисяДодаткова інформація

Автори англійськоюBoivan Anatolii Vasyliovych, Doroschenkov Hehhadii Dmytrovych, Kozhemyako Volodymyr Prokopovych

Автори російськоюБойван Анатолий Васильевич, Дорощенков Геннадий Дмитриевич, Кожемяко Владимир Прокофьевич

МПК / Мітки

МПК: H04N 5/66

Мітки: зображення, відтворення, великому, модуль, екрані, пристрою

Код посилання

<a href="https://ua.patents.su/8-14808-modul-pristroyu-dlya-vidtvorennya-zobrazhennya-na-velikomu-ekrani.html" target="_blank" rel="follow" title="База патентів України">Модуль пристрою для відтворення зображення на великому екрані</a>

Попередній патент: Пристрій для автоматичної промивки санітарних приладів

Наступний патент: Спосіб допалювання оксиду вуглецю

Випадковий патент: Ультразвуковий частотно-часовий витратомір