Пристрій для керування зустрічно-паралельно включеними тиристорами

Номер патенту: 16293

Опубліковано: 29.08.1997

Автори: Тимченко Олександр Вікторович, Черевань Сергій Миколайович

Формула / Реферат

1. Устройство управления встречно-параллельно включенными тиристорами, через индуктивность подключенными к источнику переменного напряжения, содержащее датчик тока, предназначенный для включения в силовую цепь тиристоров, датчик переменного напряжения, выход которого подключен к одному входу фазосмещающего узла, другой вход которого предназначен для подключения к выходу регулятора угла управления тиристорами, два формирователя импульсов управления тиристорами и первый управляемый двухвходовой переключатель, отличающееся тем, что, с целью снижения перенапряжений в силовой цепи и обеспечения управления тиристорами в переходных режимах, в него введены узел определения длительности полупериодов тока в силовой цепи тиристоров, узел дискретного управления и второй управляемый двухвходовой переключатель, фазосмещающий узел снабжен инверсным выходом, причем первый вход узла дискретного управления соединен с выходом датчика переменного напряжения и первым входом узла определения длительности полупериодов тока в силовой цепи тиристоров, второй вход которого соединен с вторым входом узла дискретного управления и выходом датчика тока, прямой и инверсный выходы узла дискретного управления соединены с первыми входами первого и второго управляемых двухвходовых переключателей соответственно, вторые входы которых соединены соответственно с прямым и инверсным выходами фазосмещающего узла, а входы управления - с выходом узла определения длительности полупериодов тока в силовой цепи тиристоров, выходы первого и второго управляемых двухвходовых переключателей соединены соответственно с входами первого и второго формирователей импульсов управления тиристорами, выход каждого из которых предназначен для подключения к управляющему входу соответствующего тиристора, а узел дискретного управления выполнен в виде нуль-органа по напряжению, состоящего из двух компараторов, входы которых использованы как первый вход узла дискретного управления, выходы соединены с входами соответствующих дифференцирующих элементов, нуль-органа по току, выполненного аналогично нуль-органу по напряжению, входы компараторов которого использованы как второй вход узла дискретного управления, выход первого дифференцирующего элемента нуль-органа по напряжению соединен с информационным входом первого элемента ЗАПРЕТ, запрещающий вход которого соединен с выходом первого компаратора нуль-органа по току, выход первого дифференцирующего элемента которого соединен с информационным входом второго элемента ЗАПРЕТ, запрещающий вход которого соединен с выходом первого компаратора нуль-органа по напряжению, выход второго дифференцирующего элемента которого соединен с информационным входом третьего элемента ЗАПРЕТ, запрещающий вход которого соединен с выходом второго компаратора нуль-органа по току, выход второго дифференцирующего элемента которого соединен с информационным входом четвертого элемента ЗАПРЕТ, запрещающий вход которого соединен с выходом второго компаратора нуль-органа по напряжению, выходы первого и второго элементов ЗАПРЕТ соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого использован как прямой выход узла дискретного управления, выходы третьего и четвертого элементов ЗАПРЕТ соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого использован как инверсный выход узла дискретного управления.

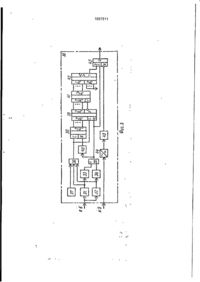

2. Устройство по п. 1, отличающееся тем, что узел определения длительности полупериодов тока в силовой цепи тиристоров выполнен в виде первого и второго компараторов, входы которых использованы как второй вход узла определения длительности полупериодов тока в силовой цепи тиристоров, выходы соединены с входами соответствующих формирователей импульсов записи и первым и вторым соответственно запрещающими входами элемента ЗАПРЕТ, информационный вход которого соединен с выходом генератора импульсов, выход элемента ЗАПРЕТ соединен со счетными входами двоичного счетчика и вычитающего счетчика, выходы формирователей импульсов записи соединены с первым и вторым входами элемента ИЛИ, выход которого соединен с входом формирователя импульсов сброса и входом записи вычитающего счетчика, выход формирователя импульсов сброса соединен с входом сброса двоичного счетчика, выходы которого соединены с входами данных вычитающего счетчика, выходы которого соединены с информационными входами формирователя модуля, управляющий вход которого соединен с выходом окончания счета вычитающего счетчика, выходы - с входами цифрового компаратора, выход которого соединен с D-входом D-триггера, тактовый вход которого соединен с выходом элемента ИЛИ, а вход сброса - с выходом элемента задержки, вход которого соединен с выходом преобразователя переменного напряжения в постоянное, вход которого использован как первый вход узла определения длительности полупериодов тока в силовой цепи тиристоров, а выход D-триггера использован как выход узла.

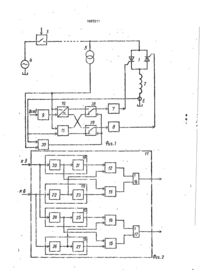

Текст

Изобретение относится к электротехнике и может быть использовано s статических компенсаторах реактивной мощности. Цель изобретений - снижение перенапряжений в силовой цепи и обеспечение управления тиристорами в переходных режимах. С зтой целью при переходном процессе первоначальный угол управления тиристорами 1 определяется моментом появления напряжения. Все последующие углы управления до окончания переходного процесса соответствуют моментам перехода тока через ноль и изменяются в соответствии с естественным переходным процессом. По окончании переходного процесса узел определения длительности полупериодов тока воздействует на переключатели. Т. о. Й установившемся режиме включение тиристоров осуществляется от фазосдвигающего узла 1 3. п. ф-лы, 6 ил. Изобретение относится к электротехнике, в частности к электроснабжению, и может быть использовано в статических компенсаторах реактивной мощности. Целью изобретения является снижение перенапряжений в силовой цепи и обеспечение управаенмя тиристорами в переходных режимах. На фиг. 1 представлена схема устройства; на фиг. 2 - узла дискретного правления; на фиг. 3 - узла определения деятельности полупериодов тока в силовой цепи тиристоров; на фиг. 4,5 и б - времемчые диаграммы, поясняющие работу устройства. Устройство для управления встречнопараляепьно включенными тиристорами 1, подсоединенными через индуктивность 2 и через управляемый ключ 3 к источнику А переменного напряжения, содержит датчик 5 напряжения сети, датчик 6 тока, два формирователя 7 и 8 импульсов управления тиристорами, ВЫХОЙ первого из которых подсоединен к управляющему электроду первого тиристора, зыход второго - к управлгющему электроду второго г-фистора, регулятор 9 угла управления тиристорами, фаэосмещающий узел 10 с двумя выходами и двумя входами, первый из которых подсоединен к датчику 5 напряжения сети, а второй - к выходу регулятора 9 угла управления тиристорами, узел 11 дискретного упраалемия с двумя входами, первый из которых подсоединен к датчику 5 напряжения сети, а второй- «датчику б тока, и двумя выходами. Узел 11 дискретного упрэйления состоит из чечыоех элементов ЗАПРЕТ 12-'.5 (фиг. 2) с 1697211 щего счетчика 39, счетные входы которых одчим запрещающим входом и одниг-і сигподсоединены к выходу элемента ЗАПРЕТ нальным входом, двух элементоо ИЛИ 16 36, причем вихорь» ДБОИЧПОГО счетчика 38 и 17, нуль-оргача 18 по напряжению и подсоединены к D-входам вычитающего нуль-оргаиэ 19 потоку, гэодый из которых состоит мз ДЕух компараторов с дифферен- 5 счетчика 39, аход ЗДРЧСИ коюро;э подсоецирующими элементами. Выход компаратодинен к выходу элемента ИЛИ 35, формирора 20 напряжения подсоединен к вателя 40 импульса сброса, вход которого запрещающему входу элемента ЗАПРЕТ 13, подсоединен к выходу элемента ИЛИ 35, а з через дифференцирующий элемент 21 к выход - к входу двоичного счетчика 38, форсинельному входу элемента ЗАПРЕТ 12, 10 мирователя 41 модуля, цифрового компзравыход компаратора 22 тока подсоединен к тора 42, входы которого подсоединены к запрещающему входу элемента ЗАПРЕТ 12, выходам формирователя 41 модуля, вхоа через дифференцирующий элемент 23 к дами подсоединенного к выходам вычисигнальному пход/ элемента ЗАГЇРЬТ 13, тающего счетчика 39, выход Р которого выход компаратора 21 напряжения подсое- 15 подсоединен к управляющему входу V фординен к запрешающему входу элемента ЗАмирователя 41 модул«, узла 43 задержки, ПРЕТ 15, а через дифференцирующий преобразователя 34 переменного напряжеэлемент 2Ь і. сигнальному входу элемента ния в постоянное, пход которого является ЗАПРЕТ 14, выход компаратора 26 тока подпервым входом узла 30, а выход подсоедисоединен к запрещающему входу элемента 20 ней к еходу узла 43 задержки, и D-триггера ЗАПРБТ 14, а через дифференцирующий 45, R вход которого подсоединен к выходу элемент 2/ к сигнальному входу элемента узла 43 задержки, тактовый С-вход - к выхоЗАПРЕТ 15. Выходы элементов ЗАПРЕТ 12 ду элемента ИПИ 35, D-вход - к выходу и 13 подсоединены к входам первого элецифрового компаратора 42, а выход являетмента ИЛИ 16, выход которого чвляется 25 ся выходом узла 30 прямым выходом узла 11 дискретного упРабота уст ройства заключается в следуравления выходы элементов ЗАПРЕТ 14 м ющем. 15 подсоединены у входам второго элеменПри отсутствии напряжения сети (U=0) та ИЛИ 17, выход которого рвляется инверуровень напряжении из первом входе узла сным выходом узла 11. Устройслво содержит также п,ъз переключателя 23 и 29 30 30 равен нулю. Нз выходе преобразователя 44 переменного напряжения в постоянное и с двумя сигнальними входами м одним упна выходе уїна 43 задержки уровень напряравляющим входом, причем вторые входы жения также оавен нулю, и низкий уровень переключателей ?8 и 29 подсоединены к напряжения на R-эходе D-триггера 45 удервыходам фазосмещающего узла 10, их пер35 живает выходное напряжение D триггера вые входы - к выходам узла 11 дискретного на низком уровне независимо от сигналов управления,» /зел ЗО определения длительпа D-зходе D-триггера, т. е. напряжение на ности полупериодов тока в силовой цепч выходе узла 30 равно нулю, переключатели тиристоров с двумя входами, выходом под28 \л 29 подключают входы формирователей соединенный к управляющим входам переключзтзлей 28 и 29. второй вход которого 40 7 и 8 к выходам узла 11 дискретного управления, синхроимпульсы на которых при подсоединен г датчику 6 тока, первый вход этом отсутствуют. Импульсы управления тик датчику 5 напряжения сети. Узеп 30 выристорами не формируются, ток индуктивполнен s виде первого 31 и второго 32 комности отсутствует, и сигнал на втором в/оде параторов (фмг. 3), входы которых язляются ВТООУМ входом узла, первого 33 и второго 45 узла 30, а значит, и на входе первого 31 и второго 32 компараторов раьем нулю Вы34 формировал слей импульсов записи, г і е ходное напргже.ше компараторов 31 и 32 ментя WПИ 35, первой вход котороїо подсотакже равно нулю и воздействует нг запресдине:( к выходу перэого формирователя 33, щающие входы элемента ЗАПРЕТ 36, котоа второй вход - к выходу второго формирователя 34 импульсов записи, элемента ЗА- 50 рый блокирует прохождение импульсов генератора 37 ка счетные С-зжоды лооичноПРЕТ 36, генератооа 3? импульсов, причем го сметчика 3d'л вичмтающего счетчика 39, о вы\олы перпого 31 и второго 32 кемпэраторезультате чего состояние счетчиков 38 и 39, роз подсоединены соответственно к входу предварительно установленных в ноль, не первого ЗЭ '• второго 34 формирователей нмпульсоз записи и соответственно к 5S изменяется и напряжение ив их вы/одах первому и второму запрещающим вхосохраняет низкий уровень Выходное надам элемем'а ЗАГРЕТ 36, иход которого пряжение цифрового ксгмгмраюоэ 42 при ' гюдсогдтк-ш к выход4/ генератора 37 имЗГОЇ-І ИМРЄТ высокий уровень пульсоз, доо''чного "четммкй 38 и сычита:оПрін включении упрааляе^'ого кпюча 3 в сети появляется напряжение и, которое че 1697211 рез датчик 5 поступает на вход узла 30 определения длительности полупериодов тока. На выходе преобразователя 44 переменного напряжения в постоянное устанавливается высокий уровень напряжения, 5 однако на выходе узла 43 задержки, а значит, на R-входе D-триггера 45 уровень напряжения сохраняется низким в течение времени задержки, составляющем около 2 гг, тем самым блокируется на этс время 10 воздействие на D-триггер 45 сигнала с выхода цифрового компаратора 42. На выходе D-триггерз 45 уровень напряжения не изменяется и равен нуію. Поэтому переключатели 28 и 29 остаются в прежнем положении, 15 т. е. подключают входы формирователей 7 и8 к выходам узла 11 дискретного управления. Напряжение U сети через датчик 5 поступает также на первый вход узла 11 20 дискретного управления, т. е. на вход нульоргана 18 по напряжению, и при появлении, например, положительной полуволны напряжения сети U на выходе компаратора 20 напряжения напряжение U20 изменяется с 25 уровня логического "0" на уровень логической " 1 " . Этот перепад напряжения выделяется дифференцирующим элементом 21 и в виде синхроимпульса напряжения U?i поступает на сигнальный вход элемента'ЗА- 30 ПРЕТ 12, на запрещающем входе которого отсутствует напряжения U22 с выхода компаратора 22 по току с уровнем логической ' "V, что является сигналом разрешения. Поэтому на выходе элемента ЗАПРЕТ 12 появ- 35 ляется синхроимпульс напряжения Ui2. проходящий через элемент ИЛИ 16 м переключатель 28 на вход формироаателя 7 импульсов управления тиристорами, который формирует импульс управления с необходи- 40 мыми параметрами (длительностью и мощностью). Происходит включение тиристора на положительной полуволне напряжения сети в ноадент времени to, соответствующий моменту подачи напряжения из сеть, Появ- 45 ляется положительная полуволна тока индуктивности і, которая чеоез датчик 6 токэ поступает на второй вход узла 11 дискретного управления тиристорами, т. е. на вход нуль-органа 19 по току, что вызывает из^е- 50 нение напряжения Узз на выходе компаратора 26 тока с уроэня логической " " і " на уровень логического "0", что является сигналом запрета для элемента ЗАПРЕТ 14, тем самым блокируется прохождение емнхро- 55 мм'іуяьеа напряжения ІІ25 на запуск,Формирователя 3 *лмпульсо& управления тиристорами. Запуск формирователя В происходит не па синхроимпульсу 025, соответствующему моменту появления отри цательного напряжения сети, а по синхроимпульсу U2T. соответствующему моменту окончания положительной полуволны тока. В этот моненг еоеменм уровень напряжения 1^6 на выходе компаратора 26 тока изменяется с уровня логического "0" на уровень логической " 1 " , выделяется дифференцирующим заементом 27 и з виде синхооимпульса напряжения U27 беспрепятственно проходит через элемент ЗАПРЕТ 15, тзк как на запрещающем входе этого элемента присутствует в это йремя напряжение U?4 от компаратора 24 напряжения с уровнем логической ' ' 1 " , что является сигналом разрешения. Происходит включение тиристора на отрицательной полуволне напряжения в момент времени, соответствующий моменту окончания предыдущей положительной полуволны тока. При появлении отрицательной полуволны тока уровень напряжения U22 на выходе компаратора 22 тока изменяется с уровня логической " 1 " на уровень логического "0", что является сигналом зэпрета для элемента ЗАПРЕТ 12, тем самым блокируется прохождение синхроимпульса напряжения U21. соответствующего моменту появления положительной полуволны напряжения сети. Запуск формирователя 7 ПРОИСХОДИТ теперь уже не по синхроимпульсу напряжения ІІ21. а по синхроимпульсу U23. соответствующему моменту окон» тываемым нуль-органом по току в момент перекода ТОІҐЗ ин^устивности через ноль, последующие синхроимпульсы нуль-органа по напряжению блокируются элементами ЗАПРЕТ, Такой синхронизацией обеспечивается естественный переходной процесс включения индуктивности р сеть ійременного напряжения, про* • дающий с постепен 697211 но вира^нгвачїщимілся амплитудами и длительностями пол/ноли тока При появлении тока индуктивности сигнал с датчика 6 гокэ поступает на первый вход узчэ 30 определения длительности полуперлодоа гокз т. о поступает на вход первого 31 и второ г о 32 компараторов, которие сраЭзтыв&ют СООТРЄТСТВЄННО на положительной и отрицательной полуволна); тока. При этом на ввГ'ояе сооі ветствующего компаратора ПОЯВПЙЄТСЯ сиг чаї разрешения, длительность которого равна дл^гепь ности ПОЛУВОЛНЫ т о к а , что разрешает прохождение через аяемєнт ЗА 1НЕТ 36 тактовых импульсов от геиератооз 37 импульсов Hd счетные С-в-соді' счетчиков 38 и 39. Двоичным счетчик. оЗ преобразует длительность положительной (отрицательной) полуволны токэ в двдичньій код В момент окончания полуволны тока сигнал разрешения на выходе соответствующего компаратора 31 (32) исчезает, элемент ЗАПРЕТ 36 блокирует сметные С-входы счетчиков 38 и 39, а на выходе соответствующего форміюовэтепи 33 (З*3) импульсов записи в момент перехода тока через ноль формируется короткий мппульс canwcfi, который через элемент ИЛИ 35 разрешает запись двоичного числа с в\,лсрв двоичного счэтчика 33 а оыЧЧІРЮЩИИ счетчик 39 и поступает на С-вход D-триггера 45 По спаду импульса записи формируется пмпу/іьс сброса в формирователе 40, который устанавливает двоичный счетчик 38 в М( \oame (нулевое) состояние При появлении следующей отрицательной (положительно**) погуволгы тока соответствующей «©"паратой 32 (31) вырабатывает сигнал разрешения счета, и преобразование ДЯМТелЬИОСТИ ПОЛУВОЛНЫ В £,а0ИЧ!'Ш1 кодсчеїч'.сом 38 ы/;ет аналогично. Одк&єоеиенно S'«11 >ЇТЧЮІДМЙ счетчик 39 производи операцию текушего вычитания двоичного числа, записанного ча предыдущей полуволне тока, и двоичного «исяа последующей (текущей) пояуоолиы тока. Результат вычитания м^ счетчика ЗУ ч'эрез формирователь 4 1 , оиесиечивзющий выделение модуля очэнсстм поступает на входы цифрового ромпаряіор? 42 Пои равенстве дпителыюстей положительной и огрицателытоР1 полуволн гока уіидугтнвности иа выходе цифрового компаратора 42 появляется напряжение высокого уровня Пои поступлении импульса записи нз С-вход D-трчггсра АЪ не его выходе пойплкется нзпояженио аусокого уровня Таким образом, по ОІ;ОМ«*ІНИИ переходною процессч, т. е. при равенстве длительности положительной м отрицйтельно^ полуволн тока, сигнал на выходе узла 50 определении длительно 5 10 15 20 25 30 35 40 45 50 55 8 полупериодов тока устанавтивается разным единице и переключатели 28 и 29 подсоединяют к ауоду формирователей 7 и 8 выходы фазосмещающего узла 10. БклюHQHMQ тсіристоров в установившемся режиме п р о и с х о д и т по с и н х р о и м п у л ь с а м , вырабатываемым фазосмещающим узлом по сигналам регулятора 9. В результате обеспечиваетсч надежное управлениетирмй о р а м и как а переходном, так и в устаноfu вшемся режиме Таким обрзздм, в устройстве первоначальное включение тиристоров соответствует м о м е н т / подключения кисточнику переменного напряжения, т е. момент включения тиристора на первой полуволне напряжения синхронизирован с моментом появления напряжения и определяется пуль-органом по напряжению, а на всех последующих полуволнах до окончания перех о д н о г о п р о ц е с с а момент включения тиристоров определяется нуль-органом по току, синхроимпульсы нуль-органа по напряжению блокируются элементами ЗАПРЕ1 по сигналам иуль-органа по току По окончании переходного процесса узел определения длительности пол/периодов тока воздействует нз переключаіель и в установившемся режиме включение тиристоров осуществляется ог фазосмещающего узла, определяющего угол включения тиристоров по сигналу регулятора угла управления Таким образом, при переходном процессе первоначальный угол управления тиристорэмп определяется,нуль-органом по напряжению и соответствует моменту появления напряжения, псе последующие углы управления на каждом полуволне напряжения при переходном процессе определяются нуль-органом по току, соответствуют моментам перехода тока через ноль и являются величиной, изменяющейся а соответствии с естественным переходным процессом В итоге обеспечивается мгновенное подключение индуктивности к сети, что снижает перенапряжение в сети, повышает устойчивость режима работы сети и повышает надежность функционирования подключенного к ней ол?:

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for back-to-back connection thyristor control

Автори англійськоюCherevan Serhii Mykolaiovych, Tymchenko Oleksandr Viktorovych

Назва патенту російськоюУстройство для управления встречно-параллельно включенными тиристорами

Автори російськоюЧеревань Сергей Николаевич, Тимченко Александр ВикторовичЫ

МПК / Мітки

МПК: H02M 1/08

Мітки: керування, пристрій, тиристорами, включеними, зустрічно-паралельно

Код посилання

<a href="https://ua.patents.su/8-16293-pristrijj-dlya-keruvannya-zustrichno-paralelno-vklyuchenimi-tiristorami.html" target="_blank" rel="follow" title="База патентів України">Пристрій для керування зустрічно-паралельно включеними тиристорами</a>

Попередній патент: Пересувна водозабірна споруда

Наступний патент: Відкидне сидіння, наприклад, парашутиста

Випадковий патент: 2-((4-аміно-5-(тіофен-2-ілметил)-4н-1,2,4-триазол-3-іл)тіо)-n'-(2-хлор-6-фторбензиліден)ацетогідразид, який проявляє актопротекторну активність