Запам’ятовуючий пристрій зі змінним форматом даних

Номер патенту: 24128

Опубліковано: 30.10.1998

Автори: Гриценко Володимир Ілліч, Мудла Борис Гордійович, Корнієнко Григорій Іванович, Беляєв Анатолій Констянтинович, Горша Леонід Юхимович

Текст

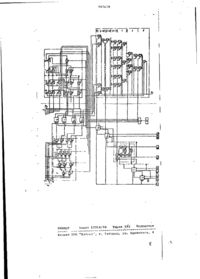

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 987678 Союз Советских Социалистических Республик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22)ЗаявленоЮ.08.81 (21) 3323615/18-24 с присоединением заявки № Государственный комитет СССР по делам изобретений и открытий (23) Приоритет (51|М.Кп.3 G 11 ]С 11/00 ~ Опубликовано 07.01.83. Бюллетень № 1 |53|УДКб81.327 Дата опубликования описания 0 7.01.83 (088.8) А.К. Беляев, Л.Е. Горша, В.И. Гриценко, Г.И.Корниенко и Б.Г.Мудла (72) Авторы изобретения (71) Заявитель Ордена Ленина институт кибернетики АН Украинской ССР (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПЕРЕМЕННЫМ ФОРМАТОМ ДАННЫХ 1 Изобретение относится к запоминающим устройствам и может быть использовано при создании вычислительных систем, работающих со словами информации различной длины, а также при необходимости параллельного обмена информацией с группами устройств. Известно запоминающее устройство с переменным форматом данных, в котором применяется разбиение памяти на блоки и циклическое считывание информации из этих блоков, причем порядок обхода блоков изменяется [1]. Недостатком данного устройства является низкая надежность. Наиболее близким к предлагаемому является запоминающее устройство с переменным форматом данных, содержащее блоки ЗУ, дешифратор номера блока, элемент ИЛИ, ЗУ слов, переключатели, управляющую шину режима, адресные шины, общую шину данных и выходную шину данных, причем адресвые шины подключены к входам дешифраторов номеров блока и . первым к входам ЗУ слов, выход дешифратора номера блока подключен к первому входу элемента ИЛИ, шина управления режимом подключена к другому входу элемента ИДИ и к первым входам переклю 10 15 20 25 чателей, выход элемента ИЛИ подключен к другому входу ЗУ слов, выход которого подключен к'вторым входам первого и второго переключателей, выход первого переключателя подключен к общей шине данных и к второму входу третьего переключателя, выходы второго и третьего переключателей подключены к второй шине данных [2]. Недостатком известного устройства является низкая надежность, так как в нем не предусмотрена защита эон памяти, используемых двумя различными абонентами, а также затруднено совмещение режимов вывода данных и режима вычислений, что приводит к снижению быстродействия устройства. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с переменным форматом данных, содержащее накопители, первые входы которых объединены и являются управляющим входом устройства, и первый регистр, введены блоки коррекции адреса, матрицы коммутаторов, блок выборки, информации, группы регистров, дешифратор и второй регистр, причем выход первого регистра подключен к первым 98767Я входам блоков коррекции адреса, вторые яхолы которых соединены с первыми входами коммутатор в первой и второй матриц, одними из входов блока выборки информации и выходами дешифратора, вход которого подключен к выходу второго регистра, первый выход каждого бпока коррекции адреса , кроме последнего, соединен с третьим входом последующего блока коррекции адреса, второй выход и чет10 вертый вход каждого блока коррекции адреса,кроме первого,подключены соответственно к пятому и шестому входам предыдущего блока коррекции адреса,выходы регистров первой и второй групп соединены соответственно с шестыми и седьмыми входами соответствующих блоков коррекции адреса, первый выход последнего из которых подключен к вторым входам накопителей, первым входом коммутаторов третьей матрицы и другому входу блока выборки информации , вторые входы коммутаторов каждого столбца, кроме первого, первой матрицы соединены с выходами коммутаторов предыдущего столбца первой матрицы, выходы коммутаторов последнего столбца первой матрицы подключены к третьим входам накопителей, вторые входы коммутаторов каждого столбца, кроме последнего, второй 30 матрицы и вторые и третьи входы коммутаторов каждого столбца, кроме последнего, третьей матрицы соединены с выходами коммутаторов последующего столбца третьей матрицы, третьи входы одних из коммутаторов каждого столбца второй матрицы подключены к выходам коммутаторов соответствующей 'строки предыдущего столбца "второй матрицы, а третьи входы других 40 коммутаторов- каждого столбпа второй матрицы - к выходам коммутаторов соответствующего столбца третьей матрицы, вторые и третьи входы коммутаторов последнего столбца третьей матрицы соединены с выходами накопи- 45 телей, выходы одних из накопителей соединены с вторыми входами коммутаторов последнего столбца второй матрицы, выходы которых являются одними из выходов устройства, выходы других накопителей являются другими выходами устройства, четвертые входы накопителей соединены с выходами блока выборки информации, управляющие входы которого являются входами вы- ,55 борки устройства, информационными входами которого являются вторые входы коммутаторов первого столбца первой матрицы и третьи входы коммутаторов первой матрицы. Кроме того, каждый блок коррекции адреса содержит сумматора по модуле два, коммутаторы, вычитатели,шиф-""" t ратор и умножитель, причем выход пер L лого сумматора по модулю два подключен, к первому входу первого' коммутатора выход которого соединен с первым входом первого вычитателя, выходы которого подключены соответственно к первому входу второго коммутатора и первому входу умножителя, второй вход которого соединен с выходом второго сумматора по модулю даа, вход которого подключен к выходу второго коммутатора, второй вход которого соединен с выходом шифратор а , входы третьего сумматора по модулю два подключены соответственно к выходу первого коммутатора и выходу умножителя, а выход является первым выходом блока, входами которого с первого по четвертый являются первый вход первого сумматора по модулю два, второй и третий входы первого коммутатора и второй вход первого сумматора по модулю два, вход шифратора подключен к первому входу второго вычитателя и является пятым входом блока, шестым входом которого является второй вход второго коммутатора, третий вход умножителя- является седьмым входом блока и соединен с вторым входом второго вычитателя, выход которого является вто- • рым выходом блока. При э том блок выборки информации содержит группы коммутаторов и мультиплексоров по числу накопителей, / причем первые входы коммутаторов каждой группы объединены и являются одними из входов блока, первые входы мультиплексоров групп язлшотеп друч им входом блока, второй вход мультиплексора первой группы и юторые входы коммутаторов групп являются управляющими входами блока, первый и второй выходы мупьтиплексоров каждой группы подкл*лтены к третьим предам соответствующих коммутаторов сднокмеиной группы, выходы коммутаторов каждой группы, кроме последней,, соединены с входами СООТВЄТСЇЬ'/Ю^ЧХ мультиплексоров последующей ГР/ППЕЛ, выходы коммутаторов последней группгсг являются иыходами блока. На чертеже изображена функцлокальсхема предаваемого у с т р о й ' ; д а . Устройство содержит накопитечи ] p ~ l m _ , , где Т У 1 - целое 'шс г ;о, инР формационные входы 2 о - 2 т _ ^ и информационные выходы З о ~ З т _ 4 , первую матрицу коммутаторов 4, состоящую ьи. і = от 0 до (га-1) сгопбцов по j - от 0 до і коммутаторов 4 в стопбце, вторую и третью матрицы коммутаторов Ь и 6 с числом столбцов (ггі-і), блоки 7 0 -7 ум коррекции адреса, каждый кз которых содержит первый сумматор 8 по модулю дв-1, первый коммутатор Я, первый ьычитатель іб, в * ,рой комму-татору 11 , дешифратор ! 2 , вхорой сум ная 987678 матор 13 по модулю два, умножитель 14, третий сумматор 15 по модулю ,два и второй вычитатель 16. Устройство содержит также первый регистр 17, предназначенный для хранения относительного адреса, первую группу ре5 гистров 18^-18^,, предназначенных для хранения адреса начала участка памяти, вторую группу регистров 19^19 т , предназначенных для установки 'размера участка, второй регистр 20, 10 предназначенный для хранения кода формата данных, дешифратор 21 и блок 22 выборки информации, содержащий m групп коммутаторов 23 и мультиплексоров 24. На чертеже обозначены вхо- 15 ды 25 выборки и управляющий вход 26 устройства. Количество накопителей 1 Ід-Іет!.^ равно 2** с объемом N и длиной слова Є разрядов (где N и Є - целые числа). 20 Устройство работает следующим образом. Со словами переменной длины запоминающее устройство работает таким образом, что по заданному адре25 су может быть произведена запись или считывание слов с информационной длиной, определяемой типом формата данных, при этом каждому циклу работы памяти соответствует свой формат дан- *п ных. В процессе работы память разбивается на участки, ячейки которых используются при работе с форматом определенного типа. Участок памяти за- ,_ дается адресом начала участка А ^ и размером М, а в пределах участка соблюдается относительная адресация. При работе устройства с одним из форматов данных реализуется обход участков памяти, отведенных для работы с 40 другими форматами данных, и органи1 зуется параллельная работа 2 накопителей 1 0 — 1щ - -- При работе с т-ым і старшим форматом одновременно работаютвсе накопители 1 О -1 Г П _ 1 , поэтому 45 разбиение памяти на участки начинается со старшего формата. Объем памяти по этому формату равен V m = N, Если при этом задан размер М * 0 участка памяти, то объем памяти, который 50 может использоваться при работе с (т-1)~ым форматом, уменьшается и составляет Чтобы при работе с (т-1) форматом обойти участок памяти, отведенный старшему формату, адрес памяти следует несколько скорректировать. Эту операцию выполняют блоки 7р-7 т . На выходе блока 7 ^ формируется физический адрес памяти, соответствующий заданному формату. Каждый из блоков 70-7/уи_її формирует адрес памяти А^ и величину объема памяти Vj . Смысл адреса памяти An-i состоит в том, что 55 65 при нулевых участках памяти форматов, старших чем І, он равен физическому адресу памяти А , при этом объем пай 1 мяти по і-му формату равен 2 "''N (2^С)-разрядных слов. Формирование адреса памяти А происходит следующим образом. На первый вход сумматора 8 с регистра 17 поступает относительный адрес А, где он складывается с адресом начала зоны А ^ , который поступает на второй вход сумматора 8 с 1-го регистра 18, Полученная сумма (А + Ац,,) подается на первый вход коммутатора 9, а на его третий вход подается адрес памяти А ^ ^ предыдущего блока 1^л • При наличии на втором входе коммутатора 9 единичного управляющего сигнала-, который соответствует работе памяти с i-ым форматом, коррекции подвергается либо абсолютный адрес по і-му формату (А + А Н 1 ) , либо адрес А^(у„,). Формование адреса памяти АИі- производится в соответствии со следующим выражением где Е(Х) - функция выделения целой части аргумента X? А - адрес на выходе коммутатора 9. Приведенное выражение реализуется следующим образом. На первый вход вычитателя 10 поступает адрес А| второй и третий входы первого коммутатора и второй Источники информации, вход первого сумматора по модулю принятые во внимание при экспертизе два, вход шифратора подключен к п е р 1. Патент Великобритании » 1524135, вому входу второго вычитателя и я в - ал кл. G 4 С^опублик. 1978. ляется входом блока, шестым входом 2. Патент США № 4092728, которого является второй вход в т о кл. G 06 F 3/00, опублик. 1976 рого коммутатора, третий вход умножи(прототип). рицы[И третьи входы коммутаторов первой матрицы. 2. Устройство по п . 1, о т л и ч а ю щ е е с я тем,что каждый блок коррекции адреса содержит сумматоры по модулю два,коммутаторы,вычитатели, шифратор и умножитель, причем выход первого сумматора по модулю д в а п о д ключен к первому входу первого коммутатора, выход которого соединен с 10 пераым входом первого вычитателя,! выходы которого подключены с о о т в е т ственно к первому входу второго коммутатора и первому входу умножителя, 987678 РНИШІИ Закаэ 10314/40 Тираж 592 Филиап ПРП "Пэт^нг*, г . Ужгород, ул. Подписное Проектная. Ї

ДивитисяДодаткова інформація

Автори англійськоюHrytsenko Volodymyr Illich

Автори російськоюГриценко Владимир Ильич

МПК / Мітки

Мітки: пристрій, даних, змінним, форматом, запам'ятовуючий

Код посилання

<a href="https://ua.patents.su/8-24128-zapamyatovuyuchijj-pristrijj-zi-zminnim-formatom-danikh.html" target="_blank" rel="follow" title="База патентів України">Запам’ятовуючий пристрій зі змінним форматом даних</a>

Попередній патент: Програмний пристрій приоритетного обслуговування запитів

Наступний патент: Пристрій для відображення інформації на екрані телевізійного індікатора

Випадковий патент: Пристрій захисту трансформатора струму від пошкоджень перенапругами