Швидкодіючий багатошаровий персептрон, що гнучко масштабується

Формула / Реферат

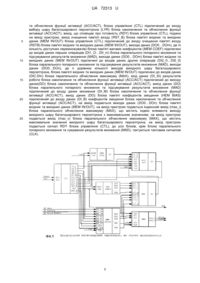

Швидкодіючий багатошаровий персептрон, що гнучко масштабується, що містить блок управління(CTL), блок паралельного попарного множення та підсумування результатів множення(MAD), блоки пам'яті вагових коефіцієнтів (MEM BIAS, MEM COEFF), блок пам'яті вхідних та вихідних даних (MEM IN/OUT), блок накопичення результатів множення та підсумування і обчислення функції активації (АСС/АСТ), який відрізняється тим, що в ньому наявний блок паралельного обчислення максимуму, до входу управління (CTL), як зовнішній вхідний сигнал, підключений сигнал скидання (RST), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, сигнал одного чи кількох елементів вхідного вектора багатошарового персептрона (IN_Data), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, підключено сигнал адреси вхідної пам'яті (IN_Address), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, підключений сигнал дозволу запису одного чи кількох елементів вхідного вектора багатошарового персептрона (IN_Write_Enable), адресний вихід для вагових коефіцієнтів (AD__C) блока управління (CTL) підключений до адресного входу (ADDR) блока пам'яті коефіцієнтів (MEM COEF), адресний вихід для коефіцієнтів зміщення(АР_В) блока управління (CTL) підключений до адресного входу (ADDR) блока коефіцієнтів зміщення (MEM BIAS), адресний вихід для запису результату роботи блока накопичення та обчислення функції активації (АСС/АСТ) (AD_S) блока управління (CTL) підключений до адресного входу (DI_SI) для запису результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід дозволу запису результатів роботи(WE_S) блока накопичення та обчислення функції активації (АСС/АСТ) блока управління (CTL) підключений до входу дозволу запису (WE_SI) результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід дозволу пересилання даних від пам'яті вхідних даних до пам'яті вихідних даних (ІС_ІМ) блока управління (CTL) підключений до входу дозволу пересилання даних від пам'яті вхідних даних до пам'яті вихідних даних (WE_IC) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід вибору банку вихідної пам'яті(MS_IM) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) блока управління (CTL) підключений до входу вибору банку вихідної пам'яті (AD MUL) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід команди накопичення (АСС_А) блока управління (CTL) підключений до входу команди накопичення (АСС_А) блока накопичення та обчислення функції активації (АСС/АСТ), вихід вибору функції активації (АСТ_А) блока управління (CTL) підключений до входу вибору функції активації (ACT) блока накопичення та обчислення функції активації (АСС/АСТ), вихід скидання (RST_A) блока накопичення та обчислення функції активації (АСС/АСТ) блока управління (CTL) підключений до входу скидання (RST) блока накопичення та обчислення функції активації (ACC/ACT), вихід вибору шару багатошарового персептрона (LAY_A), з яким буде працювати блок накопичення та обчислення функції активації (АСС/АСТ), блока управління (CTL) підключений до входу вибору шару багатошарового персептрона (LYR) блока накопичення та обчислення функції активації (АСС/АСТ), вихід, що сповіщає про готовність (RDY) блока управління (CTL), подано на вихід пристрою, вихід очищення пам'яті входу (RST_B) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) блока управління (CTL) підключений до входу очищення пам'яті входу (RSTB) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), виходи даних (DO0…DOm), де m кількість доступних перемножувачів) блока пам'яті вагових коефіцієнтів (MEM COEF) підключені до входів даних перших операндів (DI1_O…DIl_m) блока паралельного попарного множення та підсумування результатів множення (MAD), виходи даних (DO0…DOm) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) підключені до входів даних других операндів (DI2_0…DI2_0) блока паралельного попарного множення та підсумування результатів множення (MAD), виходи даних (DO0…DOn), де n дорівнює кількості виходів вихідного шару багатошарового персептрона, блока пам'яті вхідних та вихідних даних (MEM IN/OUT) підключені до входів даних (DIC.DIn) блока паралельного обчислення максимуму (МАХ), вхід даних (DI_SI) результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) підключений до виходу даних(DO) блока накопичення та обчислення функції активації (АСС/АСТ), вихід даних (DO) блока паралельного попарного множення та підсумування результатів множення (MAD) підключений до входу даних множення (DI_M) блока накопичення та обчислення функції активації (АСС/АСТ), вихід даних (DO) блока пам'яті коефіцієнтів зміщення (HEM BIAS) підключений до входу даних (DI_B) коефіцієнтів зміщення блока накопичення та обчислення функції активації (АСС/АСТ), на вихід подаються виходи даних (DO0…DOn) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), на вихід пристрою подається індексний вихід (mах_і) блока паралельного обчислення максимуму (МАХ), що містить індекс елемента виходу вихідного шару багатошарового персептрона з максимальним значенням, на вихід пристрою подається вихід (max_v) блока паралельного обчислення максимуму (МАХ), що містить максимальне значення вихідного шару багатошарового персептрона, на вихід пристрою подається сигнал RDY блока управління (CTL), до усіх блоків, крім блока паралельного попарного множення та сумування результатів множення (MAD), тактуються тактовим сигналом (CLK).

Текст

Реферат: UA 72313 U UA 72313 U 5 10 15 20 25 30 35 40 45 50 55 60 Швидкодіючий багатошаровий персептрон, що гнучко масштабується електроннообчислювальний пристрій, призначений, в основному, для класифікації образів, як графічних, так і звукових у режимі реального часу чи швидше. В цілому його можна використовувати для стохастичного вирішення погано специфікованих задач з великою кількістю вагових коефіцієнтів, після отримання їх одним з методів машинного навчання. Він є периферійним пристроєм ПЕОМ і підключається до неї через контролер одного зі швидкісних інтерфейсів. Відомо, що існує багатошаровий персептрон [1, с. 288], що має значно відмінну архітектуру від швидкодіючого багатошарового персептрона, що гнучко масштабується, але подібний функціонал. До його недоліків відноситься те, що кількість нейронів шару персептрона обмежується кількістю перемножувачів, так як на кожен нейрон необхідний один перемножувач. Крім того, якщо персептрон виконує задачу класифікації, то обчислення максимального значення вихідного шару персептрона покладається на ПЕОМ, яка виконуватиме це послідовним способом, також у зв'язку з цим існують великі накладні витрати на пересилання виходу нейронної мережі в пам'ять ПЕОМ. Запропонований швидкодіючий багатошаровий персептрон, що гнучко масштабується не залежить від кількості перемножувачів, так як в ньому використовується один блок паралельного попарного множення та підсумування результатів множення (MAD), який утилізує повністю ресурс перемножувачів на мікросхемі. Крім того в ньому присутній блок паралельного обчислення максимуму (МАХ), що виконує його обчислення швидше (один такт) за ПЕОМ (кількість залежить від кількості виходів). Найближчим аналогом швидкодіючого багатошарового персептрона, що гнучко масштабується (фіг. 1), є NeuroFPGA [2], що як і швидкодіючий багатошаровий персептрон, що гнучко масштабується, містить блок управління (CTL), блок пам'яті вхідних та вихідних даних (MEM IN/OUT), блока паралельного попарного множення та сумування результатів множення (MAD), блок пам'яті коефіцієнтів зміщення (MEM BIAS), блок накопичення та обчислення функції активації (АСС/АСТ). До його недоліків відноситься те, що кількість входів NeuroFPGA обмежується кількістю перемножувачів та неможливість обчислити максимальне значення виходу нейронної мережі паралельно прямо на мікросхемі. Як згадано вище, ці недоліки у запропонованому швидкодіючому багатошаровому персептроні, що гнучко масштабується відсутні, що дозволяє досягнути технічного результату. Швидкодіючий багатошаровий персептрон на найвищому рівні абстракції працює як перемножувач матриць на вектор і значення його виходу може бути описане наступним виразом: L1=М1Х+В1 L2=M2L1+B2 L1=M1L1+Bi OUT=Lk=MkLk-1+Bk, де Li - значення на виході шару персептрона, Мі - матриця вагових коефіцієнтів, Ві - вектор коефіцієнтів зміщення, X вхідний вектор, значення виходу персептрона. Додатково у запропонованому багатошаровому персептроні обчислюється max (OUT). Запропонований швидкодіючий багатошаровий персептрон, що гнучко масштабується включає наступні блоки: блок управління (CTL), блок пам'яті вхідних та вихідних даних (MEM IN/OUT), блок пам'яті коефіцієнтів зміщення (MEM BIAS), блок пам'яті вагових коефіцієнтів (MEM COEF), блок паралельного попарного множення та підсумування результатів множення (MAD), блок паралельного обчислення максимуму (МАХ), блок накопичення та обчислення функції активації (АСС/АСТ). Всі блоки працюють синхронно, крім блока паралельного попарного множення та сумування результатів множення (MAD). Блок управління (CTL) виставляє адреси на всі блоки пам'яті, дає віддає команду запису (WE_IN) та команду очищення для вхідної пам'яті (RSTB) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), визначає функцію активації (ACT), віддає команду накопичення (АСС), віддає команду скидання (RST), визначає номер робочого шapy (LYR) для блока накопичення та обчислення функції активації (АСС/АСТ). Для блока паралельного попарного множення та підсумування результатів множення (MAD) вхідними даними є: вихід блока пам'яті вхідних та вихідних даних (MEM IN/OUT) та блока пам'яті вагових коефіцієнтів (MEM COEF), кількість паралельних операцій множення дорівнює кількості доступних перемножувачів. Дані з виходу блока паралельного попарного множення та підсумування результатів множення (MAD) потрапляють до блока накопичення та обчислення функції активації (АСС/АСТ), де результати множення накопичуються до тих пір, поки не буде обчислено елемент вектора результату операції Мі х Li-1. Далі до цього результату додається відповідний елемент вектора В і, який отримується з блока пам'яті коефіцієнтів зміщення (MEM BIAS), та обчислюється одна з двох можливих функцій активації: Хевісайда чи лінійна. Функція Хевісайда повертає максимально допустиме значення 1 UA 72313 U 5 10 15 20 25 30 при додатному значенні аргументу, та нуль - при від'ємному. Лінійна функція активації виконує зсув результату вліво так, щоб вихідний результат не перевищував максимально допустиме значення виходу. Вихід блока накопичення та обчислення функції активації (АСС/АСТ) підключений до входу даних блока пам'яті вхідних та вихідних даних (MEM IN/OUT), і по команді блока управління (СТL) вони в ньому зберігаються. До блока пам'яті вхідних та вихідних даних (MEM IN/OUT) підключено паралельний обчислювач максимуму, що обчислює максимум вхідного вектора за наступним принципом, описаним у псевдокоді: if(IN1 > IN2 and IN1 > IN2 and IN1 > IN3 … and IN1 > INn) return IN1; if(IN2 > IN1 and IN2 > IN3 and IN1 > IN4 … and IN2 > INn) return IN2; if(INi > IN1 and INi > IN2 and INi > IN3 … and INi > INn) return Ini. Вказані оператори "if" (якщо) можна обчислити паралельно, тим самим отримавши можливість обчислити функцію максимуму за один такт. Блок пам'яті вхідних та вихідних даних (фіг. 2) (MEM IN/OUT) має два блоки пам'яті: вхідної (В) та вихідної (А). У блок вхідної пам'яті (сигнали _SI) записують дані з блока накопичення та обчислення функції активації (АСС/АСТ), вміст його можна скинути сигналом RSTB. По сигналу WE_IС з блока вхідної пам'яті відбувається запис у блок вихідної пам'яті. По сигналам типу _IN відбувається запис вхідного вектора. Можливий запис кількох елементів одночасно, якщо розширити шину даних (зручно у випадку використання 128 бітної шини РСІ). На вихід подається кількість елементів, рівна кількості перемножувачів, а так як кількість елементів вхідного вектора може бути більшою за кількість перемножувачів, передбачена можливість мультиплексування з блока вихідних даних (В) на вихід блока пам'яті вхідних та вихідних даних (MEM IN/OUT) через керуючий вхід AD_MUL. Роботу самого блока управління (CTL) можна описати як роботу кінцевого автомата таблицею переходів та таблицею станів переходів в своїх рядках містить можливі стани кінцевого автомата, а в колонках умови для переходу. Таблиця станів містить в своїх рядках стани, а в стовпчиках необхідні операції з виходами чи внутрішніми станами пристрою для переходу у Таблиця 1 Таблиця переходів № Q(1) Q(2) Q(3) Q(4) Q(5) Q(6) Q(7) Q(8) Q(9) Q(10) Q(11) Q(12) Q(13) Q(14) Q(15) Q(16) RST 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 RDY 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Semaphore Clayers Couts MS_imem AD_S Поч. стан Довільний Довільний 0 Довільний ~2 ( i-1) 0 Довільний 2 ( i-1) ~Li_max ~(ni-1) 0 ~(ni-1) Довільний 2 ( -1) Li_max 0 (ni-1) 2 ( -1) ~Li max -Li_max Довільний 0 (ni-i) 2 ( -1) ~Li_max Li_max Довільний 0 (ni-1) 2 ( -1) Li_max ~Li_max Довільній 0 (ni-1) 2 ( -l) Li_max Li_max Довільний 1 Довільний 2 Довільний ~2 ( -1) 2 Довільний 2 ( -1) 3 Довільний ~2 ( -1) 3 -(ni-1) Довільний 2 ( -1) Li_max 3 Довільний 2 ( -1) ~Li_ max (ni-1) 3 (ni-1) Довільний 2 ( -1) Li_max 35 2 UA 72313 U Таблиця 2 Таблиця станів № AD_C AD_В AD_S WE_S IC_IM MS_IM ACC_A ACT_A RST_A LAY_A RDY RST_В semaphore clayers couts Q(1) 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 Q(2) 0 +1 Q(3) + 1 0 +1 0 +1 Q(4) + 1 0 +1 0 G +1 Q(5) + 1 0 +1 0 0 1 1 +1 2 ( -1) 0 Q(6) + 1 +1 +1 0 0 0 0 +1 +1 Q(7) + 1 +1 0 0 0 0 0 +1 +1 Q(8) + 1 +1 +1 0 0 0 0 1 1 +1 2 ( -1) 0 Q(9) + 1 +1 0 0 0 0 0 1 1 +1 2 ( -1) 0 Q(10) 1 0 0 +1 Q(11) 0 0 +1 Q(12) 1 0 0 +1 Q(13) 0 0 +1 Q(14) 0 1 0 +1 Q(15) 0 1 +1 Q(16) 0 1 1 +1 5 відповідний стан. Крім входів та виходів, у таблицях містяться внутрішні стани пристрою, умовно позначені як: Semaphore, Clayers, Couts, MS_imem, AD_S. Деякі записи у таблиці можуть бути не зрозумілі з першого погляду, ось їх тлумачення: nі кількість результатів роботи блока паралельного попарного множення та сумування результатів множення (MAD), необхідна отримання значень одного з елементів виходу і-го шару Li max ~Li max 15 20 25 число, що не рівне максимальній кількості нейронів у будь-якому з шарів. 2 (i-1) 10 число, рівне максимальній кількості нейронів у одному з шарів число, що позначає номер і-го шару, отримується наступним чином: 2 (і-1), і має співпадати з тим і, що вказаний у стані Couts, AD_S та MS_imem У динаміці пристрій працює наступним чином, описаним у псевдокоді: ЗАСЛАТИ В MEM IN/OUT ВХІДНИЙ ВЕКТОР; ВІДПРАВИТИ СИГНАЛ RST ДЛЯ БЛОКА CTL; ПРИВЕСТИ ЗНАЧЕННЯ ВСІХ СИГНАЛІВ БЛОКА УПРАВЛІННЯ У ПОЧАТКОВЕ ПОЛОЖЕННЯ; ПОКИ КІЛЬК. ШАРІВ МАКС. КІЛЬК. ШАРІВ ВИКОНАТИ ПОКИ КІЛЬК. ВИХ. ШАРУ МАКС. КІЛЬК. ВИХ. ШАРУ ВИКОНАТИ ПОКИ КІЛЬК. РЕЗ. MAD nі ЗБІЛЬШИТИ КІЛЬК. РЕЗ. MAD на 1; НАКОПИЧИТИ РЕЗУЛЬТАТ MAD В АКУМУЛЯТОР; ЗБІЛЬШИТИ АДРЕСУ. ДЛЯ MEM COEF НА 1; ЗБІЛЬШИТИ ЗНАЧЕННЯ КЕРУЮЧОГО ВХОДУ МУЛЬТИПЛЕКСОРА MEM IN/OUT HA 1; КІНЕЦЬ ПОКИ ДОДАТИ ДО АКУМУЛЯТОРА ВІДПОВІДНИЙ ЕЛЕМЕНТ З MEM BIAS; ЗБІЛЬШИТИ АДРЕСУ MEM BIAS НА 1; ОБЧИСЛИТИ ФУНКЦІЮ АКТИВАЦІЇ; ЗАПИСАТИ РЕЗУЛЬТАТ У MEM IN/OUT; ЗБІЛЬШИТИ АДРЕСУ ВХІДНОЇ ПАМ'ЯТІ MEM IN/OUT НА 1; ВСТАНОВИТИ ЗНАЧЕННЯ КЕРУЮЧОГО ВХОДУ МУЛЬТИПЛЕКСОРА; MEM IN/OUT РІВНИМ 0; 3 UA 72313 U 5 10 15 20 СКИНУТИ БЛОК АСС/АСТ; КІНЕЦЬ ПОКИ ПЕРЕСЛАТИ ДАНІ ЗІ ВХІДНОЇ ПАМ'ЯТІ У ВИХІДНУ; ЗМІНИТИ ТИП ФУНКЦІЇ АКТИВАЦІЇ АСС/АСТ; ЗМІНИТИ НОМЕР ШАРУ ДЛЯ АСС/АСТ; ВИКОНАТИ ОЧИСТКУ ВХІДНОЇ ПАМ'ЯТІ; КІНЕЦЬ ПОКИ ВИСТАВИТИ СИГНАЛ RDY; ПРОЧИТАТИ МАКСИМАЛЬНЕ ЗНАЧЕННЯ ТА ЙОГО ІНДЕКС ВИХІДНОГО ШАРУ; ЗА НЕОБХІДНОСТІ ПРОЧИТАТИ ВСІ ЗНАЧЕННЯ ВИХІДНОГО ШАРУ; ОЧІКУВАТИ СИГНАЛ RST. Як правило такого роду пристрій реалізується на програмованій логіці типу FPGA чи ASIC та описується засобами мови опису апаратного забезпечення Verilog HDL чи VHDL. Той факт, що алгоритм роботи пристрою та його структура формалізовані, є необхідним та достатнім підтвердженням того, що пристрій можливо реалізувати. Очевидним підтвердженням можливості досягнення технічного результату, є безпосередньо архітектура запропонованого пристрою. Джерела інформації: 1. AMOS R. OMONDI "FPGA Implementations of Neural Networks" - Sringer, 2006 - 364 p. 2. Daniel Ferrer, Ramiro Gonz’lez, Roberto Fleitas and others "NeuroFPGA-Implementing Artificial Neural Networks on Programmable Logic Devices" ФОРМУЛА КОРИСНОЇ МОДЕЛІ 25 30 35 40 45 50 55 60 Швидкодіючий багатошаровий персептрон, що гнучко масштабується, що містить блок управління(CTL), блок паралельного попарного множення та підсумування результатів множення(MAD), блоки пам'яті вагових коефіцієнтів (MEM BIAS, MEM COEFF), блок пам'яті вхідних та вихідних даних (MEM IN/OUT), блок накопичення результатів множення та підсумування і обчислення функції активації (АСС/АСТ), який відрізняється тим, що в ньому наявний блок паралельного обчислення максимуму, до входу управління (CTL), як зовнішній вхідний сигнал, підключений сигнал скидання (RST), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, сигнал одного чи кількох елементів вхідного вектора багатошарового персептрона (IN_Data), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, підключено сигнал адреси вхідної пам'яті (IN_Address), до блока пам'яті вхідних та вихідних даних (MEM IN/OUT), як зовнішній вхідний сигнал, підключений сигнал дозволу запису одного чи кількох елементів вхідного вектора багатошарового персептрона (IN_Write_Enable), адресний вихід для вагових коефіцієнтів (AD__C) блока управління (CTL) підключений до адресного входу (ADDR) блока пам'яті коефіцієнтів (MEM COEF), адресний вихід для коефіцієнтів зміщення(АР_В) блока управління (CTL) підключений до адресного входу (ADDR) блока коефіцієнтів зміщення (MEM BIAS), адресний вихід для запису результату роботи блока накопичення та обчислення функції активації (АСС/АСТ) (AD_S) блока управління (CTL) підключений до адресного входу (DI_SI) для запису результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід дозволу запису результатів роботи(WE_S) блока накопичення та обчислення функції активації (АСС/АСТ) блока управління (CTL) підключений до входу дозволу запису (WE_SI) результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід дозволу пересилання даних від пам'яті вхідних даних до пам'яті вихідних даних (ІС_ІМ) блока управління (CTL) підключений до входу дозволу пересилання даних від пам'яті вхідних даних до пам'яті вихідних даних (WE_IC) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід вибору банку вихідної пам'яті(MS_IM) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) блока управління (CTL) підключений до входу вибору банку вихідної пам'яті (AD MUL) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), вихід команди накопичення (АСС_А) блока управління (CTL) підключений до входу команди накопичення (АСС_А) блока накопичення та обчислення функції активації (АСС/АСТ), вихід вибору функції активації (АСТ_А) блока управління (CTL) підключений до входу вибору функції активації (ACT) блока накопичення та обчислення функції активації (АСС/АСТ), вихід скидання (RST_A) блока накопичення та обчислення функції активації (АСС/АСТ) блока управління (CTL) підключений до входу скидання (RST) блока накопичення та обчислення функції активації (ACC/ACT), вихід вибору шару багатошарового персептрона (LAY_A), з яким буде працювати блок накопичення 4 UA 72313 U 5 10 15 20 25 та обчислення функції активації (АСС/АСТ), блока управління (CTL) підключений до входу вибору шару багатошарового персептрона (LYR) блока накопичення та обчислення функції активації (АСС/АСТ), вихід, що сповіщає про готовність (RDY) блока управління (CTL), подано на вихід пристрою, вихід очищення пам'яті входу (RST_B) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) блока управління (CTL) підключений до входу очищення пам'яті входу (RSTB) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), виходи даних (DO0…DOm), де m кількість доступних перемножувачів) блока пам'яті вагових коефіцієнтів (MEM COEF) підключені до входів даних перших операндів (DI1_O…DIl_m) блока паралельного попарного множення та підсумування результатів множення (MAD), виходи даних (DO0…DOm) блока пам'яті вхідних та вихідних даних (MEM IN/OUT) підключені до входів даних других операндів (DI2_0…DI2_0) блока паралельного попарного множення та підсумування результатів множення (MAD), виходи даних (DO0…DOn), де n дорівнює кількості виходів вихідного шару багатошарового персептрона, блока пам'яті вхідних та вихідних даних (MEM IN/OUT) підключені до входів даних (DIC.DIn) блока паралельного обчислення максимуму (МАХ), вхід даних (DI_SI) результатів роботи блока накопичення та обчислення функції активації (АСС/АСТ) підключений до виходу даних(DO) блока накопичення та обчислення функції активації (АСС/АСТ), вихід даних (DO) блока паралельного попарного множення та підсумування результатів множення (MAD) підключений до входу даних множення (DI_M) блока накопичення та обчислення функції активації (АСС/АСТ), вихід даних (DO) блока пам'яті коефіцієнтів зміщення (HEM BIAS) підключений до входу даних (DI_B) коефіцієнтів зміщення блока накопичення та обчислення функції активації (АСС/АСТ), на вихід подаються виходи даних (DO0…DOn) блока пам'яті вхідних та вихідних даних (MEM IN/OUT), на вихід пристрою подається індексний вихід (mах_і) блока паралельного обчислення максимуму (МАХ), що містить індекс елемента виходу вихідного шару багатошарового персептрона з максимальним значенням, на вихід пристрою подається вихід (max_v) блока паралельного обчислення максимуму (МАХ), що містить максимальне значення вихідного шару багатошарового персептрона, на вихід пристрою подається сигнал RDY блока управління (CTL), до усіх блоків, крім блока паралельного попарного множення та сумування результатів множення (MAD), тактуються тактовим сигналом (CLK). 5 UA 72313 U Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

Назва патенту англійськоюQuick-response flexibly scalable multilayer perceptron

Автори англійськоюZakharchenko Taras Leonidovych

Назва патенту російськоюБыстродействующий многослойный гибко масштабируемый персептрон

Автори російськоюЗахарченко Тарас Леонидович

МПК / Мітки

МПК: G06F 15/00

Мітки: персептрон, багатошаровий, швидкодіючий, гнучкої, масштабується

Код посилання

<a href="https://ua.patents.su/8-72313-shvidkodiyuchijj-bagatosharovijj-perseptron-shho-gnuchko-masshtabuehtsya.html" target="_blank" rel="follow" title="База патентів України">Швидкодіючий багатошаровий персептрон, що гнучко масштабується</a>

Попередній патент: Вхідний пристрій схеми порівняння струмів

Наступний патент: Спосіб ранньої діагностики гемодинамічних порушень у хворих на цироз печінки невірусного походження

Випадковий патент: Корм для гусей