Формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами

Номер патенту: 96435

Опубліковано: 10.02.2015

Автори: Харченко Вячеслав Сергійович, Коробков Микола Григорович, Рубанов Василь Григорович, Коробкова Олена Миколаївна

Формула / Реферат

Формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами, який містить: два реверсивні двійкові лічильники, які мають вхід подачі імпульсів синхронізації, вхід налагодження на режим підсумовування/віднімання, вхід дозволу синхронного паралельного завантаження і входи подачі даних, вхід дозволу режиму рахування, вхід асинхронної установки у нульовий стан, вихід переповнювання; інвертор; перший і другий елементи АБО; ланцюжок, що складається з послідовно поєднаних резистора і конденсатора; синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І, при цьому спільна точка послідовно сполучених резистора і конденсатора поєднана з інформаційним входом D-тригера, з одним входом першого та другого двовходового елемента І; вихід першого двовходового елемента І з'єднано зі входом асинхронної установки D-тригера у нульовий стан; другий вхід другого елемента І з'єднано з виходом першого елемента АБО, один з входів якого з'єднано з виходом D-тригера; вихід другого елемента АБО з'єднано зі входом дозволу синхронного паралельного завантаження першого лічильника; вихід переповнювання першого лічильника з'єднано зі входом інвертора, вихід якого з'єднано зі входом дозволу режиму лічби першого лічильника; входи паралельного завантаження даних лічильників утворюють входи програмування формувача на задані часові параметри імпульсів на виході формувача; вихід другого елемента І з'єднано зі входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, створюючи вхід формувача - вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; тактовий вхід D-тригера створює вхід подачі імпульсів запуску, який відрізняється тим, що введено: третій і четвертий елементи АБО; перший і другий елементи І-НІ; другий інвертор; елемент АБО-НІ; третій елемент І; перший і другий JK-тригери зі входом асинхронної установки у нульовий стан, при цьому входи другого елемента АБО з'єднано з виходами другого, четвертого розрядів першого лічильника і виходом елемента АБО-НІ; вихід першого інвертора з'єднано зі входом третього елемента І, з першими входами першого і другого елементів І-НІ і другим входом першого елемента І; вихід переповнення другого лічильника з'єднано з другим входом першого елемента І-НІ, зі входом четвертого елемента АБО, входом другого інвертора, вихід якого з'єднано з другим входом другого елемента І-НІ; вихід першого елемента І-НІ з'єднано зі входом дозволу режиму лічби другого лічильника; вихід другого елемента І-НІ з'єднано зі входами J і К першого JK-тригера, першим входом третього елемента АБО і першим входом елемента АБО-НІ; другий вхід елемента АБО-НІ з'єднано з інверсним виходом першого JK-тригера; прямий вихід першого JK-тригера з'єднано з другим входом третього елемента АБО і входом дозволу синхронного паралельного завантаження другого лічильника; прямий вихід другого JK-тригера з'єднано зі входом першого елемента АБО і першим входом четвертого елемента АБО, вихід якого з'єднано зі входом третього елемента І; вихід третього елемента І утворює вихід формувача; вихід третього елемента АБО з'єднано зі входами J і К другого JK-тригера; тактові входи JK-тригерів з'єднано зі входом формувача; входи асинхронної установки у нульовий стан JK-тригерів з'єднано з входом другого елемента І.

Текст

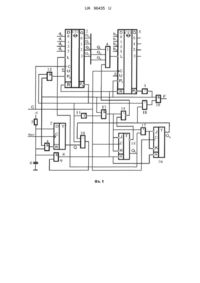

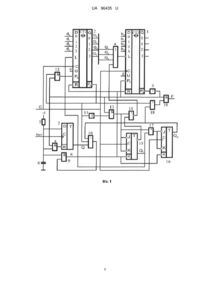

Реферат: Формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами містить: два реверсивні двійкові лічильники, які мають вхід подачі імпульсів синхронізації, вхід налагодження на режим підсумовування/віднімання, вхід дозволу синхронного паралельного завантаження і входи подачі даних, вхід дозволу режиму рахування, вхід асинхронної установки у нульовий стан, вихід переповнювання; інвертор; перший і другий елементи АБО; ланцюжок, що складається з послідовно поєднаних резистора і конденсатора; синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І. Введено: третій і четвертий елементи АБО; перший і другий елементи ІНІ; другий інвертор; елемент АБО-НІ; третій елемент І; перший і другий JK-тригери зі входом асинхронної установки у нульовий стан. UA 96435 U (54) ФОРМУВАЧ СИМЕТРИЧНОЇ ОДИНОЧНОЇ ТРИІМПУЛЬСНОЇ КОДОВОЇ СЕРІЇ З ПРОГРАМОВАНИМИ ЧАСОВИМИ ПАРАМЕТРАМИ UA 96435 U UA 96435 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до імпульсної техніки і призначена для формування симетричної одиночної триімпульсної кодової серії з програмованою тривалістю імпульсів в серії і паузи між ними. Відомі формувачі, що містять кварцовий задавальний генератор, який працює в безперервному режимі, пристрій синхронізації і вихідний пристрій, що забезпечує формування необхідних імпульсів, часові параметри яких визначаються часовими параметрами імпульсів, що подаються на вхід (Тактовий генератор. Авторське свідоцтво СРСР № 307502. - Бюлетень винаходів. № 20, 1971; Тактовий генератор. АС СРСР № 354544. - Бюлетень винаходів. № 30, 1972). Патенти на корисну модель України №№ 55951, 61312, 65818, 71778, 72614. Недолік відомих пристроїв - обмежені функціональні можливості, обумовлені налагоджуванням на фіксований режим параметрів імпульсів. Найбільш близьким за технічною суттю і результатом, що досягається, є формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами, (патент на корисну модель № 53542 від 11.10.2010), який містить: два реверсивні двійкові лічильники, кожен з яких має вхід подачі імпульсів синхронізації, вхід налагодження на режим підсумовування/віднімання, вхід дозволу режиму рахування, вхід дозволу синхронного паралельного завантаження і входи подачі даних, вхід асинхронної установки у нульовий стан, вихід переповнювання; інвертор; перший і другий елементи АБО; ланцюжок, що складається з послідовно поєднаних резистора і конденсатора; синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І, при цьому спільна точка послідовно сполучених резистора і конденсатора поєднана з інформаційним входом D-тригера, з одним входом першого та другого двовходового елемента І; вихід першого двоходового елемента І з'єднано зі входом асинхронної установки D-тригера у нульовий стан; другий вхід другого елемента І з'єднано з виходом першого елемента АБО, один з входів якого з'єднано з виходом D-тригера; вихід другого елемента АБО з'єднано зі входом дозволу синхронного паралельного завантаження першого лічильника; вихід переповнювання першого лічильника з'єднано зі входом інвертора, вихід якого з'єднано зі входом дозволу режиму лічби першого лічильника; входи паралельного завантаження даних лічильників утворюють входи програмування формувача на задані часові параметри імпульсів на виході формувача; вихід другого елемента І з'єднано зі входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, створюючи вхід формувача вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; тактовий вхід D-тригера створює вхід подачі імпульсів запуску. Недолік відомого пристрою - обмежені функціональні можливості. В основу корисної моделі поставлено задачу удосконалення формувача періодичної послідовності триімпульсних кодових серій з програмованими параметрами шляхом введення нового складу елементів і нової організації взаємних з'єднань між ними. Поставлена задача вирішується тим, що в формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами, який містить: два реверсивні двійкові лічильники, які мають вхід подачі імпульсів синхронізації, вхід налагодження на режим підсумовування/віднімання, вхід дозволу синхронного паралельного завантаження і входи подачі даних, вхід дозволу режиму рахування, вхід асинхронної установки у нульовий стан, вихід переповнювання; інвертор; перший і другий елементи АБО; ланцюжок, що складається з послідовно поєднаних резистора і конденсатора; синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І, при цьому спільна точка послідовно сполучених резистора і конденсатора поєднана з інформаційним входом D-тригера, з одним входом першого та другого двовходового елемента І; вихід першого двовходового елемента І з'єднано зі входом асинхронної установки D-тригера у нульовий стан; другий вхід другого елемента І з'єднано з виходом першого елемента АБО, один з входів якого з'єднано з виходом D-тригера; вихід другого елемента АБО з'єднано зі входом дозволу синхронного паралельного завантаження першого лічильника; вихід переповнювання першого лічильника з'єднано зі входом інвертора, вихід якого з'єднано зі входом дозволу режиму лічби першого лічильника; входи паралельного завантаження даних лічильників утворюють входи програмування формувача на задані часові параметри імпульсів на виході формувача; вихід другого елемента І з'єднано зі входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, створюючи вхід формувача вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; тактовий вхід D-тригера створює вхід подачі імпульсів запуску, відповідно до корисної моделі введено: третій і четвертий елементи АБО; перший і другий елементи І-НІ; другий інвертор; елемент АБО-НІ; третій елемент І; перший і другий JK-тригери зі входом асинхронної установки 1 UA 96435 U 5 10 15 20 25 30 35 40 45 50 55 60 у нульовий стан, при цьому входи другого елемента АБО з'єднано з виходами другого, четвертого розрядів першого лічильника і виходом елемента АБО-НІ; вихід першого інвертора з'єднано зі входом третього елемента І, з першими входами першого і другого елементів І-НІ і другим входом першого елемента І; вихід переповнення другого лічильника з'єднано з другим входом першого елемента І-НІ, зі входом четвертого елемента АБО, входом другого інвертора, вихід якого з'єднано з другим входом другого елемента І-НІ; вихід першого елемента І-НІ з'єднано зі входом дозволу режиму лічби другого лічильника; вихід другого елемента І-НІ з'єднано зі входами J і K першого JK-тригера, першим входом третього елемента АБО і першим входом елемента АБО-НІ; другий вхід елемента АБО-НІ з'єднано з інверсним виходом першого JK-тригера; прямий вихід першого JK-тригера з'єднано з другим входом третього елемента АБО і входом дозволу синхронного паралельного завантаження другого лічильника; прямий вихід другого JK-тригера з'єднано зі входом першого елемента АБО і першим входом четвертого елемента АБО, вихід якого з'єднано зі входом третього елемента І; вихід третього елемента І утворює вихід формувача; вихід третього елемента АБО з'єднано зі входами J і K другого JKтригера; тактові входи JK-тригерів з'єднано зі входом формувача; входи асинхронної установки у нульовий стан JK-тригерів з'єднано з виходом другого елемента І. Заявлений формувач має новий склад елементів і нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості. Технічний результат, як наслідок цих властивостей, розширення області використання і функціональних можливостей формувача. На фіг. 1 приведена схема формувача. Формувач містить: перший (1) і другий (2) реверсивні двійкові лічильники, кожен з яких має вхід налагодження на режим підсумовування/віднімання U, вхід подачі тактових імпульсів С, вхід дозволу паралельного завантаження L і входи подачі даних D 0-D3, вхід Р0 дозволу/заборони режиму лічби, вхід асинхронної установки у нульовий стан R, вихід переповнювання Р4; перший (15) і другий (16) JK-тригери зі входом асинхронної установки у нульовий стан; перший (3) і другий (11) інвертори; перший (10), другий (4), третій (17) і четвертий (18) елементи АБО; перший (8), другий (9) і третій (19) елементи І; перший (12) і другий (13) елементи І-НІ; елемент АБО-НІ (14); ланцюжок з послідовно сполучених резистора (5) і конденсатора (6), підключеного до джерела живлення +Е; синхронний D-тригер (7) зі входом R асинхронної установки у нульовий стан. Загальна точка послідовно сполучених резистора 5 і конденсатора 6 з'єднана з інформаційним входом D-тригера 7, з одним входом елементів 8, 9. Вихід елемента 8 з'єднано зі входом асинхронної установки D-тригера 7 у нульовий стан. Другий вхід елемента 9 з'єднано з виходом елемента 10. Вихід елемента 9 з'єднано зі входами R асинхронної установки у нульовий стан JK-тригерів і лічильників. Один зі входів елемента 10 поєднаний з виходом D-тригера 7, другий - з прямим виходом другого JKтригера і входом елемента 18, вихід якого з'єднано з першим входом елемента 19. Входи елемента 4 з'єднано з виходами другого (Q1), третього (Q2) і четвертого (Q3) розрядів лічильника 1 і виходом елемента 14. Вихід переповнювання лічильника 1 з'єднано зі входом інвертора 3. Вихід інвертора 3 з'єднано зі входом Р0 дозволу режиму лічби лічильника 1, першими входами елементів 12, 13, другим входом елемента 19, вихід якого утворює вихід формувача. Вихід переповнення лічильника 2 з'єднано зі входами елементів 10, 12, 18 і входом інвертора 11, якого з'єднано з другим входом елемента 13. Вихід елемента 13 з'єднано зі входами J і К JK-тригера 15 і входами елементів 14, 17. Другий вхід елемента 14 з'єднано з інверсним виходом JK-тригера 15. Прямий вихід JK-тригера 15 з'єднано зі входом елемента 17 і входом дозволу синхронного паралельного завантаження лічильника 2. Вихід елемента 17 зі входами J і K JK-тригера 16. Входи паралельного завантаження D 0-D3 лічильника 1 утворюють входи b0-b3 налагодження формувача на задану тривалість паузи між імпульсами в серії. Входи паралельного завантаження D0-D3 лічильника 2 утворюють входи d0-d3 налагодження формувача на задану тривалість першого і третього імпульсу в серії. Тактові входи JK-тригерів і лічильників сполучені між собою, створюючи вхід С формувача - вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора. Тактовий вхід С тригера 7 утворює вхід подачі імпульсів запуску (Start) формування вихідних імпульсів. Заявлений формувач має новий склад елементів і нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості. Технічний результат, як наслідок цих властивостей, розширення області використання і функціональних можливостей формувача. Працює формувач в наступній послідовності. Наявність ланцюжка, що складається із поєднаних послідовно резистора 5 і конденсатора 6, підключеного до шини живлячої напруги +Е, при включенні джерела живлення протягом деякого проміжку часу формує рівень логічного нуля на вході R асинхронної установки у нульовий стан 2 UA 96435 U 5 10 15 20 25 30 35 40 45 50 55 60 тригера 7 і входах елементів 8 та 9, забезпечуючи формування рівня логічного нуля на входах R асинхронної установки у нульовий стан відповідно D-тригера, JK-тригерів і лічильників. Після закінчення перехідного процесу, пов'язаного з включенням джерела живлення тригери і лічильники переходять у нульовий стан, формуючи рівень логічного нуля відповідно на виходах Q тригерів і на виходах переповнювання Р4 лічильників, що веде до формування рівня 0 на виході елемента 10, з'єднаного зі входом елемента І 9, що забезпечує підтвердження (блокування) рівня 0 на його виході і по закінченню перехідного процесу, пов'язаного із зарядом конденсатора 6, що забезпечує рівень 0 на входах асинхронної установки у нульовий стан JKтригерів і лічильників. Оскільки режим асинхронної установки у нульовий стан має пріоритет по відношенню до всіх останніх режимів, то до тих пор поки на вході елемента 9 (а отже і на його виході) зберігатиметься рівень логічного нуля, нульовий стан JK-тригерів і лічильників залишатиметься незмінним. Під час вступу імпульсу запуску (Start) на тактовий вхід С тригера 7 по його фронту тригер переходить в одиничний стан (Q=1), формуючи рівень логічної одиниці на вході і виході елемента 10, а отже на вході і виході елемента 9, що забезпечує рівень логічної одиниці на входах R JK-тригерів і лічильників, знімаючи блокування нульового стану. Нульове значення сигналу з прямого виходу JK-тригера 15 надходить на вхід дозволу паралельного завантаження L лічильника 2, готуючи його до прийому інформації зі входів d 0-d3, а нульове значення сигналу з виходу елемента 4 надходить на вхід дозволу синхронного паралельного завантаження L лічильника 1, готуючи його до прийому інформації зі входів b0-b3. Нульове значення сигналу з виходів елементів 13, 17 надходить на входи J і K JK-тригерів, готуючи їх до переходу в одиничний стан. Під час вступу першого (після закінчення перехідного процесу, пов'язаного із зняттям блокування) тактового імпульсу С відбувається перехід JK-тригерів в одиничний стан і паралельне завантаження лічильників значеннями сигналів, що подаються на відповідні входи D0-D3, тобто лічильник 1 переходить у стан B=b3b2b1b0, формуючі одиничне значення на виході переповнення і нульове значення на виході інвертора 3 (вході Р 0 лічильника 1), що веде до переходу D-тригера у нульовий стан, лічильника 1 у режим лічби, а лічильник 2 переходить у стан D=d3d2d1d0, формуючи нульове значення на виході елемента 14 і одиничне значення на виходах елемента 4, 12, 13, 17, тобто на входах L лічильників і на входах J і K JK-тригерів, що забезпечує режим зберігання лічильника 2 і JK-тригерів. І тоді під час вступу другого тактового імпульсу лічильник 1 переходить у стан В-1, стан лічильника 2, рівний d3d2d1d0, і одиничний стан JK-тригерів залишаться незмінними. Під час вступу подальших тактових імпульсів процеси аналогічні, до тих пір, поки зміст лічильника 1 не стане рівним 0, що забезпечує рівень логічного 0 на його виході переповнення і рівень логічної одиниці на виході інвертора 3 (на вході Р0 лічильника 1), рівень логічного 0 на виході елемента 12 (на вході Р 0 лічильника 2), у результаті чого лічильник 1 переходить у режим зберігання, а лічильник 2 - у режим лічби. Одиничний стан JK-тригерів залишиться незмінними. І тоді під час вступу наступного тактового імпульсу лічильник 2 переходить у стан D-1, нульовий стан лічильника 1 і одиничний стан JK-тригерів залишаться незмінними. Під час вступу подальших тактових імпульсів процеси аналогічні, до тих пір, поки зміст лічильника 2 не стане рівним 0001, що забезпечує рівень логічного 0 на виході елемента 4 (на вході Р 0 лічильника 1), у результаті чого лічильник 1 переходить у режим завантаження. З приходом чергового тактового імпульсу лічильник 2 переходить у нульовий стан, лічильник 1 знову переходить у стан В=b3b2b1b0, формуючи одиничне значення на його виході переповнення і на виходах елементів 4, 12, 13, 17, тобто на входах J і K тригерів, і нульове значення на вході Р 0 лічильника 1, що забезпечує режим лічби лічильника 1 і режим зберігання лічильника 2 і JKтригерів. Під час вступу подальших тактових імпульсів зміст лічильника 1 буде зменшуватись, а нульовий стан лічильника 2 і одиничний стан JK-тригерів залишаться незмінними, до тих пір, поки зміст лічильника 1 не стане рівним 0, що веде до формування рівня логічного нуля на входах J і K тригера 15 і тоді з приходом наступного тактового імпульсу тригер 15 переходить у нульовий стан. Одиничний стан тригера 16 і нульовий стан лічильників залишиться незмінним. Під час вступу наступного тактового імпульсу відбувається перехід JK-тригера 15 в одиничний стан, JK-тригера 16 у нульовий стан і паралельне завантаження лічильників значеннями сигналів, що подаються на відповідні входи D0-D3, тобто лічильник 1 переходить у стан B=b3b2b1b0, лічильник 2 переходить у стан D=d 3d2d1d0. Надалі процеси повторюються, але тільки до тих пір, поки зміст лічильника 2 не стане рівним 0, що веде до формування рівня логічного нуля на виході елемента 10, обумовлюючи рівень 0 на вході та виході елемента 9, що приведе до блокування нульового стану JK-тригерів і 3 UA 96435 U 5 10 15 лічильників, а отже, до припинення процесу генерації. Зі вступом наступного імпульсу запуску усі процеси повторюються. Таким чином, після закінчення перехідного процесу, пов'язаного із зняттям блокування, під час вступу на вхід С формувача періодичної послідовності імпульсів з періодом Т на виході переповнення лічильника 1 генерується одиночна серія імпульсів, що містять три імпульси рівної програмованої тривалості і програмованої тривалості паузи між ними. Тривалість імпульсів на виході переповнення лічильника 1 визначається значенням В:t и=ВТ. Тривалість паузи між першим і другим імпульсами визначається значенням D:t п=DT. Тривалість паузи між другим і третім імпульсами на виході переповнення лічильника 1 дорівнює 2Т, і тоді відповідно зі схемою формування імпульсів на виході формувача, отримуємо tи1=tи3=DT, tи2=2T, tп1=tп2=ВТ. На фіг. 2 приведені епюри, що ілюструють роботу для варіанту налагодження В=4, D=7 визначаючого параметри вихідної послідовності імпульсів, тобто тривалість імпульсів в серії tи1=tи3=7Т, tи2=2Т, тривалість паузи між імпульсами в серії t п1=tп2=4Т. На відміну від відомого пристрою формування симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами розширює функціональні можливості формувача. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 20 25 30 35 40 45 50 55 Формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами, який містить: два реверсивні двійкові лічильники, які мають вхід подачі імпульсів синхронізації, вхід налагодження на режим підсумовування/віднімання, вхід дозволу синхронного паралельного завантаження і входи подачі даних, вхід дозволу режиму рахування, вхід асинхронної установки у нульовий стан, вихід переповнювання; інвертор; перший і другий елементи АБО; ланцюжок, що складається з послідовно поєднаних резистора і конденсатора; синхронний D-тригер зі входом асинхронної установки у нульовий стан, перший і другий двовходові елементи І, при цьому спільна точка послідовно сполучених резистора і конденсатора поєднана з інформаційним входом D-тригера, з одним входом першого та другого двовходового елемента І; вихід першого двовходового елемента І з'єднано зі входом асинхронної установки D-тригера у нульовий стан; другий вхід другого елемента І з'єднано з виходом першого елемента АБО, один з входів якого з'єднано з виходом D-тригера; вихід другого елемента АБО з'єднано зі входом дозволу синхронного паралельного завантаження першого лічильника; вихід переповнювання першого лічильника з'єднано зі входом інвертора, вихід якого з'єднано зі входом дозволу режиму лічби першого лічильника; входи паралельного завантаження даних лічильників утворюють входи програмування формувача на задані часові параметри імпульсів на виході формувача; вихід другого елемента І з'єднано зі входами асинхронної установки лічильників у нульовий стан; тактові входи першого та другого лічильників сполучені між собою, створюючи вхід формувача - вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; тактовий вхід D-тригера створює вхід подачі імпульсів запуску, який відрізняється тим, що введено: третій і четвертий елементи АБО; перший і другий елементи І-НІ; другий інвертор; елемент АБО-НІ; третій елемент І; перший і другий JK-тригери зі входом асинхронної установки у нульовий стан, при цьому входи другого елемента АБО з'єднано з виходами другого, четвертого розрядів першого лічильника і виходом елемента АБО-НІ; вихід першого інвертора з'єднано зі входом третього елемента І, з першими входами першого і другого елементів І-НІ і другим входом першого елемента І; вихід переповнення другого лічильника з'єднано з другим входом першого елемента І-НІ, зі входом четвертого елемента АБО, входом другого інвертора, вихід якого з'єднано з другим входом другого елемента І-НІ; вихід першого елемента І-НІ з'єднано зі входом дозволу режиму лічби другого лічильника; вихід другого елемента І-НІ з'єднано зі входами J і К першого JK-тригера, першим входом третього елемента АБО і першим входом елемента АБО-НІ; другий вхід елемента АБО-НІ з'єднано з інверсним виходом першого JK-тригера; прямий вихід першого JK-тригера з'єднано з другим входом третього елемента АБО і входом дозволу синхронного паралельного завантаження другого лічильника; прямий вихід другого JK-тригера з'єднано зі входом першого елемента АБО і першим входом четвертого елемента АБО, вихід якого з'єднано зі входом третього елемента І; вихід третього елемента І утворює вихід формувача; вихід третього елемента АБО з'єднано зі входами J і К другого JK-тригера; тактові входи JKтригерів з'єднано зі входом формувача; входи асинхронної установки у нульовий стан JKтригерів з'єднано з входом другого елемента І. 4 UA 96435 U 5 UA 96435 U Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

Автори англійськоюKorobkov Mykola Hryhorovych, Korobkova Olena Mykolaivna, Rubanov Vasyl Hryhorovych, Kharchenko Viacheslav Serhiiovych

Автори російськоюКоробков Николай Григорьевич, Коробкова Елена Николаевна, Рубанов Василий Григорьевич, Харченко Вячеслав Сергеевич

МПК / Мітки

МПК: H03K 3/78

Мітки: формувач, часовими, параметрами, програмованими, одиночної, кодової, симетрично, серії, триімпульсної

Код посилання

<a href="https://ua.patents.su/8-96435-formuvach-simetrichno-odinochno-triimpulsno-kodovo-seri-z-programovanimi-chasovimi-parametrami.html" target="_blank" rel="follow" title="База патентів України">Формувач симетричної одиночної триімпульсної кодової серії з програмованими часовими параметрами</a>

Попередній патент: Пристрій для дозованої подачі порошку

Наступний патент: Формувач одиночної симетричної триімпульсної кодової серії з програмованими часовими параметрами

Випадковий патент: Плавучий глибоководний хвилелом