Обчислювальний пристрій для апаратного розпаралелення на рівні завдань

Номер патенту: 121574

Опубліковано: 11.12.2017

Автори: Сторожук Олександр Миколайович, Жабін Валерій Іванович, Клименко Ірина Анатоліївна

Формула / Реферат

Обчислювальний пристрій для апаратного розпаралелення на рівні завдань, що містить п блоків обробки інформації, блок вводу даних, блок виводу даних, блок пам'яті заявок, блок реєстраційної пам'яті, регістр актора і регістр дескриптора, блок селектора умови, блок встановлення пріоритету, чергу із буферної пам'яті заявок та регістр буфера завдань, причому перший інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра актора, другий інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра дескриптора, перший інформаційний вихід якого зв'язаний з шиною адреси акторів, яка в свою чергу зв'язана з першим інформаційним виходом регістра актора та другим інформаційним входом блока встановлення пріоритету, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока селектора умови, який в свою чергу через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока реєстраційної пам'яті, який через перший інформаційний вхід зв'язаний із шиною адреси завдань, яка зв'язує другий інформаційний вихід регістра дескриптора та другий і третій інформаційні входи блока пам'яті заявок, який через перший інформаційний вхід зв'язаний із шиною адреси дескрипторів, яка зв'язує четвертий інформаційний вихід регістра актора та четвертий інформаційний вихід регістра дескриптора, також блок пам'яті заявок через перший інформаційний вихід зв'язаний із першим інформаційним входом регістра завдань, який через перший інформаційний вихід зв'язаний із другим інформаційним виходом пристрою, а перший управляючий вихід пристрою зв'язаний із першим управляючим виходом блока буферної пам'яті заявок, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока встановлення пріоритету, який через третій інформаційний вхід зв'язаний із другим інформаційним виходом регістра актора, в якого третій інформаційний вихід через шину зв'язаний із третім інформаційним виходом регістра дескриптора та із другим інформаційним входом блока селектора умови, який відрізняється тим, що додатково містить блок завчасної реконфігурації, який через перший інформаційний вхід зв'язаний із п'ятим інформаційним виходом регістра актора та перший інформаційний вихід якого з'єднаний із четвертим інформаційним входом блока встановлення пріоритету.

Текст

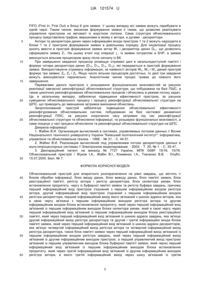

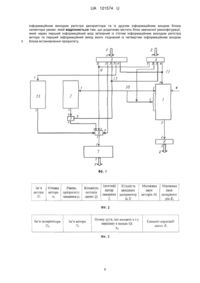

Реферат: Обчислювальний пристрій для апаратного розпаралелення на рівні завдань містить п блоків обробки інформації, блок вводу даних, блок виводу даних, блок пам'яті заявок, блок реєстраційної пам'яті, регістр актора і регістр дескриптора, блок селектора умови, блок встановлення пріоритету, чергу із буферної пам'яті заявок та регістр буфера завдань, причому перший інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра актора, другий інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра дескриптора, перший інформаційний вихід якого зв'язаний з шиною адреси акторів, яка в свою чергу зв'язана з першим інформаційним виходом регістра актора та другим інформаційним входом блока встановлення пріоритету, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока селектора умови, який в свою чергу через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока реєстраційної пам'яті, який через перший інформаційний вхід зв'язаний із шиною адреси завдань, яка зв'язує другий інформаційний вихід регістра дескриптора та другий і третій інформаційні входи блока пам'яті заявок, який через перший інформаційний вхід зв'язаний із шиною адреси дескрипторів, яка зв'язує четвертий інформаційний вихід регістра актора та четвертий інформаційний вихід регістра дескриптора, також блок пам'яті заявок через перший інформаційний вихід зв'язаний із першим інформаційним входом регістра завдань, який через перший інформаційний вихід зв'язаний із другим інформаційним виходом пристрою, а перший управляючий вихід пристрою зв'язаний із першим управляючим виходом блока буферної пам'яті заявок, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока встановлення пріоритету, який через третій інформаційний вхід зв'язаний із другим інформаційним виходом регістра актора, в якого третій інформаційний вихід через шину зв'язаний із третім інформаційним виходом регістра дескриптора та із другим інформаційним входом блока селектора умови, крім того додатково містить блок завчасної реконфігурації, який через перший інформаційний вхід зв'язаний із п'ятим інформаційним виходом регістра актора та перший інформаційний вихід якого з'єднаний із четвертим інформаційним входом блока встановлення пріоритету. UA 121574 U (54) ОБЧИСЛЮВАЛЬНИЙ ПРИСТРІЙ ДЛЯ АПАРАТНОГО РОЗПАРАЛЕЛЕННЯ НА РІВНІ ЗАВДАНЬ UA 121574 U UA 121574 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель стосується обчислювальної техніки і може бути застосована при побудові високопродуктивних обчислювальних систем. Відомий обчислювальний пристрій для систем під управлінням потоку даних, який містить блоки вводу і виводу даних для обчислень, блоки буферної пам'яті даних і команд, блоки обробки інформації, пристрої пам'яті керуючих слів і операндів, регістри адрес і даних. Недоліком даного пристрою є те, що в середовищі формування керуючих слів зберігаються керуючі слова й операнди, що обмежує функціональні можливості пристрою, оскільки не забезпечує виконання алгоритмів в паралельному режимі, при багаторазовому повторенні однакових обчислювальних процесів у циклічному режимі (реалізуються однакові алгоритми з різними даними). Крім цього неможливість суміщення процесів на рівні алгоритмів (задач) приводить до зниження продуктивності пристрою [1]. Відомий також обчислювальний пристрій для систем під управлінням потоку дескрипторів даних, який містить блоки обробки інформації, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреси, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, регістр додаткової пам'яті операнду. Функціональні елементи відомого пристрою формують загальне комунікаційне середовище формування команд на підставі управляючих слів (акторів) та слів даних (дескрипторів), та паралельну обчислювальну структуру, яка складається з кінцевої кількості однотипних блоків обробки інформації [2]. Недоліком відомого обчислювального пристрою є обмежені функціональні можливості, які не забезпечують реалізацію двомісних операцій в рамках ациклічних обчислювальних алгоритмів, а також неможливість - масштабування обчислювальної потужності. Найбільш близьким до корисної моделі по технічній суті є обчислювальний пристрій, який містить n блоків обробки інформації, блок вводу даних, блок виводу даних, блок пам'яті заявок, блок реєстраційної пам'яті, регістр актора і регістр дескриптора, блок селектора умови, блок встановлення пріоритету, чергу із буферної пам'яті заявок та регістр буферу завдань, причому перший інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра актора, другий інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра дескриптора, перший інформаційний вихід якого зв'язаний за допомогою шини адреси акторів з першим інформаційним виходом регістра актора та другим інформаційним входом блока встановлення пріоритету, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока селектора умови, який в свою чергу через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока реєстраційної пам'яті, який через перший інформаційний вхід зв'язаний із шиною адреси завдань, яка зв'язує другий інформаційний вихід регістра дескриптора та другий і третій інформаційні входи блока пам'яті заявок, який через перший інформаційний вхід зв'язаний за допомогою шини адреси дескрипторів з четвертим інформаційним виходом регістра актора та четвертим інформаційним виходом регістра дескриптора, також блок пам'яті заявок через перший інформаційний вихід зв'язаний із першим інформаційним входом регістра завдань, який через перший інформаційний вихід зв'язаний із другим інформаційним виходом пристрою, а перший управляючий вихід пристрою зв'язаний із першим управляючим виходом блока буферної пам'яті заявок, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока встановлення пріоритету, який через третій інформаційні вхід зв'язаний із другим інформаційним виходом регістра актора, в якого третій інформаційний вихід через шину зв'язаний із третім інформаційним виходом регістра дескриптора та із другим інформаційним входом блока селектора умови [3]. Недоліком даного пристрою є непродуктивні витрати часу на здійснення процесу реконфігурації обчислювального середовища на програмованих логічних інтегральних схемах (далі - ШПС) під час розподілу задач. В результаті цього, час витрачений на реконфігурацію, може дорівнювати або навіть бути більшим, ніж час виконання команди. Це вносить критичну часову затримку, що негативно впливає на ефективність обчислень в реконфігурованих обчислювальних системах. В основу корисної моделі поставлено задачу удосконалення відомого обчислювального пристрою шляхом розширення його функціональних можливостей за рахунок введення блока завчасної реконфігурації, що забезпечить поєднування у часі процесів обчислення та реконфігурації обчислювальної структури на ШПС, та підвищить обчислювальну ефективність пристрою. Поставлена задача вирішується тим, що в обчислювальному пристрої, який містить n блоків обробки інформації, блок вводу даних, блок виводу даних, блок пам'яті заявок, блок 1 UA 121574 U 5 10 15 20 25 30 35 реєстраційної пам'яті, регістр актора і регістр дескриптора, блок селектора умови, блок встановлення пріоритету, чергу із буферної пам'яті заявок та регістр буфера завдань, причому перший інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра актора, другий інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра дескриптора, перший інформаційний вихід якого зв'язаний з шиною адреси акторів, яка в свою чергу зв'язана з першим інформаційним виходом регістра актора та другим інформаційним входом блока встановлення пріоритету, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока селектора умови, який в свою чергу через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока реєстраційної пам'яті, який через перший інформаційний вхід зв'язаний із шиною адреси завдань, яка зв'язує другий інформаційний вихід регістра дескриптора та другий і третій інформаційні входи блока пам'яті заявок, який через перший інформаційний вхід зв'язаний із шиною адреси дескрипторів, яка зв'язує четвертий інформаційний вихід регістра актора та четвертий інформаційний вихід регістра дескриптора, також блок пам'яті заявок через перший інформаційний вихід зв'язаний із першим інформаційним входом регістра завдань, який через перший інформаційний вихід зв'язаний із другим інформаційним виходом пристрою, а перший управляючий вихід пристрою зв'язаний із першим управляючим виходом блока буферної пам'яті заявок, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока встановлення пріоритету, який через третій інформаційний вхід зв'язаний із другим інформаційним виходом регістра актора, в якому третій інформаційний вихід через шину зв'язаний із третім інформаційним виходом регістра дескриптора та із другим інформаційним входом блока селектора умови. Згідно з корисною моделлю, до складу обчислювального пристрою добавлено блок завчасної реконфігурації, який через перший інформаційний вхід зв'язаний із п'ятим інформаційним виходом регістра актора, крім того перший інформаційний вихід якого з'єднаний із четвертим інформаційним входом блока встановлення пріоритету, що в результаті забезпечує суміщення в часі обчислювального процесу та процесу реконфігурації обчислювальної структури на ШПС, що в свою чергу зменшує затримки виконання обчислень. Суть корисної моделі пояснюється кресленнями: де на фіг. 1 представлена структурна схема обчислювального пристрою апаратного розпаралелення на рівні завдань, що складається: 1 - блок пам'яті заявок, 2 - блок реєстраційної пам'яті, 3 - регістр актора і 4 - регістр дескриптора, 5 - блок селектора умови, 6 блок встановлення пріоритету, 7 - буферна пам'ять заявок та 8 - регістр буферу завдань, 9 шина адреси акторів, 10 - шина адреси завдань, 11 - шина адреси дескрипторів, 12 - шина даних та 13 - блок завчасної реконфігурації; на фіг. 2 - регістр актора; на фіг. 3 - регістр дескриптора; на фіг. 4 - регістр заявки; на фіг. 5 - регістр блоку кон'юнктура; на фіг. 6 - граф обчислювального процесу завдань. Пристрій працює наступним чином. Обчислювальний процес описується за допомогою W (i l, m) 40 45 50 i графу G = (W, D), де W - множина вершин, D - множина дуг. Кожній вершині відповідає завдання (певний обсяг роботи, процес), а кожній дузі Dji - потік даних, необхідних для виконання завдання. Вихідні дані для кожної задачі підготовляються на підставі графа обчислювального алгоритму G і являють собою набір дескрипторів завдань і даних, що надходять на регістр 3 актора та регістр 4 дескриптора відповідно, а також заздалегідь синтезовану бібліотеку реалізацій функцій. Як компоненти бібліотеки можуть використовуватися програмні модулі, що функціонують в заданому операційному середовищі та виконують необхідні операції, для вирішення задачі, перетворення даних, та які синтезовані на мові конфігурації VHDL (Hardware Description Language), для програмування на ПЛІС. Завдання описується актором (множиною елементів). Для i-oї вершини графа G актор має вигляд: Wi i ,Ni ,Ii , Qi ,pi ,K,Mi ,Ri , n N 55 де ni - ознака актора; i - ім'я актора; Ii - ідентифікатор завдання (команди, програми, процесу); Q i - сумарна кількість потоків даних для завдання (дуг графа, що входять в вершину); pi - рівень пріоритету завдання; Mi - множина імен акторів, для яких і-е завдання готує дані; R i - множина імен потоків даних, які формуються при виконанні і-го завдання. В модифікованому пристрої в кожному акторі зберігається також кількість акторів (K), які формуються при виконанні i-го завдання. Потік даних, який відповідає дузі графа, що з'єднує j-y вершину з i-ю вершиною, характеризується дескриптором, що є множиною елементів: 2 UA 121574 U D ji n ji,Ni , Qi , A ji , де n ji - ім'я (номер) потоку даних (дуги, що входить до i-у вершину); A ji - елемент адресації даних. 5 10 15 20 25 30 35 40 45 Всі вершини графа мають унікальні імена Ni (i l, m) . Елемент адресації визначає місце розташування даних у блоці 2 реєстраційної пам'яті, доступної для кожного процесора. Ім'я актора N i одночасно є ознакою, що відрізняє дескриптор даних від актора. З елементів дескрипторів відповідно до певної процедури F формуються заявки на виконання i-го завдання: F( Wi ,Di ) Zi i ,Pi , A i ,Mi , I . де A i A ji j J - множина елементів адресації даних для і-го завдання; Di D ji j J множина дескрипторів даних для завдання Wi ; J - множина імен вершин графа, пов'язаних вихідними дугами з і-ю вершиною; Mi - маска, що визначає, які дескриптори вихідних даних необхідно формувати при повторному виконанні завдання. Для формування заявок Z i може бути використаний будь-який з обчислювальних модулів 1 (далі - ОМ). Такий обчислювальний модуль будемо називати керуючим, а ОМ, які виконують заявки - виконуючими. Функції керуючого модуля можуть бути покладені на спеціалізований пристрій, який є загальним системним апаратним ресурсом. Також в системі присутній блок часткової реконфігурації 13 (далі - БЧР), в основі якого лежить асоціативна пам'ять, а функції якого можуть бути також покладені на спеціалізований пристрій або ж на інший загальнообчислювальний модуль системи. Реконфігурація прив'язана до типу операції, що несе в собі актор (ідентифікатор завдання Ii ). Якщо в регістр 3 актора надходить слово актор, операція якого не реконфігурована в системі, то даний тип виконуваної функції ставиться в чергу на реконфігурацію на ШПС в блоці 13 часткової реконфігурації (БЧР). При надходженні наступного актора, який має таке саме поле ідентифікатору завдання, в компараторі виконується перевірка на наявність такої функції у черзі на реконфігурацію і пропускається у разі її присутності, в іншому випадку, ім'я актора ставиться у чергу в блок 13 завчасної реконфігурації. Для цього в блоці 13 (БЧР) використовується асоціативна пам'ять. Тегом в якій є поле - ідентифікатор завдання Ii . На компараторі порівнюється новий ідентифікатор завдання (поле Ii регістра актора) та тег пам'яті (поле Ii регістра заявки), при цьому на керуючому виході компаратора формується керуючий сигнал "Hit" (влучання), якщо така функція Ii присутня, інакше формується керуючий сигнал "Miss" (промах) і відбувається запис у чергу блока завчасної реконфігурації 13. В кожній комірці пам'яті зберігається логічний прапорець, що відповідає ознаці зреконфігуровності задачі. Коли формується наступна заявка, в регістрі блока кон'юнктора (далі - БК) знову відбувається звернення в 13 БЧР - до асоціативної пам'яті по ідентифікатору завдання актора, якщо признак зреконфігурованості дорівнює 1 (Рек), функція є у черзі блока 13 завчасної реконфігурації та готові дані в блоці 2 реєстраційної пам'яті, це свідчить, що задача вже сконфігурована і заявка готова до формування. Тобто виконується умова формування заявки. Складність формування заявок полягає в тому, що дані для i-го завдання формуються в різні моменти часу і, крім того, можливо різними ОМ. Також до цього кожна операція перед виконанням має бути зреконфігурована і завантажена в систему, що входить в умову активізації заявки. Умова активізації заявки можна представити як кон'юнкцію: i R i & i & ij , i де R i - ознака реконфігурації заявки, i - умова отримання дескриптора і-го завдання; ji умова отримання зреконфігурованого елемента адресації Ni 50 A ji . Враховуючи унікальність імен - дескрипторів для кожного завдання, умову активізації завдання можна також представити у вигляді: , 1 якщо Сi Qi ; i 0, якщо Сi Qi , 3 UA 121574 U N 5 де С i - число прийнятих в керуючий ОМ дескрипторів з ім'ям i . Другий варіант визначення готовності даних для формування заявки на виконання завдання більш зручний для апаратурної реалізації, так як підрахунок дескрипторів можна виконувати послідовно в часі в міру їх надходження до ОМ, а наявність в кожному акторі кількість акторів (К), які формуються при виконанні i-го завдання, дозволяє спростити процес підрахунку. В управляючому ОМ створюється таблиця (масив об'єктів), і-й рядок Si якої має вигляд: Ni : Si Ii ,Pi , A i ,Li , Ci , Qi , - ім'я рядка; C i - лічильник дескрипторів, L i ji - ознаки наявності дескрипторів даних, які поступили. Число ознак в рядку S i дорівнює числу вхідних потоків даних Q i . У керуючий ОМ вводяться дескриптори і вихідні дані. При надходженні дескрипторів завдань у відповідні позиції рядків таблиці вводяться значення Ii і Pi . При надходженні дескрипторів де 10 Ni даних у відповідні позиції рядків записуються елементи множини A i і відповідні їм ознаки ji . Позиція елементів адресації визначається значеннями n ji , присутніми в дескрипторах завдань. 15 20 25 30 35 Повне накопичення множини A i елементів адресації даних для завдання визначається за допомогою лічильника С i . При надходженні будь-якого дескриптора порівнюються значення Q i і С i , потім С i збільшується на одиницю. Рівність зазначених значень є однією із умово i активізації заявки. Заявка передається у виконуючий ОМ, за готовністю. При цьому обнуляється лічильник С i , тобто система готова для повторного формування заявки з даним ім'ям, якщо це необхідно. У системі одночасно можуть вирішуватися кілька задач. Будь-який ОМ може виконувати функції керуючого та виконуючого модуля (у тому числі одночасно). Вільні ОМ звертаються до керуючих ОМ за заявками. Після виконання завдання керуючому ОМ повертається дескриптор даних, який бере участь при формуванні нової заявки. На стадії формування заявок між модулями пересилаються тільки короткі повідомлення (дескриптори), при цьому безпосередньо переміщуються потоки даних. До складу загального системного ресурсу вводиться блок часткової реконфігурації, який з використанням стандартних засобів підключається до комунікаційного середовища, що забезпечує доступ до нього всіх процесорних модулів. Підготовка завдань згідно з даним методом здійснюється без урахування числа ОМ, а один із ОМ, може виконувати функції керуючого та виконуючого. Слова акторів і даних надходять в пристрій через порти виводу процесорів - інформаційні входи пристрою 1, 2 в блоках 1 та 2 відповідно. До складу пристрою входять два блоки (3, 4) пам'яті з довільним доступом. У пам'яті заявок (далі - ПЗ), блок 4, накопичуються дані, необхідні для формування заявок, а в реєстраційній пам'яті (далі - ПР), блок 3, формуються змінні CTi, що визначають кількість акторів і дескрипторів, що надійшли по інформаційним входом 1 для кожного завдання. Необхідні для формування заявки в блоці 1, елементи Mi, Ri, Qi і Ii актори записуються в ПР N блок 3, за адресами, які визначаються ім'ям i , що передається по інформаційному виході І (використовується необхідне число комірок). Для запису полів A ji дескрипторів даних в блок 4, 40 використовуються адреси, які визначаються значеннями N i і n ji , що передаються по інформаційному вході 3. Значення Q i порівнюється із змінною СТі в блоці 7, яка знаходиться в N блоці 3 (ПР) за адресою, що визначається ім'ям i із його інформаційного входу 1. Рівність значень Q i і СТi означає, що вся інформація для формування заявки Zi в блоці 8, отримана. 45 50 При цьому ім'я N i записується в один з вихідних буферів типу FIFO (First In, First Out) - в блоці 6, відповідно до рівня пріоритету (поле рі управляє мультиплексором М) в блоці 8. Завдяки унікальності імен, кожне слово ( N i *) в буфері однозначно визначає розташування даних у ПЗ в блоці 4, які необхідні для формування заявки Z i в блоці 5. Використовуючи різні механізми доступу до блока 3 (ПР), що визначаються архітектурою системи, процесори можуть самостійно зчитувати необхідну інформацію з блоку З (ПР) для виконання завдання, визначаючи адреси на підставі значень N i * та Q i що отримується по 3 інформаційному вході із блока 1. Це сприяє зниженню витрат апаратури і спрощує рішення задачі взаємного виключення при доступі процесорів до спільного ресурсу. У разі використання безпріоритетних дисциплін обслуговування заявок, відпадає необхідність у декількох чергах 4 UA 121574 U 5 10 15 20 25 30 35 FIFO (First In, First Out) в блоці 6 для заявок. У цьому випадку всі заявки можуть перебувати в одній черзі. Таким чином, механізм формування заявок є таким, що дозволяє реалізувати управління пристроєм на автоматі із жорсткою логікою. Сама структура обчислювального процесу представлена графом, вершинами в якому є актори, а дугами - дескриптори. Актори та дескриптори даних через інформаційні входи пристрою 1 та 2 можуть надходити в блоки 1 та 2 пристрою формування заявок в довільному порядку. Для ініціалізації процесу досить ввести в пристрій формування заявок актор W 1 і дескриптор даних D01, що дозволить сформувати заявку Z1. На цьому етапі код операції Ii , із заявки потрапляє в БЧР, а заявка виконується вільним процесором зразу після сигналу із БК. При завершенні завдання процесор розміщує отримані дані в загальнодоступній пам'яті і формує чотири дескриптора даних (D12, D13, D14, D15), які передаються в пристрій формування заявок. Використовуючи отриману інформацію, за наявності акторів W 2, W 3 і W 4 даний пристрій формує три заявки: Z2, Z3 і Z4. Якщо число вільних процесорів достатньо, то далі три завдання можуть виконуватися паралельно. Аналогічним чином процес триває до повного його завершення. Перевагами даного пристрою є розширення функціональних можливостей за рахунок реалізації завчасної реконфігурації обчислювальної структури, що побудована на базі ПШС, а також циклічних реконфігурованих обчислювальних процесів і обчислень в режимі потоку задач. Це, в загальному випадку, забезпечує підвищення ефективності пристрою, за рахунок суміщення обчислювального процесу і процесу реконфігурації обчислювальної структури на ШПС, що приводить до зменшення затримок виконання обчислень. Запропонований пристрій забезпечує підвищення обчислювальної ефективності реконфігурованих обчислювальних систем, побудованих на базі часткової динамічної реконфігурації ПЛІС, за рахунок скорочення часу затримки під час реконфігурації обчислювальної структури та обчислення інформації, та розширює функціональні можливості, а саме поєднує у часі процеси обчислення та реконфігурації обчислювальної структури на ШПС. Джерела інформації: 1. Жабин В.И. Организация вычислений в системах, управляемых потоком данных // Вісник Національного технічного університету України "Київський політехнічний інститут". Інформатика, управління та обчислювальна техніка. - 1998. - № 31. - С. 44-51 2. Жабин В.И. Реализация вычислений под управлением потока дескрипторов данных в мультипроцессорных системах // Электронное моделирование. - 2003. - Т. 25, № 1. - С. 35-47. 3. Деклараційний патент на винахід № 7727 України, МПК G06F 15/16, 15/76. Обчислювальний пристрій / Жуков I.A., Жабін В.І., Клименко I.A., Ткаченко В.В. - Опубл. 15.07,2005. Бюл. № 7. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 40 45 50 55 60 Обчислювальний пристрій для апаратного розпаралелення на рівні завдань, що містить п блоків обробки інформації, блок вводу даних, блок виводу даних, блок пам'яті заявок, блок реєстраційної пам'яті, регістр актора і регістр дескриптора, блок селектора умови, блок встановлення пріоритету, чергу із буферної пам'яті заявок та регістр буфера завдань, причому перший інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра актора, другий інформаційний вхід пристрою з'єднаний з першим інформаційним входом регістра дескриптора, перший інформаційний вихід якого зв'язаний з шиною адреси акторів, яка в свою чергу зв'язана з першим інформаційним виходом регістра актора та другим інформаційним входом блока встановлення пріоритету, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока селектора умови, який в свою чергу через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока реєстраційної пам'яті, який через перший інформаційний вхід зв'язаний із шиною адреси завдань, яка зв'язує другий інформаційний вихід регістра дескриптора та другий і третій інформаційні входи блока пам'яті заявок, який через перший інформаційний вхід зв'язаний із шиною адреси дескрипторів, яка зв'язує четвертий інформаційний вихід регістра актора та четвертий інформаційний вихід регістра дескриптора, також блок пам'яті заявок через перший інформаційний вихід зв'язаний із першим інформаційним входом регістра завдань, який через перший інформаційний вихід зв'язаний із другим інформаційним виходом пристрою, а перший управляючий вихід пристрою зв'язаний із першим управляючим виходом блока буферної пам'яті заявок, який через перший інформаційний вхід зв'язаний із першим інформаційним виходом блока встановлення пріоритету, який через третій інформаційний вхід зв'язаний із другим інформаційним виходом регістра актора, в якого третій інформаційний вихід через шину зв'язаний із третім 5 UA 121574 U 5 інформаційним виходом регістра дескриптора та із другим інформаційним входом блока селектора умови, який відрізняється тим, що додатково містить блок завчасної реконфігурації, який через перший інформаційний вхід зв'язаний із п'ятим інформаційним виходом регістра актора та перший інформаційний вихід якого з'єднаний із четвертим інформаційним входом блока встановлення пріоритету. 6 UA 121574 U Комп’ютерна верстка А. Крулевський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 7

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/16

Мітки: рівні, пристрій, завдань, апаратного, розпаралелення, обчислювальній

Код посилання

<a href="https://ua.patents.su/9-121574-obchislyuvalnijj-pristrijj-dlya-aparatnogo-rozparalelennya-na-rivni-zavdan.html" target="_blank" rel="follow" title="База патентів України">Обчислювальний пристрій для апаратного розпаралелення на рівні завдань</a>

Попередній патент: Імітатор теплового потоку

Наступний патент: Пристрій для відокремлення від шини бортових кілець

Випадковий патент: Головний повітряний тракт карбюратора з системою дифузорів