Обчислювальний пристрій непрямої стеганографії

Номер патенту: 92841

Опубліковано: 10.12.2010

Автори: Палагін Олександр Васильович, Алішов Надір Ісмаїл-огли

Формула / Реферат

1. Обчислювальний пристрій непрямої стеганографії, що складається із блока вводу-виводу, блока керування, мікропроцесора, блока керування пам'яттю, блока оперативного запам'ятовувального пристрою, блока постійного запам'ятовувального пристрою, блока генерування випадкових чисел, при цьому перший вхід-вихід блока вводу-виводу є входом-виходом пристрою, другий вхід та вихід - підключено до першого входу та виходу блока керування, другий вхід та вихід якого підключено до першого входу та виходу мікропроцесора, другий вхід-вихід якого підключено до першого входу-виходу блока керування пам'яттю, другий вхід-вихід якого підключено до входу-виходу блока оперативного запам'ятовувального пристрою, а третій вхід-вихід - підключено до входу-виходу блока постійного запам'ятовувального пристрою, який відрізняється тим, що додатково містить блок асоціативно-функціональної пам'яті, перший та другий вхід якого підключено до першого та другого виходу блока керування пам'яттю, перший вихід - підключено до першого входу блока керування пам'яттю, а третій вхід блока асоціативно-функціональної пам'яті підключено до виходу блока генерування випадкових чисел, вхід якого підключено до третього виходу блока керування.

2. Обчислювальний пристрій за п. 1, який відрізняється тим, що блок асоціативно-функціональної пам'яті містить регістр даних лівий, регістр даних правий, асоціативну пам'ять ліву, асоціативну пам'ять праву, регістр адрес лівий, регістр адрес правий, причому вхід регістра даних лівого є першим входом блока, вихід якого підключено до входу блока асоціативної пам'яті лівої, вхід-вихід якого підключено до входу-виходу регістра адрес лівого, вхід якого є другим входом блока, а вихід - підключено до входу регістра даних правого, вихід якого є виходом блока, а вхід-вихід - підключено до входу-виходу блока асоціативної пам'яті правої, вхід якого підключено до першого виходу регістра адрес правого, перший вхід якого є третім входом блока, а другий вхід - підключено до другого виходу регістра даних лівого.

Текст

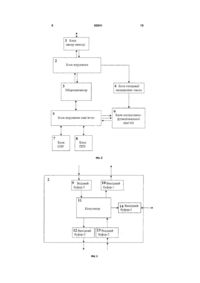

1. Обчислювальний пристрій непрямої стеганографії, що складається із блока вводу-виводу, блока керування, мікропроцесора, блока керування пам'яттю, блока оперативного запам'ятовувального пристрою, блока постійного запам'ятовувального пристрою, блока генерування випадкових чисел, при цьому перший вхід-вихід блока вводувиводу є входом-виходом пристрою, другий вхід та вихід - підключено до першого входу та виходу блока керування, другий вхід та вихід якого підключено до першого входу та виходу мікропроцесора, другий вхід-вихід якого підключено до першого входу-виходу блока керування пам'яттю, другий вхід-вихід якого підключено до входувиходу блока оперативного запам'ятовувального пристрою, а третій вхід-вихід - підключено до вхо C2 2 92841 1 3 підключено до другого входу-виходу мікропроцесора, третій вхід-вихід якого підключений до входу-виходу блока спеціалізованих обчислень. Загальними ознаками є наявність блока вводувиводу, блока керування, мікропроцесора, блока керування пам'яттю, блока постійного запам'ятовувального пристрою, блока оперативного запам'ятовувального пристрою, при цьому перший вхід-вихід блока вводу-виводу є входом-виходом пристрою, другий вхід та вихід підключено до першого входу та виходу блока керування, другий вхід та вихід якого підключено до першого входу та виходу мікропроцесора, другий вхід-вихід якого підключено до першого входу-виходу блока керування пам'яттю, другий вхід-вихід якого підключено до входу-виходу блока оперативного запам'ятовувального пристрою, а третій вхід-вихід підключено до входу-виходу блока постійного запам'ятовувального пристрою Причиною, що заважає досягненню поставленої мети є те, що пристрій не дозволяє забезпечити необхідний рівень захисту від несанкціонованого доступу, формувати шифри, що не розкриваються, файлів і документів. Найбільш близьким є устрій CodeShelter™(Компанія Software Security Lab, 2005, адреса в Інтернеті www.seculab.ru), який містить блок вводу-виводу, блок керування, мікропроцесор, блок симетричного шифрування, блок генерації випадкових чисел, блок керування пам'яттю, блок оперативного запам'ятовувального пристрою, блок постійного запам'ятовувального пристрою, при цьому перший вхід-вихід блока вводу-виводу є входом-виходом пристрою, другий вхід-вихід підключено до першого входу-виходу блоку керування, другий вхід-вихід якого підключений до першого входу-виходу мікропроцесора, четвертий вихід якого підключено до виходу генератора випадкових чисел, третій вихід підключено до виходу блока симетричного шифрування, а другий вхід-вихід підключено до першого входувиходу блока керування пам'яттю, другий вхідвихід якого підключений до входу-виходу блока оперативного запам'ятовувального пристрою, третій вхід-вихід підключено до входу-виходу блока постійного запам'ятовувального пристрою. Загальними ознаками є наявність блока вводувиводу, блока керування, мікропроцесора, блока керування пам'яттю, блока оперативного запам'ятовувального пристрою, блока постійного запам'ятовувального пристрою, блока генерації випадкових чисел, при цьому перший вхід-вихід блока вводу-виводу є входом-виходом пристрою, другий вхід-вихід підключено до першого входу-виходу блока керування, другий вхід-вихід якого підключено до першого входу-виходу мікропроцесора, другий вихід якого підключено до першого виходу блока керування пам’яттю, другий вхід-вихід якого підключений до входу-виходу блока оперативного запам'ятовувального пристрою, а третій вхід-вихід підключено до входу-виходу блоку постійного запам'ятовувального пристрою. Причиною, що заважає досягти технічного результату є те, що пристрій не дозволяє передавати файл будь-якої довжини, щоб при цьому накла 92841 4 дні витрати дорівнювали накладним витратам передачі не захищеного файлу, а довжина ключа не впливала на обчислювальну складність, що як наслідок не дозволяє забезпечити необхідний рівень захисту від несанкціонованого доступу, формувати шифри, що не розкриваються, файлів і документів. В основу винаходу покладено завдання створення такого обчислювального пристрою непрямої стеганографії, який при введенні нових блоків і зв'язків дозволив реалізувати необхідний рівень захисту від несанкціонованого доступу, формувати шифри, що не розкриваються, файлів і документів. Поставлене завдання досягається тим, що в пристрій, який містить блок вводу-виводу, блок керування, мікропроцесор, блок керування пам'яттю, блок оперативного запам'ятовувального пристрою, блок постійного запам'ятовувального пристрою, блок генерації випадкових чисел, при цьому перший вхід-вихід блока вводу-виводу є входом-виходом пристрою, другий вхід та вихід підключено до першого входу та виходу блока керування, другий вхід та вихід якого підключено до першого виходу та виходу мікропроцесора, вихід-вихід якого підключено до першого входувиходу блока керування пам'яттю, другий вхідвихід якого підключено до входу-виходу блока оперативного запам'ятовувального пристрою, а третій вхід-вихід підключено до входу-виходу блока постійного запам'ятовувального пристрою, додатково введений блок асоціативнофункціональної пам'яті, причому, перший та другий вхід підключено до першого та другого виходу блока керування пам'яттю, а перший вихід підключено до першого входу блока керування пам'яттю і третій вхід блока асоціативно-функціональної пам'яті підключено до виходу блокуй генерації випадкових чисел вхід якого підключено до третього виходу блока керування. Відмітними ознаками є наявність блока асоціативно-функціональної пам'яті, причому, перший та другий вхід підключено до першого та другого виходу блока керування пам'яттю, а перший вихід підключено до першого входу блока керування пам'яттю і третій вхід блока асоціативнофункціональної пам'яті підключено до виходу блока генерації випадкових чисел вхід якого підключено до третього виходу блока керування. Введення цього додаткового блока дозволило реалізувати необхідний рівень захисту від несанкціонованого доступу, формувати шифри, що не розкриваються, файлів і документів. На Фіг.1 представлена блок-схема прототипу. На Фіг.2 представлена блок-схема пропонованого пристрою. На Фіг.3 представлена блок-схема блока керування. На Фіг.4 представлена блок-схема блока керування пам'яттю. На Фіг.5 представлена блок-схема блока асоціативно-функціональної пам'яті. Запропонований обчислювальний пристрій непрямої стеганографії (Фіг.2) містить блок вводувиводу 1, блок керування 2, мікропроцесор 3, блок генерації випадкових чисел 4, блок керування па 5 м'яттю 5, блок асоціативно-функціональної пам'яті 6, блок оперативного запам'ятовувального пристрою 7 (ОЗУ), блок постійного запам'ятовувального пристрою 8 (ПЗУ), при цьому перший вхідвихід блока вводу-виводу 1 є входом-виходом пристрою, другий вхід та вихід підключено до першого входу та виходу блока керування 2, другий вхід та вихід якого підключено до першого входу та виходу мікропроцесора 3, а третій вихід підключено до входу блока генерації випадкових чисел 4, вихід якого підключено до третього входу блока асоціативно-функціональної пам'яті 6, перший та другий вхід якого підключено до першого та другого виходу блока керування пам'яттю 5, а перший вихід підключено до першого входу блока керування пам'яттю 5, перший вхід-вихід якого підключено до другого входу-виходу мікропроцесора 3, другий вхід-вихід підключено до входувиходу блока оперативного запам'ятовувального пристрою 7, третій вхід-вихід підключено до входувиходу постійного запам'ятовувального пристрою 8. Як мікропроцесор 3 може бути використаний процесор Pentium III (компанія Intel,www.intel.com), блок керування пам'яттю 5 реалізується на стандартному чипсеті Intel 840 (компанія Intel, www.intel.com). Блок керування 2 представлений на Фіг.3 і складається із двох вхідних буферів 9, 13, трьох вихідних буферів 10, 12, 14, комутатора 11, при чому вхід вхідного буфера-1 9 є першим входом блока керування, вихід якого підключено до першого входу комутатора 11, перший вихід якого підключено до входу вихідного буфера-1 10, вихід якого є першим виходом блоку керування, вхід вхідного буфера-2 13 є другим входом блока керування, вихід якого підключено до другого входу комутатора 11, другий вихід якого підключено до входу другого вихідного буфера-2 12, вихід якого є другим виходом блока керування, вихід третього вихідного буфера-3 14 є третім виходом блока керування, вхід якого підключено до третього виходу комутатора 11. Блок керування пам'яттю представлений на Фіг.4 і складається із шести регістрів 15, 17, 18, 19, 20, 21 та пристрою керування 16, при чому перший вхід-вихід регістра 15 є першим входом-виходом блока, а другий вхід-вихід підключено до першого входу-виходу пристрою керування 16, другий вхідвихід якого підключено до першого входу-виходу регістра 17, другий вхід-вихід якого є другим входом-виходом блока, третій вхід-вихід пристрою керування 16 підключено до першого входу-виходу регістра 18, другий вхід-вихід якого є третім входом-виходом блока, перший вихід пристрою керування 16 підключено до входу регістра 19, вихід якого є першим виходом блока, другий вихід пристрою керування 16 підключено до входу регістра 20 вихід якого є другим виходом блока, перший вхід пристрою керування 16 підключено до виходу регістра 21 вхід якого є другим входом блока. Блок асоціативно-функціональної пам'яті представлений на Фіг.5 і складається із регістра адрес лівий 22, регістра адрес правий 23, асоціативної пам'яті лівої 24, асоціативної пам'яті правої 92841 6 25, регістра даних лівий 26, регістра даних правий 27, при чому вхід регістра даних лівий 22 є першим входом блока, вхід-вихід якого підключено до входу-виходу блока асоціативна пам'ять ліва 24, вхід якого підключено до виходу регістра даних лівий 26, вхід якого є другим входом блока, а другий вихід підключено до входу регістра адрес правий 23, вхід якого є другим входом блока, а вихід підключено до входу блока асоціативна пам'ять права 25, вхід-вихід якого підключено до входувиходу регістра даних правий 27, перший вихід якого є виходом блоку, а вхід підключено до виходу регістра адрес лівий 22. Пристрій функціонує наступним чином. На першому етапі роботи пристрою, що називається Початкове налаштування, по команді із блока керування 2 включається робота блока генерації випадкових чисел 4: що генерує двійкові послідовності байтів. Вихідні послідовності байтів надходять до блока асоціативно-функціональної пам'яті 6 у регістр даних лівий 26. Адреси записуваних байтів для блока асоціативна пам'ять ліва 24 формуються блоком керування пам'яттю 5. Ці адреси одночасно передаються в регістр даних правий 27, а вміст регістра даних лівий 26 передається, як адреси, для блока асоціативна пам'ять права 25, у регістр адрес правий 23. При цьому коректність формування, як адресної частини, так і даних для блока асоціативна пам'ять ліва 24 і блока асоціативна пам'ять права 25 контролюється блоком керування пам'яттю 5 керованого від мікропроцесора 3. Початкова установка завершується після формування відповідних масивів даних в блоці асоціативна пам'ять ліва 24 та блоці асоціативна пам'ять права 25. Після завершення цього етапу пристрій вважається готовим до роботи й може проводити шифрування й дешифрування даних. Під час етапу шифрування, масив даних що підлягають шифруванню надходять від блока вводу-виводу 1 через блок керування 2 та мікропроцесор 3, за допомогою блока керування пам'яттю 5 у блок ОЗУ 7 окремими порціями. Далі записана в ОЗУ 7 порція інформації побайтно передається в блок асоціативно-функціональної пам'яті 6 через блок керування пам'яттю 5 та регістр адрес правий 23 у блок асоціативна пам'ять права 25, як адресна інформація. У регістрі даних правий 27 блока асоціативно-функціональної пам'яті 6 формується байт, що є вмістом елемента блока асоціативна пам'ять права 25 розміщеним за адресою записаною в регістр адрес правий 23. Цей байт заміщає відповідний байт в ОЗУ 7. Цей процес повторюється поки у вихідному масиві, що шифрується, не буде повністю заміщені всі байти з блока асоціативна пам'ять права 25. Шифрований файл через блок вводу-виводу 1 передається в головний комп'ютер. При дешифруванні, масив даних, що підлягає дешифруванню, через блок вводу-виводу 1 записується порціями через блок керування 2 та мікропроцесор 3, за допомогою блока керування пам'яттю 5 у блок ОЗУ 7. Далі записана в ОЗУ 7 порція інформації побайтно передається через блок керування пам'яттю 5 у блок асоціативнофункціональної пам'яті 6 за допомогою регістра 7 адрес лівий 22 до асоціативної пам'яті лівої 24 в якості адресної інформації. У регістрі даних лівий 26 формується байт, що є вмістом елемента за адресою, записаному в регістрі адрес лівий 22. Цей процес повторюється поки у вихідному дешифрованому масиві не буде повністю заміщені всі байти з блока асоціативна пам'ять ліва 24. Деши 92841 8 фрований файл через блок вводу-виводу 1 передається в головний комп'ютер. Обчислювальний пристрій непрямої стеганографії, як виходить з опису, може бути реалізований промисловим чином, тому що складові блоки можуть бути побудовані на основі елементної бази широкого застосування. 9 92841 10 11 Комп’ютерна верстка М. Ломалова 92841 Підписне 12 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюIndirect steganography computing unit

Автори англійськоюAlishov Nadir Ismail-ogly, Palahin Oleksandr Vasyliovych

Назва патенту російськоюВычислительное устройство непрямой стеганографии

Автори російськоюАлишов Надир Исмаил-оглы, Палагин Александр Васильевич

МПК / Мітки

МПК: G09C 1/06, G06F 12/14

Мітки: стеганографії, пристрій, непрямо, обчислювальній

Код посилання

<a href="https://ua.patents.su/6-92841-obchislyuvalnijj-pristrijj-nepryamo-steganografi.html" target="_blank" rel="follow" title="База патентів України">Обчислювальний пристрій непрямої стеганографії</a>

Попередній патент: Полімерна композиція

Наступний патент: Спосіб одержання замороженої молочно-білкової маси

Випадковий патент: Диспергатор-змішувач