Пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи

Номер патенту: 13188

Опубліковано: 15.03.2006

Автори: Осіпов Валерій Анатолійович, Пузько Ігор Данилович, Неня Віктор Григорович

Формула / Реферат

Пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи, що містить вимірювальний перетворювач швидкості, установлений на випробуваному об'єкті, два ключі, два регістри, генератор імпульсів, інтегратор, два знакочутливих елементи, елемент І, два елементи диференціювання, чотири діоди, два інвертори, два тригери, два лічильники імпульсів, два цифро-аналогових перетворювачі, елемент затримки, перший блок ділення, два блоки множення, вихід вимірювального перетворювача швидкості з'єднаний з об'єднаними входами першого знакочутливого елемента і інтегратора, вихід якого з'єднаний з входом другого знакочутливого елемента, вихід якого з'єднаний з другим входом елемента І, перший вхід якого з'єднаний з виходом першого знакочутливого елемента, вихід елемента І з'єднаний з входом першого елемента диференціювання, вихід якого через перший діод в прямому напрямку з'єднаний з S-входом першого тригера, R-вхід якого з'єднаний з виходом першого інвертора, вхід якого через третій діод в зворотному напрямку з'єднаний з виходом першого елемента диференціювання, вихід другого знакочутливого елемента з'єднаний з входом другого елемента диференціювання, вихід якого через другий діод в прямому напрямку з'єднаний з S-входом другого тригера, R-вхід якого з'єднаний з виходом другого інвертора, вхід якого через четвертий діод в зворотному напрямку з'єднаний з виходом другого елемента диференціювання, вихід другого інвертора з'єднаний з об'єднаними входами першого елемента затримки і входами Прийом першого і другого регістрів, вихід першого елемента затримки з'єднаний з об'єднаними установочними входами першого і другого лічильників імпульсів, лічильні входи яких з'єднані з виходами першого і другого ключів, відповідно, інформаційні входи яких об'єднані і з'єднані з виходом генератора імпульсів, а керувальні входи першого і другого ключів з'єднані з прямими виходами першого і другого тригерів, відповідно, прямі виходи розрядів першого і другого лічильників імпульсів з'єднані з входами відповідних розрядів першого і другого регістрів, відповідно, прямі виходи розрядів яких з'єднані з входами розрядів першого і другого цифро-аналогових перетворювачів, відповідно, причому вихід першого блока ділення з'єднаний з першим входом першого блока множення, джерело напруги величиною p, який відрізняється тим, що пристрій додатково містить два комутатори, першу і другу групи із N блоків пам'яті з першого по N-й кожна, де N - число циклів вимірювання, другий блок ділення, групу із N блоків ділення з першого по N-й, першу, другу, третю, четверту і п'яту групи із N блоків множення з першого по N-й кожна, групу із N перетворювачів синуса з першого по N-й, групу із N перетворювачів котангенса з першого по N-й, чотири N-входові суматори, дешифратор, N-входовий елемент І, формувач імпульсів, третій лічильник імпульсів, реєстратор, другий і третій елементи затримки, причому виходи першого і другого цифро-аналогових перетворювачів з'єднані з входами першого і другого комутаторів, відповідно, виходи з першого по N-й першого комутатора з'єднані з інформаційними входами відповідних блоків пам'яті з першого по N-й першої групи із N блоків пам'яті, виходи яких з'єднані з входами Ділене відповідних блоків ділення з першого по N-й групи із N блоків ділення, виходи з першого по N-й другого комутатора з'єднані з інформаційними входами відповідних блоків пам'яті з першого по N-й другої групи із N блоків пам'яті, виходи яких з'єднані з входами Подільник відповідних блоків ділення з першого по N-й групи із N блоків ділення, виходи яких з'єднані з першими входами відповідних блоків множення з першого по N-й першої групи із N блоків множення, другі входи яких об'єднані і з'єднані з виходом джерела напруги величиною p, виходи блоків множення з першого по N-й першої групи із N блоків множення з'єднані з входами відповідних перетворювачів синуса з першого по N-й групи із N перетворювачів синуса, виходи яких з'єднані з першими входами відповідних блоків множення з першого по N-й другої групи із N блоків множення, другі входи яких з'єднані з виходами відповідних блоків пам'яті з першого по N-й другої групи із N блоків пам'яті, виходи блоків множення з першого по N-й другої групи із N блоків множення з'єднані з входами першого N-входового суматора, вихід якого з'єднаний з входом Ділене першого блока ділення, вхід Подільник якого з'єднаний з виходом другого N-входового суматора, входи якого з'єднані з виходами відповідних блоків множення з першого по N-й четвертої групи із N блоків множення, входи яких поблочно об'єднані і з'єднані з виходами відповідних блоків множення з першого по N-й другої групи із N блоків множення, другий вхід першого блока множення з'єднаний з виходом джерела напруги величиною p, а вихід - з першим інформаційним входом ![]() реєстратора, другий інформаційний вхід

реєстратора, другий інформаційний вхід ![]() якого з'єднаний з виходом другого блока множення, перший вхід якого з'єднаний з виходом другого блока ділення, а другий вхід - з виходом джерела напруги величиною p, вхід Ділене другого блока ділення з'єднаний з виходом третього N-входового суматора, входи якого з'єднані з виходами блоків множення з першого по N-й третьої групи із N блоків множення, перші входи яких з'єднані з виходами відповідних перетворювачів котангенса з першого по N-й групи із N блоків перетворювачів котангенса, входи яких з'єднані з виходами відповідних блоків множення з першого по N-й першої групи із N блоків множення, другі входи блоків множення з першого по N-й третьої групи із N блоків множення з'єднані з виходами відповідних блоків пам'яті з першого по N-й другої групи із N блоків пам'яті, вихід другого інвертора через другий елемент затримки з'єднаний з лічильним входом третього лічильника імпульсів, прямі виходи розрядів якого з'єднані з входами дешифратора, виходи якого з першого по N-й з'єднані з відповідними керувальними входами з першого по N-й першого і другого комутаторів, з входами Запис блоків пам'яті з першого по N-й, відповідно, першої групи із N блоків пам'яті, з входами Запис блоків пам'яті з першого по N-й, відповідно, другої групи із N блоків пам'яті, входи Читання блоків пам'яті з першого по N-й першої групи із N блоків пам'яті і блоків пам'яті з першого по N-й другої групи із N блоків пам'яті об'єднані і з'єднані з виходами формувача імпульсів, вхід якого з'єднаний з виходом N-входового елемента І, входи якого з'єднані з прямими виходами розрядів третього лічильника імпульсів, вихід другого елемента затримки через третій елемент затримки з'єднаний з об'єднаними входами Скид першого і другого регістрів.

якого з'єднаний з виходом другого блока множення, перший вхід якого з'єднаний з виходом другого блока ділення, а другий вхід - з виходом джерела напруги величиною p, вхід Ділене другого блока ділення з'єднаний з виходом третього N-входового суматора, входи якого з'єднані з виходами блоків множення з першого по N-й третьої групи із N блоків множення, перші входи яких з'єднані з виходами відповідних перетворювачів котангенса з першого по N-й групи із N блоків перетворювачів котангенса, входи яких з'єднані з виходами відповідних блоків множення з першого по N-й першої групи із N блоків множення, другі входи блоків множення з першого по N-й третьої групи із N блоків множення з'єднані з виходами відповідних блоків пам'яті з першого по N-й другої групи із N блоків пам'яті, вихід другого інвертора через другий елемент затримки з'єднаний з лічильним входом третього лічильника імпульсів, прямі виходи розрядів якого з'єднані з входами дешифратора, виходи якого з першого по N-й з'єднані з відповідними керувальними входами з першого по N-й першого і другого комутаторів, з входами Запис блоків пам'яті з першого по N-й, відповідно, першої групи із N блоків пам'яті, з входами Запис блоків пам'яті з першого по N-й, відповідно, другої групи із N блоків пам'яті, входи Читання блоків пам'яті з першого по N-й першої групи із N блоків пам'яті і блоків пам'яті з першого по N-й другої групи із N блоків пам'яті об'єднані і з'єднані з виходами формувача імпульсів, вхід якого з'єднаний з виходом N-входового елемента І, входи якого з'єднані з прямими виходами розрядів третього лічильника імпульсів, вихід другого елемента затримки через третій елемент затримки з'єднаний з об'єднаними входами Скид першого і другого регістрів.

Текст

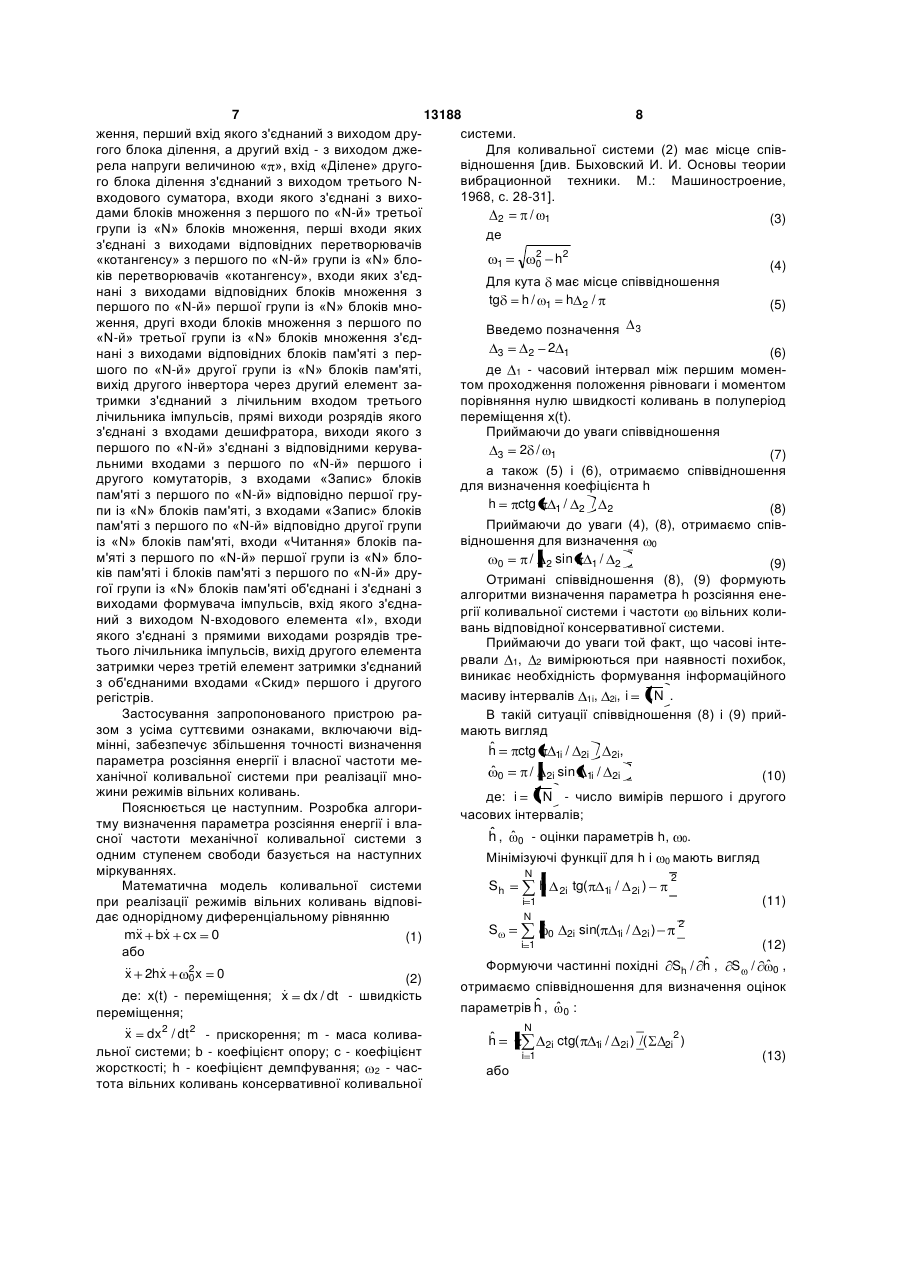

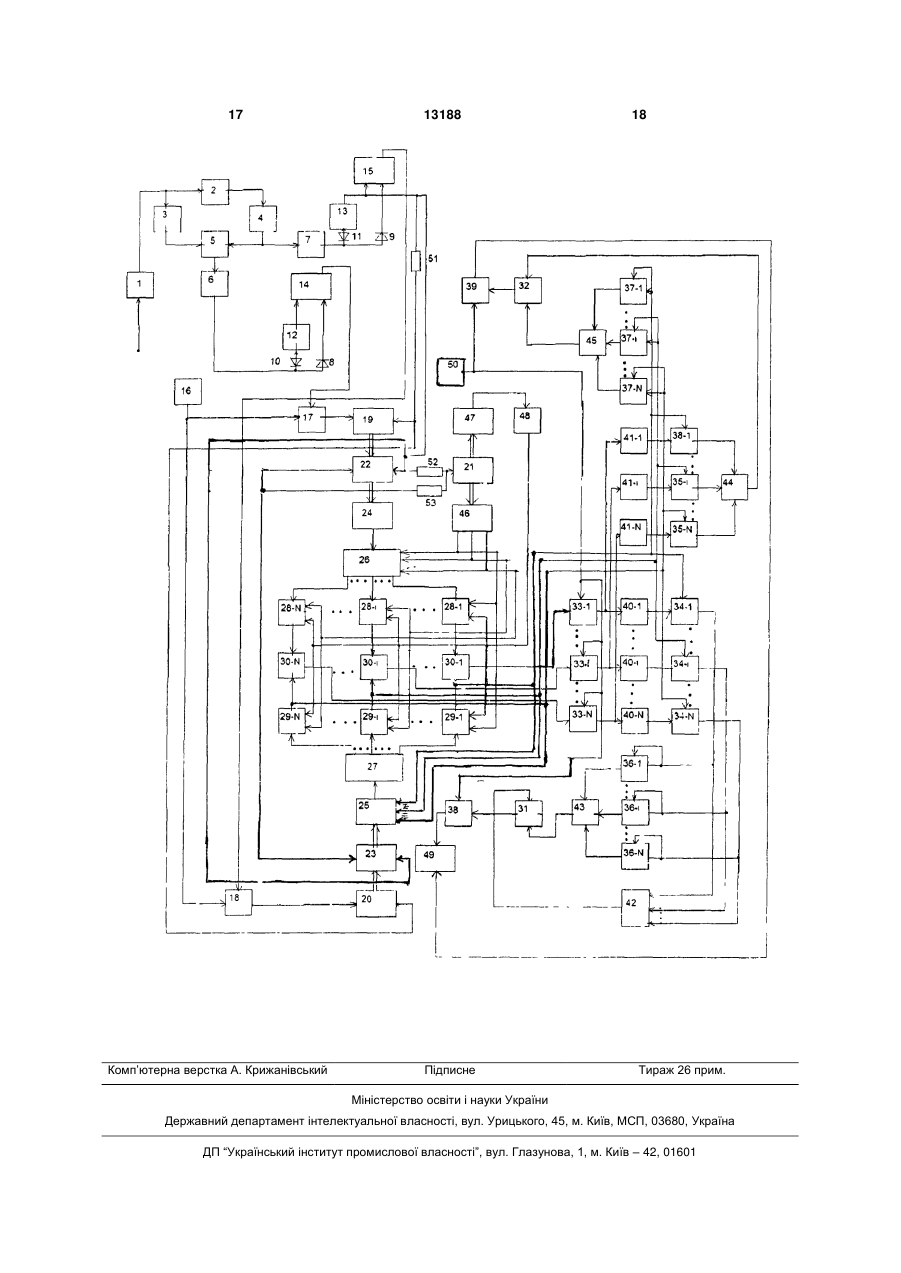

Пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи, що містить вимірювальний перетворювач швидкості, установлений на випробуваному об'єкті, два ключі, два регістри, генератор імпульсів, інтегратор, два знакочутливих елементи, елемент І, два елементи диференціювання, чотири діоди, два інвертори, два тригери, два лічильники імпульсів, два цифро-аналогових перетворювачі, елемент затримки, перший блок ділення, два блоки множення, вихід вимірювального перетворювача швидкості з'єднаний з об'єднаними входами першого знакочутливого елемента і інтегратора, вихід якого з'єднаний з входом другого знакочутливого елемента, вихід якого з'єднаний з другим входом елемента І, перший вхід якого з'єднаний з виходом першого знакочутливого елемента, вихід елемента І з'єднаний з входом першого елемента диференціювання, вихід якого через перший діод в прямому напрямку з'єднаний з S-входом першого тригера, R-вхід якого з'єднаний з виходом першого інвертора, вхід якого через третій діод в зворотному напрямку з'єднаний з виходом першого елемента диференціювання, вихід другого знакочутливого елемента з'єднаний з входом другого елемента диференціювання, вихід якого через другий діод в прямому напрямку з'єднаний з S-входом другого тригера, R-вхід якого з'єднаний з виходом другого інвертора, вхід якого через четвертий діод в зворотному напрямку з'єднаний з виходом другого елемента диференціювання, вихід другого інвертора з'єднаний з об'єднаними входами першого елемента затримки і входами Прийом першого і другого регістрів, вихід першого елемента затримки з'єднаний з об'єднаними установочними входами першого і другого лічильників імпульсів, лічильні входи яких з'єднані з виходами першого і другого ключів, відповідно, інформаційні входи яких об'єднані і з'єднані з виходом генератора імпульсів, а керувальні входи першого і другого клю 2 (19) 1 3 13188 4 групи із N блоків пам'яті, виходи блоків множення з виходами відповідних блоків множення з першого першого по N-й другої групи із N блоків множення по N-й першої групи із N блоків множення, другі з'єднані з входами першого N-входового суматора, входи блоків множення з першого по N-й третьої вихід якого з'єднаний з входом Ділене першого групи із N блоків множення з'єднані з виходами блока ділення, вхід Подільник якого з'єднаний з відповідних блоків пам'яті з першого по N-й другої виходом другого N-входового суматора, входи групи із N блоків пам'яті, вихід другого інвертора якого з'єднані з виходами відповідних блоків мночерез другий елемент затримки з'єднаний з лічиження з першого по N-й четвертої групи із N блоків льним входом третього лічильника імпульсів, прямноження, входи яких поблочно об'єднані і з'єднамі виходи розрядів якого з'єднані з входами дені з виходами відповідних блоків множення з першифратора, виходи якого з першого по N-й шого по N-й другої групи із N блоків множення, з'єднані з відповідними керувальними входами з другий вхід першого блока множення з'єднаний з першого по N-й першого і другого комутаторів, з входами Запис блоків пам'яті з першого по N-й, виходом джерела напруги величиною , а вихід - з відповідно, першої групи із N блоків пам'яті, з вхоˆ0 першим інформаційним входом Регістрація дами Запис блоків пам'яті з першого по N-й, відпореєстратора, другий інформаційний вхід відно, другої групи із N блоків пам'яті, входи Чиˆ Регістрація h якого з'єднаний з виходом другого тання блоків пам'яті з першого по N-й першої групи із N блоків пам'яті і блоків пам'яті з першого по N-й блока множення, перший вхід якого з'єднаний з другої групи із N блоків пам'яті об'єднані і з'єднані виходом другого блока ділення, а другий вхід - з з виходами формувача імпульсів, вхід якого з'єдвиходом джерела напруги величиною , вхід Діленаний з виходом N-входового елемента І, входи не другого блока ділення з'єднаний з виходом треякого з'єднані з прямими виходами розрядів третього N-входового суматора, входи якого з'єднані з тього лічильника імпульсів, вихід другого елемента виходами блоків множення з першого по N-й трезатримки через третій елемент затримки з'єднаний тьої групи із N блоків множення, перші входи яких з об'єднаними входами Скид першого і другого з'єднані з виходами відповідних перетворювачів регістрів. котангенса з першого по N-й групи із N блоків перетворювачів котангенса, входи яких з'єднані з Корисна модель відноситься до галузі випробувальної техніки і може бути застосована в машинобудуванні, авіаційній і космічній техніці. Відомийпристрій для вібровипробувань, що містить вимірювальний перетворювач швидкості, установлений на випробуваному об'єкті, два ключі, два регістра і генератор імпульсів [див. ав. св. СРСР №1352321, МПК G01М7/00, 1987]. Недолік відомого пристрою - недостатня точність визначення параметра розсіяння енергії і власної частоти механічної коливальної системи, що пояснюється похибками виміру, фіксації та запам'ятовування. За найближчий аналог вибрано пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи, що містить віброперетворювач, установлений на випробуваному об'єкті, два ключі, два регістра, генератор сигналів, інтегратор, два знакочутливих елемента, елемент «І», два елемента диференціювання, чотири діода, два інвертора, два тригера, два лічильника імпульсів, два цифро-аналогових перетворювачі, елемент затримки, блок ділення, три блока множення, два перетворювачі, в ролі генератора сигналів виступає генератор імпульсів, а віброперетворювач являє собою перетворювач швидкості, вихід якого з'єднаний з входами першого знакочутливого елемента і інтегратора, вихід якого з'єднаний з входом другого знакочутливого елемента, вихід якого з'єднаний з першим входом елемента «І», другий вхід якого з'єднаний з виходом першого знакочутливого елемента, вихід елемента «І» з'єднаний з входом першого елемента диференціювання, вихід якого через перший діод в прямому напрямку з'єднаний з S-входом першого тригера, R-вхід якого з'єднаний з виходом першого інвертора, вихід другого знакочутливого елемента з'єднаний з входом другого елемента диференціювання , вихід якого через другий діод в прямому напрямку з'єднаний з S-входом другого тригера, R-вхід якого з'єднаний з виходом другого інвертора, вихід першого елемента диференціювання через третій діод в зворотному напрямку з'єднаний з входом першого інвертора, вихід другого елемента диференціювання через четвертий діод в зворотному напрямку з'єднаний з входом другого інвертора, вихід якого з'єднаний з входом елемента затримки і керувальними входами першого і другого регістрів, вихід елемента затримки з'єднаний з установочними входами першого і другого лічильників імпульсів, лічильні входи яких з'єднані з виходами першого і другого ключів, відповідно, входи яких об'єднані і з'єднані з виходом генератора імпульсів, а керувальні входи - з прямими виходами першого і другого тригерів, відповідно, виходи розрядів першого і другого лічильників імпульсів з'єднані з входами відповідних розрядів першого і другого регістрів, відповідно, виходи розрядів яких з'єднані з входами розрядів першого і другого цифро-аналогових перетворювачів, відповідно, вихід першого цифро-аналового перетворювача з'єднаний з першим входом першого блока множення, вихід якого з'єднаний з входами першого і другого перетворювачів, вихід другого цифро-аналового перетворювача з'єднаний з входом «Подільник» блока ділення, вхід «Ділене» якого з'єднаний з виходом джерела напруги величиною « », а вихід з'єднаний з другим входом 5 13188 6 першого блока множення, виходи першого і другочів з'єднані з прямими виходами першого і другого го перетворювачів з'єднані з другими входами друтригерів, відповідно, прямі виходи розрядів першогого і третього блоків множення, відповідно, вихого і другого лічильників імпульсів з'єднані з входади яких з'єднані з першим і другим виходами ми відповідних розрядів першого і другого регістпристрою, відповідно [див. ав. св. СРСР рів, відповідно, прямі виходи розрядів яких з'єднані №1583778, МПК G01M7/00, 1990]. з входами розрядів першого і другого цифроНедоліком відомого пристрою є недостатня аналогових перетворювачів, відповідно, причому точність визначення параметра розсіяння енергії і вихід першого блока ділення з'єднаний з першим власної частоти механічної коливальної системи, входом першого блока множення, джерело напрущо пояснюється похибками виміру, фіксації та ги величиною « », згідно з корисною моделлю, запам'ятовування значень часових інтервалів, а пристрій додатково містить два комутатори, першу також недостатнім по множині інформаційним маі другу групи із «N» блоків пам'яті з першого по «Nсивом даних для зменшення похибок шляхом усей» кожна, де N - число циклів вимірювання, другий реднення. блок ділення, групу із «N» блоків ділення з першоВ основу запропонованої корисної моделі посго по «N-й», першу, другу, третю, четверту і п'яту тавлене завдання підвищення точності шляхом групи із «N» блоків множення з першого по «N-й» удосконалення пристрою за рахунок введення до кожна, групу із «N» перетворювачів «синусу» з його складу додаткових елементів, блоків і функпершого по «N-й», групу із «N» перетворювачів ціональних зв'язків, введення яких забезпечує фо«котангенсу» з першого по «N-й», чотири Nрмування нового алгоритму, який заснований на входові суматори, дешифратор, N-входовий еленових аналітичних співвідношеннях, що базується мент «І», формувач імпульсів, третій лічильник на розширенні масиву інформаційних даних і фоімпульсів, реєстратор, другий і третій елементи рмування регресійних залежностей для зменшензатримки, причому виходи першого і другого цифня похибок вимірювання. ро-аналогових перетворювачів з'єднані з входами Поставлене завдання вирішується тим, що у першого і другого комутаторів, відповідно, виходи відомому пристрої для визначення параметра розз першого по «N-й» першого комутатора з'єднані з сіяння енергії і власної частоти механічної коливаінформаційними входами відповідних блоків пальної системи, що містить вимірювальний перетм'яті з першого по «N-й» першої групи із «N» бловорювач швидкості, установлений на ків пам'яті, виходи яких з'єднані з входами «Ділевипробуваному об'єкті, два ключі, два регістри, не» відповідних блоків ділення з першого по «N-й» генератор імпульсів, інтегратор, два знакочутлигрупи із «N» блоків ділення, виходи з першого по вих елементи, елемент «І», два елементи дифе«N-й» другого комутатора з'єднані з інформаційренціювання, чотири діоди, два інвертори, два ними входами відповідних блоків пам'яті з першого тригери, два лічильники імпульсів, два цифропо «N-й» другої групи із «N» блоків пам'яті, виходи аналогових перетворювачі, елемент затримки, яких з'єднані з входами «Подільник» відповідних перший блок ділення, два блоки множення, вихід блоків ділення з першого по «N-й» групи із «N» вимірювального перетворювача швидкості з'єднаблоків ділення, виходи яких з'єднані з першими ний з об'єднаними входами першого знакочутливходами відповідних блоків множення з першого вого елемента і інтегратора, вихід якого з'єднаний по «N-й» першої групи із «N» блоків множення, з входом другого знакочутливого елемента, вихід другі входи яких об'єднані і з'єднані з виходом якого з'єднаний з другим входом елемента «І», джерела напруги величиною « », виходи блоків перший вхід якого з'єднаний з виходом першого множення з першого по «N-й» першої групи із «N» знакочутливого елемента, вихід елемента «І» блоків множення з'єднані з входами відповідних з'єднаний з входом першого елемента диференперетворювачів «синусу» з першого по «N-й» груціювання, вихід якого через перший діод в прямопи із «N» перетворювачів «синусу», виходи яких му напрямку з'єднаний з S-входом першого тригез'єднані з першими входами відповідних блоків ра, R-вхід якого з'єднаний з виходом першого множення з першого по «N-й» другої групи із «N» інвертора, вхід якого через третій діод в зворотноблоків множення, другі входи яких з'єднані з вихому напрямку з'єднаний з виходом першого елемедами відповідних блоків пам'яті з першого по «Nнта диференціювання, вихід другого знакочутливой» другої групи із «N» блоків пам'яті, виходи блоків го елемента з'єднаний з входом другого елемента множення з першого по «N-й» другої групи із «N» диференціювання, вихід якого через другий діод в блоків множення з'єднані з входами першого Nпрямому напрямку з'єднаний з S-входом другого входового суматора, вихід якого з'єднаний з вхотригера, R-вхід якого з'єднаний з виходом другого дом «Ділене» першого блока ділення, вхід «Подіінвертора, вхід якого через четвертий діод в звольник» якого з'єднаний з виходом другого Nротному напрямку з'єднаний з виходом другого входового суматора, входи якого з'єднані з вихоелемента диференціювання, вихід другого інвердами відповідних блоків множення з першого по тора з'єднаний з об'єднаними входами першого «N-й» четвертої групи із «N» блоків множення, елемента затримки і входами «Прийом» першого і входи яких поблочно об'єднані і з'єднані з виходадругого регістрів, вихід першого елемента затримми відповідних блоків множення з першого по «Nки з'єднаний з об'єднаними установочними входай» другої групи із «N» блоків множення, другий ми першого і другого лічильників імпульсів, лічивхід першого блока множення з'єднаний з виходом льні входи яких з'єднані з виходами першого і джерела напруги величиною « », а вихід - з пердругого ключів, відповідно, інформаційні входи шим інформаційним входом «Реєстрація 0» реяких об'єднані і з'єднані з виходом генератора імєстратора, другий інформаційний вхід «Реєстрація пульсів, а керувальні входи першого і другого клюh» якого з'єднаний з виходом другого блока мно 7 13188 8 ження, перший вхід якого з'єднаний з виходом друсистеми. гого блока ділення, а другий вхід - з виходом джеДля коливальної системи (2) має місце співвідношення [див. Быховский И. И. Основы теории рела напруги величиною « », вхід «Ділене» друговибрационной техники. M.: Машиностроение, го блока ділення з'єднаний з виходом третього N1968, с. 28-31]. входового суматора, входи якого з'єднані з виходами блоків множення з першого по «N-й» третьої / 1 2 (3) групи із «N» блоків множення, перші входи яких де з'єднані з виходами відповідних перетворювачів 2 2 «котангенсу» з першого по «N-й» групи із «N» бло1 0 h (4) ків перетворювачів «котангенсу», входи яких з'єдДля кута має місце співвідношення нані з виходами відповідних блоків множення з tg h/ 1 h 2 / (5) першого по «N-й» першої групи із «N» блоків множення, другі входи блоків множення з першого по 3 Введемо позначення «N-й» третьої групи із «N» блоків множення з'єд3 2 2 1 (6) нані з виходами відповідних блоків пам'яті з перде 1 - часовий інтервал між першим моменшого по «N-й» другої групи із «N» блоків пам'яті, том проходження положення рівноваги і моментом вихід другого інвертора через другий елемент запорівняння нулю швидкості коливань в полуперіод тримки з'єднаний з лічильним входом третього лічильника імпульсів, прямі виходи розрядів якого переміщення х(t). Приймаючи до уваги співвідношення з'єднані з входами дешифратора, виходи якого з першого по «N-й» з'єднані з відповідними керува2 / 1 3 (7) льними входами з першого по «N-й» першого і а також (5) і (6), отримаємо співвідношення другого комутаторів, з входами «Запис» блоків для визначення коефіцієнта h пам'яті з першого по «N-й» відповідно першої груh ctg 1 / 2 / 2 (8) пи із «N» блоків пам'яті, з входами «Запис» блоків Приймаючи до уваги (4), (8), отримаємо співпам'яті з першого по «N-й» відповідно другої групи відношення для визначення 0 із «N» блоків пам'яті, входи «Читання» блоків пам'яті з першого по «N-й» першої групи із «N» бло/ 2 sin 1 / 2 0 (9) ків пам'яті і блоків пам'яті з першого по «N-й» друОтримані співвідношення (8), (9) формують гої групи із «N» блоків пам'яті об'єднані і з'єднані з алгоритми визначення параметра h розсіяння еневиходами формувача імпульсів, вхід якого з'єднаргії коливальної системи і частоти 0 вільних колиний з виходом N-входового елемента «І», входи вань відповідної консервативної системи. якого з'єднані з прямими виходами розрядів треПриймаючи до уваги той факт, що часові інтетього лічильника імпульсів, вихід другого елемента рвали 1, 2 вимірюються при наявності похибок, затримки через третій елемент затримки з'єднаний виникає необхідність формування інформаційного з об'єднаними входами «Скид» першого і другого масиву інтервалів 1i, 2i, i 1, N . регістрів. Застосування запропонованого пристрою раВ такій ситуації співвідношення (8) і (9) прийзом з усіма суттєвими ознаками, включаючи відмають вигляд мінні, забезпечує збільшення точності визначення ˆ h ctg 1i / 2i / 2i, параметра розсіяння енергії і власної частоти меˆ0 / 2i sin 1i / 2i (10) ханічної коливальної системи при реалізації множини режимів вільних коливань. Пояснюється це наступним. Розробка алгоритму визначення параметра розсіяння енергії і власної частоти механічної коливальної системи з одним ступенем свободи базується на наступних міркуваннях. Математична модель коливальної системи при реалізації режимів вільних коливань відповідає однорідному диференціальному рівнянню m bx cx 0 x (1) або 2 2hx x 0x 0 (2) де: x(t) - переміщення; x dx / dt - швидкість переміщення; dx 2 / dt 2 - прискорення; m - маса коливаx льної системи; b - коефіцієнт опору; с - коефіцієнт жорсткості; h - коефіцієнт демпфування; 2 - частота вільних коливань консервативної коливальної де: i 1, N - число вимірів першого і другого часових інтервалів; ˆ h , ˆ - оцінки параметрів h, 0. 0 Мінімізуючі функції для h і N Sh i 1 N ˆ h 2i tg( ˆ0 2i 2i S ctg( 1i sin( / 2i ) 1i / 0 мають вигляд 2 (11) 2 2i ) (12) ˆ, S / ˆ , Формуючи частинні похідні Sh / h 0 отримаємо співвідношення для визначення оцінок ˆ параметрів h , ˆ 0 : i 1 ˆ h N i 1 або 1i / 2i ) /( 2 2i ) (13) 9 ˆ h ˆ0 13188 N [ N 2i tg( 1i / 2 2i )] /[ i 1 N 2i tg2 ( 1i / 2i )] (14) i 1 IV [ 2i sin( 1i / 2 2i )] /[ i 1 2i 2 sin ( 1i / 2i )] i 1 Число «і» вимірів першого 1і і другого 2і часових інтервалів визначається або числом N1 зафіксованих полуперіодів в одній реалізацій' при одному значенні начальних умов або числом N2 зафіксованих значень одного полуперіоду при N2 значеннях начальних умов. Таким чином, для визначення оцінки параметˆ розсіяння енергії і власної частоти (частоти ра h вільних коливань) ˆ 0 механічної коливальної системи на підставі (13), (15) отримаємо алгоритм роботи пристрою: 1) реалізувати режим (режими) вільних коливань дисипативної коливальної системи з одним ступенем вільності; 2) провести фіксацію і запам'ятовування «N» полуперіодів вільних коливань коливальної системи, що відповідає фіксації і запам'ятовуванню інформаційного масиву із «N» других часових інтервалів 2і; 3) провести фіксацію і запам'ятовування інформаційного масиву із «N» перших часових інтервалів 1і між моментами часу нульових значень переміщення і швидкості; 4) сформувати сигнали, що відповідають співвідношенням N ˆ h ˆ0 N 2i ctg( 1i / 2i ) i 1 N [ 2i ), i 1 N 2i i 1 2 /( sin( 1i / 2i )] /[ 2 2i sin2 ( 1i / 10 2i )] i 1 . Застосування запропонованого алгоритму визначення параметра h розсіяння енергії і власної частоти 0 механічної коливальної системи, а саме, фіксація і запам'ятовування множини першого і другого часових інтервалів, перший з яких дорівнює часовому інтервалу між нульовими значеннями переміщення і швидкості, а другий - інтервалу між сусідніми значеннями переміщення дозволяє шляхом формування регресійних залежностей ˆ зменшити похибку при визначенні оцінок h і ˆ 0 . Новим в алгоритмі є формування двох регресійних залежностей h=f1( 1, 2), 0 =f2( 1, 2), паˆ раметрами яких є оцінки h , ˆ , що дозволяє за0 ˆ стосувати для визначення h і ˆ 0 метод найменших квадратів. Приведена корисна модель пояснюється кресленням, де на Фіг. показана структурна схема пристрою для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи. Пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи містить вимірювальний перетворювач 1 швидкості x , інтегратор 2, перший і другий знакочутливі елементи 3 і 4, відповідно, елемент 5 «І», (15) перший і другий елементи 6 і 7 диференціювання, чотири діоди 8, 9, 10 і 11 з першого по четвертий, відповідно, перший і другий інвертори 12 і 13, перший і другий тригери 14 і 15, генератор 16 імпульсів, перший і другий ключі 17 і 18, перший, другий і третій лічильники імпульсів 19, 20 і 21, перший і другий регістри 22 і 23, перший і другий цифро-аналогові перетворювачі 24 і 25, перший і другий комутатори 26 і 27, першу групу із «N» блоків пам'яті з першого по «N-й» 28-1, ... 28-і, ... 28-N відповідно, другу групу із «N» блоків пам'яті з першого по «N-й» 29-1, ... 29-і, ... 29-N, відповідно, групу із «N» блоків ділення з першого по «N-й» 301, ... 30-і, ... 30-N, відповідно, перший і другий блоки 31, 32 ділення (окремі), першу групу із «N» блоків множення з першого по «N-й» 33-1, ... 33-і, ... 33-N, відповідно, другу групу із «N» блоків множення з першого по «N-й» 34-1, ... 34-і, ... 34-N, відповідно, третю групу із «N» блоків множення з першого по «N-й» 35-1, ... 35-і, ... 35-N, відповідно, четверту групу із «N» блоків множення з першого по «N-й» 36-1, ... 36-і, ... 36-N, відповідно, п'яту групу із «N» блоків множення з першого по «N-й» 37-1, ... 37-і, ... 37-N, відповідно, перший і другий блоки 38 і 39 множення (окремі), групу із «N» блоків перетворювачів «синусу» з першого по «N-й» 40-1, ... 40-і, ... 40-N, відповідно, групу із «N» блоків перетворювачів «котангенсу» з першого по «N-й» 41-1, ... 41-і, ... 41-N, відповідно, чотири N-входові суматори 42, 43, 44 і 45 з першого по четвертий відповідно, дешифратор 46, N-входовий елемент 4 «І», формувач імпульсів 48, реєстратор 49, джерело 50 напруги величиною « », перший, другий і третій елементи 51, 52 і 53 затримки відповідно. Елементи і блоки пристрою з'єднані таким чином. Вихід вимірювального перетворювача 1 швид кості x з'єднаний з об'єднаними входами інтегратора 2 і першого знакочутливого елемента 3. Вихід інтегратора 2 з'єднаний з входом другого знакочутливого елемента 4, вихід якого з'єднаний з другим входом елемента 5 «І» безпосередньо, а через послідовно з'єднані другий елемент 7 диференціювання і другий діод 9 в прямому напрямку - з S-входом другого тригера 15, R-вхід якого через послідовно з'єднані четвертий діод 11 в зворотному напрямку і другий інвертор 13 з'єднаний з виходом другого елемента 7 диференціювання. Вихід першого знакочутливого елемента 3 з'єднаний з першим входом елемента 5 «І» , вихід якого через послідовно з'єднані перший елемент 6 диференціювання і перший діод 8 в прямому напрямку з'єднаний з S-входом першого тригера 14, R-вхід якого через послідовно з'єднані третій діод 10 в зворотному напрямку і перший інвертор 12 з'єднаний з виходом першого елемента 6 диференціювання. 11 13188 12 Прямі виходи першого і другого тригерів 14 і ... 34-N, відповідно. 15 з'єднані з керувальними входами першого і друВиходи перетворювачів «котангенсу» групи із гого ключів 17 і 18 відповідно, інформаційні входи «N» блоків перетворювачів «котангенсу» з першояких об'єднані і з'єднані з виходом генератора 16 го по «N-й» 41-1, ... 41-і, ... 41-N відповідно з'єднані імпульсів. з входами блоків множення третьої групи із «N» Виходи першого і другого ключів 17 і 18 з'єдблоків множення з першого по «N-й» 35-1, ... 35-і, нані з лічильними входами першого і другого лічи... 35-N, відповідно, виходи яких з'єднані з входами льників 19, 20 імпульсів, відповідно. третього N-входового суматора 44, вихід якого Прямі виходи розрядів першого і другого лічиз'єднаний з входом «Ділене» другого блоку 32 дільників 19 і 20 імпульсів з'єднані з розрядними лення, вхід «Подільник» якого з'єднаний з виходом входами першого і другого регістрів 22 і 23, відпочетвертого N-входового суматора 45, входи якого відно. Розрядні виходи першого регістра 22 з'єдз'єднані з виходами блоків множення п'ятої групи із нані з входами першого цифро-аналового перет«N» блоків множення з першого по «N-й» 37-1, ... ворювача 24, розрядні виходи другого регістра 23 37-i, ... 37-N, відповідно, перший і другий входи з'єднані з входами другого цифро-аналового перекожного з яких об'єднані і з'єднані з виходами друтворювача 25. Виходи першого і другого цифрогої групи із «N» блоків пам'яті з першого по «N-й» аналогових перетворювачів 24 і 25 з'єднані з вхо29-1, ... 29-і, ... 29-N відповідно. дами першого і другого комутаторів 26 і 27, відпоВиходи першого і другого блоків 31 і 32 діленвідно. Виходи з першого по N-й першого комутатоня з'єднані з першими входами першого і другого ра 26 з'єднані з інформаційними входами блоків блоків 38 і 39 множення, відповідно. пам'яті першої групи із «N» блоків пам'яті з першоВиходи першого і другого блоків 38 і 39 много по «N-й» 28-1, ... 28-і, ... 28-N, відповідно. ження з'єднані з першим і другим входами, відпоВиходи з першого по N-й другого комутатора відно, реєстратора 49. 27 з'єднані з інформаційними входами блоків паДругі входи блоків множення першої групи із м'яті другої групи із «N» блоків пам'яті з першого «N» блоків множення з першого по «N-й» 33-1, ... по «N-й» 29-1, ... 29-і, ... 29-N, відповідно. 33-і, ... 33-N, відповідно, другі входи першого і друВиходи блоків пам'яті першої групи із «N» блогого блоків 38 і 39 множення об'єднані і з'єднані з ків пам'яті з першого по «N-й» 28-1, ... 28-і, ... 28-N, виходом джерела 50 напруги величиною « ». відповідно з'єднані з входами «Ділене» блоків діДругі входи блоків другої групи із «N» блоків лення групи із «N» блоків ділення з першого по «Nмноження з першого по «N-й» 34-1, ... 34-і, ... 34-N й» 30-1, ... 30-і, ... 30-N, відповідно, входи «Подільвідповідно з'єднані з виходами блоків пам'яті друник» яких з'єднані з виходами блоків пам'яті другої гої групи із «N» блоків пам'яті з першого по «N-й» групи із «N» блоків пам'яті з першого по «N-й» 2929-1, ... 29-і, ... 29-N, відповідно. Другі входи блоків 1, ... 29-і, ... 29-N, відповідно. множення третьої групи із «N» блоків множення з Виходи блоків ділення групи із «N» блоків діпершого по «N-й» 35-1, ... 35-і, ... 35-N відповідно лення з першого по «N-й» 30-1, ... 30-і, ... 30-N, з'єднані з виходами блоків пам'яті другої групи із відповідно з'єднані з першими входами блоків «N» блоків пам'яті з першого по «N-й» 29-1, ... 29-i, множення першої групи із «N» блоків множення з ... 29-N, відповідно. першого по «N-й» 33-1, ... 33-і, ... 33-N, відповідно, Вихід другого інвертора 13 з'єднаний з установиходи яких з'єднані з входами перетворювачів вочними входами першого і другого регістрів 22 і «синусу» групи із «N» блоків перетворювачів «си23 безпосередньо, а з установочними входами нусу» з першого по «N-й» 40-1, ... 40-і, ... 40-N, першого і другого лічильників 19 і 20 - через первідповідно, а також з входами перетворювачів «коший елемент 51 затримки. тангенсу» групи із «N» блоків перетворювачів «коЛічильний вхід третього лічильника 21 імпультангенсу» з першого по «N-й» 41-1, ... 41-і, ... 41-N, сів через другий елемент 52 затримки з'єднаний з відповідно. виходом другого інвертора 13. Виходи перетворювачів «синусу» групи із «N» Прямі виходи розрядів третього лічильника 21 блоків перетворювачів «синусу» з першого по «Nімпульсів з'єднані з входами дешифратора 46, й» 40-1, ... 40-і, ... 40-N відповідно з'єднані з вховиходи якого з першого по N-й з'єднані з відповіддами блоків множення другої групи із «N» блоків ними об'єднаними керувальними входами першого множення з першого по «N-й» 34-1, ...34-і, ... 34-N, комутатора 26, другого комутатора 27, входами відповідно, виходи яких з'єднані з входами четвер«Запис» блоків пам'яті першої групи із «N» блоків тої групи із «N» блоків множення з першого по «Nпам'яті з першого по «N-й» 28-1, ... 28-і, ... 28-N, й» 36-1, ... 36-і, ... 36-N, відповідно. Перший і друвідповідно, входами «Запис» блоків пам'яті другої гий входи кожного блоку множення четвертої групи групи із «N» блоків пам'яті з першого по «N-й» 29із «N» блоків множення з першого по «N-й» 36-1, ... 1, ... 29-і, ... 29-N відповідно. Прямі виходи розря36-і, ... 36-N, відповідно об'єднані. дів третього лічильника 21 імпульсів з'єднані з Виходи блоків множення четвертої групи із входами N-входового елемента 47 «І», вихід якого «N» блоків множення з першого по «N-й» 36-1, ... через формувач 48 імпульсів з'єднаний з об'єдна36-і, ... 36-N відповідно з'єднані з входами другого ними входами «Читання» блоків пам'яті першої N-входового суматора 43, вихід якого з'єднаний з групи із «N» блоків пам'яті з першого по «N-й» 28входом «Подільник» першого блока 31 ділення, 1, ... 28-і, ... 28-N, відповідно, з об'єднаними вховхід «Ділене» якого з'єднаний з виходом першого дами «Читання» блоків пам'яті другої групи із «N» N-входового суматора 42, входи якого з'єднані з блоків пам'яті з першого по «N-й» 29-1, ... 29-і, ... виходами блоків множення другої групи із «N» 29-N, відповідно. Вихід другого елемента 52 заблоків множення з першого по «N-й» 34-1, ... 34-і, тримки через третій елемент 53 затримки з'єдна 13 13188 14 ний з входами «Скид» першого і другого регістрів другого інвертора 13 після проходження через 22 і 23 відповідно. перший елемент 51 затримки надходить на устаПристрій функціонує таким чином. новочні входи першого і другого лічильників 19 і 20 Вимірювальний перетворювач 1 швидкості імпульсі, установлюючи їх в нульовий стан. формує на виході напругу, що пропорційна швидІмпульс з виходу другого інвертора 13 через другий елемент 52 затримки надходить на лічиль кості x dx / dt , а на виході інтегратора 2 формуний вхід третього N-розрядного лічильника 21 імється напруга, пропорціональна переміщенню х. пульсів, установлюючи його в стан 000...1. На виходах першого і другого знакочутливих елеПри цьому на першому виході дешифратора ментів 3 і 4 формуються сигнали в часових інтер46 формується сигнал, що надходить на перші валах позитивних полуперіодів вхідних сигналів x керувальні входи першого і другого комутаторів 26 і х відповідно. і 27, на вхід «Запис» першого блока 28-1 пам'яті На виході елемента 5 «І» сигнал формується в першої групи із «N» блоків пам'яті і на вхід «Зачасовому інтервалі при умові співпадання позитипис» першого блока 29-1 пам'яті другої групи із вних значень х і x в кожному полу періоді. «N» блоків пам'яті, тим самим в блоці 28-1 пам'яті В часовий момент t1 початку формування сигфіксується сигнал 11, що формується після надналу на виході елемента 5 «І» перший тригер 14 ходження цифрового сигналу з виходу першого установлюється в одиничний стан імпульсом, що регістра 22 на вхід першого цифро-аналового пенадходить з виходу першого елемента 6 дифереретворювача 24 і через перший комутатор 26 на нціювання через перший діод 8 на його S-вхід. При інформаційний вхід першого блока 28-1 пам'яті цьому перший ключ 17 замикається за рахунок першої групи із «N» блоків пам'яті. В блоці 29-1 надходження на його керувальний вхід напруги з пам'яті другої групи із «N» блоків пам'яті фіксуєтьпрямого виходу першого тригера 14, а тому на ся сигнал 21, що формується після надходження лічильний вхід першого лічильника 19 імпульсів цифрового сигналу з виходу другого регістра 23 на надходять імпульси з виходу генератора 16 імпувхід другого цифро-аналового перетворювача 25 і льсів. через другий комутатор 27 на інформаційний вхід В той же часовий момент t1 другий тригер 15 першого блока 29-1 пам'яті другої групи із «N» установлюється в одиничний стан імпульсом, що блоків пам'яті. надходить з виходу другого елемента 7 диференІмпульсний сигнал з виходу другого елемента ціювання через другий діод 9 на його S-вхід. 52 затримки через третій елемент 53 затримки При цьому замикається другий ключ 18 за ранадходить на входи «Скид» першого і другого регіхунок надходження на його керувальний вхід настрів 22 і 23, установлюючи їх в нульовий стан. пруги з прямого виходу другого тригера 15, а тому Таким чином, кожний наступний і-й полуперіод на лічильний вхід другого лічильника 20 імпульсів сигналу з виходу вимірювального перетворювача надходять імпульси з виходу генератора 16 імпу1 швидкості призводить формування в лічильниках льсів. 19 і 20 імпульсів послідовно сигналів величиною Перший тригер 14 установлюється в нуль ім, 1i, 2i, відповідно (i 1 N) . пульсом з виходу першого елемента 6 диференціювання, що відповідає задньому фронту імпульЦі сигнали в аналоговій формі після прохосу з виходу елемента 5 «І» після його дження через перший і другий цифро-аналогові проходження через третій діод 10 і перший інверперетворювачі 24 і 25 відповідно надходять на тор 12 на R-вхід першого тригера 14. При цьому входи відповідно першого або другого комутаторів перший ключ 17 розмикається, імпульси на лічи26, 27. льний вхід першого лічильника 19 імпульсів не Число N полуперіодів вхідного сигналу надходять, зміст першого лічильника 19 імпульсів x dx / dt фіксується змістом третього лічильника залишається незмінним. 21 імпульсів. Після формування відповідного сигВ момент часу, що відповідає задньому фронналу на виході дешифратора 46 величина кожного ту імпульса з виходу другого знакочутливого елеі-го інтервалу 1i фіксується відповідним і-м бломента 4, після його проходження через другий ком 28-і пам'яті першої групи із «N» блоків пам'яті, елемент 7 диференціювання і проходження негаа величина кожного і-го інтервалу 2i фіксується тивного імпульсу через четвертий діод 11 і другий відповідно і-м блоком 29-і пам'яті другої групи із інвертор 13 на R-вхід другого тригера 15 цей три«N» блоків пам'яті. гер установлюється в нульовий стан. При цьому Після формування необхідної кількості і=N інна керувальний вхід другого ключа 18 надходить тервалів 1i, 2i на виході N-входового елемента нульовий рівень напруги, ключ 18 розмикається, 47 «І» з'являється сигнал, а на виході формувача імпульси на лічильний вхід другого лічильника 20 48 імпульсів формується імпульсний сигнал необімпульсів не надходять, зміст другого лічильника хідної тривалості, що надходить на входи «Читан20 імпульсів залишається незмінним. ня» блоків 28-1, ... 28-і, ... 28-N пам'яті першої груІмпульс, що відповідає задньому фронту імпупи із «N» блоків пам'яті і на входи «Читання» льсу з виходу другого знакочутливого елемента 4, блоків пам'яті 29-1, ... 29-і, ... 29-N другої групи із з виходу другого інвертора 13 надходить на входи «N» блоків пам'яті. «Прийом» першого і другого регістрів 22 і 23 безНа входи «Ділене» блоків 30-1, ... 30-і, ... 30-N посередньо. При цьому зміст першого лічильника ділення групи із «N» блоків ділення надходять сиг19 імпульсів переноситься в перший регістр 22, а нали 11, ... 1i, ... 1N, з виходів відповідних блоків зміст другого лічильника 20 імпульсів переносить28-1, ... 28-і, ... 28-N пам'яті першої групи із «N» ся в другий регістр 23. Той же імпульс з виходу блоків пам'яті, а на входи «Подільник» блоків 30-1, 15 13188 16 N N ... 30-і, ... 30-N ділення групи із «N» блоків ділення 2 2 [ 2i sin ( 2i sin( 1i / 2i )] /[ 1i / 2i )] , надходять сигнали 21, ... 2i, ... 2N з виходів відi 1 i 1 повідних блоків 29-1, ... 29-і, ... 29-N пам'яті другої надходить на перший вхід «Реєстрація ˆ 0 » групи із «N» блоків пам'яті. На виходах блоків 30-1, ... 30-і, ... 30-N ділення групи із «N» блоків ділення реєстратора 49. формуються сигнали 11/ 21 ... 1i/ 2і, ... 1N/ 2N Вихідні сигнали 11/ 21, ... 2i/ 2i, … 1N/ 2N відповідно. Ці сигнали надходять на перші входи блоків 33-1, ... 33-i, ... 33-N множення першої групи блоків 33-1, ... 33-i, ... 33-N множення першої групи із «N» блоків множення надходять на входи перетіз «N» блоків множення, на об'єднані другі входи ворювачів 41-1, ... 41-і, ... 41-N «котангенсу» групи яких надходять сигнали величиною « » з виходу із «N» блоків перетворювачів «котангенсу», вихідні джерела 50 напруги величиною « ». сигнали яких ctg( 11/ 21), ... ctg( 1i/ 2i), ... Вихідні сигнали ctg( 1N/ 2N) надходять на перші входи блоків 3511/ 21 ... 2i/ 2і, ... 1N/ 2N блоків 33-1, ... 33-і, ... 33-N множення першої групи 1, ... 35-і, ... 35-N множення третьої групи із «N» із «N» блоків множення надходять на входи перетблоків множення, на другі входи яких надходять ворювачів 40-1, ... 40-i, ... 40-N «синусу» групи із сигнали 21, ... 2i, ... 2N з виходів блоків 29-1, ... «N» блоків перетворювачів «синусу», вихідні сиг29-і, ... 29-N пам'яті другої групи із «N» блоків панали яких sin( 11/ 21), ... sin( 1i/ 2i), ... м'яті. sin( 1N/ 2N) надходять на перші входи відповідних Вихідні сигнали ... 21ctg( 11/ 21), блоків 34-1, ... 34-i, ... 34-N множення другої групи 2ictg( 1i/ 2i), ... 2Nctg( 1N/ 2N) блоків 35-1, ... 35із «N» блоків множення, на другі входи яких переі, ... 35-N множення третьої групи із «N» блоків ходять сигнали 21, ... 2і, ... 2N з виходів відповідмноження надходять на входи третього суматора них блоків 29-1, ... 29-і, ... 29-N пам'яті другої групи 44, вихідний сигнал якого, що дорівнює величині із «N» блоків пам'яті. Вихідні сигнали N ... ... 2i ctg( 1i / 2i ) , 21sin( 1i/ 2i), 2Nsin( 1N/ 2N), i 1 2Nsin( 1N/A2N) блоків 34-1, ... 34-i, ... 34-N мнонадходить на вхід «Ділене» другого блока 32 ження другої групи із «N» блоків множення надходілення. дять на входи першого суматора 42, вихідний сигВихідні сигнали 21, ... 2i, ... 2N блоків 29-1, ... нал якого, що дорівнює величині 2іsin( 1і/ 2і), 29-і, ... 29-N пам'яті другої групи із «N» блоків панадходить на вхід «Ділене» першого блока 31 дім'яті надходять на об'єднані входи поблочно блолення. ків 37-1, ... 37-і, ... 37-N множення п'ятої групи із Вихідні сигнали ... 21sin( 11/ 21), «N» блоків множення, на виходах яких формують2іsin( 1i/ 2i), ... 2Nsin( 1N/ 2N) блоків 34-1, ... 34ся сигнали 212, ... 2i2, ... 2N2. і, ... 34-N множення другої групи із «N» блоків мноВихідні сигнали блоків 37-1, ... 37-і, ... 37-N ження надходять на об'єднані перший і другий множення п'ятої групи із «N» блоків множення навходи відповідних блоків 36-1, ... 36-і, ... 36-N мнодходять на входи четвертого суматора 45, вихідження четвертої групи із «N» блоків множення, вихідні сигнали яких, що дорівнюють величинам 2 2 2 2 ... ... 21sin ( 11/ 21), 2isin ( 1i/ 2i), 2 2 2Nsin ( 1N/ 2N), надходять на входи другого суматора 43, на виході якого формується сигнал, що дорівнює величині N 2 2i sin( 1i / ний сигнал якого, що дорівнює величині N [ [ IV 2i i 1 sin( 1i / 2i )] /[ 2 2i sin2 ( 1i / 2i )] , i 1 надходить на перший вхід першого блока 38 множення, на другий вхід якого надходить сигнал величини « » з виходу джерела 50 напруги величиною « ». Вихідний сигнал першого блока 38 множення, що дорівнює величині 2i , надходить на вхід «Подільник» другого блока 32 ділення, вихідний сигнал якого, що дорівнює величині i 1 який надходить на вхід «Подільник» першого блока 31 ділення, вихідний сигнал якого, що дорівнює величині 2 i 1 N 2i ) , N N 2i ctg( 1i / 2i )] /[ i 1 2 2i ] i 1 надходить на перший вхід другого блока 39 множення, на другий вхід якого надходить сигнал величиною « » з виходу джерела 50 напруги величиною « ». Вихідний сигнал другого блока 39 множення, що дорівнює величині N [ N 2i i 1 ctg( 1i / 2i )] /[ 2 2i ] , i 1 ˆ надходить на другий вхід «Реєстрація h » реєстратора 49. 17 Комп’ютерна верстка А. Крижанівський 13188 Підписне 18 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determining the power dissipation coefficient and natural frequency of a mechanical system

Автори англійськоюPuz'ko Ihor Danylovych, Osipov Valerii Anatoliiovych

Назва патенту російськоюУстройство для определения коэффициента рассеяния энергии и собственной частоты механической колебательной системы

Автори російськоюПузько Игорь Данилович, Осипов Валерий Анатольевич

МПК / Мітки

МПК: G01M 7/00

Мітки: власної, енергії, механічної, частоти, коливальної, параметра, розсіяння, пристрій, системі, визначення

Код посилання

<a href="https://ua.patents.su/9-13188-pristrijj-dlya-viznachennya-parametra-rozsiyannya-energi-i-vlasno-chastoti-mekhanichno-kolivalno-sistemi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення параметра розсіяння енергії і власної частоти механічної коливальної системи</a>

Попередній патент: Регенераторний пристрій

Наступний патент: Апарат для термічної обробки брикетів

Випадковий патент: Спосіб одержання постійного струму і пристрій для його здійснення