Мережевий пристрій управління

Номер патенту: 119773

Опубліковано: 10.10.2017

Автори: Кургаєв Олександр Пилипович, Григор'єв Сергій Миколайович

Формула / Реферат

Мережевий пристрій управління, що містить множину автоматів управління, кожний з яких складають із вихідної логіки, блока станів та логіки переходів, чиї перший та другий входи підключено до виходу умов операційного пристрою та до перших виходів блока станів, чий тактовий вхід з'єднано із виходом тактового сигналу, а другі виходи підключено до входів вихідної логіки, чиї виходи з'єднано із входами управління операційного пристрою, який відрізняється тим, що кожен з виходів логіки переходів будь-якого автомата управління підключено до входу активізації блока станів деякого автомата управління.

Текст

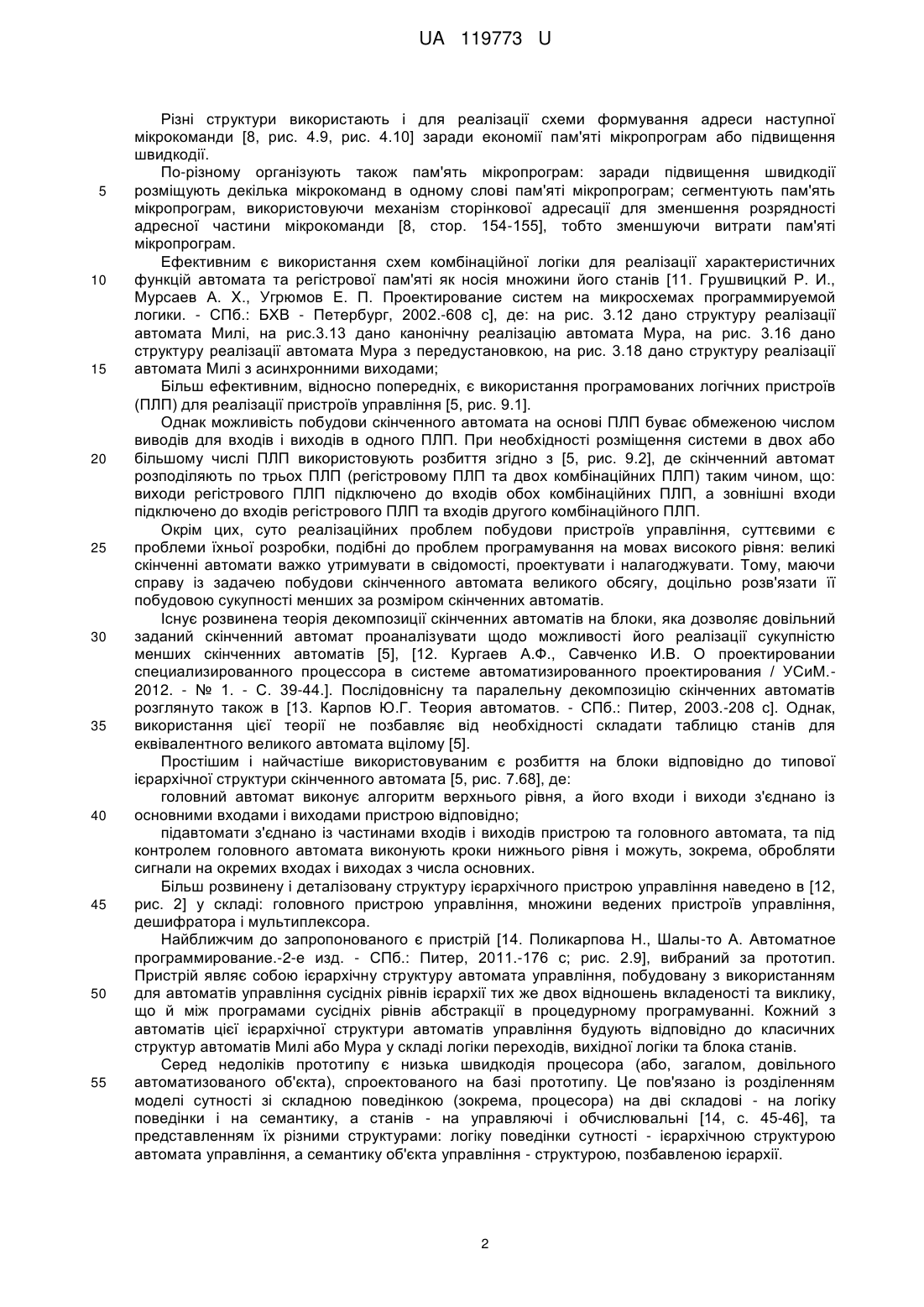

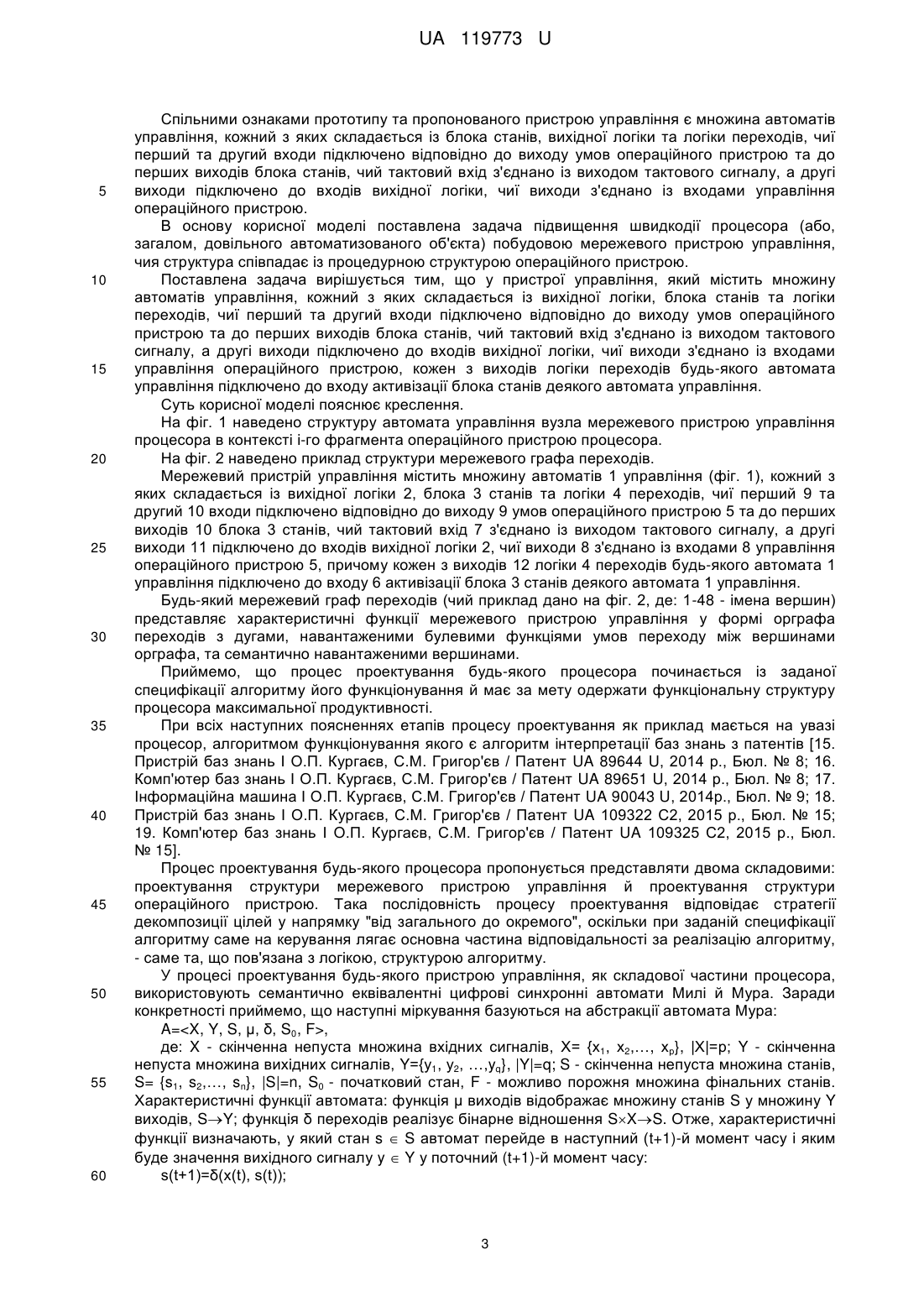

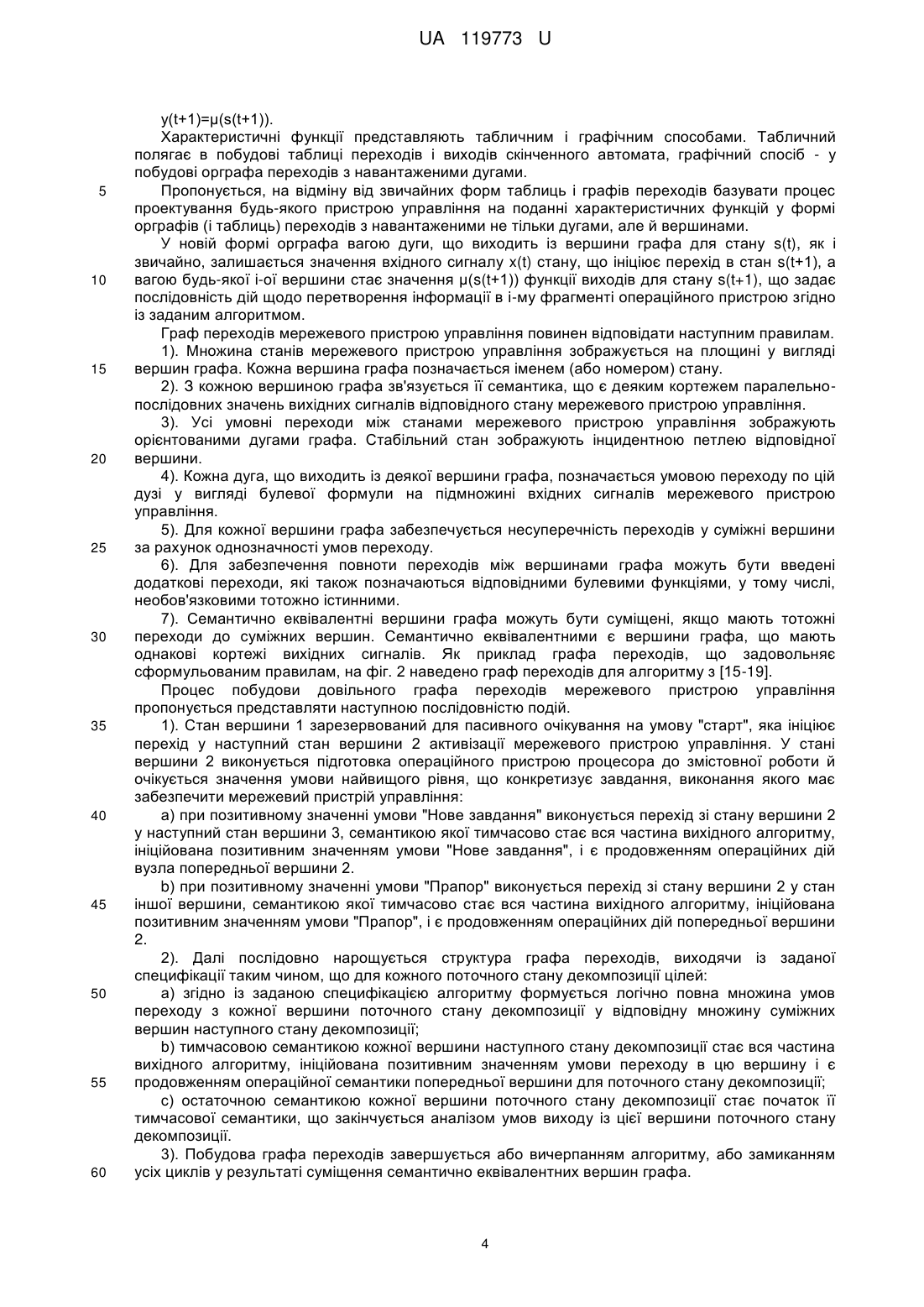

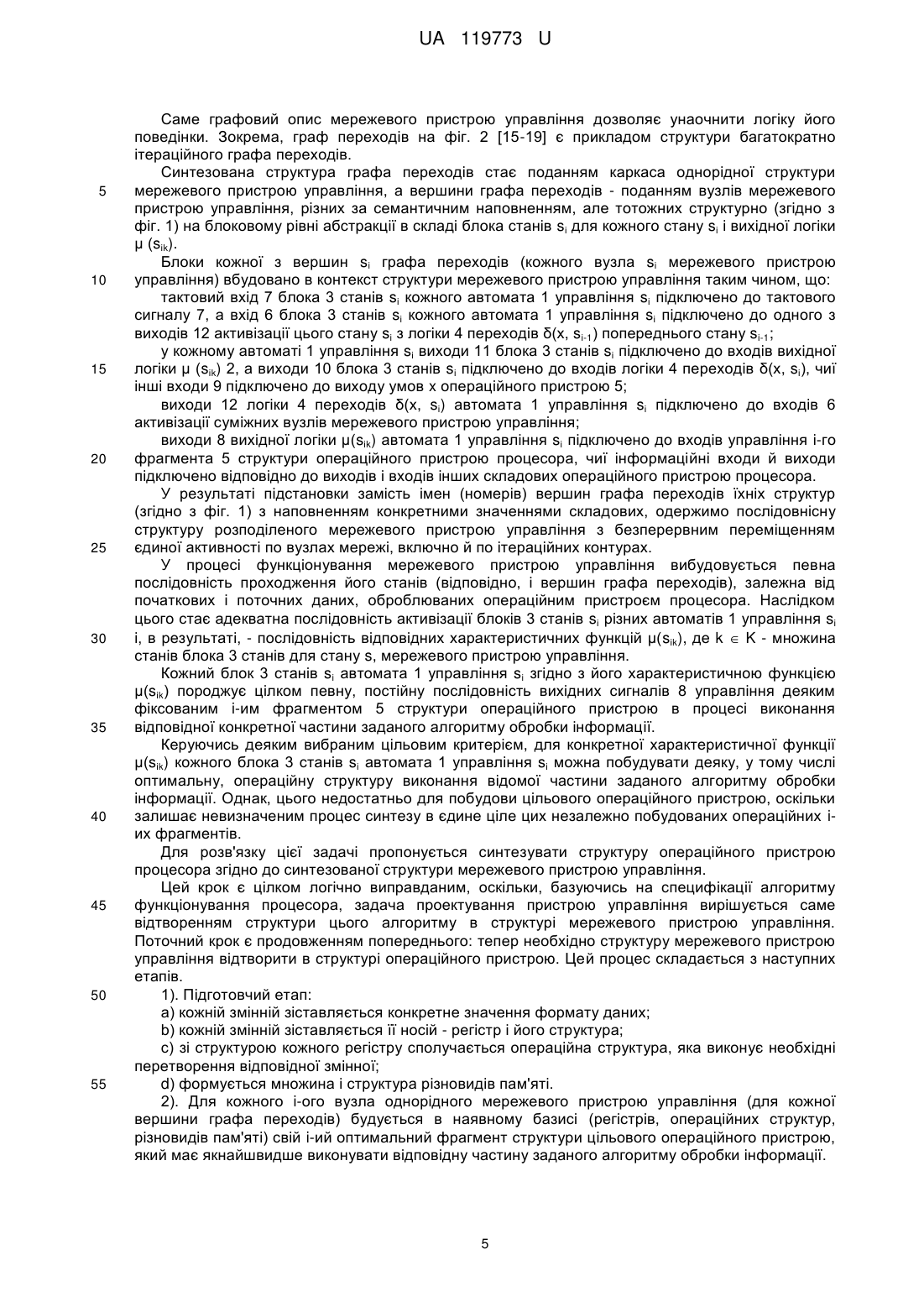

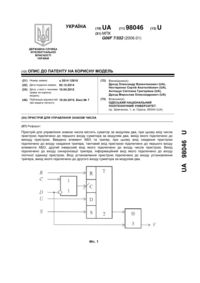

Реферат: UA 119773 U UA 119773 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до області обчислювальної техніки та може бути використана при побудові універсальних і спеціалізованих процесорів різного призначення. Моделлю послідовнісного дискретного пристрою є скінченний автомат, тобто система, здатна перебувати в одному із станів з деякої дискретної множини, змінювати стан залежно від входу й формувати виходи відповідно до певного алгоритму. Хоча теорія скінченних автоматів вивчає дуже прості моделі, вона є фундаментом великої кількості різноманітних додатків - від інтелектуальних, мовних процесорів до систем управління реального часу, протоколів зв'язку, вбудованих контролерів та, навіть, покладена в основу нового типу програмування автоматного програмування. На сьогодні накопичена величезна бібліографія щодо теорії та практики побудови і реалізації пристроїв управління різної досконалості та призначення на основі моделей автомата. До ґрунтовних робіт в цій області належать [1. Глушков В.М. Синтез цифровых автоматов. - М: Физматгиз, 1962.-476 с; 2. Майоров С. А., Новиков Г. И. Структура электронных вычислительных машин. - Л.: Машиностроение, 1979. - 384 с; 3. Брауэр В. Введение в теорию конечных автоматов: Пер. с нем. - М.: Радио и связь, 1987.-392 с; 4. Лазарев В.Г., Пийль Е.И. Синтез управляющих автоматов.-3-е изд., перераб. и доп. - М.: Энерго-атомиздат, 1989.-328 с; 5. Уэйкерли Джон Ф. Проектирование цифровых устройств. - М.: ПОСТМАРКЕТ, 2002.-1088 с; 6. Мозговой М.В. Классика программирования: алгоритмы, языки, автоматы, компиляторы. Практический подход. - СПб.: Наука и Техника, 2006.-320 с; 7. Хопкрофт, Джон, Э., Мотва-ни, Раджив, Ульман, Джеффри, Д. Введение в теорию автоматов, языков и вычислений, 2-е изд…: Пер. с англ. - М.: Издательский дом "Вильяме", 2008.-528 с; 8. Орлов С. А., Цилькер Б. Я. Организация ЭВМ и систем: Учебник для вузов. 2-е изд. - СПб.: Питер, 2011.-688 с; 9. Паттерсон Д., Хеннесси Дж. Архитектура компьютера и проектирование компьютерных систем. Классика Computers Science. 4-е изд. - СПб.: Питер, 2012.-784 с; 10. Таненбаум Э., Остин Т. Архитектура компьютера. 6-е изд. - СПб.: Питер, 2013.-816 с.]. Традиційним є розподіл автоматів на класичні моделі скінченних автоматів Милі й Мура. В автоматі Милі стан і вихідний сигнал у черговому такті визначаються станом і вхідним сигналом у попередньому такті роботи, а в автоматі Мура вихідний сигнал залежить лише від стану автомата в поточний момент часу. Структура синхронного пристрою управління складається з: логіки переходів, пам'яті станів і вихідної логіки. Пам'ять станів представляється набором запам'ятовуючих елементів, що зберігають поточний стан автомата. Логіка переходів визначає наступний стан автомата і є функцією від вхідної інформації пристрою управління й поточного стану. Вихідна команда визначається засобами вихідної логіки і є функцією від вхідної інформації пристрою управління й поточного стану (для автомата Милі) або лише від поточного стану (для автомата Мура). Останнім часом набір застосовуваних моделей, виходячи з вимог і можливостей практики, розширився: нарівні із синхронними, використовуються автомати Милі із асинхронними виходами, автомати Мура із предустановкою і ряд інших модифікацій. Реалізацією найпростішого автомата є тригер: його стани є станами автомата, а виходи є виходами автомата, тобто тригер реалізує автомат Мура; входами автомата на базі RS-тригера є його Reset і Set входи, а автомата на базі лічильного тригера - його лічильний вхід. Для реалізації реальних пристроїв управління використовують більш ефективні структури та засоби, зокрема, наступні. Структура формувача сигналів управління загального застосування в мікропрограмному автоматі з програмованою логікою включає [8, рис. 4.6]: схему формування адреси мікрокоманд, регістр адреси управляючої пам'яті, управляючу пам'ять, регістр мікрокоманд та дешифратор мікрокоманд. Конкретну реалізацію цієї структури наведено в [10, рис. 4.5] Використанням різнотипів кодування мікрооперацій [8, рис. 4.7] зменшують витрати пам'яті на представлення мікрокоманд. Іноді використовується дворівневе кодування мікрооперацій. На першому рівні з вертикальним кодуванням вибирається мікрокоманда, чиє поле мікрооперацій містить адресу горизонтальної мікрокоманди другого рівня - нанокоманди. Даний спосіб комбінування вертикального й горизонтального кодування називають нанокодуванням. Метод припускає дворівневу систему кодування мікрооперацій і, відповідно, дворівневу організацію управляючої пам'яті [8, рис. 4.8]. В цій структурі верхній рівень управління складають мікропрограми, що зберігаються в пам'яті мікропрограм. Кожній мікрокоманді відповідає деяка із нанокоманд, що зберігаються в управляючій пам'яті нижнього рівня - пам'яті нанокоманд. Саме нанокоманди використовуються для безпосереднього формування сигналів управління. Такий підхід, зберігаючи всі переваги горизонтального кодування, дозволяє значно скоротити сумарну ємність управляючої пам'яті. 1 UA 119773 U 5 10 15 20 25 30 35 40 45 50 55 Різні структури використають і для реалізації схеми формування адреси наступної мікрокоманди [8, рис. 4.9, рис. 4.10] заради економії пам'яті мікропрограм або підвищення швидкодії. По-різному організують також пам'ять мікропрограм: заради підвищення швидкодії розміщують декілька мікрокоманд в одному слові пам'яті мікропрограм; сегментують пам'ять мікропрограм, використовуючи механізм сторінкової адресації для зменшення розрядності адресної частини мікрокоманди [8, стор. 154-155], тобто зменшуючи витрати пам'яті мікропрограм. Ефективним є використання схем комбінаційної логіки для реалізації характеристичних функцій автомата та регістрової пам'яті як носія множини його станів [11. Грушвицкий Р. И., Мурсаев А. X., Угрюмов Е. П. Проектирование систем на микросхемах программируемой логики. - СПб.: БХВ - Петербург, 2002.-608 с], де: на рис. 3.12 дано структуру реалізації автомата Милі, на рис.3.13 дано канонічну реалізацію автомата Мура, на рис. 3.16 дано структуру реалізації автомата Мура з передустановкою, на рис. 3.18 дано структуру реалізації автомата Милі з асинхронними виходами; Більш ефективним, відносно попередніх, є використання програмованих логічних пристроїв (ПЛП) для реалізації пристроїв управління [5, рис. 9.1]. Однак можливість побудови скінченного автомата на основі ПЛП буває обмеженою числом виводів для входів і виходів в одного ПЛП. При необхідності розміщення системи в двох або більшому числі ПЛП використовують розбиття згідно з [5, рис. 9.2], де скінченний автомат розподіляють по трьох ПЛП (регістровому ПЛП та двох комбінаційних ПЛП) таким чином, що: виходи регістрового ПЛП підключено до входів обох комбінаційних ПЛП, а зовнішні входи підключено до входів регістрового ПЛП та входів другого комбінаційного ПЛП. Окрім цих, суто реалізаційних проблем побудови пристроїв управління, суттєвими є проблеми їхньої розробки, подібні до проблем програмування на мовах високого рівня: великі скінченні автомати важко утримувати в свідомості, проектувати і налагоджувати. Тому, маючи справу із задачею побудови скінченного автомата великого обсягу, доцільно розв'язати її побудовою сукупності менших за розміром скінченних автоматів. Існує розвинена теорія декомпозиції скінченних автоматів на блоки, яка дозволяє довільний заданий скінченний автомат проаналізувати щодо можливості його реалізації сукупністю менших скінченних автоматів [5], [12. Кургаев А.Ф., Савченко И.В. О проектировании специализированного процессора в системе автоматизированного проектирования / УСиМ.2012. - № 1. - С. 39-44.]. Послідовнісну та паралельну декомпозицію скінченних автоматів розглянуто також в [13. Карпов Ю.Г. Теория автоматов. - СПб.: Питер, 2003.-208 с]. Однак, використання цієї теорії не позбавляє від необхідності складати таблицю станів для еквівалентного великого автомата вцілому [5]. Простішим і найчастіше використовуваним є розбиття на блоки відповідно до типової ієрархічної структури скінченного автомата [5, рис. 7.68], де: головний автомат виконує алгоритм верхнього рівня, а його входи і виходи з'єднано із основними входами і виходами пристрою відповідно; підавтомати з'єднано із частинами входів і виходів пристрою та головного автомата, та під контролем головного автомата виконують кроки нижнього рівня і можуть, зокрема, обробляти сигнали на окремих входах і виходах з числа основних. Більш розвинену і деталізовану структуру ієрархічного пристрою управління наведено в [12, рис. 2] у складі: головного пристрою управління, множини ведених пристроїв управління, дешифратора і мультиплексора. Найближчим до запропонованого є пристрій [14. Поликарпова Н., Шалы-то А. Автоматное программирование.-2-е изд. - СПб.: Питер, 2011.-176 с; рис. 2.9], вибраний за прототип. Пристрій являє собою ієрархічну структуру автомата управління, побудовану з використанням для автоматів управління сусідніх рівнів ієрархії тих же двох відношень вкладеності та виклику, що й між програмами сусідніх рівнів абстракції в процедурному програмуванні. Кожний з автоматів цієї ієрархічної структури автоматів управління будують відповідно до класичних структур автоматів Милі або Мура у складі логіки переходів, вихідної логіки та блока станів. Серед недоліків прототипу є низька швидкодія процесора (або, загалом, довільного автоматизованого об'єкта), спроектованого на базі прототипу. Це пов'язано із розділенням моделі сутності зі складною поведінкою (зокрема, процесора) на дві складові - на логіку поведінки і на семантику, а станів - на управляючі і обчислювальні [14, с. 45-46], та представленням їх різними структурами: логіку поведінки сутності - ієрархічною структурою автомата управління, а семантику об'єкта управління - структурою, позбавленою ієрархії. 2 UA 119773 U 5 10 15 20 25 30 35 40 45 50 55 60 Спільними ознаками прототипу та пропонованого пристрою управління є множина автоматів управління, кожний з яких складається із блока станів, вихідної логіки та логіки переходів, чиї перший та другий входи підключено відповідно до виходу умов операційного пристрою та до перших виходів блока станів, чий тактовий вхід з'єднано із виходом тактового сигналу, а другі виходи підключено до входів вихідної логіки, чиї виходи з'єднано із входами управління операційного пристрою. В основу корисної моделі поставлена задача підвищення швидкодії процесора (або, загалом, довільного автоматизованого об'єкта) побудовою мережевого пристрою управління, чия структура співпадає із процедурною структурою операційного пристрою. Поставлена задача вирішується тим, що у пристрої управління, який містить множину автоматів управління, кожний з яких складається із вихідної логіки, блока станів та логіки переходів, чиї перший та другий входи підключено відповідно до виходу умов операційного пристрою та до перших виходів блока станів, чий тактовий вхід з'єднано із виходом тактового сигналу, а другі виходи підключено до входів вихідної логіки, чиї виходи з'єднано із входами управління операційного пристрою, кожен з виходів логіки переходів будь-якого автомата управління підключено до входу активізації блока станів деякого автомата управління. Суть корисної моделі пояснює креслення. На фіг. 1 наведено структуру автомата управління вузла мережевого пристрою управління процесора в контексті і-го фрагмента операційного пристрою процесора. На фіг. 2 наведено приклад структури мережевого графа переходів. Мережевий пристрій управління містить множину автоматів 1 управління (фіг. 1), кожний з яких складається із вихідної логіки 2, блока 3 станів та логіки 4 переходів, чиї перший 9 та другий 10 входи підключено відповідно до виходу 9 умов операційного пристрою 5 та до перших виходів 10 блока 3 станів, чий тактовий вхід 7 з'єднано із виходом тактового сигналу, а другі виходи 11 підключено до входів вихідної логіки 2, чиї виходи 8 з'єднано із входами 8 управління операційного пристрою 5, причому кожен з виходів 12 логіки 4 переходів будь-якого автомата 1 управління підключено до входу 6 активізації блока 3 станів деякого автомата 1 управління. Будь-який мережевий граф переходів (чий приклад дано на фіг. 2, де: 1-48 - імена вершин) представляє характеристичні функції мережевого пристрою управління у формі орграфа переходів з дугами, навантаженими булевими функціями умов переходу між вершинами орграфа, та семантично навантаженими вершинами. Приймемо, що процес проектування будь-якого процесора починається із заданої специфікації алгоритму його функціонування й має за мету одержати функціональну структуру процесора максимальної продуктивності. При всіх наступних поясненнях етапів процесу проектування як приклад мається на увазі процесор, алгоритмом функціонування якого є алгоритм інтерпретації баз знань з патентів [15. Пристрій баз знань І О.П. Кургаєв, С.М. Григор'єв / Патент UA 89644 U, 2014 р., Бюл. № 8; 16. Комп'ютер баз знань І О.П. Кургаєв, С.М. Григор'єв / Патент UA 89651 U, 2014 р., Бюл. № 8; 17. Інформаційна машина І О.П. Кургаєв, С.М. Григор'єв / Патент UA 90043 U, 2014р., Бюл. № 9; 18. Пристрій баз знань І О.П. Кургаєв, С.М. Григор'єв / Патент UA 109322 С2, 2015 р., Бюл. № 15; 19. Комп'ютер баз знань І О.П. Кургаєв, С.М. Григор'єв / Патент UA 109325 С2, 2015 р., Бюл. № 15]. Процес проектування будь-якого процесора пропонується представляти двома складовими: проектування структури мережевого пристрою управління й проектування структури операційного пристрою. Така послідовність процесу проектування відповідає стратегії декомпозиції цілей у напрямку "від загального до окремого", оскільки при заданій специфікації алгоритму саме на керування лягає основна частина відповідальності за реалізацію алгоритму, - саме та, що пов'язана з логікою, структурою алгоритму. У процесі проектування будь-якого пристрою управління, як складової частини процесора, використовують семантично еквівалентні цифрові синхронні автомати Милі й Мура. Заради конкретності приймемо, що наступні міркування базуються на абстракції автомата Мура: A=, де: X - скінченна непуста множина вхідних сигналів, Х= {х1, х2,…, хр}, |Х|=р; Y - скінченна непуста множина вихідних сигналів, Y={у1, у2, …,yq}, |Y|=q; S - скінченна непуста множина станів, S= {s1, s2,…, sn}, |S|=n, S0 - початковий стан, F - можливо порожня множина фінальних станів. Характеристичні функції автомата: функція μ виходів відображає множину станів S у множину Y виходів, SY; функція δ переходів реалізує бінарне відношення SXS. Отже, характеристичні функції визначають, у який стан s S автомат перейде в наступний (t+1)-й момент часу і яким буде значення вихідного сигналу y Y у поточний (t+1)-й момент часу: s(t+1)=δ(x(t), s(t)); 3 UA 119773 U 5 10 15 20 25 30 35 40 45 50 55 60 y(t+1)=μ(s(t+1)). Характеристичні функції представляють табличним і графічним способами. Табличний полягає в побудові таблиці переходів і виходів скінченного автомата, графічний спосіб - у побудові орграфа переходів з навантаженими дугами. Пропонується, на відміну від звичайних форм таблиць і графів переходів базувати процес проектування будь-якого пристрою управління на поданні характеристичних функцій у формі орграфів (і таблиць) переходів з навантаженими не тільки дугами, але й вершинами. У новій формі орграфа вагою дуги, що виходить із вершини графа для стану s(t), як і звичайно, залишається значення вхідного сигналу x(t) стану, що ініціює перехід в стан s(t+1), а вагою будь-якої і-ої вершини стає значення μ(s(t+1)) функції виходів для стану s(t+1), що задає послідовність дій щодо перетворення інформації в і-му фрагменті операційного пристрою згідно із заданим алгоритмом. Граф переходів мережевого пристрою управління повинен відповідати наступним правилам. 1). Множина станів мережевого пристрою управління зображується на площині у вигляді вершин графа. Кожна вершина графа позначається іменем (або номером) стану. 2). З кожною вершиною графа зв'язується її семантика, що є деяким кортежем паралельнопослідовних значень вихідних сигналів відповідного стану мережевого пристрою управління. 3). Усі умовні переходи між станами мережевого пристрою управління зображують орієнтованими дугами графа. Стабільний стан зображують інцидентною петлею відповідної вершини. 4). Кожна дуга, що виходить із деякої вершини графа, позначається умовою переходу по цій дузі у вигляді булевої формули на підмножині вхідних сигналів мережевого пристрою управління. 5). Для кожної вершини графа забезпечується несуперечність переходів у суміжні вершини за рахунок однозначності умов переходу. 6). Для забезпечення повноти переходів між вершинами графа можуть бути введені додаткові переходи, які також позначаються відповідними булевими функціями, у тому числі, необов'язковими тотожно істинними. 7). Семантично еквівалентні вершини графа можуть бути суміщені, якщо мають тотожні переходи до суміжних вершин. Семантично еквівалентними є вершини графа, що мають однакові кортежі вихідних сигналів. Як приклад графа переходів, що задовольняє сформульованим правилам, на фіг. 2 наведено граф переходів для алгоритму з [15-19]. Процес побудови довільного графа переходів мережевого пристрою управління пропонується представляти наступною послідовністю подій. 1). Стан вершини 1 зарезервований для пасивного очікування на умову "старт", яка ініціює перехід у наступний стан вершини 2 активізації мережевого пристрою управління. У стані вершини 2 виконується підготовка операційного пристрою процесора до змістовної роботи й очікується значення умови найвищого рівня, що конкретизує завдання, виконання якого має забезпечити мережевий пристрій управління: а) при позитивному значенні умови "Нове завдання" виконується перехід зі стану вершини 2 у наступний стан вершини 3, семантикою якої тимчасово стає вся частина вихідного алгоритму, ініційована позитивним значенням умови "Нове завдання", і є продовженням операційних дій вузла попередньої вершини 2. b) при позитивному значенні умови "Прапор" виконується перехід зі стану вершини 2 у стан іншої вершини, семантикою якої тимчасово стає вся частина вихідного алгоритму, ініційована позитивним значенням умови "Прапор", і є продовженням операційних дій попередньої вершини 2. 2). Далі послідовно нарощується структура графа переходів, виходячи із заданої специфікації таким чином, що для кожного поточного стану декомпозиції цілей: a) згідно із заданою специфікацією алгоритму формується логічно повна множина умов переходу з кожної вершини поточного стану декомпозиції у відповідну множину суміжних вершин наступного стану декомпозиції; b) тимчасовою семантикою кожної вершини наступного стану декомпозиції стає вся частина вихідного алгоритму, ініційована позитивним значенням умови переходу в цю вершину і є продовженням операційної семантики попередньої вершини для поточного стану декомпозиції; c) остаточною семантикою кожної вершини поточного стану декомпозиції стає початок її тимчасової семантики, що закінчується аналізом умов виходу із цієї вершини поточного стану декомпозиції. 3). Побудова графа переходів завершується або вичерпанням алгоритму, або замиканням усіх циклів у результаті суміщення семантично еквівалентних вершин графа. 4 UA 119773 U 5 10 15 20 25 30 35 40 45 50 55 Саме графовий опис мережевого пристрою управління дозволяє унаочнити логіку його поведінки. Зокрема, граф переходів на фіг. 2 [15-19] є прикладом структури багатократно ітераційного графа переходів. Синтезована структура графа переходів стає поданням каркаса однорідної структури мережевого пристрою управління, а вершини графа переходів - поданням вузлів мережевого пристрою управління, різних за семантичним наповненням, але тотожних структурно (згідно з фіг. 1) на блоковому рівні абстракції в складі блока станів sі для кожного стану sі і вихідної логіки μ (sіk). Блоки кожної з вершин sі графа переходів (кожного вузла sі мережевого пристрою управління) вбудовано в контекст структури мережевого пристрою управління таким чином, що: тактовий вхід 7 блока 3 станів sі кожного автомата 1 управління sі підключено до тактового сигналу 7, а вхід 6 блока 3 станів sі кожного автомата 1 управління sі підключено до одного з виходів 12 активізації цього стану sі з логіки 4 переходів δ(х, sі-1) попереднього стану sі-1; у кожному автоматі 1 управління sі виходи 11 блока 3 станів sі підключено до входів вихідної логіки μ (sіk) 2, а виходи 10 блока 3 станів sі підключено до входів логіки 4 переходів δ(х, sі), чиї інші входи 9 підключено до виходу умов x операційного пристрою 5; виходи 12 логіки 4 переходів δ(х, sі) автомата 1 управління sі підключено до входів 6 активізації суміжних вузлів мережевого пристрою управління; виходи 8 вихідної логіки μ(sіk) автомата 1 управління sі підключено до входів управління і-го фрагмента 5 структури операційного пристрою процесора, чиї інформаційні входи й виходи підключено відповідно до виходів і входів інших складових операційного пристрою процесора. У результаті підстановки замість імен (номерів) вершин графа переходів їхніх структур (згідно з фіг. 1) з наповненням конкретними значеннями складових, одержимо послідовнісну структуру розподіленого мережевого пристрою управління з безперервним переміщенням єдиної активності по вузлах мережі, включно й по ітераційних контурах. У процесі функціонування мережевого пристрою управління вибудовується певна послідовність проходження його станів (відповідно, і вершин графа переходів), залежна від початкових і поточних даних, оброблюваних операційним пристроєм процесора. Наслідком цього стає адекватна послідовність активізації блоків 3 станів sі різних автоматів 1 управління sі і, в результаті, - послідовність відповідних характеристичних функцій μ(sіk), де k K - множина станів блока 3 станів для стану s, мережевого пристрою управління. Кожний блок 3 станів sі автомата 1 управління sі згідно з його характеристичною функцією μ(sіk) породжує цілком певну, постійну послідовність вихідних сигналів 8 управління деяким фіксованим i-им фрагментом 5 структури операційного пристрою в процесі виконання відповідної конкретної частини заданого алгоритму обробки інформації. Керуючись деяким вибраним цільовим критерієм, для конкретної характеристичної функції μ(sіk) кожного блока 3 станів sі автомата 1 управління sі можна побудувати деяку, у тому числі оптимальну, операційну структуру виконання відомої частини заданого алгоритму обробки інформації. Однак, цього недостатньо для побудови цільового операційного пристрою, оскільки залишає невизначеним процес синтезу в єдине ціле цих незалежно побудованих операційних iих фрагментів. Для розв'язку цієї задачі пропонується синтезувати структуру операційного пристрою процесора згідно до синтезованої структури мережевого пристрою управління. Цей крок є цілком логічно виправданим, оскільки, базуючись на специфікації алгоритму функціонування процесора, задача проектування пристрою управління вирішується саме відтворенням структури цього алгоритму в структурі мережевого пристрою управління. Поточний крок є продовженням попереднього: тепер необхідно структуру мережевого пристрою управління відтворити в структурі операційного пристрою. Цей процес складається з наступних етапів. 1). Підготовчий етап: a) кожній змінній зіставляється конкретне значення формату даних; b) кожній змінній зіставляється її носій - регістр і його структура; c) зі структурою кожного регістру сполучається операційна структура, яка виконує необхідні перетворення відповідної змінної; d) формується множина і структура різновидів пам'яті. 2). Для кожного i-ого вузла однорідного мережевого пристрою управління (для кожної вершини графа переходів) будується в наявному базисі (регістрів, операційних структур, різновидів пам'яті) свій i-ий оптимальний фрагмент структури цільового операційного пристрою, який має якнайшвидше виконувати відповідну частину заданого алгоритму обробки інформації. 5 UA 119773 U 5 10 15 20 25 30 35 40 45 3). На кожному наступному кроці для чергового і-го вузла мережі виконується контекстна вставка i-го фрагмента структури операційного пристрою в структуру операційного пристрою, побудовану до початку цього кроку. 4). Процес побудови структури операційного пристрою завершується повним обходом усіх вершин графа. 5). Результатом є структура операційного пристрою процесора максимальної швидкодії, оскільки кожен крок синтезу цільової структури лише накопичує найпродуктивніші реалізації фрагментів заданого алгоритму. Згідно із запропонованим процесом синтезу побудовано й дано в [15-19] варіанти структури операційного пристрою процесора. Кроки проектування операційного пристрою процесора цілком природно об'єднується із кроками проектування мережевого пристрою управління в єдиний процес, послідовно нарощуючи їхні структури по етапах декомпозиції початкового алгоритму. Мережевий пристрій управління працює наступним чином. Алгоритм обробки даних задано структурою мережі та семантичним наповненням автоматів управління її вузлів. Початкові дані записано в регістрах та пам'ятях операційного пристрою. З початку, мережевий пристрій управління перебуває в стані 1, очікуючи на команду "старт". Команда "старт" надходить із операційного пристрою по лінії 9 в логіку 4 переходів вузла 1 мережі у формі значення умови х та, пройшовши з виходів 12 логіки 4 переходів вузла 1 мережі на вхід 6 блока 3 станів вузла 2 мережі, активізує перехід мережевого пристрою управління у стан вузла 2 мережі. У стані вузла 2 мережі виконується семантична обробка даних деякого фрагмента 5 операційного пристрою. Зокрема, це може бути підготовка операційного пристрою процесора до змістовної роботи й очікується значення умови найвищого рівня, що конкретизує завдання, виконання якого має забезпечити мережевий пристрій управління: Позитивне значення умови x="Нове завдання" на вході 9 логіки 4 переходів вузла 2 мережі, пройшовши з виходів 12 логіки 4 переходів автомата 1 управління вузла 2 мережі на вхід 6 блока 3 станів вузла 3 мережі, активізує перехід мережевого пристрою управління у наступний стан - у стан вузла 3 мережі. У цьому стані блок 3 станів цього вузла 3 мережі згідно із своїм вмістом ініціює деяку послідовність команд управління, яку вихідна логіка 2 перетворює в кортеж сигналів 8 управління семантичною обробкою даних деякого фрагмента 5 операційного пристрою, яка є продовженням операційних дій попереднього вузла 2 мережі. Позитивне значення умови х="Прапор" на вході 9 логіки 4 переходів вузла 2 мережі, пройшовши з виходів 12 логіки 4 переходів автомата 1 управління вузла 2 мережі на вхід 6 блока 3 станів деякого вузла (вузла 21 для прикладу на фіг. 2) мережі, активізує перехід мережевого пристрою управління у наступний стан - у стан відповідного вузла (вузла 21 для прикладу на фіг. 2) мережі. У цьому стані блок 3 станів цього вузла мережі згідно із своїм вмістом ініціює деяку послідовність команд управління, яку вихідна логіка 2 перетворює в кортеж сигналів 8 управління семантичною обробкою даних відповідного фрагмента 5 операційного пристрою, яка є продовженням операційних дій попереднього вузла 2 мережі. Далі у процесі функціонування мережевого пристрою управління вибудовується активізацією блоків 3 станів si різних автоматів 1 управління si певна послідовність проходження його вузлів, залежна від початкових і поточних даних, оброблюваних операційним пристроєм процесора. При цьому у кожному з вузлів мережі блок 3 станів відповідного автомата 1 управління згідно із своїм вмістом ініціює деяку послідовність команд управління, яку вихідна логіка 2 цього автомата 1 управління перетворює в кортеж сигналів 8 управління семантичною обробкою даних відповідного фрагмента 5 операційного пристрою процесора, що є продовженням операційних дій попереднього вузла мережі. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 50 55 Мережевий пристрій управління, що містить множину автоматів управління, кожний з яких складають із вихідної логіки, блока станів та логіки переходів, чиї перший та другий входи підключено до виходу умов операційного пристрою та до перших виходів блока станів, чий тактовий вхід з'єднано із виходом тактового сигналу, а другі виходи підключено до входів вихідної логіки, чиї виходи з'єднано із входами управління операційного пристрою, який відрізняється тим, що кожен з виходів логіки переходів будь-якого автомата управління підключено до входу активізації блока станів деякого автомата управління. 6 UA 119773 U 7 UA 119773 U Комп’ютерна верстка А. Крижанівський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 9/00

Мітки: управління, мережевий, пристрій

Код посилання

<a href="https://ua.patents.su/10-119773-merezhevijj-pristrijj-upravlinnya.html" target="_blank" rel="follow" title="База патентів України">Мережевий пристрій управління</a>

Попередній патент: Інтелектуальна розподілена система пам’яті із секціонованими модулями на пліс

Наступний патент: Спосіб моделювання хронічного іммобілізаційного стресу в експерименті

Випадковий патент: Спосіб одержання алюмінійоксидного каталізатора