Двійковий суматор

Номер патенту: 107131

Опубліковано: 25.11.2014

Автори: Палагін Олександр Васильович, Білик Віктор Кирилович, Клімовська Алла Іванівна, Боюн Віталій Петрович

Формула / Реферат

1. Двійковий суматор, до складу якого входять перший та другий обчислювальні блоки, причому перший та другий входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока, вихід якого з'єднано з першим входом другого обчислювального блока, другий вхід якого з'єднано з третім входом двійкового суматора, а вихід другого обчислювального блока з'єднано з першим виходом двійкового суматора, який відрізняється тим, що додатково введено аналоговий суматор та два інвертори, причому перший вихід двійкового суматора додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з другим виходом двійкового суматора, перший та другий входи аналогового суматора з'єднано відповідно з другими виходами першого та другого обчислювальних блоків, а вихід аналогового суматора з'єднано з третім виходом двійкового суматора, а також з входом другого інвертора, вихід якого з'єднано з четвертим виходом двійкового суматора.

2. Двійковий суматор за п. 1, який відрізняється тим, що обчислювальний блок складається з першого та другого аналогових суматорів, першого та другого інверторів, першого та другого порогових елементів, першого та другого детекторів та масштабного елемента, причому перший та другий входи обчислювального блока з'єднано відповідно з першим та другим входами першого аналогового суматора, а також один із входів обчислювального блока додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з першим входом другого аналогового суматора, другий вхід якого з'єднано з іншим входом обчислювального блока та першого аналогового суматора, при цьому вихід другого аналогового суматора з'єднано зі входом першого порогового елемента, вихід якого з'єднано зі входом першого детектора, вихід якого з'єднано з першим входом другого інвертора, вихід якого з'єднано з першим виходом обчислювального блока, при цьому вихід першого аналогового суматора з'єднано з другим входом другого інвертора, зі входом другого порогового елемента та з першим входом масштабного елемента, вихід якого з'єднано з другим виходом обчислювального блока, при цьому вихід другого порогового елемента з'єднано зі входом другого детектора, вихід якого з'єднано з другим входом масштабного елемента.

3. Двійковий суматор за п. 2, який відрізняється тим, що аналоговий суматор складається з резонаторів, де входи першого та другого резонаторів з'єднано відповідно з першим та другим входами аналогового суматора, а їх виходи з'єднано між собою та з входом третього резонатора, вихід якого з'єднано з виходом аналогового суматора.

4. Двійковий суматор за п. 2, який відрізняється тим, що масштабний елемент складається з осцилятора та двох резонаторів, при цьому перший та другий входи масштабного елемента з'єднано відповідно з першим та другим входами осцилятора, вихід якого з'єднано зі входами першого та другого резонаторів, виходи яких з'єднано з виходом масштабного елемента.

Текст

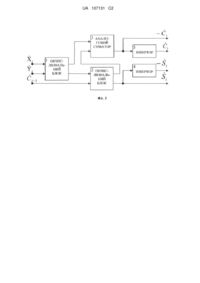

Реферат: Двійковий суматор належить до обчислювальної техніки і може бути використаний в комп'ютерах, зокрема, при побудові арифметико-логічних пристроїв та процесорів. До складу двійкового суматора входять перший та другий обчислювальні блоки, аналоговий суматор та перший і другий інвертори. Перший та другий входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока, перший вихід якого з'єднано з першим входом другого обчислювального блока, другий вхід якого з'єднано з третім входом двійкового суматора, а перший вихід другого обчислювального блока з'єднано з першим виходом двійкового суматора. Перший та другий входи аналогового суматора з'єднано відповідно з другими виходами першого та другого обчислювальних блоків, а вихід аналогового суматора з'єднано з другим виходом двійкового суматора, а також з'єднано з входом першого інвертора, вихід якого з'єднано з третім виходом двійкового суматора, причому четвертий вихід двійкового суматора з'єднано з виходом другого інвертора, вхід якого з'єднано з першим виходом другого обчислювального блока та з першим виходом двійкового суматора. Технічним результатом є можливість кодування негативного числа "-1" сигналом змінного струму резонансної частоти з фазою 180°, що дозволяє знизити споживану потужність пристроєм та розширити функціональні можливості так, щоб на тому ж обладнанні виконувалась як операція додавання, так і віднімання. UA 107131 C2 (12) UA 107131 C2 UA 107131 C2 5 10 15 20 25 30 35 40 45 50 55 Винахід належить до обчислювальної техніки і може бути використано в комп'ютерах, зокрема, при побудові арифметико-логічних пристроїв та процесорів. Споживання і розсіювання потужності в інтегральних схемах стає головною турботою напівпровідникової індустрії в даний час. Тому останнім часом основні зусилля фахівців спрямовані на пошук технічних рішень щодо скорочення потужності споживання в інтегральних схемах. Відомий пристрій [патент US 1969/3427445. Full adder using field effect transistor of the insulated gate type (Inventor: Jack R. Dailey. Applicant: International Business Machines Corporation (IBM)], який складається з першого і другого півсуматорів та логічного елемента АБО, при цьому перший і другий входи пристрою з'єднані паралельно з першим та другим входами, відповідно, першого півсуматора, перший вихід якого з'єднаний з першим входом другого півсуматора, перший вихід якого є виходом розряду суми повного суматора, а другий його вихід з'єднано з першим входом логічного елемента АБО, вихід якого є виходом розряду переносу повного суматора, а другий вхід логічного елемента АБО з'єднано з другим виходом першого півсуматора, при цьому другий вхід другого півсуматора з'єднано з третім входом повного суматора. Скорочення потужності споживання в ньому досягається за рахунок мінімізації кількості необхідних елементів шляхом застосування транзисторів різних типів (PMOS та NMOS). Спільними ознаками аналога та пропонованого двійкового суматора є перший та другий півсуматори, причому перший та другий входи двійкового суматора з'єднано з відповідними входами першого півсуматора, перший вихід якого з'єднано з першим входом другого півсуматора, другий вхід якого з'єднано з третім входом двійкового суматора, а вихід другого півсуматора з'єднано з першим виходом двійкового суматора. Причиною, що заважає досягненню поставленого завдання є те, що на сьогодні вже практично вичерпані можливості подальшого зниження споживаної потужності пристроїв, які створені на основі MOS транзисторів. Тому доводиться розширювати пошук перспективних технічних рішень за рахунок елементів, побудованих на основі альтернативних фізичних явищ. Другою причиною є неможливість кодування негативного числа "-1", що не забезпечує виконання операції віднімання на тому ж обладнанні. Одним з перспективних альтернативних напрямків створення елементів для комп'ютерів з низьким споживанням енергії на сьогодні є використання пристроїв з електромеханічним переносом електронів. При цьому можна знизити споживану потужність на порядок в порівнянні з МОП (MOS). В патенті US 2008/7414437 В1 [Blick and Marsland. Nanomechanical computer] запропоновано наноелектромеханічний елемент, на основі якого можуть бути побудовані стандартні логічні елементи НЕ та І-НЕ, з яких, як відомо, можливо побудувати двійковий суматор для комп'ютера. Спільними ознаками аналога та пропонованого двійкового суматора є те, що в ньому для побудови двійкового суматора використовуються енергоощадні елементи з електромеханічним переносом електронів. Причиною, що заважає досягненню поставленого завдання є складність елемента, що обмежує зниження його споживаної потужності, а також неможливість кодування негативного числа "-1", що не забезпечує виконання операції віднімання на тому ж обладнанні. Найбільш близьким пристроєм, що має значне число ознак, спільних з запропонованим технічним рішенням, є пристрій, наведений в патенті [US 2012/0124120 А1. Hirofumi Morise, Shiho Nakamura, Dalsuke Saida, Tsuyoshi Kondo (JP). Adder], який вибрано прототипом. Прототип (фіг. 1) складається з першого і другого спін-хвильових обчислювальних блоків та третього спін-хвильового порогового блока. При цьому перший і другий входи двійкового суматора з'єднані паралельно з першим та другим входами, відповідно, першого обчислювального блока та третього порогового блока, а третій вхід двійкового суматора з'єднаний з першим входом другого обчислювального блока і третім входом третього порогового блока, відповідно, вихід якого є виходом розряду переносу двійкового суматора. При цьому вихід першого обчислювального блока з'єднаний з другим входом другого обчислювального блока, вихід якого є виходом розряду суми двійкового суматора. Спільними ознаками запропонованого двійкового суматора з прототипом є перший та другий обчислювальні блоки, причому перший та другий входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока, вихід якого з'єднано з першим входом другого обчислювального блока, другий вхід якого з'єднано з третім входом двійкового суматора, а вихід другого обчислювального блока з'єднано з першим виходом двійкового суматора. 1 UA 107131 C2 5 10 15 20 25 30 35 40 45 50 55 60 Причиною, що заважає вирішенню поставленої задачі є те, що не забезпечена можливість кодування негативного числа "-1", що обмежує функціональні можливості двійкового суматора, оскільки не дозволяє на тому ж обладнанні виконувати, крім додавання, операцію віднімання та обмежує зниження споживаної потужності пристроєм. В основу винаходу, що пропонується, поставлена задача створити такий двійковий суматор, в якому забезпечена можливість кодування негативного числа "-1" сигналом змінного струму резонансної частоти з фазою 180°, що дозволяє знизити споживану потужність пристроєм та розширити функціональні можливості так, щоб на тому ж обладнанні виконувалась, як операція додавання, так і віднімання. Вирішення поставленої задачі досягається тим, що до складу двійкового суматора входять перший та другий обчислювальні блоки, аналоговий суматор та перший та другий інвертори, причому перший та другий входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока, перший вихід якого з'єднано з першим входом другого обчислювального блока, другий вхід якого з'єднано з третім входом двійкового суматора, а перший вихід другого обчислювального блока з'єднано з першим виходом двійкового суматора, перший та другий входи аналогового суматора з'єднано відповідно з другими виходами першого та другого обчислювальних блоків, а вихід аналогового суматора з'єднано з другим виходом двійкового суматора, а також з'єднано з входом першого інвертора, вихід якого з'єднано з третім виходом двійкового суматора, причому четвертий вихід двійкового суматора з'єднано з виходом другого інвертора, вхід якого з'єднано з першим виходом другого обчислювального блока та з першим виходом двійкового суматора. При цьому обчислювальний блок складається з першого та другого аналогових суматорів, першого та другого інверторів, першого та другого порогових елементів, першого та другого детекторів та масштабного елемента, причому перший та другий входи з'єднано відповідно з першим та другим входами першого аналогового суматора, а також один із входів обчислювального блока ще додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з першим входом другого аналогового суматора, другий вхід якого з'єднано з іншим входом обчислювального блока та першого аналогового суматора, при цьому вихід другого аналогового суматора з'єднано зі входом першого порогового елемента, вихід якого з'єднано зі входом першого детектора, вихід якого з'єднано з першим входом другого інвертора, вихід якого з'єднано з першим виходом обчислювального блока; при цьому вихід першого аналогового суматора з'єднано з другим входом другого інвертора, зі входом другого порогового елемента та з першим входом масштабного елемента, вихід якого з'єднано з другим виходом обчислювального блока, при цьому вихід другого порогового елемента з'єднано зі входом другого детектора, вихід якого з'єднано з другим входом масштабного елемента. При цьому аналоговий суматор складається з першого та другого резонаторів, входи яких з'єднано відповідно з першим та другим входами аналогового суматора, а їх виходи з'єднано між собою та з входом третього резонатора, вихід якого з'єднано з виходом аналогового суматора. При цьому масштабний елемент складається з резонаторів, при цьому перший та другий входи масштабного елемента з'єднано відповідно з першим та другим входами першого резонатора, вихід якого з'єднано зі входами другого та третього резонаторів, виходи яких з'єднано між собою, а також з виходом масштабного елемента. Відмітними ознаками запропонованого двійкового суматора є: введення кодування числа "1" сигналом змінного струму резонансної частоти з фазою 180° та додаткове введення до його складу аналогового суматора та двох інверторів, причому перший вихід двійкового суматора додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з другим виходом двійкового суматора, перший та другий входи аналогового суматора з'єднано відповідно з другими виходами першого та другого обчислювальних блоків, а вихід аналогового суматора з'єднано з третім виходом двійкового суматора, а також з входом другого інвертора, вихід якого з'єднано з четвертим виходом двійкового суматора. Введення до двійкового суматора нових ознак дозволило поєднати розширення функціональних можливостей пристрою зі зниженням споживаної потужності. На фіг. 1 наведена функціональна схема прототипу. На фіг. 2 наведена функціональна схема двійкового суматора. На фіг. 3 наведена функціональна схема обчислювального блока. На фіг. 4 наведена функціональна схема аналогового суматора, на фіг. 5 - масштабного елемента, на фіг. 6 - інвертора 8 синусоїдальних сигналів, на фіг. 7 - двовходового інвертора 9, порогового елемента та детектора. Двійковий суматор (фіг. 2) складається: з двох обчислювальних блоків 1, 2, двовходового аналогового суматора 3 змінного струму та двох інверторів 4, 5 синусоїдального сигналу. 2 UA 107131 C2 Причому перший X i та другий Y i , входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока 1, перший вихід якого з'єднано з першим входом другого обчислювального блока 2, другий вхід якого з'єднано з третім входом Ci 1 двійкового суматора, 5 а перший вихід другого обчислювального блока 2 є виходом позитивного значення S i сигналу розряду повної суми двійкового суматора та ще з'єднаний зі входом інвертора 4 синусоїдального сигналу, вихід якого є виходом інверсного значення S i сигналу розряду повної суми двійкового суматора. Причому перший та другий входи аналогового суматора 3 з'єднано відповідно з другими виходами першого 1 та другого 2 обчислювальних блоків, а вихід 10 аналогового суматора 3 з'єднано з виходом інверсного значення Ci сигналу розряду переносу двійкового суматора та з входом інвертора 5 синусоїдального сигналу, вихід якого є виходом позитивного значення C i сигналу розряду переносу двійкового суматора. Обчислювальний блок 1, 2 складається (фіг. 3): з двох аналогових суматорів 6, 7, двох інверторів 8, 9 синусоїдальних сигналів, масштабного елемента 10 множення на постійний коефіцієнт k=-1/2, двох порогових елементів 11, 12 та двох детекторів 13, 14. При цьому перший 15 20 X i та другий Y i входи обчислювального блока з'єднано відповідно з першим та другим входами першого аналогового суматора 6, а також один із входів обчислювального блока ще додатково з'єднано зі входом першого інвертора 8 синусоїдальних сигналів, вихід якого з'єднано з першим входом другого аналогового суматора 7, другий вхід якого з'єднано з іншим входом обчислювального блока та першого аналогового суматора 6, при цьому вихід другого аналогового суматора 7 з'єднано зі входом першого порогового елемента 11, вихід якого з'єднано зі входом першого детектора 13, вихід якого з'єднано з першим входом другого 25 інвертора 9 синусоїдального сигналу, вихід якого є виходом сигналу розряду півсуми si обчислювального блока; при цьому вихід першого аналогового суматора 6 з'єднано з другим входом другого інвертора 9 синусоїдального сигналу, зі входом другого порогового елемента 12 та з першим входом масштабного елемента 10, вихід якого з'єднано з виходом сигналу розряду 30 35 40 45 переносу (напівпереносу) c i , обчислювального блока, при цьому вихід другого порогового елемента 12 з'єднано зі входом другого детектора 14, вихід якого з'єднано з другим входом масштабного елемента 10. Аналоговий суматор 6, 7 складається (фіг. 4) з першого та другого резонаторів, входи яких з'єднано відповідно з першим та другим входами аналогового суматора, а їх виходи з'єднано між собою та з входом третього резонатора, вихід якого є виходом аналогового суматора. Знаком J позначені резонатори. Масштабний елемент 10 складається (фіг. 5) з осцилятора та двох резонаторів, при цьому перший та другий входи масштабного елемента з'єднано відповідно з першим та другим входами осцилятора, вихід якого з'єднано зі входами першого та другого резонаторів, виходи ˆ яких з'єднано між собою, а також з виходом масштабного елемента. Знаком J позначений осцилятор. Інвертор 8 синусоїдальних сигналів складається (фіг. 6) з двох послідовно з'єднаних резонаторів, при цьому вхід інвертора з'єднано зі входом першого резонатора, вихід якого з'єднано зі входом другого резонатора, вихід якого є виходом інвертора. Інвертор 9 синусоїдальних сигналів, пороговий елемент 11, 12 та детектор 13, 14 складаються (фіг. 7): з осцилятора та резонатора, при цьому інформаційний вхід елемента з'єднано з відповідним входом осцилятора, а вхід керування елемента з'єднано з відповідним другим входом осцилятора, вихід якого з'єднано зі входом резонатора, вихід якого є виходом елемента. Робота двійкового суматора (фіг. 2) здійснюється наступним чином. На фіг. 2 X i , Y i , C i , S i - комплексні значення напруги змінного (синусоїдального) струму. При синхронному надходженні на входи двійкового суматора двох синусоїдальних сигналів з амплітудами напруги X i і Y i , що відповідають значенням двох двійкових і-х розрядів доданків, в 3 UA 107131 C2 обчислювальному блоці 1 спочатку здійснюється обчислення значення розряду суми лише двох розрядів (півсуми) та розряду переносу (напівпереносу). Потім синусоїдальний сигнал з 5 амплітудою, що відповідає значенню розряду переносу Ci 1 з молодшого (i-1) розряду надходить на перший вхід другого обчислювального блока 2, на другий вхід якого з першого виходу обчислювального блока 1 синхронно надходить щойно одержаний синусоїдальний сигнал з амплітудою, що відповідає значенню розряду суми двох розрядів (півсуми). В результаті, на першому виході обчислювального блока 2 появиться синусоїдальний сигнал з амплітудою, що відповідає значенню і-го розряду повної суми S i трьох розрядів двійкового суматора. Додатково, сигнал з першого виходу обчислювального блока 2 надійде на вхід 10 15 інвертора 5, після чого сигнал інверсного значення S i і-го розряду повної суми появиться на виході інвертора 4 і на другому виході двійкового суматора. Одночасно з тим, сигнал напівпереносу з другого виходу обчислювального блока 1 надійде на перший вхід аналогового суматора 3, на другий вхід якого синхронно надійде сигнал напівпереносу з другого виходу обчислювального блока 2. В результаті аналогового підсумовування амплітуд напруги вхідних сигналів, на виході аналогового суматора 3 буде одержано синусоїдальний сигнал з амплітудою, що відповідає інверсному значенню C i розряду переносу при двійковому додаванні трьох розрядів, на третьому виході двійкового суматора. Далі, після проходження щойно одержаного сигналу з виходу аналогового суматора 3 20 через інвертор 5, синусоїдальний сигнал з амплітудою, що відповідає позитивному значенню C i розряду переносу появиться на виході інвертора 5 і на четвертому виході двійкового суматора. Для здійснення операції віднімання кодів необхідно значення розряду від'ємника подавати у вигляді інверсної (по відношенню до того з якого віднімають) напруги змінного струму на один з входів X i або, Y i , відповідно. Робота обчислювального блока 1, 2 (фіг. 3) здійснюється таким чином. При синхронному 25 30 надходженні на входи пристрою двох синусоїдальних сигналів з амплітудами напруги X i і Y i , що відповідають значенням двох двійкових розрядів доданків, в аналоговому суматорі 6 здійснюється аналогове підсумовування амплітуд напруги цих сигналів і сигнал результату підсумовування надійде на входи трьох елементів: інвертора синусоїдальних сигналів 9, масштабного елемента 10 та порогового елемента 12. У разі Xi Y i 1 , коли значення амплітуди напруги сигналу результату аналогового підсумовування на виході аналогового суматора 6 помітно перевищить рівень значення напруги, що відповідає значенню логічної одиниці, спрацьовує пороговий елемент 12. В результаті цього, високий потенціал з виходу детектора 14 дозволяє проходження синусоїдального сигналу з виходу аналогового суматора 6 через масштабний елемент 10 (з 35 1 множенням на коефіцієнт k=-( /2), на вихід розряду переносу (напівпереносу) C i обчислювального блока (півсуматора). При цьому на виході аналогового суматора 7 відсутній вихідний сигнал, оскільки Xi Y i 0 . 40 У всіх інших випадках, за винятком двох нульових значень вхідних сигналів, синусоїдальний сигнал з виходу другого аналогового суматора 7 надходить на вхід порогового елемента 11, поріг спрацьовування якого, наприклад, більше лише половини рівня напруги, що відповідає значенню логічної одиниці. При спрацьовуванні порогового елемента 11, високий потенціал з виходу детектора 13 дозволяє проходження синусоїдального сигналу з виходу аналогового 45 суматора 6 через інвертор 9 на вихід розряду суми (півсуми) S i обчислювального блока (півсуматора). Результати роботи обчислювального блока 1, 2 (фіг. 3) наведено в таблиці. Розглянемо далі докладно роботу кожного з елементів схеми, наведеної на фіг. 3 наступним чином. 4 UA 107131 C2 5 10 15 ˆ На фіг. 8 наведено схематичне зображення можливого виду осцилятора J (резонатора J ) (див. обведене пунктиром) [запозичене з патентів US 2005/6946693 В1, WO 2005/109520 А2, US 2007/7214571 В2; Dominik V. Scheible, Robert H. Blick. Electromechanical electron transfer devices]. Осцилятор складається з вібратора 33, розташованого між електродами 25 (S) та 26 (D), через які подається напруга постійного та/або змінного струму. При необхідності в осцилятор може бути добавлений третій електрод 27 (G) для керування роботою осцилятора. Інший вид осцилятора (резонатора) може бути реалізовано на основі нанотрубок [Jeffrey A. Weldon, Benjamin Alema'n, Allen Sussman, William Gannett, and Alex K. Zettl. Sustained Mechanical SelfOscillations in Carbon Nanotubes. Nano Lett. 2010, 10, 1728-1733]. Можуть бути й інші варіанти. Зважаючи на те, що коливання в наноелектромеханічному осциляторі (див. обведене пунктиром на фіг. 8) є результатом періодичного переходу потенціальної енергії електричного поля в кінетичну енергію механічного вібратора, з його моментом інерції та пружністю (еластичністю), можна представити електричну модель осцилятора (резонатора) в першому (лінійному) наближенні в вигляді, як це наведено на фіг. 9. На фіг. 10 наведена електрична модель інвертора синусоїдального сигналу 8 [Юффлер Г.Ж. Новый тип универсальной вычислительной машины. Труды ИФАК (IFАС) том 3, издательство АН СССР, М. 1962 г.]. Амплітуда сигналу вихідної напруги моделі інвертора визначається за формулою 20 V 2 L 2 / L1 V1 , а при умові, що L1 L2 , одержимо V 2 V1. На фіг. 11 наведена електрична модель аналогового суматора 6, 7 двох синусоїдальних сигналів [Юффлер Г.Ж. Новый тип универсальной вычислительной машины. Труды ИФАК (IFAC) том 3, издательство АН СССР, М. 1962 г.]. Згідно з першим законом Кірхгофа V1/ L1 V 2 / L 2 V 3 / L 3 0 , і при умові, що L1=L2=L3, одержимо V 3 V 1 V 2 . 25 30 35 40 45 У випадку, коли V1 V 2 V , можна з'єднати відповідні клеми на фіг. 11 і отримати в результаті масштабний елемент 10 для множення на постійний коефіцієнт k=2), у відповідності з виразом V 1/ 2 V 3 (при зворотному включенні), за умови, що L1=L2=L3 (див. елемент 10 на фіг. 5). Робота порогових елементів 11, 12 (фіг. 3) пояснюється безпосередньо властивостями (характеристиками) наномеханічних осциляторів в різних режимах, що описано, наприклад, у статтях [Jeffrey A. Weldon, Benjamin Alema'n, Allen Sussman, William Gannett, and Alex K. Zettl. Sustained Mechanical Self-Oscillations in Carbon Nanotubes. Nano Lett. 2010, 10, 1728-1733.] та [Heun S. Kim, Hua Qin and Robert H. Blick. Self excitation of nanomechanical pillar, New J Phys, 12 (2010) 033008.]. При цьому величина порогу встановлюється, наприклад, за допомогою подачі відповідного значення напруги постійного струму на вхід керування (фіг. 7). Робота детекторів 13, 14 (фіг. 3) може здійснюватися одним із відомих способів. Наприклад, способом однопівперіодного детектування при синхронній одночасній подачі синусоїдального сигналу на обидва входи: інформаційний та вхід керування (фіг. 7). Можна здійснювати двопівперіодне детектування, використовуючи нелінійність вольт-амперної характеристики осцилятора, вибравши відповідну робочу точку за допомогою входу керування, що описано, наприклад, в п. 0054 опису патенту [US 2010/0271003 А1. Zettl at all. Nanotube resonator devices]. Відзначимо те, що, залежно від обставин, керування в елементах 9 і 10 (фіг. 3) може здійснюватися двояко. Або просто шляхом подачі напруги постійного струму на один із двох входів осцилятора (див. V на фіг. 8), при неперервній присутності на другому вході резонатора напруги змінного струму Vac. Або, як варіант, для керування може бути використаний і окремий електрод, наприклад, електрод G (27), як показано на фіг. 8 [патенти US 2005/6946693 В1, WO 2005/109520 А2, US 2007/7214571 В2; Dominik V. Scheible, Robert H. Blick. Electromechanical electron transfer devices]. Таким чином, наведене вище свідчить про можливість реалізації двійкового суматора на основі наноелектромеханічних та інших елементів. 50 5 UA 107131 C2 Таблиця Варіант Вхід Х Вхід Y 1 2 3 4 5 6 7 8 9 0 1 0 1 -1 0 1 -1 -1 0 0 1 1 0 -1 -1 1 -1 Cуматор 6 Cуматор 7 0 -1 -1 -2 1 1 0 0 2 0 -1 1 0 1 -1 -2 2 0 Детектор 13 0 1 1 0 1 1 1 1 0 Детектор 14 0 0 0 1 0 0 0 0 1 Вихід S Вихід C 0 1 1 0 -1 -1 0 0 0 0 0 0 1 0 0 0 0 -1 ФОРМУЛА ВИНАХОДУ 5 10 15 20 25 30 35 1. Двійковий суматор, до складу якого входять перший та другий обчислювальні блоки, причому перший та другий входи двійкового суматора з'єднано з відповідними входами першого обчислювального блока, вихід якого з'єднано з першим входом другого обчислювального блока, другий вхід якого з'єднано з третім входом двійкового суматора, а вихід другого обчислювального блока з'єднано з першим виходом двійкового суматора, який відрізняється тим, що додатково введено аналоговий суматор та два інвертори, причому перший вихід двійкового суматора додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з другим виходом двійкового суматора, перший та другий входи аналогового суматора з'єднано відповідно з другими виходами першого та другого обчислювальних блоків, а вихід аналогового суматора з'єднано з третім виходом двійкового суматора, а також з входом другого інвертора, вихід якого з'єднано з четвертим виходом двійкового суматора. 2. Двійковий суматор за п. 1, який відрізняється тим, що обчислювальний блок складається з першого та другого аналогових суматорів, першого та другого інверторів, першого та другого порогових елементів, першого та другого детекторів та масштабного елемента, причому перший та другий входи обчислювального блока з'єднано відповідно з першим та другим входами першого аналогового суматора, а також один із входів обчислювального блока додатково з'єднано зі входом першого інвертора, вихід якого з'єднано з першим входом другого аналогового суматора, другий вхід якого з'єднано з іншим входом обчислювального блока та першого аналогового суматора, при цьому вихід другого аналогового суматора з'єднано зі входом першого порогового елемента, вихід якого з'єднано зі входом першого детектора, вихід якого з'єднано з першим входом другого інвертора, вихід якого з'єднано з першим виходом обчислювального блока, при цьому вихід першого аналогового суматора з'єднано з другим входом другого інвертора, зі входом другого порогового елемента та з першим входом масштабного елемента, вихід якого з'єднано з другим виходом обчислювального блока, при цьому вихід другого порогового елемента з'єднано зі входом другого детектора, вихід якого з'єднано з другим входом масштабного елемента. 3. Двійковий суматор за п. 2, який відрізняється тим, що аналоговий суматор складається з резонаторів, де входи першого та другого резонаторів з'єднано відповідно з першим та другим входами аналогового суматора, а їх виходи з'єднано між собою та з входом третього резонатора, вихід якого з'єднано з виходом аналогового суматора. 4. Двійковий суматор за п. 2, який відрізняється тим, що масштабний елемент складається з осцилятора та двох резонаторів, при цьому перший та другий входи масштабного елемента з'єднано відповідно з першим та другим входами осцилятора, вихід якого з'єднано зі входами першого та другого резонаторів, виходи яких з'єднано з виходом масштабного елемента. 6 UA 107131 C2 7 UA 107131 C2 8 UA 107131 C2 9 UA 107131 C2 Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 10

ДивитисяДодаткова інформація

Автори англійськоюPalahin Oleksandr Vasyliiovych, Boiun Vitalii Petrovych

Автори російськоюПалагин Александр Васильевич, Боюн Виталий Петрович

МПК / Мітки

МПК: G06J 1/00, H03H 9/00, G06F 7/502

Код посилання

<a href="https://ua.patents.su/12-107131-dvijjkovijj-sumator.html" target="_blank" rel="follow" title="База патентів України">Двійковий суматор</a>

Попередній патент: Спосіб двійкового додавання/віднімання

Наступний патент: Газогенератор вологої біомаси

Випадковий патент: Спосіб одержання диспергованого швидкозагартованого сплаву