Багаторозрядний суматор

Текст

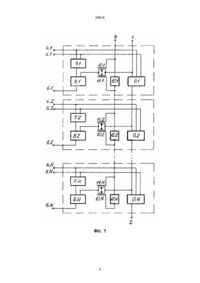

Багаторозрядний суматор, який має вхід і вихід переносу, а в кожному розряді містить входи розрядів першого і другого операндів, вихід розряду суми, перший і другий елементи додавання по модулю два і вузол формування переносу, при цьому в кожному розряді перший вхід першого елементу додавання по модулю два під'єднаний до входу першого операнда вузла формування переносу і одночасно є входом розряду першого операнда, другий вхід першого елементу додавання по модулю два з'єднаний зі входом другого операнда вузла формування переносу і одночасно є входом розряду другого операнда, вихід першого елементу додавання по модулю два з'єднаний з першим входом другого елементу додавання по модулю два, вихід якого є виходом розряду суми, вхід переносу вузла формування переносу першо A (54) БАГАТОРОЗРЯДНИЙ СУМАТОР 29616 льский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справ очник. - М.: Радио и связь, 1990. С. 132, рис. 3.44а; с. 133, рис. 3.45). В відомому багаторозрядному суматорі в кожному розряді другий вхід другого елемента додавання по модулю два під'єднаний до входу переносу вузла формування переносу. Внаслідок цього, розповсюдження сигналу переносу відбувається одночасно з формуванням вихідного значення суми. Причому вихідний струм вузла формування переносу кожного розряду використовується для одночасного заряду в наступному розряді вхідних ємностей входу переносу вузла формування переносу і другого входу другого елемента додавання по модулю два, що збільшує тривалість перехідного процесу на даному виході та зменшує швидкість розповсюдження сигналу переносу і, відповідно, швидкодію багаторозрядного суматора. Загальний час додавання T2 відомого пристрою становить: T2 = (N - 1) × (t 2 + t Ф ) + t 2 + max{t Ф , t Д } , (1) де: N - розрядність суматора; tФ - затримка спрацювання вузла формування переносу; tД – затримка спрацювання елемента додавання по модулю два; t2 - тривалість перехідних процесів на вході вузла, формування переносу. Останній операнд в формулі (1) відповідає умові спрацювання останнього N-ого повного однорозрядного суматора, час його спрацювання відносно значення вхідного переносу рівний більшій величині з tФ, tД. Як правило, затримка спрацювання вузла формування перекосу tФ менше, ніж затримка спрацювання елемента додавання по модулю два tД. В основу винаходу поставлене завдання створити багаторозрядний суматор, в якому нові елементи і відповідні взаємозв'язки дозволили б зменшити тривалість перехідних процесів на виході вузла формування переносу при розповсюдженні сигналу переносу між розрядами шляхом розділення в часі процесів формування вихідного значення суми в біжучому розряді і генерації переносу в наступний розряд і, за рахунок цього, збільшити швидкодію багаторозрядного суматора. Поставлене завдання досягається за рахунок того, що багаторозрядний суматор, який має вхід і вихід переносу, а в кожному розряді містить входи розрядів першого та другого операндів, вихід розряду суми, перший та другий елементи додавання по модулю два і вузол формування переносу, при цьому в кожному розряді перший вхід першого елемента додавання по модулю два під'єднаний до входу першого операнда вузла формування переносу і одночасно є входом розряду першого операнда, другий вхід першого елемента додавання по модулю два з'єднаний зі входом другого операнда вузла формування переносу і одночасно є входом розряду другого операнда, вихід першого елемента додавання по модулю два з'єднаний з першим входом другого елемента додавання по модулю два, вихід якого є виходом розряду суми, вхід переносу вузла формування переносу першого розряду одночасно є входом переносу багаторозрядного суматора, вхід переносу вузла формування переносу кожного, крім першого, розряду з'єднаний з виходом вузла формування переносу попереднього розряду, вихід вузла формування перекосу останнього розряду одночасно є виходом переносу багаторозрядного суматора, згідно винаходу, додатково має вхід строба заборони додавання і в кожному розряді містить рМОН транзиттор, nМОН транзистор і інвертор, при цьому в кожному розряді витоки р- і nМОН транзисторів з'єднані між собою і під'єднані до входу переносу вузла формування переносу, їх стоки також з'єднані між собою і під'єднані до другого входу другого елемента додавання по модулю два, а в кожному непарному розряді, починаючи з першого, затвор рМОН транзистора з'єднаний зі входом інвертора, затвор nМОН транзистора - з виходом інвертора, в кожному парному розряді затвор nМОН транзистора з'єднаний зі входом інвертора, затвор рМОН транзистора - з виходом інвертора, вхід інвертора першого розряду одночасно є входом строба за борони додавання, вхід інвертора кожного, крім першого, розряду з'єднаний з виходом інвертора попереднього розряду. Введення в кожний розряд багаторозрядного суматора рМОН транзистора, nМОН транзистора, інвертора і відповідних взаємозв'язків збільшує швидкість розповсюдження сигналу переносу і, відповідно, швидкодію багаторозрядного суматора за рахунок розділення в часі процесів утворення вихідного значення суми в біжучому розряді та генерації переносу в наступний розряд. На фіг. 1 представлена принципова схема багаторозрядного суматора; на фіг. 2 приведені часові діаграми функціонування багаторозрядного суматора. Багаторозрядний суматор має вхід 1 і вихід 2 переносу, вхід строба заборони додавання 3, а в кожному і-ому розряді, де і=1, ..., N, N - розрядність суматора, містить входи розрядів першого 4і та другого 5і операндів, вихід розряду суми 6і, перший 7і і другий 8і елементи додавання по модулю два, вузол формування переносу 9і, рМОН транзистор 10і, nМОН транзистор 11і і інвертор 12і, причому вхід переносу вузла формування переносу 9.1 першого розряда одночасно є входом переносу 1 багаторозрядного суматора, вхід переноса вузла формування переносу 9і кожного і-ого, крім першого, розряду під'єднаний до виходу переносу вузла формування переносу 9і-1 попереднього (і-1)-ого розряду, вихід переносу вузла формування переносу 9.N останнього розряду одночасно є виходом переносу 2 багаторозрядного суматора, вхід інвертора 10.1 першого розряду одночасно є входом строба розповсюдження переносу 3, вхід інвертора 10і кожного 1-ого, крім першого, розряду під'єднаний до виходу інвертора 10і-1 попереднього (і-1)-ого розряду, в кожному і-ому розряді перший вхід першого елемента додавання по модулю два 7і з'єднаний зі входом першого операнда вузла формування переносу 9і і одночасно є входом розряду першого операнда 4і, другий вхід першого елемента додавання по модулю два 7і з'єднаний зі входом другого операнда вузла формування переносу 9і і одночасно є входом розряду другого операнда 5і, вихід першого елемента додавання по модулю два 7і під'єднаний до першого входу другого елемента додавання по модулю два 3і, вихід якого одночасно є виходом розряду суми 6і, стоки р- і nМОН транзисторів 10і і 11і об'єднані між 2 29616 собою і під'єднані до другого входу другого елемента додавання по модулю два 8і, витоки р- і nMOH транзисторів 10і і 11і також об'єднані між собою і під'єднані до входу переносу вузла формування переносу 9і, в кожному (2j-1)-ому непарному розряді, де j=1, ..., N/2, затвор рМОН транзистора 102j-1 з'єднаний зі входом інвертора 122j-1, а затвор nMOH транзистора 112j-1 - з виходом інвертора 122j-1, в кожному (2j)-ому парному розряді затвор nMOH транзистора 112j з'єднаний зі входом інвертора 122j, а затвор рМОН транзистора 122j - з виходом інвертора 122j. При описі функціонування багаторозрядного суматора вважається, що початковий перенос зі входу переносу 1 послідовно розповсюджується через всі розряди до виходу переносу 2 (можливий випадок, по якому необхідно розраховувати швидкодію багаторозрядного суматора). По додатному фронту біжучого тактового імпульсу на вхід строба заборони додавання 3 подається сигнал високого рівня, який поступає в першому розряді на затвор рМОН транзистора 10.1 і на вхід інвертора 12.1 (фіг. 2 А), з виходу якого на затвор nMOH транзистора 11.1 подається низький потенціал (фіг. 2 С). При цьому р- і nMOH транзистори 10.1 і 11.1 закриваються і від'єднують вхід переносу вузла формування переносу 9.1 від другого входу другого елемента додавання по модулю два 8.1. Одночасно на вхід переносу 1 і на входи розрядів першого 4і і другого 5і операндів подаються біжучі значення початкового переносу і доданків (фіг. 2 В), які поступають на входи відповідних перших елементів додавання по модулю два 7і і вузлів формування переносу 9і. Струм джерела сигналу початкового переносу використовується тільки для заряду вхідної ємності входу переносу вузла формування переносу першого розряду 9.1. Низький потенціал з виходу інвертора 12.1 поступає в другому розряді на затвор nMOH транзистора 11.2 і на вхід інвертора 12.2 (фіг. 2 С), з виходу якого на затвор рМОН транзистора 10.2 подається високий потенціал (фіг. 2 Е). Внаслідок цього, р- і nMOH транзистори 10.2 і 11.2 також закриваються і від'єднують вхід переносу вузла формування переносу 9.2 від другого входу другого елемента додавання по модулю два 8.2. Затримка tФ спрацювання вузла формування переносу 9.1 більше, ніж час tСТ формування на затворах р- і nMOH транзисторів 10.2 і 11.2 потенціалів, які закривають дані транзистори. Тому, при утворенні істинного сигналу переносу (фіг. 2 D), струм виходу переносу вузла формування переносу 9.1 використовується тільки для заряду вхідної ємності входу перекосу наступного вузла формування пере носу 9.2. Строб заборони додавання і сигнал переносу розповсюджуються між непарними і парними розрядами в напрямку останнього N-ого розряду багаторозрядного суматора (фіг. 2 F, G, Н) аналогічно, як і між описаними, відповідно, першим і другим розрядами. В кожному і-ому розряді при цьому, струм виходу переносу вузла формування переносу 9і в наступному (і+1)-ому розряді завжди використовується тільки для заряду вхідної ємності входу переносу вузла формування переносу 9і+1. Через час ТСТ на вході строба заборони додавання 3 високий рівень сигналу змінюється на низький (фіг. 2 А). Низький потенціал поступає в пер шому розряді на затвор рМОН транзистора 10.1 і на вхід інвертора 12.1 (фіг. 2А), з виходу якого на затвор nMOH транзистора 11.1 подається високий потенціал (фіг. 2С). При цьому р- і nMOH транзистори 10.1 і 11.1 відкриваються і з'єднують вхід переносу вузла формування переносу 9.1 з другим входом другого елемента додавання по модулю 8.1. З затримкою tД', на виході другого елемента додавання по модулю два 8.1 зформується вихідне значення суми, яке поступає на вихід розряда суми 6.1 (фіг. 2І), причому: t Д ' = t1 ' + t Д , (2) де: t1' - тривалість заряду вхідної ємності другого входу другого елемента додавання по модулю два. Високий потенціал з виходу інвертора 12.1 поступає в другому розряді (фіг. 2С) на затвор nMOH транзистора 11.2 і на вхід інвертора 12.2. з виходу якого на затвор рМОН транзистора 10.2 подається низький потенціал (фіг. 2Е). При цьому р- і nMOH транзистори 10.2 і 11.2 також відкриваються і з'єднують вхід переносу вузла формування переносу 9.2 з другим входом другого елемента додавання по модулю два 8.2, на виході якого сформуються значення другого розряду суми (фіг. 2J). Процес формування значень розрядів суми розповсюджується між розрядами багаторозрядного суматора зі швидкістю tСТ в напрямку останнього N-ого розряду (фіг. 2К). Для спрощення розрахунку швидкодії пропонованого багаторозрядного суматора приймемо, що в кожному і-ому розряді вхідні ємності другого входу елемента додавання по модулю два 8і і вузла формування переносу 9і однакові між собою, а також, що, якщо р- і nMOH транзистори 10і і 11і закриті, то їх об'єднані витоки мають безмежний вхідний опір і не мають вхідної паразитної ємності. В такому випадку, паразитна ємність виходу біжучого вузла формування переносу і, відповідно, тривалість перехідних процесів на цьому виході при розповсюдженні сигналу перекосу зменшуються в два рази, тобто: t 2 = 2 × t1 , (3) де: t1 - тривалість перехідних процесів на вході вузлів формування переноса в пропонованому багаторозрядному суматорі. Максимальна тривалість строба заборони додавання ТСТ вибирається такою, щоб формування значення останнього N-ого розряду суми закінчилось на протязі біжучого періоду тактових імпульсів Т: N × t CT + TCT + t Д ' £ T , (4) звідки: max TCT = T - N × t CT - t Д ' . (5) Найбільш ефективно функціонує багаторозрядний суматор, в якому в (N-1)-розряді формування переносу в наступний N-ний розряд і виконання другого додавання по модулю два з даному розряді-ще виконуються послідовно в часі, а в останньому N-ому вже можуть відбуватися одночасно. Тому мінімальна тривалість строба заборони додавання ТСТ обмежується умовою роздільного формування вихідного переносу і значення суми в передостанньому (N-1)-ому розряді: (N - 1) × t CT + TCT ³ (N - 1) × (t1 + t Ф ) , (6) 3 29616 звідки: значно менше, ніж тривалість перехідних процесів на виході переносу t1, тобто: t Ф

ДивитисяДодаткова інформація

Назва патенту англійськоюMulti-bit adder

Автори англійськоюPankov Ruslan Stepanovych

Назва патенту російськоюМногоразрядный сумматор

Автори російськоюПаньков Руслан Степанович

МПК / Мітки

МПК: G06F 7/503, G06F 7/48

Мітки: багаторозрядний, суматор

Код посилання

<a href="https://ua.patents.su/7-29616-bagatorozryadnijj-sumator.html" target="_blank" rel="follow" title="База патентів України">Багаторозрядний суматор</a>

Попередній патент: Ротативний двигун “зоря”

Наступний патент: Спосіб одержання протимікробного фітозасобу з інтерфероніндукуючою активністю

Випадковий патент: Відстоювач