Адаптер канал-канал

Номер патенту: 15863

Опубліковано: 30.06.1997

Формула / Реферат

1. Адаптер канал-канал, содержащий буферный регистр, блок заданиярежима и два блока связи с каналом, первый из которых содержит узел согласования входных сигналов, регистр адреса, регистр команд, узел памяти кодов совпадения адресов, дешифратор команд и блок микропрограммного управления, регистр байта состояния и узел согласования выходных сигналов, выход которого является выходом адаптера для подключения к информационному входу первого абонента, вход узла согласования входных сигналов является входом адаптера для подключения к информационному выходу первого канала, выход узла согласования входных сигналов подключен к первому адресному входу узла памяти кодов совпадения адресов, к первому информационному входу узла выходных сигналов и информационному входу регистра команд, выход которого через дешифратор команд подключен к первому входу логического условия блока микропрограммного управления первого блока связи с каналом, первый выход поля управления которого подключен к входу управления узла согласования выходных сигналов, вторым информационным входом подключенный через регистр байт а к второму выходу поля управления блока микропрограммного управления первого блока связи с каналом второй вход логического условия и третий выход поля управления которого подсоединены к выходу и входу разрешения узла памяти кодов совпадения адресов соответственно, четвертый выход поля управления блока микропрограммного управления первого блока связи с каналом соединен с входом разрешения буферного регистра, пятый выход поля управления блока микропрограммного управления первого блока связи с каналом является выходом адаптера для подключения к входу управления первого абонента, шестой выход поля управления блока микропрограммного управления первого блока связи с каналом соединен с синхровходом регистра команд третий вход логического условия блока микропрограммного управления первого блока связи с каналом является входом адаптера для подключения к выходу управления первого канала, второй адресный вход узла памяти кодов совпадения адреса соединен с выходом регистра адреса, первый и второй выходы блока задания режима работы соединены с входами режимов работы блока микропрограммного управления первого блока связи с каналом и второго блока связи с каналом, вход режима работы которого соединен с входом режима работы блока микропрограммного управления второго блока связи с каналом, содержащим также узел согласования входных сигналов, узел согласования выходных сигналов, причем вход узла согласования входных сигналов второго блока связи с каналом является входом адаптера для подключения к выходу информации второго канала, выход узла согласования входных сигналов второго блока связи с каналом соединен с первым информационным входом буферного регистра, синхровход которого соединен с первым выходом поля управления блока микропрограммного управления второго блока согласования, первый вход логического условия которого соединен с входом адаптера для подключения к выходу управления второго канала, второй выход поля управления блока микропрограммного управления второго блока связи с каналом соединен с управляющим входом узла согласования выходных сигналов второго блока связи с каналом, выход которого является выходом адаптера для подключения к информационному входу второго абонента, третий выход поля управления узла микропрограммного управления второго блока связи с каналом является выходом адаптера для подключения к входу управления второго абонента, первый информационный вход узла согласования выходных сигналов второго блока связи с каналом соединен с выходом буферного регистра, отличающийся тем, что в адаптер введены буферная память и память состояния, а второй блок связи с каналом содержит дешифратор адреса, причем первый информационный вход памяти состояний соединен с выходом буферного регистра и третьим информационным входом узла согласования выходных сигналов первого блока связи с каналом, второй информационный вход памяти состояний соединен с выходом узла согласования входных сигналов, с информационным входом дешифратора адреса второго блока связи с каналом, вторым информационным входом буферного регистра, первым информационным входом буферной памяти, информационными входами узла памяти кодов совпадения адресов и регистра адреса, третий информационный вход памяти состояния соединен с выходом узла согласования входных сигналов первого блока связи с каналом и с вторым информационным входом буферной памяти, третий информационный вход буферной памяти соединен с выходом памяти состояний, вторым информационным входом узла согласования выходных сигналов второго блоха связи с каналом, четвертым информационным входом узла согласования выходных сигналов первого блока связи с каналом и четвертым входом логического условия узла микропрограммного управления первого блока связи с каналом, вход управления буферной памяти и памяти состояния соединены с четвертым и пятым выходом поля управления узла микропрограммного управления второго блока связи с каналом соответственно, входы разрешения памяти состояний и буферной памяти соединены с седьмым и восьмым выходом поля управления узла микропрограммного управления первого блока связи с каналом соответственно, первый выход буферной памяти соединен с третьим информационным входом узла согласования выходных сигналов второго блока связи с каналом, второй выход буферной памяти соединен с пятым информационным входом узла согласования выходных сигналов первого блока связи с каналом, третий выход буферной памяти соединен с пятым входом логического условия узла микропрограммного управления первого блока связи с каналом, управляющий вход регистра адреса первого блока связи с каналом объединен с управляющим входом узла памяти кодов совпадения адресов и соединен с шестым выходом поля управления узла микропрограммного управления второго блока связи с каналом, седьмой выход поля управления которого соединен с управляющим входом дешифратора адреса второго блока связи с каналом, выход которого соединен с первым адресным входом узла микропрограммного управления второго блока связи с каналом, второй адресный вход которого соединен с девятым выходом поля управления узла микропрограммного управления первого блока связи с каналом, шестой вход логического условия соединен с восьмым выходом поля управления узла микропрограммного управления второго блока связи с каналом.

2. Адаптер по п.1, отличающийся тем, что буферная память содержит два счетчика адреса, коммутатор адреса, коммутатор информации, блок памяти, регистр длины массива, схему сравнения, два выходных регистра, причем выход первого выходного регистра является первым информационным выходом памяти, выход второго выходного регистра - вторым информационным выходом памяти, первый информационный вход первого выходного регистра объединен с первым информационным входом второго выходного регистра и подключен к выходу блока памяти, второй информационный вход первого выходного регистра объединен с первым входом схемы сравнения, первым информационным входом коммутатора адреса и подключен к выходу первого счетчика адреса, информационный вход которого является третьим информационным входом памяти, счетный и синхровход первого счетчика адреса объединены и соединены с первыми управляющими входами коммутатора адреса, коммутатора информации, блока памяти, синхровходом второго выходного регистра и являются входом разрешения памяти, синхровход которой объединен с входами такта и счета второго счетчика адреса, синхровходом регистра длины массива, управляющим входом первого выходного регистра, вторыми управляющими входами коммутатора адреса, коммутатора информации и блока памяти, информационный и адресный входы которого соединены с выходом коммутатора информации и выходом коммутатора адреса соответственно, второй информационный вход которого объединен с информационным входом регистра длины массива и с выходом второго счетчика адреса, информационный вход которого объединен с вторым информационным входом коммутатора информации и является первым информационным входом памяти, выход регистра длины массива соединен с вторым входом схемы сравнения, выход которой является третьим выходом памяти.

Текст

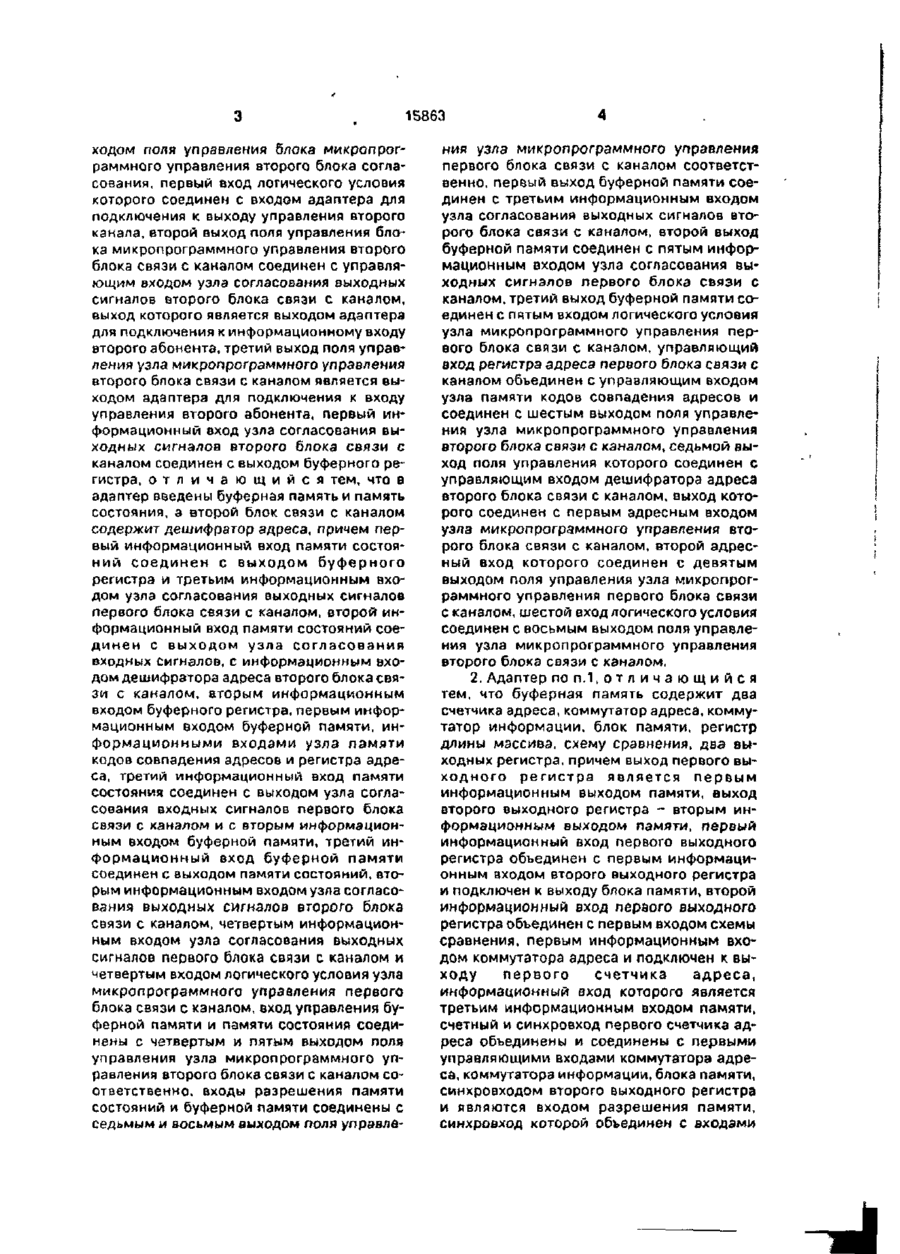

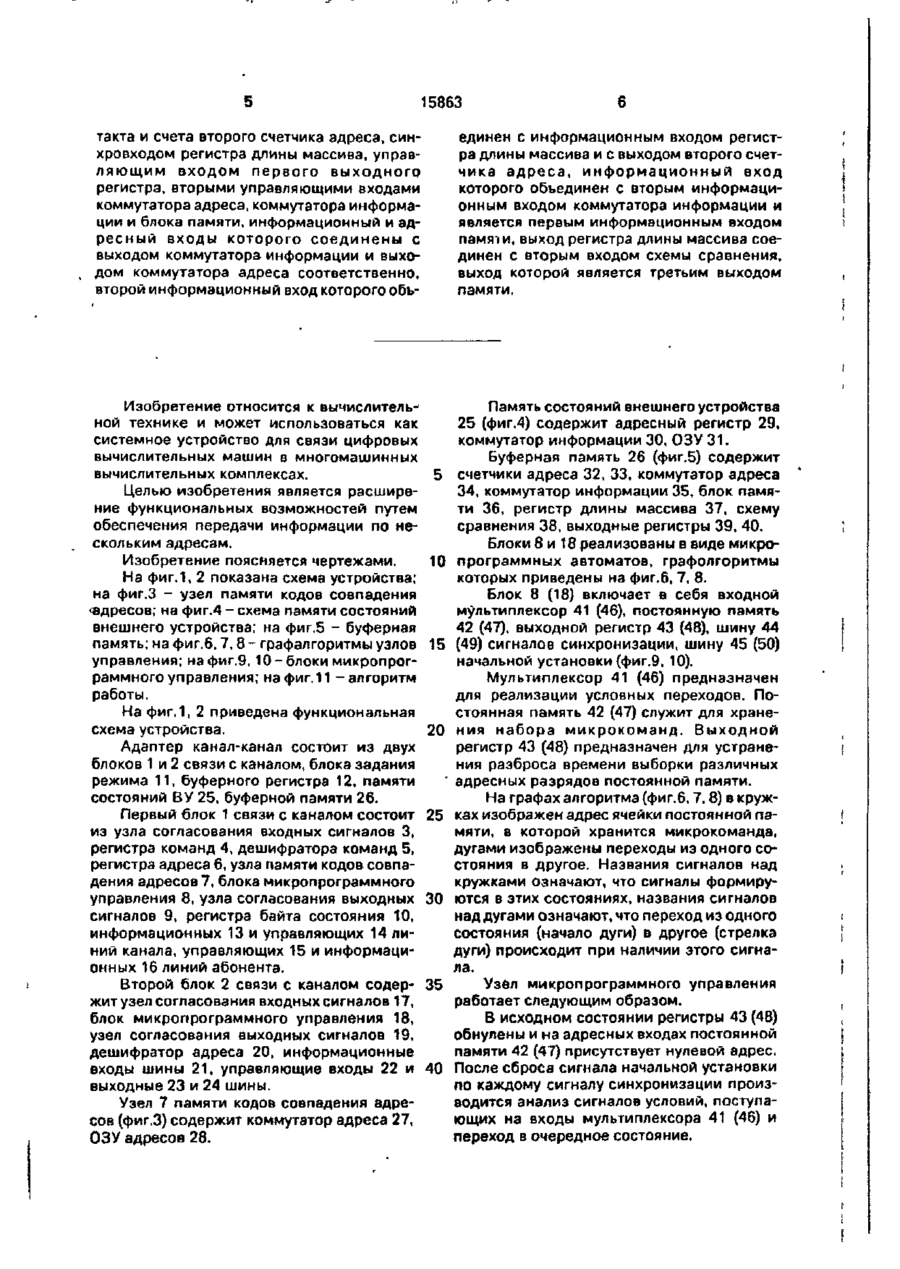

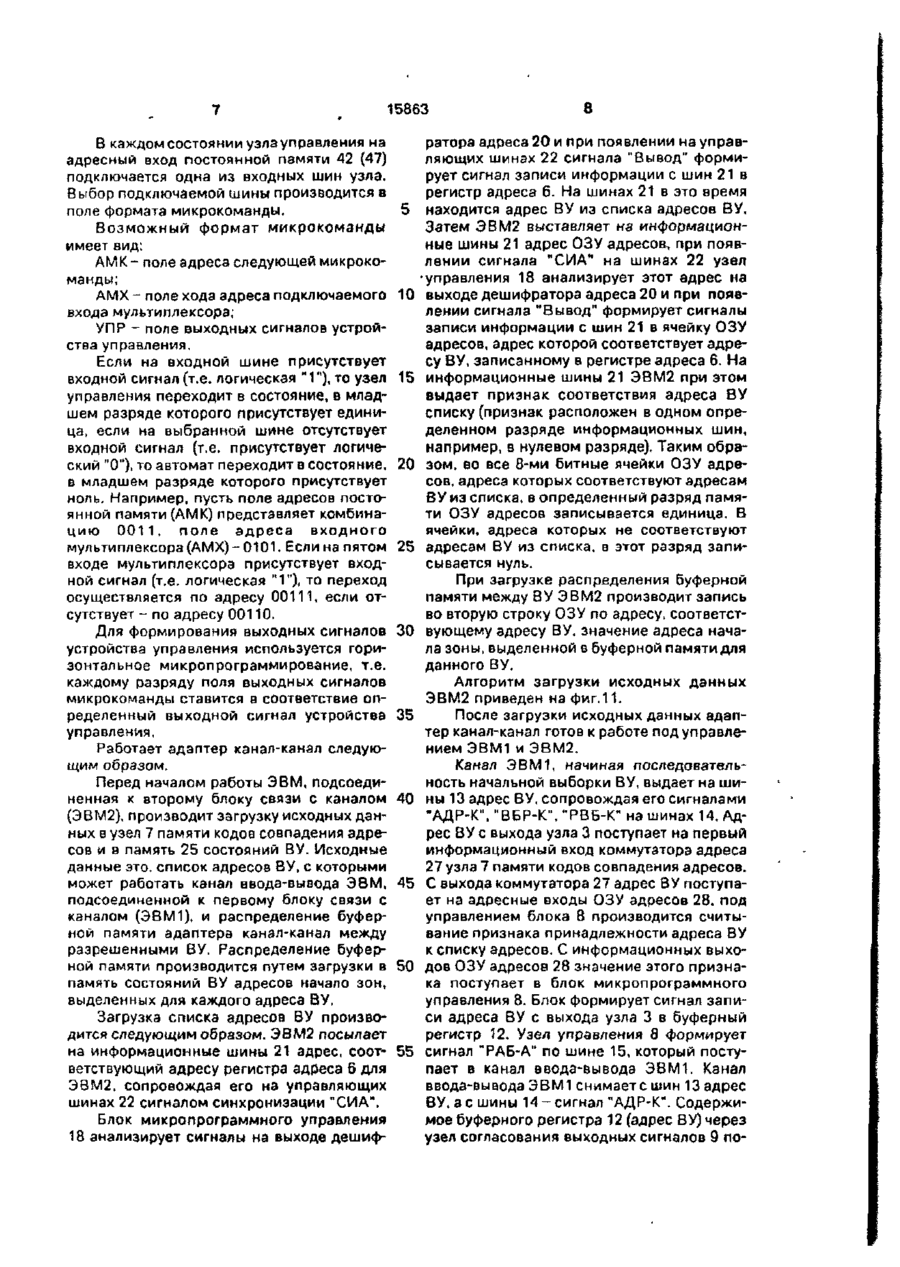

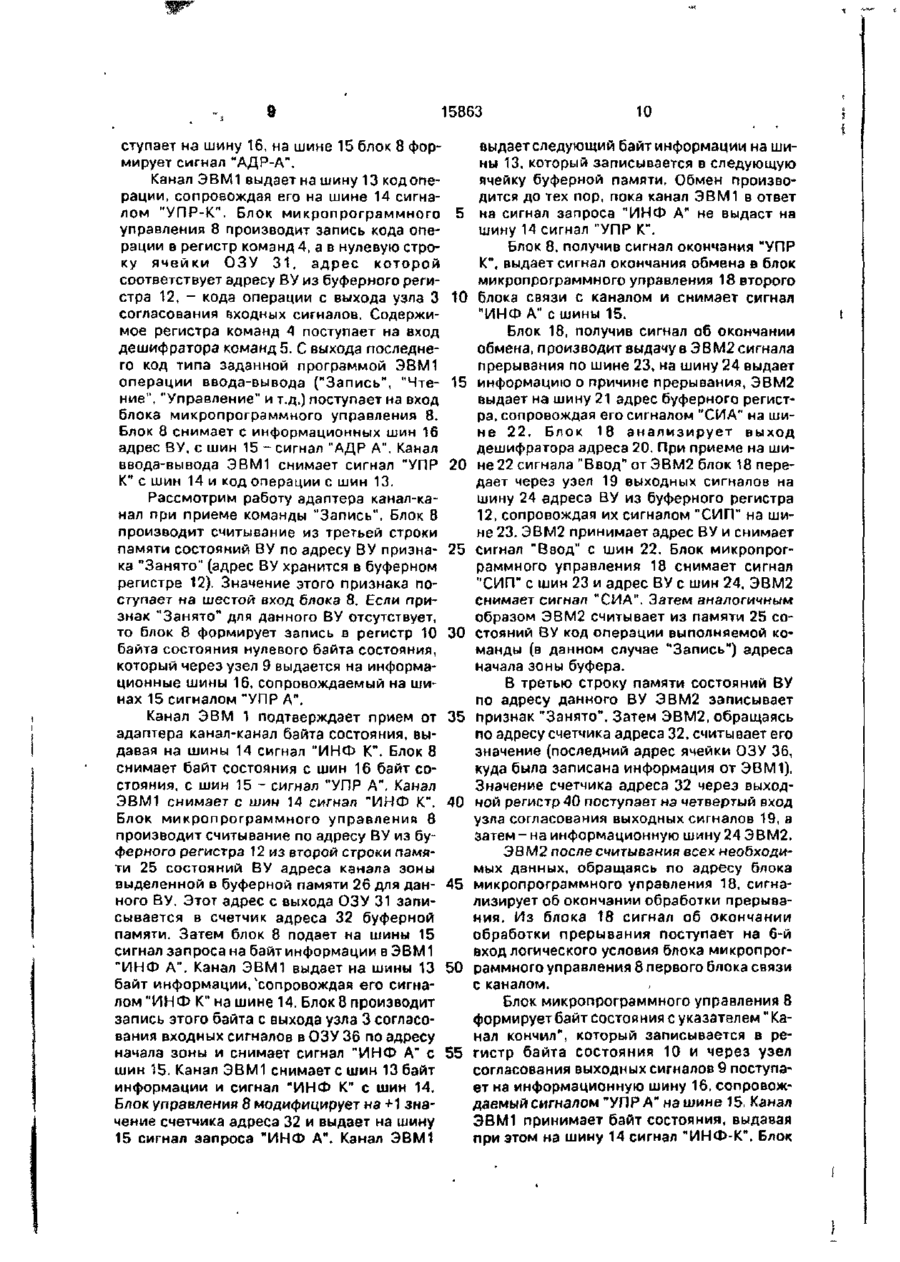

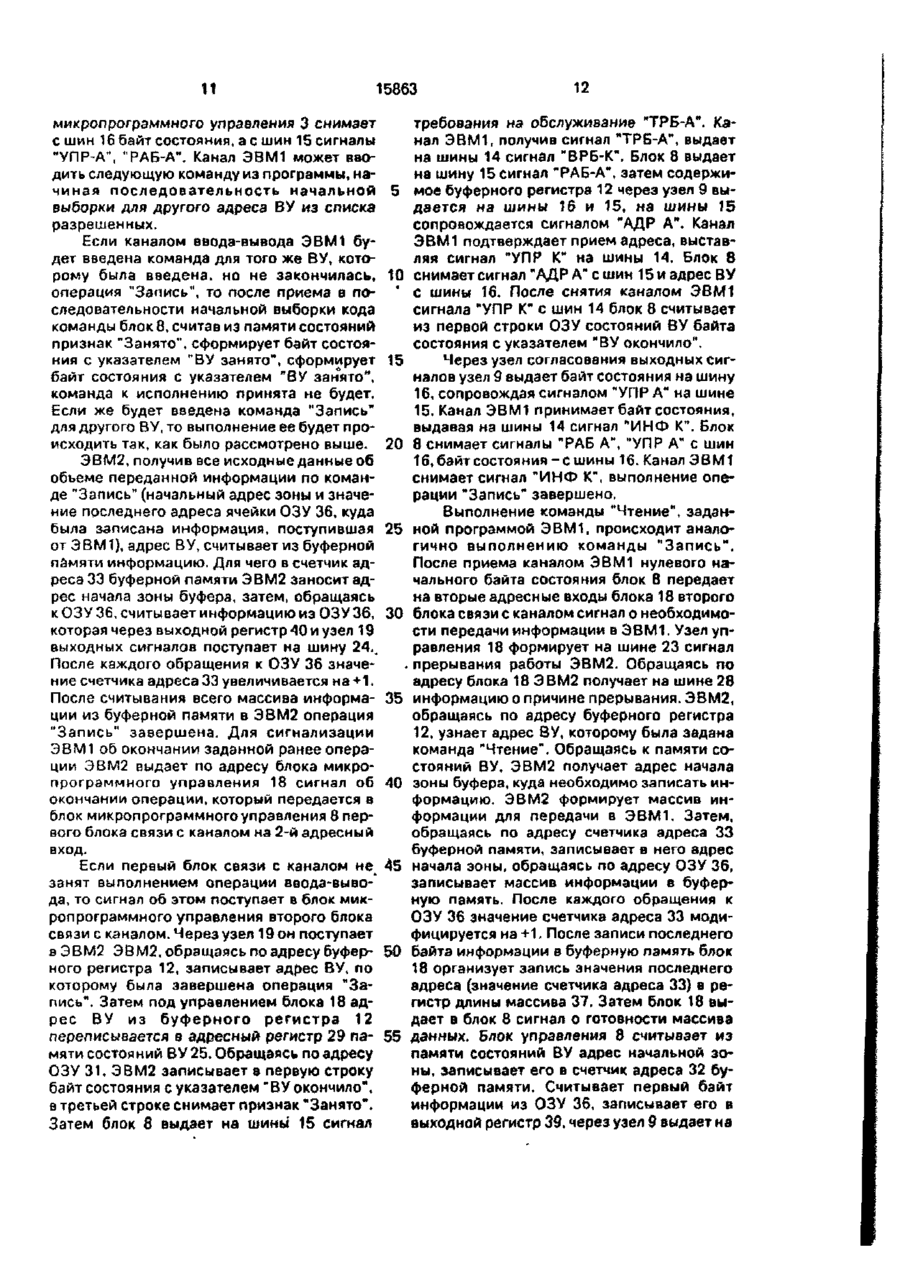

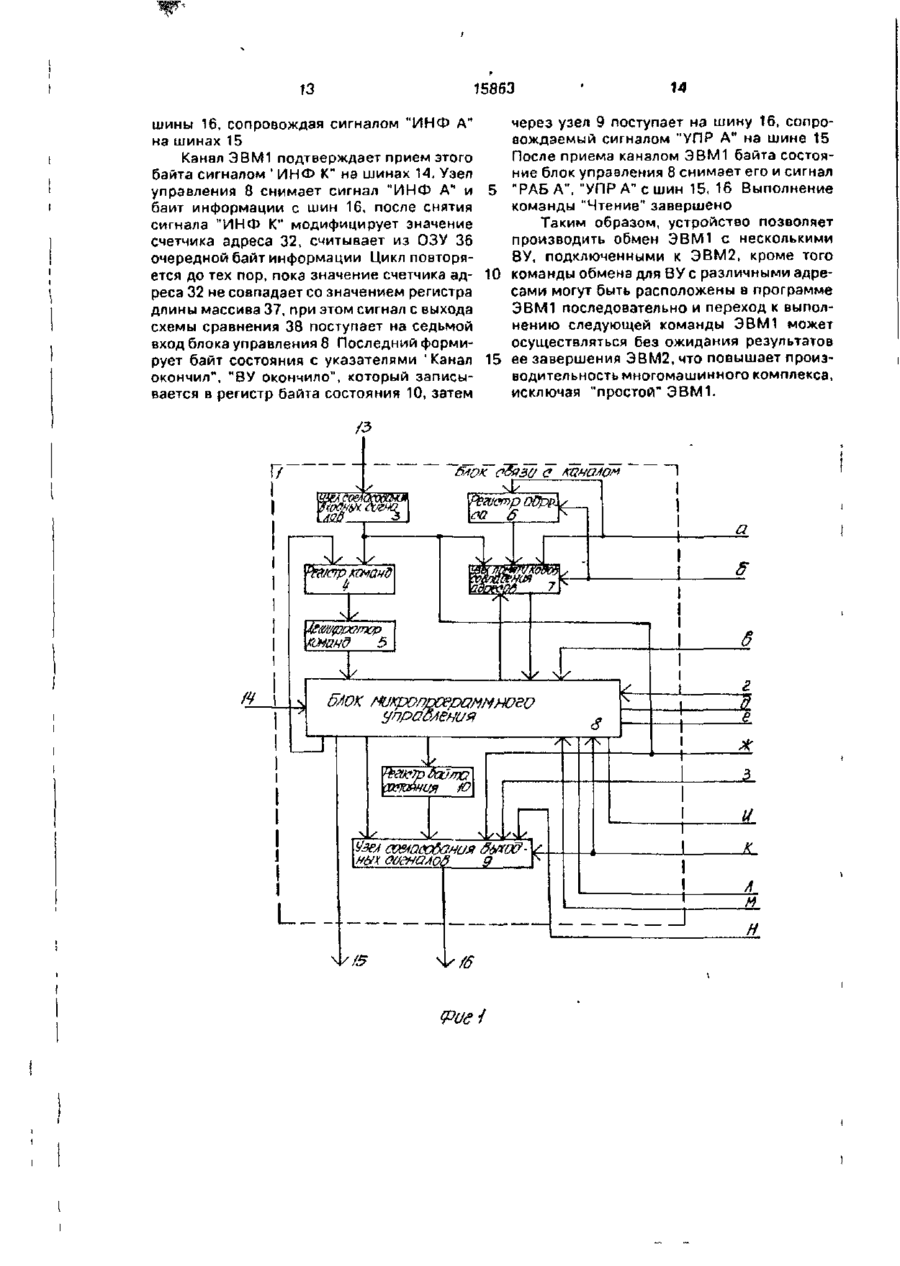

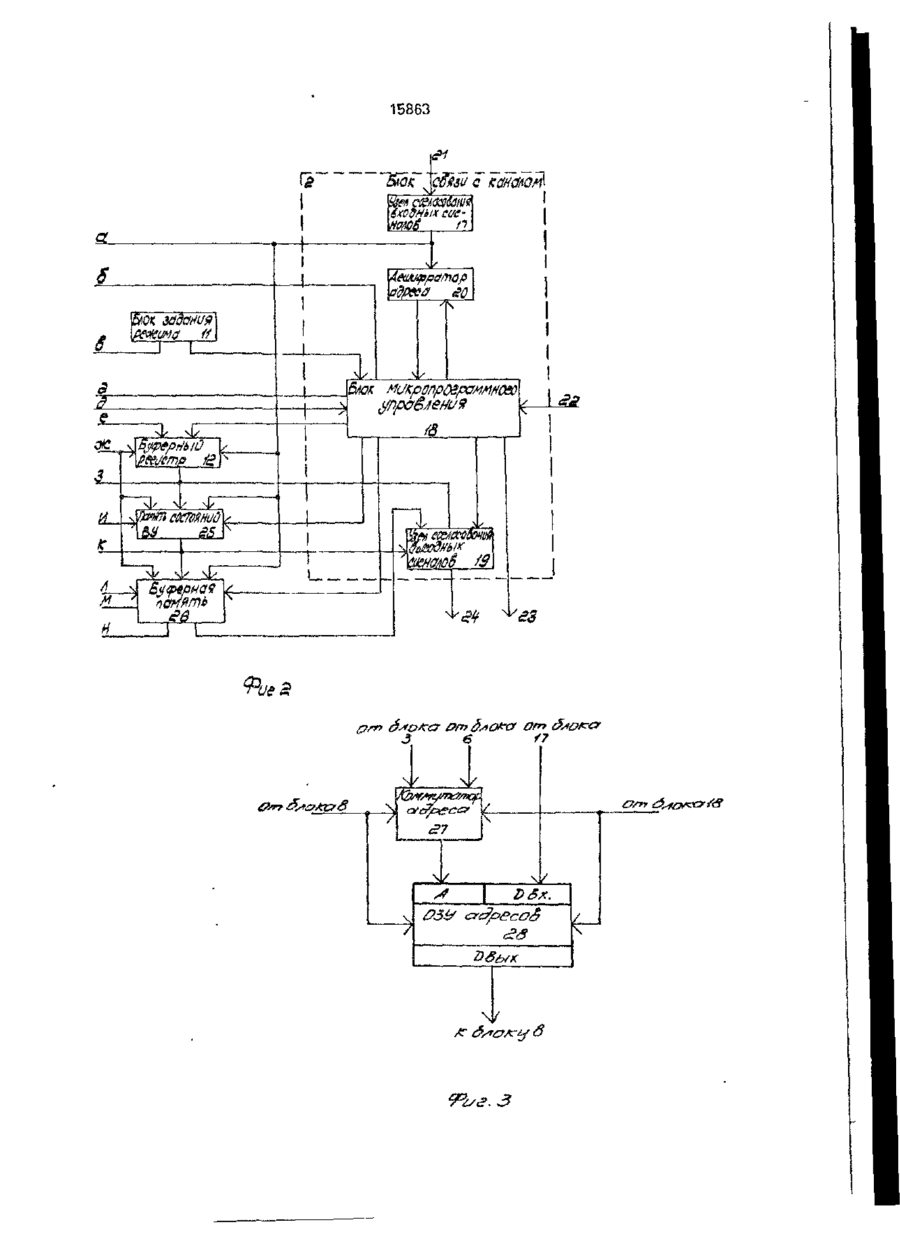

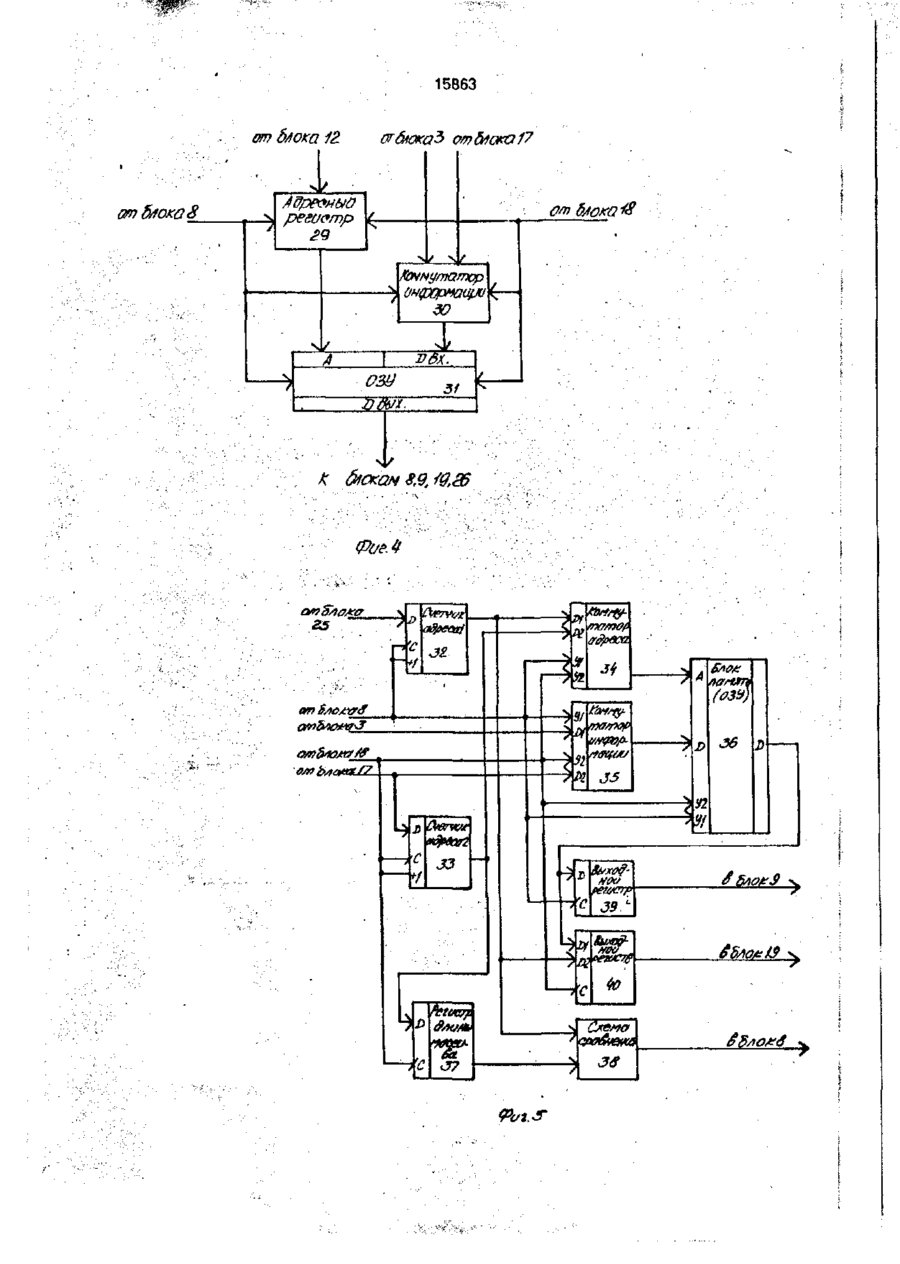

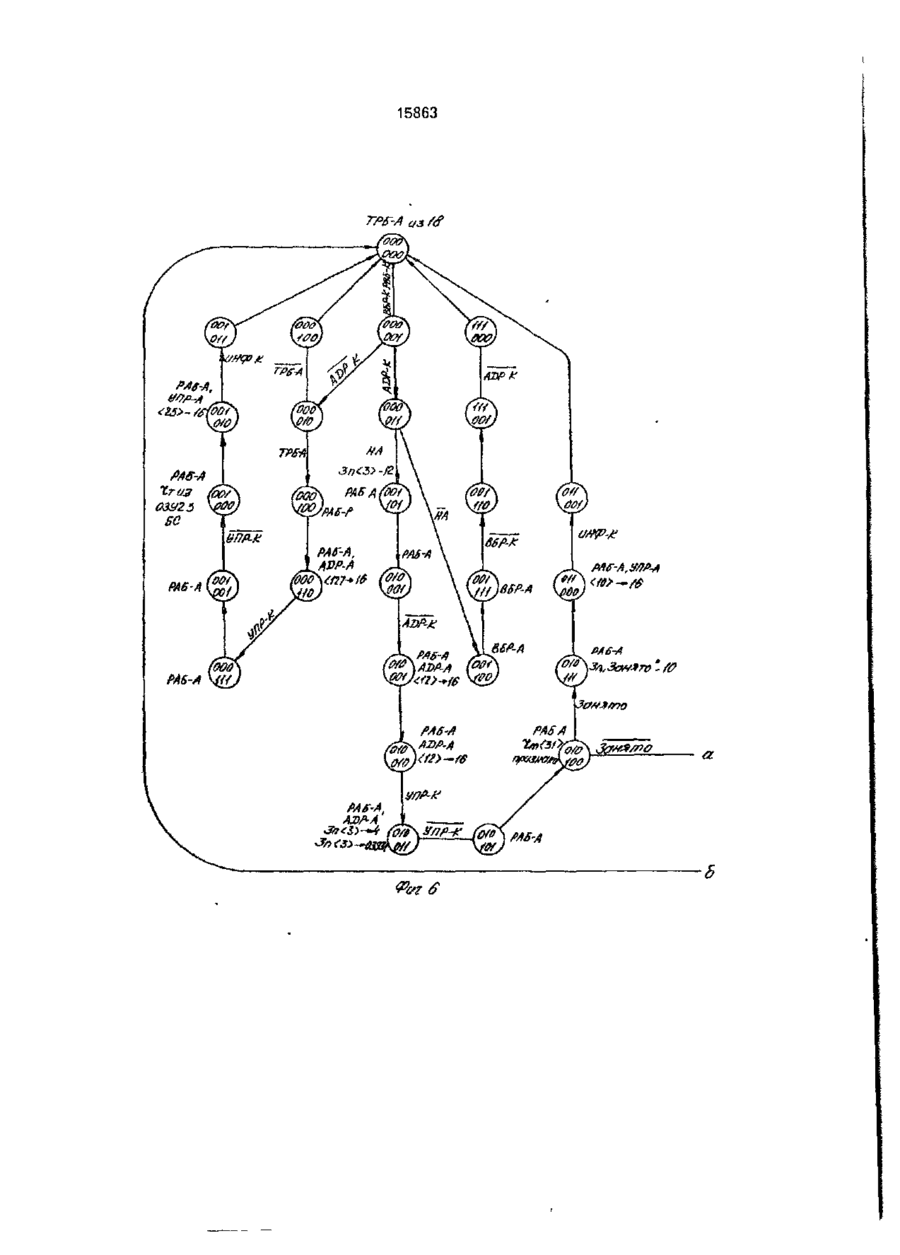

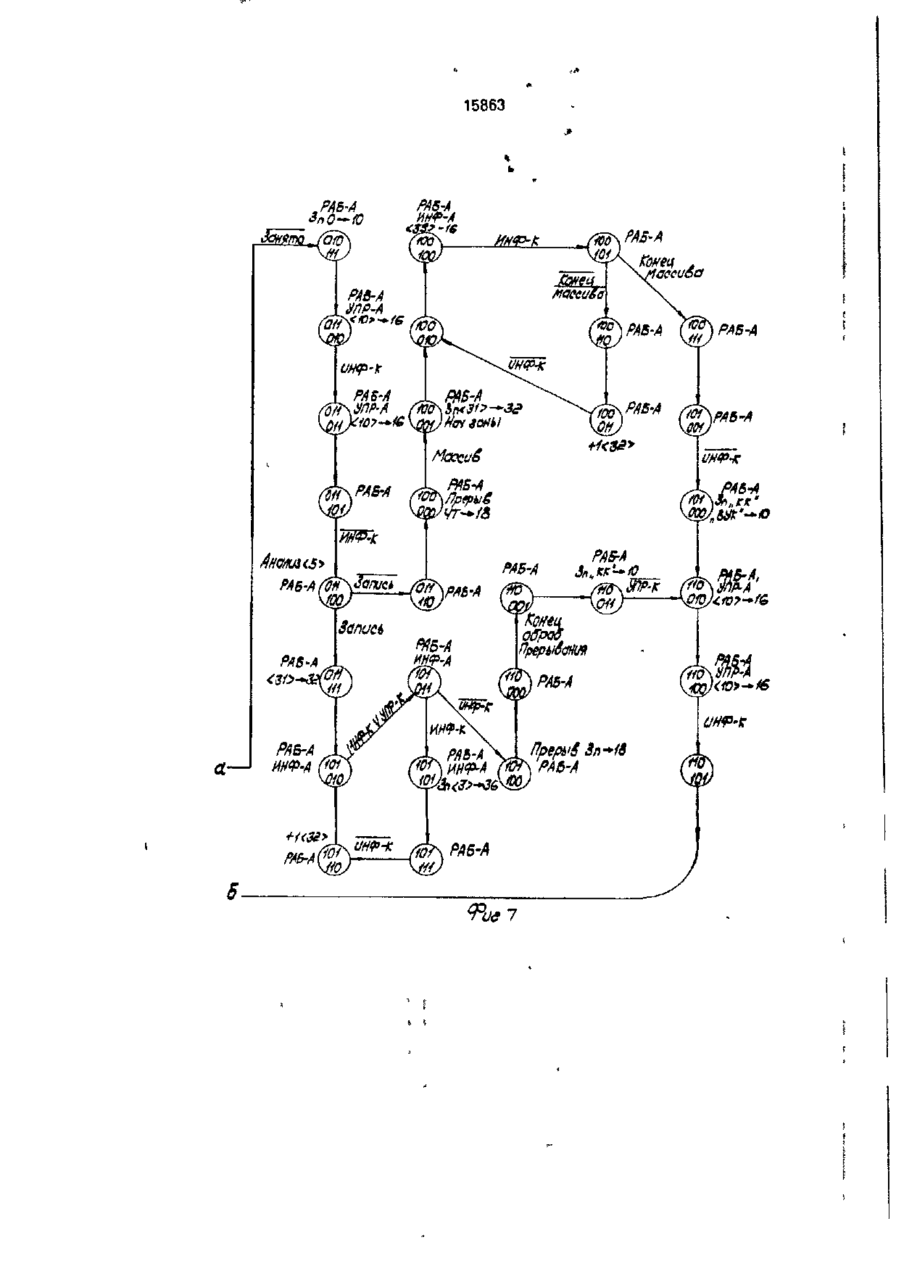

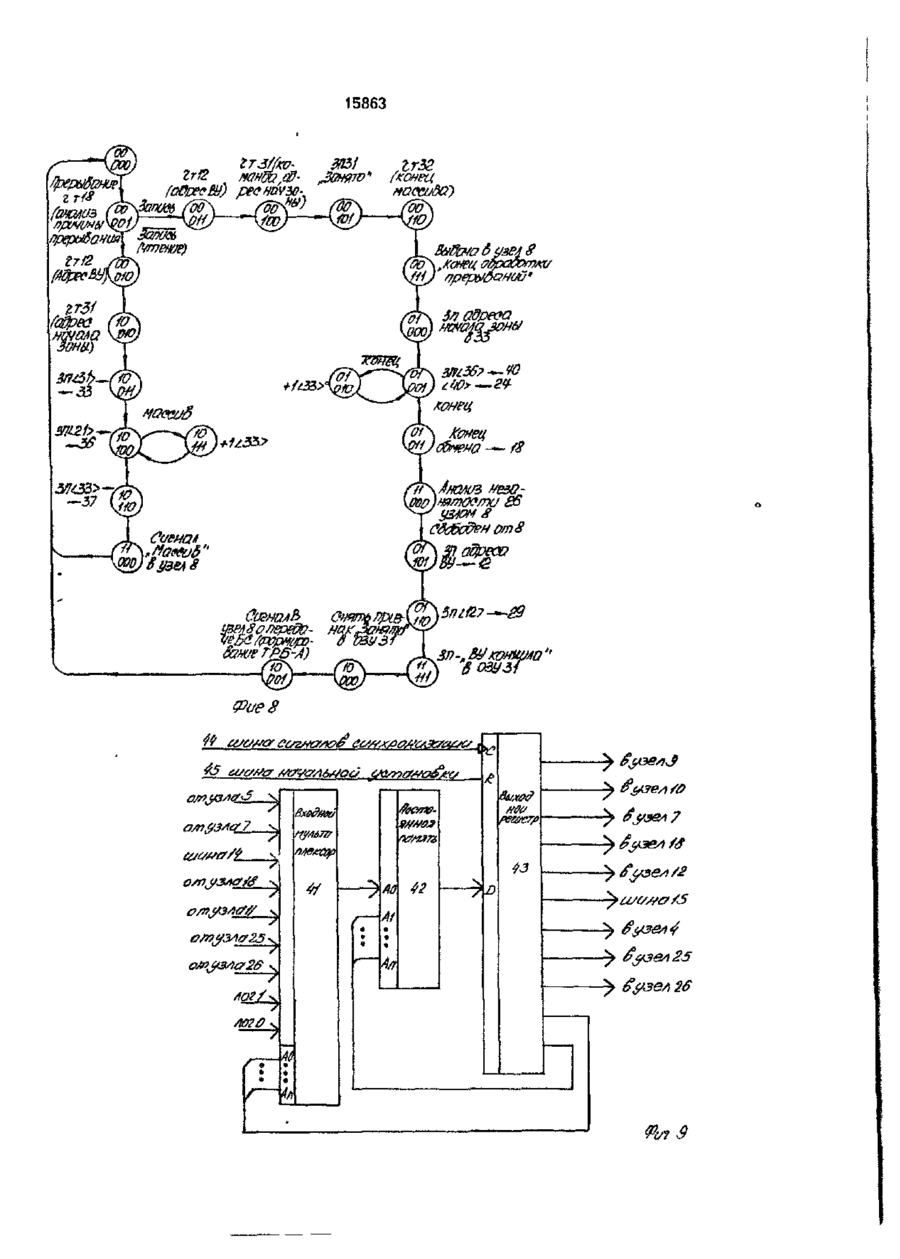

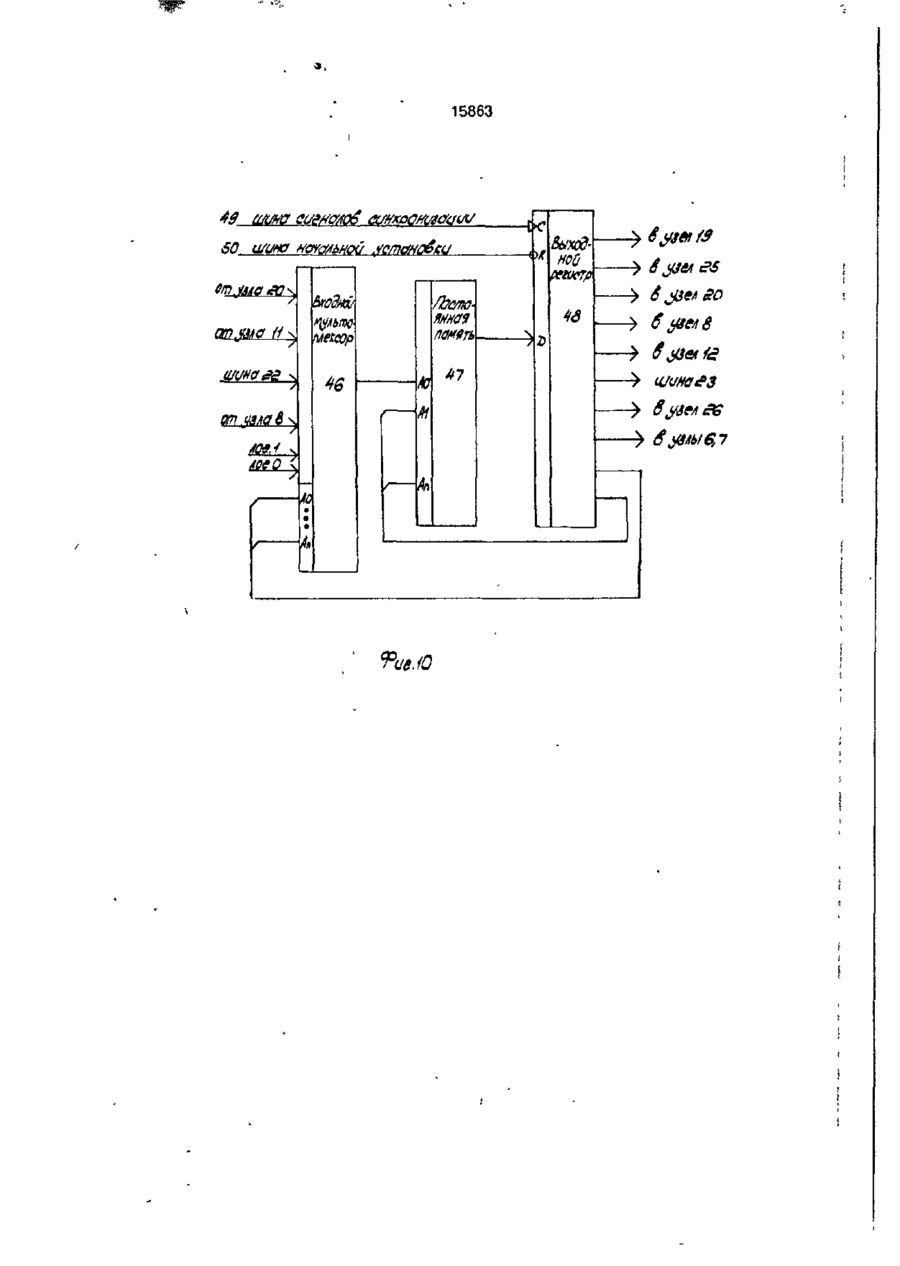

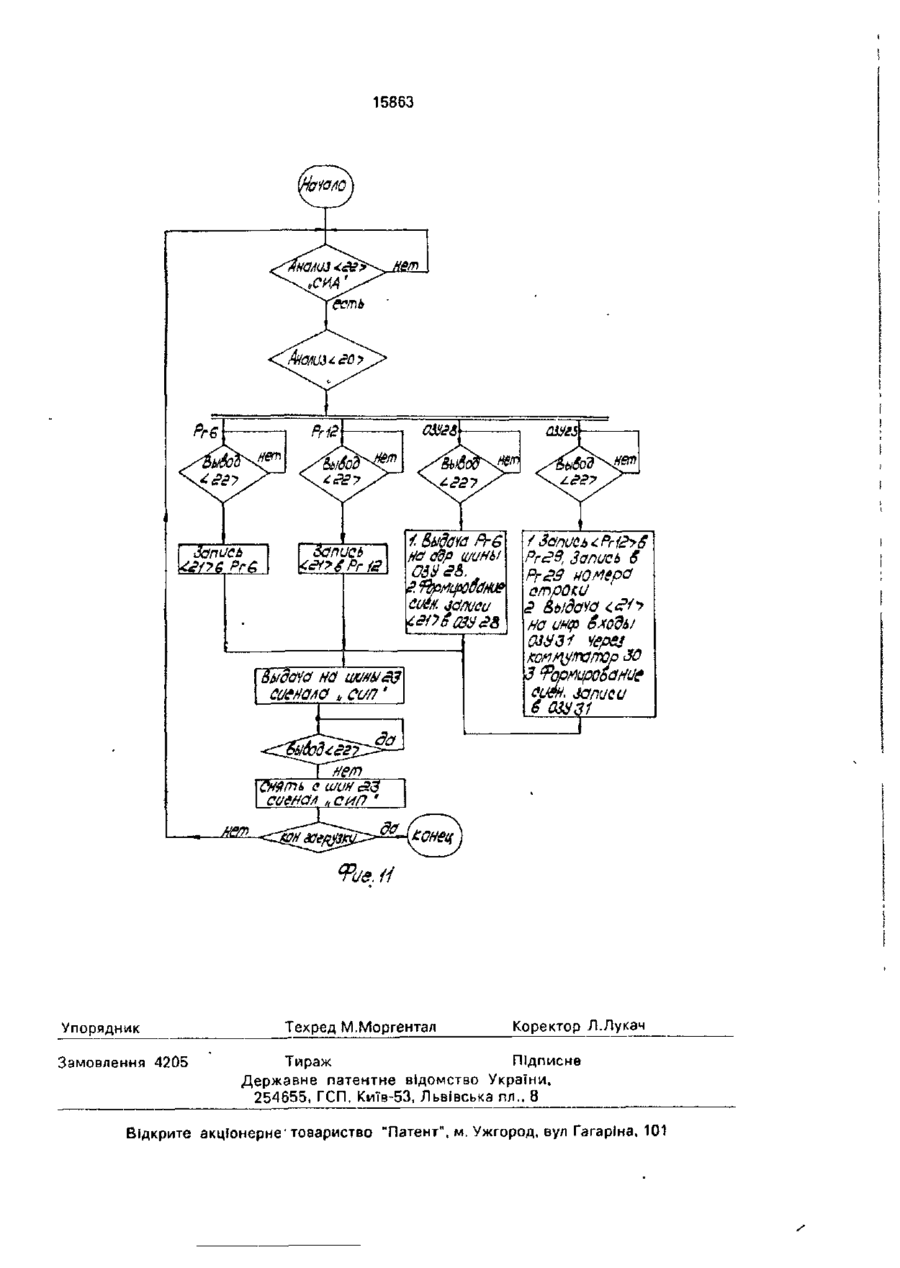

1 Адаптер канал-канал, содержащий буферный регистр, блок задания режима и два блока связи с каналом, первый из которых содержит узел согласования входных сигналов, регистр адреса, регистр команд, узел памяти кодов совпадения адресов, дешифратор команд и блок микропрограммного управления, регистр байта состояния и узел согласования выходных сигналов, выход которого является выходом адаптера для подключения к информационному входу первого абонента, вход узла согласования входных сигналов является входом адаптера для подключения к информационному выходу первого канала, выход узла согласования входных сигналов подключен к первому адресному входу узла памяти кодов совпадения адресов, к первому информационному входу узла выходных сигналов и информационному входу регистра команд, выход которого через дешифратор команд подключен к первому входу логического условия блока микропрограммного управления первого блока связи с каналом, первый выход поля управления которого подключен к входу управления узла согласования выходных сигналов, вторым информационным входом подключенный через регистр байта к второму выходу поля управления блока микропрограммного управления первого блока связи с каналом второй вход логического условия и третий выход поля управления которого подсоединены к выходу и входу разрешения узла памяти кодов совпадения адресов соответственно, четвертый выход поля управления блока микропрограммного управления первого блока связи с каналом соединен с входом разрешения буферного регистра, пятый выход поля управления блока микропрограммного управления первого блока связи с каналом является выходом адаптера для подключения к входу управления первого абонента, шестой выход поля управления блока микропрограммного управления первого блока связи с каналом соединен с синхровходом регистра команд третий вход логического условия блока микропрограммного управления первого блока связи с каналом является входом адаптера для подключения к выходу управления первого канала, второй адресный вход узла памяти кодов совпадения адреса соединен с выходом регистра адреса, первый и второй выходы блока задания режима работы соединены с входами режимов работы блока микропрограммного управления первого блока связи с каналом и второго блока связи с каналом, вход режима работы которого соединен с входом режима работы блока микропрограммного управления второго блока связи с каналом, содержащим также узел согласования входных сигналов, узел согласования выходных сигналов, причем вход узла согласования входных сигналов второго блока связи с каналом является входом адаптера для подключения к выходу информации второго канала, выход узла согласования входных сигналов второго блока связи с каналом соединен с первым информационным входом буферного регистра, синхровход которого соединен с первым вы с > с» CN со о 15863 ходом поля управления блока микропрограммного управления второго блока согласования, первый вход логического условия которого соединен с входом адаптера для подключения к выходу управления второго канала, второй выход поля управления блока микропрограммного управления второго блока связи с каналом соединен с управляющим входом узла согласования выходных сигналов второго блока связи с каналом, выход которого является выходом адаптера для подключения к информационному входу второго абонента, третий выход поля управления узла микропрограммного управления второго блока связи с каналом является выходом адаптера для подключения к входу управления второго абонента, первый информационный вход узла согласования выходных сигналов второго блока связи с каналом соединен с выходом буферного регистра, о т л и ч а ю щ и й с я тем, что в адаптер введены буферная память и память состояния, а второй блок связи с каналом содержит дешифратор адреса, причем первый информационный вход памяти состояний с о е д и н е н с выходом буферного регистра и третьим информационным входом узла согласования выходных сигналов первого блока связи с каналом, второй информационный вход памяти состояний соед и н е н с выходом узла согласования входных сигналов, с информационным входом дешифратора адреса второго блока связи с каналом, вторым информационным входом буферного регистра, первым информационным входом буферной памяти, информационными входами узла памяти кодов совпадения адресов и регистра адреса, третий информационный вход памяти состояния соединен с выходом узла согласования входных сигналов первого блока связи с каналом и с вторым информационным входом буферной памяти, третий информационный вход буферной памяти соединен с выходом памяти состояний, вторым информационным входом узла согласования выходных сигнапов второго блоха связи с каналом, четвертым информационным входом узла согласования выходных сигналов первого блока связи с каналом и четвертым входом логического условия узла микропрограммного управления первого блока связи с каналом, вход управления буферной памяти и памяти состояния соединены с четвертым и пятым выходом поля управления узла микропрограммного управления второго блока связи с каналом соответственно, входы разрешения памяти состояний и буферной памяти соединены с седьмым и восьмым выходом поля управле ния узла микропрограммного управления первого блока связи с каналом соответственно, первый выход буферной памяти соединен с третьим информационным входом узла согласования выходных сигналов второго блока связи с каналом, второй выход буферной памяти соединен с пятым информационным входом узла согласования выходных сигналов первого блока связи с каналом, третий выход буферной памяти соединен с пятым входом логического условия узла микропрограммного управления первого блока связи с каналом, управляющий вход регистра адреса первого блока связи с каналом объединен с управляющим входом узла памяти кодов совпадения адресов и соединен с шестым выходом поля управления узла микропрограммного управления второго блока связи с каналом, седьмой выход поля управления которого соединен с управляющим входом дешифратора адреса второго блока связи с каналом, выход которого соединен с первым адресным входом узла микропрограммного управления второго блока связи с каналом, второй адресный вход которого соединен с девятым выходом поля управления узла микропрограммного управления первого блока связи с каналом, шестой вход логического условия соединен с восьмым выходом поля управления узла микропрограммного управления второго блока связи с каналом. 2. Адаптер по п.1 . о т л и ч а ю щ и й с я тем. что буферная память содержит два счетчика адреса, коммутатор адреса, коммутатор информации, блок памяти, регистр длины массива, схему сравнения, два выходных регистра, причем выход первого вых о д н о г о р е г и с т р а является п е р в ы м информационным выходом памяти, выход второго выходного регистра - вторым информационным выходом памяти, первый информационный вход первого выходного регистра объединен с первым информационным входом второго выходного регистра и подключен к выходу блока памяти, второй информационный вход первого выходного регистра объединен с первым входом схемы сравнения, первым информационным входом коммутатора адреса и подключен к выходу первого счетчика адреса, информационный вход которого является третьим информационным входом памяти, счетный и синхровход первого счетчика адреса объединены и соединены с первыми управляющими входами коммутатора адреса, коммутатора информации, блока памяти, синхровходом второго выходного регистра и являются входом разрешения памяти, синхровход которой объединен с входами 15863 такта и счета второго счетчика адреса, синхровходом регистра длины массива, управляющим входом первого выходного регистра, вторыми управляющими входами коммутатора адреса, коммутатора информации и блока памяти, информационный и адресный входы которого соединены с выходом коммутатора информации и выходом коммутатора адреса соответственно, второй информационный вход которого объ единен с информационным входом регистра длины массива и с выходом второго счетчика адреса, информационный вход которого объединен с вторым информационным входом коммутатора информации и является первым информационным входом памяти, выход регистра длины массива соединен с вторым входом схемы сравнения, выход которой является третьим выходом памяти. Изобретение относится к вычислитель" Память состояний внешнего устройства ной технике и может использоваться как 25 (фиг.4) содержит адресный регистр 29, системное устройство для связи цифровых коммутатор информации 30, ОЗУ 31. вычислительных машин в многомашинных Буферная память 26 (фиг.5) содержит вычислительных комплексах. 5 счетчики адреса 32, 33, коммутатор адреса Целью изобретения является расшире34, коммутатор информации 35, блок памяние функциональных возможностей путем ти 36, регистр длины массива 37, схему обеспечения передачи информации по несравнения 38, выходные регистры 39, 40. скольким адресам. Блоки 8 и 18 реализованы в виде микроИзобретение поясняется чертежами. 10 программных автоматов, графолгоритмы которых приведены на фиг.б, 7, 8. На фиг.1, 2 показана схема устройства; Блок 8 (18) включает в себя входной на фиг.З - узел памяти кодов совпадения мультиплексор 41 (46), постоянную память «дресов; на фиг.4 - схема памяти состояний 42 (47), выходной регистр 43 (48), шину 44 внешнего устройства; на фиг.5 - буферная память; на фиг.6,7,8- грзфалгоритмы узлов 15 (49) сигналов синхронизации, шину 45 (50) начальной установки (фиг.9, 10). управления; на фиг.9, 10-блоки микропрогМультиплексор 41 (46) предназначен раммного управления; на фиг. 11 -алгоритм для реализации условных переходов. Поработы. стоянная память 42 (47) служит для хранеНа фиг.1, 2 приведена функциональная схема устройства. 20 ния набора микрокоманд. Выходной регистр 43 (48) предназначен для устранеАдаптер канал-канал состоит из двух ния разброса времени выборки различных блоков 1 и 2 связи с каналом, блока задания адресных разрядов постоянной памяти. режима 11, буферного регистра 12, памяти состояний ВУ 25, буферной памяти 26. На графах алгоритма (фиг.6,7,8) в кружПервый блок 1 связи с каналом состоит 25 ках изображен адрес ячейки постоянной паиз узла согласования входных сигналов 3, мяти, в которой хранится микрокоманда, регистра команд 4, дешифратора команд 5, дугами изображены переходы из одного сорегистра адреса 6, узла памяти кодов совпастояния в другое. Названия сигналов над дения адресов 7, блока микропрограммного кружками означают, что сигналы формирууправления 8, узла согласования выходных 30 ются в этих состояниях, названия сигналов сигналов 9, регистра байта состояния 10, над дугами означают, что переход из одного информационных 13 и управляющих 14 лисостояния (начало дуги) в другое (стрелка ний канала, управляющих 15 и информацидуги) происходит при наличии этого сигнаонных 16 линий абонента. ла. Узел микропрограммного управления Второй блок 2 связи с каналом содер- 35 работает следующим образом. житузел согласования входных сигналов 17, В исходном состоянии регистры 43 (48) блок микропрограммного управления 18, обнулены и на адресных входах постоянной узел согласования выходных сигналов 19, памяти 42 (47) присутствует нулевой адрес. дешифратор адреса 20, информационные входы шины 21, управляющие входы 22 и 40 После сброса сигнала начальной установки по каждому сигналу синхронизации произвыходные 23 и 24 шины. водится анализ сигналов условий, поступаУзел 7 памяти кодов совпадения адреющих на входы мультиплексора 41 (46) и сов (фиг.З) содержит коммутатор адреса 27, переход в очередное состояние. ОЗУ адресов 28. 15863 В каждом состоянии узла управления на адресный вход постоянной памяти 42 (47) подключается одна из входных шин узла. Выбор подключаемой шины производится а поле формата микрокоманды, Возможный формат микрокоманды имеет вид: А М К - поле адреса следующей микрокоманды; АМХ - поле хода адреса подключаемого входа мультиплексора; УПР - поле выходных сигналов устройства управления. Если на входной шине присутствует входной сигнал (т.е. логическая "1"), то узел управления переходит в состояние, в младшем разряде которого присутствует единица, если на выбранной шине отсутствует входной сигнал (т.е. присутствует логический "0"), то автомат переходит в состояние, в младшем разряде которого присутствует ноль. Например, пусть поле адресов постоянной памяти (АМК) представляет комбинацию 0 0 1 1 , поле адреса в х о д н о г о мультиплексора (АМХ)-0101. Если на пятом входе мультиплексора присутствует входной сигнал (т.е. логическая "1"), то переход осуществляется по адресу 00111, если отсутствует - по адресу 00110. Для формирования выходных сигналов устройства управления используется горизонтальное микропрограммирование, т.е. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие определенный выходной сигнал устройства управления. Работает адаптер канал-канал следующим образом. Перед началом работы ЭВМ, подсоединенная к второму блоку связи с каналом (ЭВМ2), производит загрузку исходных данных в узел 7 памяти кодов совпадения адресов и о память 25 состояний ВУ. Исходные данные это. список адресов ВУ, с которыми может работать канал ввода-вывода ЭВМ, подсоединенной к первому блоку связи с каналом (ЭВМ1), и распределение буферной памяти адаптера канал-канал между разрешенными ВУ. Распределение буферной памяти производится путем загрузки в память состояний ВУ адресов начало зон, выделенных для каждого адреса ВУ. Загрузка списка адресов ВУ производится следующим образом. ЭВМ2 посылает на информационные шины 21 адрес, соответствующий адресу регистра адреса 6 для ЭВМ2, сопровождая его на управляющих шинах 22 сигналом синхронизации "СИА". Блок микропрограммного управления 18 анализирует сигналы на выходе дешиф 5 10 15 20 25 30 35 40 45 50 55 8 ратора адреса 20 и при появлении на управляющих шинах 22 сигнала "Вывод" формирует сигнал записи информации с шин 21 в регистр адреса 6. На шинах 21 в это время находится адрес ВУ из списка адресов ВУ. Затем ЭВМ2 выставляет на информационные шины 21 адрес ОЗУ адресов, при появлении сигнала "СИА" на шинах 22 узел •управления 18 анализирует этот адрес на выходе дешифратора адреса 20 и при появлении сигнала "Вывод" формирует сигналы записи информации с шин 21 в ячейку ОЗУ адресов, адрес которой соответствует адресу ВУ, записанному в регистре адреса 6. На информационные шины 21 ЭВМ2 при этом выдает признак соответствия адреса ВУ списку (признак расположен в одном определенном разряде информационных шин, например, в нулевом разряде). Таким образом, во все 8-ми битные ячейки ОЗУ адресов, адреса которых соответствуют адресам ВУ из списка, в определенный разряд памяти ОЗУ адресов записывается единица. В ячейки, адреса которых не соответствуют адресам ВУ из списка, в этот разряд записывается нуль. При загрузке распределения буферной памяти между ВУ ЭВМ2 производит запись во вторую строку ОЗУ по адресу, соответствующему адресу ВУ, значение адреса начала зоны, выделенной в буферной памяти для данного ВУ. Алгоритм загрузки исходных данных ЭВМ2 приведен на фиг.11. После загрузки исходных данных адаптер канал-канал готов к работе под управлением ЭВМ1 и ЭВМ2. Канал ЭВМ1, начиная последовательность начальной выборки ВУ, выдает на шины 13 адрес ВУ, сопровождая его сигналами "АДР-К", "ВБР-К", "РВБ-К" на шинах 14. Адрес ВУ с выхода узла 3 поступает на первый информационный вход коммутатора адреса 27 узла 7 памяти кодов совпадения адресов. С выхода коммутатора 27 адрес ВУ поступает на адресные входы ОЗУ адресов 28. под управлением блока 8 производится считывание признака принадлежности адреса ВУ к списку адресов. С информационных выходов ОЗУ адресов 28 значение этого признака поступает в блок микропрограммного управления 8. Блок формирует сигнал записи адреса ВУ с выхода узла 3 в буферный регистр 12. Узел управления 8 формирует сигнал "РАБ-А" по шине 15, который поступает в канал ввода-вывода ЭВМ1. Канал ввода-вывода ЭВМ1 снимает с шин 13 адрес ВУ, ас шины 14-сигнал "АДР-К". Содержимое буферного регистра 12 (адрес ВУ) через узел согласования выходных сигналов 9 по 15863 10 ступает на шину 16, на шине 15 блок 8 форвыдает следующий байт информации на шимирует сигнал "АДР-А". ны 13, который записывается в следующую ячейку буферной памяти. Обмен произвоКанал ЭВМ1 выдает на шину 13 код опедится до тех пор, пока канал ЭВМ1 в ответ рации, сопровождая его на шине 14 сигналом "УПР-К". Блок микропрограммного 5 на сигнал запроса "ИНФ А" не выдаст на шину 14 сигнал "УПР К". управления 8 производит запись кода операции в регистр команд 4, а в нулевую строБлок 8, получив сигнал окончания "УПР ку я ч е й к и ОЗУ 3 1 , адрес к о т о р о й К", выдает сигнал окончания обмена в блок соответствует адресу ВУ из буферного регимикропрограммного управления 18 второго стра 12, - кода операции с выхода узла 3 10 блока связи с каналом и снимает сигнал согласования входных сигналов. Содержи"ИНФ А" с шины 15. мое регистра команд 4 поступает на вход Блок 18, получив сигнал об окончании дешифратора команд 5. С выхода последнеобмена, производит выдачу в ЭВМ2 сигнала го код типа заданной программой ЭВМ1 прерывания по шине 23, на шину 24 выдает операции ввода-вывода ("Запись", "Чте- 15 информацию о причине прерывания, ЭВМ2 ние", "Управление" и т.д.) поступает на вход выдает на шину 21 адрес буферного регистблока микропрограммного управления 8. ра, сопровождая его сигналом "СИА" на шиБлок 8 снимает с информационных шин 16 не 22. Б Л О К 18 а н а л и з и р у е т выход адрес ВУ. с шин 15 - сигнал "АДР А". Канал дешифратора адреса 20. При приеме на шиввода-вывода ЭВМ1 снимает сигнал "УПР 20 не 22 сигнала "Ввод"отЭВМ2 блок 18 переК" с шин 14 и код операции с шин 13. дает через узел 19 выходных сигналов на Рассмотрим работу адаптера канал-кашину 24 адреса ВУ из буферного регистра нал при приеме команды "Запись". Блок 8 12, сопровождая их сигналом "СИП" на шипроизводит считывание из третьей строки не 23. ЭВМ2 принимает адрес ВУ и снимает памяти состояний ВУ по адресу ВУ призна- 25 сигнал "Ввод" с шин 22. Блок микропрогка "Занято" (адрес ВУ хранится в буферном раммного управления 18 снимает сигнал регистре 12). Значение этого признака по"СИП" с шин 23 и адрес ВУ с шин 24, ЭВМ2 ступает иа шестой вход блока 8. Если приСнимает сигнал "СИА". Затем аналогичным знак "Занято" для данного ВУ отсутствует, образом ЭВМ2 считывает из памяти 25 сото блок 8 формирует запись в регистр 10 30 стояний ВУ код операции выполняемой кобайта состояния нулевого байта состояния, манды (в данном случае "Запись") адреса который через узел 9 выдается на информаначала зоны буфера. ционные шины 16, сопровождаемый на шиВ третью строку памяти состояний ВУ нах 15 сигналом "УПР А". по адресу данного ВУ ЭВМ2 записывает Канал ЭВМ 1 подтверждает прием от 35 признак "Занято". Затем ЭВМ2, обращаясь адаптера канал-канал байта состояния, выпо адресу счетчика адреса 32, считывает его давая на шины 14 сигнал "ИНФ К". Блок 8 значение (последний адрес ячейки ОЗУ 36, снимает байт состояния с шин 16 байт сокуда была записана информация от ЭВМ1). стояния, с шин 15 - сигнал "УПР А". Канал Значение счетчика адреса 32 через выходЭВМ1 снимает с шин 14 сигнал "ИНФ К". 40 ной регистр 40 поступает на четвертый вход Блок микропрограммного управления 8 узла согласования выходных сигналов 19, а производит считывание по адресу ВУ из бузатем-на информационную шину 24 ЭВМ2. ферного регистра 12 из второй строки памяЭВМ2 после считывания всех необходити 25 состояний ВУ адреса канала зоны мых данных, обращаясь по адресу блока выделенной в буферной памяти 26 для дан- 45 микропрограммного управления 18, сигнаного ВУ. Этот адрес с выхода ОЗУ 31 запилизирует об окончании обработки прерывасывается в счетчик адреса 32 буферной ния. Из блока 18 сигнал об окончании памяти. Затем блок 8 подает на шины 15 обработки прерывания поступает на 6-й сигнал запроса на байт информации в ЭВМ1 вход логического условия блока микропрог"ИНФ А". Канал ЭВМ1 выдает на шины 13 50 раммного управления 8 первого блока связи байт информации, 'сопровождая его сигнас каналом. лом " И Н Ф К" на шине 14. Блок 8 производит Блок микропрограммного управления 8 запись этого байта с выхода узла 3 согласоформирует байт состояния с указателем "Кавания входных сигналов в ОЗУ 36 по адресу нал кончил", который записывается в реначала зоны и снимает сигнал "ИНФ А" с 55 гистр байта состояния 10 и через узел шин 15. Канал ЭВМ1 снимаете шин 13 байт согласования выходных сигналов 9 поступаинформации и сигнал "ИНФ К" с шин 14, ет на информационную шину 16, сопровожБлок управления 8 модифицирует на +1 знадаемый сигналом "УПР Ам на шине 15. Канал чение счетчика адреса 32 и выдает на шину ЭВМ1 принимает байт состояния, выдавая 15 сигнал запроса "ИНФ А". Канал ЭВМ1 при этом на шину 14 сигнал "ИНФ-К". Блок 11 15863 12 требования на обслуживание "ТРБ-А". Камикропрограммного управления 3 снимает нал ЭВМ1, получив сигнал "ТРБ-А", выдает с шин 16 байт состояния, а с шин 15 сигналы на шины 14 сигнал "ВРБ-К". Блок 8 выдает "УПР-А", "РАБ-А". Канал ЭВМ1 может ввона шину 15 сигнал "РАБ-А", затем содержидить следующую команду из программы, начиная последовательность начальной 5 мое буферного регистра 12 через узел 9 выдается на шины 16 и 15, на шины 15 выборки для другого адреса ВУ из списка сопровождается сигналом "АДР А". Канал разрешенных. ЭВМ1 подтверждает прием адреса, выставЕсли каналом ввода-вывода ЭВМ1 буляя сигнал "УПР К" на шины 14. Блок 8 дет введена команда для того же ВУ, которому была введена, но не закончилась, 10 снимает сигнал "АДР А" с шин 15 и адрес ВУ операция "Запись", то после приема в по- * с шины 16. После снятия каналом ЭВМ* следовательности начальной выборки кода сигнала "УПР К" с шин 14 блок 8 считывает команды блок 8, считав из памяти состояний из первой строки ОЗУ состояний ВУ байта признак "Занято", сформирует байт состоясостояния с указателем "ВУ окончило". ния с указателем "ВУ занято", сформирует 15 Через узел согласования выходных сигбайт состояния с указателем "ВУ занято", налов узел 9 выдает байт состояния на шину команда к исполнению принята не будет. 16, сопровождая сигналом "УПР А" на шине Если же будет введена команда "Запись" 15. Канал ЭВМ1 принимает байт состояния, для другого ВУ, то выполнение ее будет провыдавая на шины 14 сигнал "ИНФ К". Блок исходить так, как было рассмотрено выше. 20 8 снимает сигналы "РАБ А", "УПР А" с шин ЭВМ2, получив все исходные данные об 16, байт состояния - с шины 16. Канал ЭВМ1 объеме переданной информации по команснимает сигнал "ИНФ К", выполнение опеде "Запись" (начальный адрес зоны и значерации "Запись" завершено. ние последнего адреса ячейки ОЗУ 36, куда Выполнение команды "Чтение", заданбыла записана информация, поступившая 25 ной программой ЭВМ1, происходит аналоот ЭВМ1), адрес ВУ, считывает из буферной гично выполнению команды "Запись". памяти информацию. Для чего в счетчик адПосле приема каналом ЭВМ1 нулевого нареса 33 буферной памяти ЭВМ2 заносит адчального байта состояния блок 8 передает рес начала зоны буфера, затем, обращаясь на вторые адресные входы блока 18 второго к ОЗУ 36, считывает информацию из ОЗУ 36, 30 блока связи с каналом сигнал о необходимокоторая через выходной регистр 40 и узел 19 сти передачи информации вЭВМ1. Узел упвыходных сигналов поступает на шину 24., равления 18 формирует на шине 23 сигнал После каждого обращения к ОЗУ 36 значе. прерывания работы ЭВМ2. Обращаясь по ние счетчика адреса 33 увеличивается на +1. адресу блока 18 ЭВМ2 получает на шине 28 После считывания всего массива информа- 35 информацию о причине прерывания. ЭВМ2, ции из буферной памяти в ЭВМ2 операция обращаясь по адресу буферного регистра "Запись" завершена. Для сигнализации 12, узнает адрес ВУ, которому была задана ЭВМ! об окончании заданной ранее операкоманда "Чтение". Обращаясь к памяти соции ЭВМ2 выдает по адресу блока микростояний ВУ, ЭВМ2 получает адрес начала программного управления 18 сигнал об 40 зоны буфера, куда необходимо записать инокончании операции, который передается в формацию. ЭВМ2 формирует массив инблок микропрограммного управления 8 перформации для передачи в ЭВМ1. Затем, вого блока связи с каналом на 2-й адресный обращаясь по адресу счетчика адреса 33 вход. буферной памяти, записывает в него адрес Если первый блок связи с каналом не 45 начала зоны, обращаясь по адресу ОЗУ 36, занят выполнением операции ввода-вывозаписывает массив информации в буферда, то сигнал об этом поступает в блок микную память. После каждого обращения к ропрограммного управления второго блока ОЗУ 36 значение счетчика адреса 33 модисвязи с каналом. Через узел 19 он поступает фицируется на +1. После записи последнего вЭВМ2 ЭВМ2, обращаясь по адресу буфер- 50 байта информации в буферную память блок ного регистра 12, записывает адрес ВУ, по 18 организует запись значения последнего которому была завершена операция "Заадреса (значение счетчика адреса 33) в репись". Затем под управлением блока 18 адгистр длины массива 37. Затем блок 18 вырес ВУ из буферного регистра 12 дает в блок 8 сигнал о готовности массива переписывается в адресный регистр 29 па- 55 данных. Блок управления 8 считывает из мяти состояний ВУ 25, Обращаясь по адресу памяти состояний ВУ адрес начальной зоОЗУ 31, ЭВМ2 записывает в первую строку ны, записывает его в счетчик адреса 32 бубайт состояния с указателем "ВУ окончило", ферной памяти. Считывает первый байт в третьей строке снимает признак "Занято". информации из ОЗУ 36, записывает его в Затем блок 8 выдает на шины 15 сигнал выходной регистр 39, через узел 9 выдает на 13 15863 14 через узел 9 поступает на шину 16, сопрошины 16, сопровождая сигналом "ИНФ А" вождаемый сигналом "УПР А" на шине 15 на шинах 15 После приема каналом ЭВМ1 байта состояКанал ЭВМ1 подтверждает прием этого ние блок управления 8 снимает его и сигнал байта сигналом " ИНФ К" на шинах 14. Узел управления 8 снимает сигнал "ИНФ А" и 5 "РАБ А", "УПР А" с шин 15, 16 Выполнение команды "Чтение" завершено байт информации с шин 16, после снятия Таким образом, устройство позволяет сигнала "ИНФ К" модифицирует значение производить обмен ЭВМ1 с несколькими счетчика адреса 32, считывает из ОЗУ 36 ВУ, подключенными к ЭВМ2, кроме того очередной байт информации Цикл повторяется до тех пор, пока значение счетчика ад- 10 команды обмена для ВУ с различными адресами могут быть расположены а программе реса 32 не совпадает со значением регистра ЭВМ1 последовательно и переход к выполдлины массива 37, при этом сигнал с выхода нению следующей команды ЭВМ1 может схемы сравнения 38 поступает на седьмой осуществляться без ожидания результатов вход блока управления 8 Последний формирует байт состояния с указателями ' Канал 15 ее завершения ЭВМ2, что повышает произокончил", "ВУ окончило", который записыводительность многомашинного комплекса, вается в регистр байта состояния 10, затем исключая "простой" ЭВМ1. Г ? ~1 а Узе/ амоеобания н&х оаеншоб д L 15863 15863 дюка 12 l 1 cm блока S N . ; 73 С L регистр 29 ока, от 6JOK f N / Nf 30 s s t A ОЗУ 3f s/ блокам Щ 49.35 I 25 -І'С 31 (озэ) 33 39" Схемо 3S Фиг.З* 15863 ТРГ-А аз /if PJS-A, .0/0 Ш-А ОЗУ23 ВС РАЄ-А №-A PAS-A AJDAA 15863 PAS-A РАБ-А Фиеі 15863 гтзг Ґконщ яассидсо 15863 4$ шша сигхояоб SO шина мт&ьной о/ Выходное oetuerp от. /bcmІШН09 11 \ 47 .mat *^~{№ец Упорядник Замовлення 4205 Техред М.Моргентал Коректор Л.Лукач Тираж Підписне Державне патентне відомство України. 254655, ГСП, Київ-53, Львівська пл., 8 Відкрите акціонерне'товариство "Патент", м. Ужгород, вул Ґагаріна, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюChannel-channel adapter

Автори англійськоюBurman Yosyp Shmulevych

Назва патенту російськоюАдаптер канал-канал

Автори російськоюБурман Иосиф Шмулевич

МПК / Мітки

МПК: G06F 13/00

Мітки: канал-канал, адаптер

Код посилання

<a href="https://ua.patents.su/14-15863-adapter-kanal-kanal.html" target="_blank" rel="follow" title="База патентів України">Адаптер канал-канал</a>

Попередній патент: Робочий орган землерийної машини

Наступний патент: Машина для гнуття одночасно двох протилежних кромок листів

Випадковий патент: Метод лікування синдрому дефіциту уваги і гіперактивності