Пристрій та спосіб обробки даних

Формула / Реферат

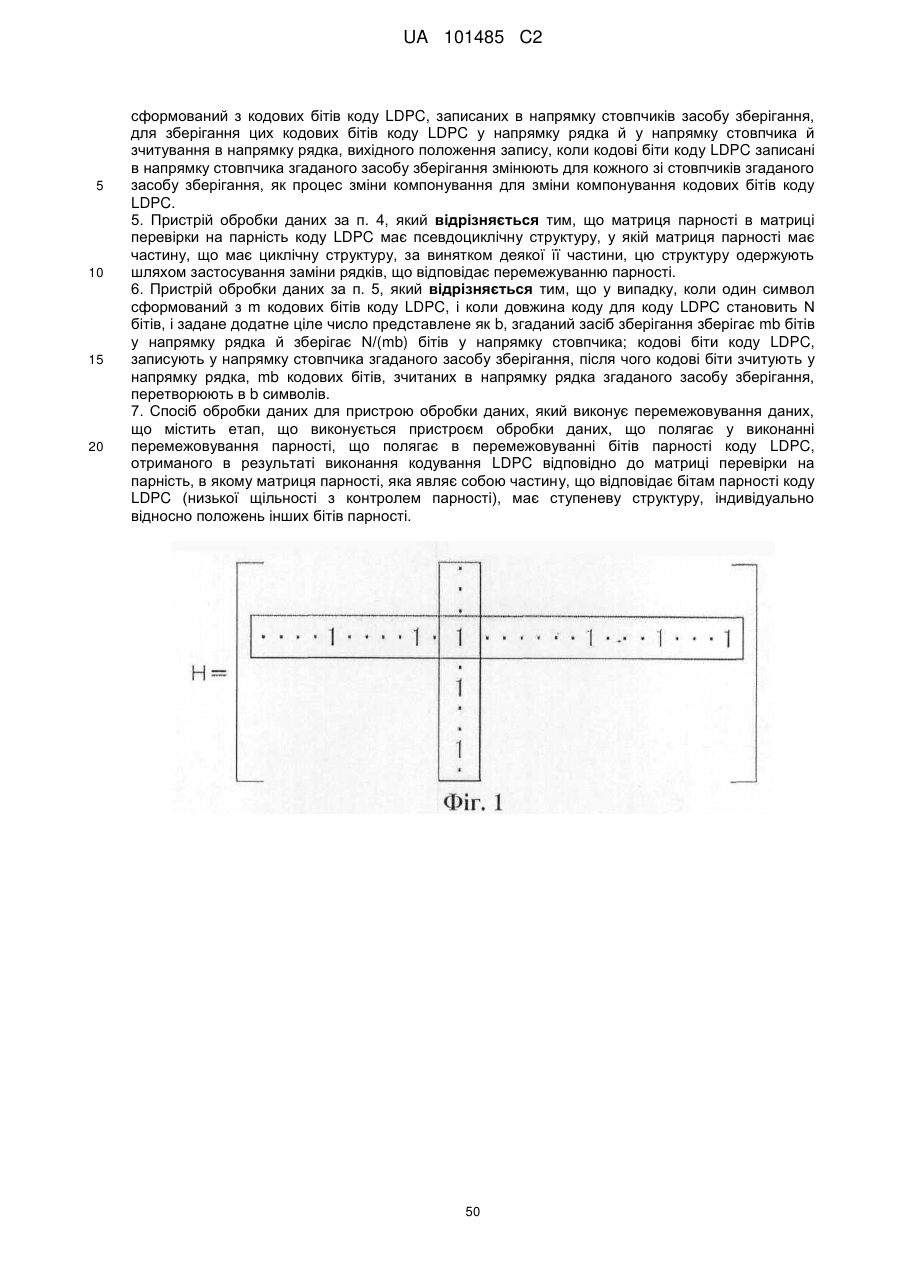

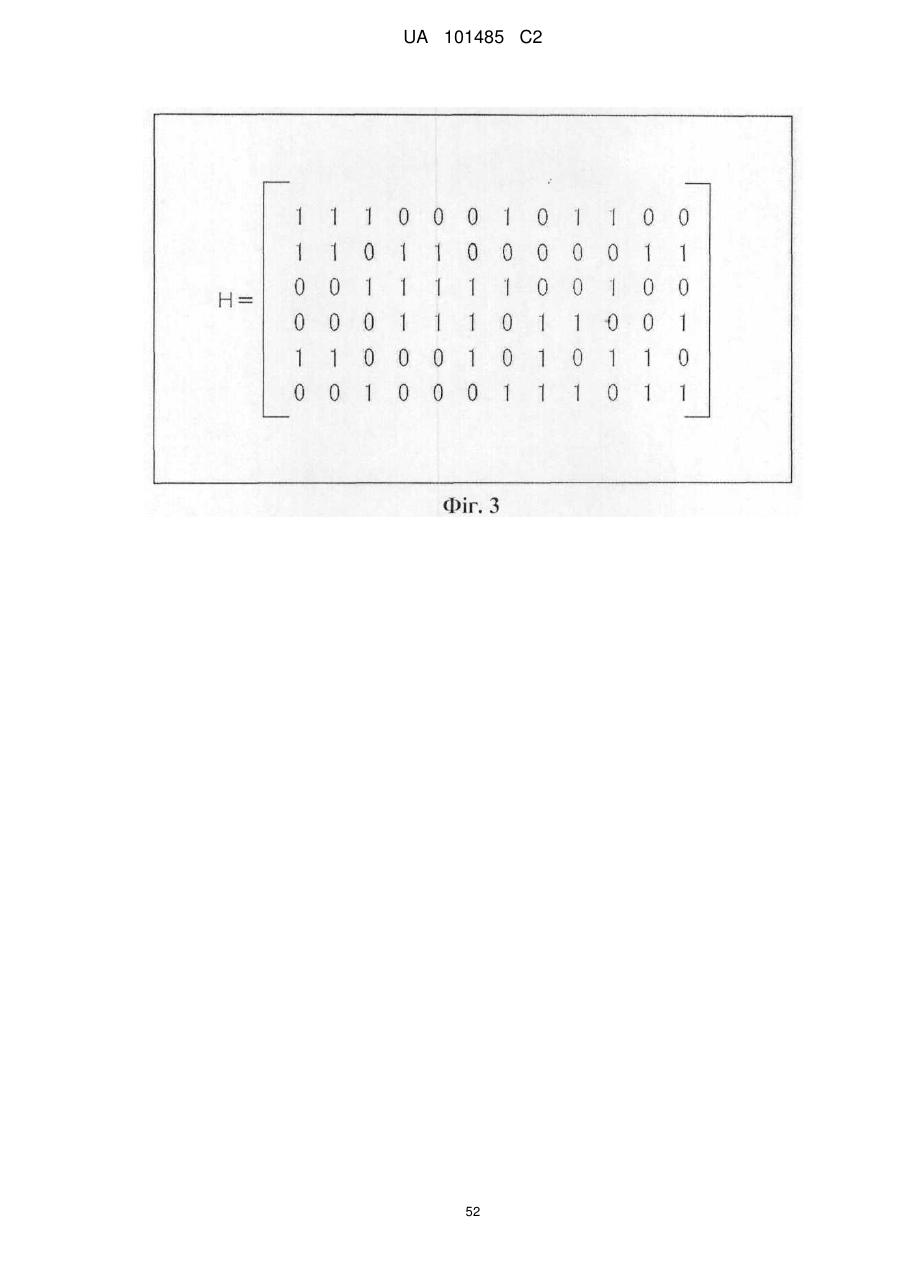

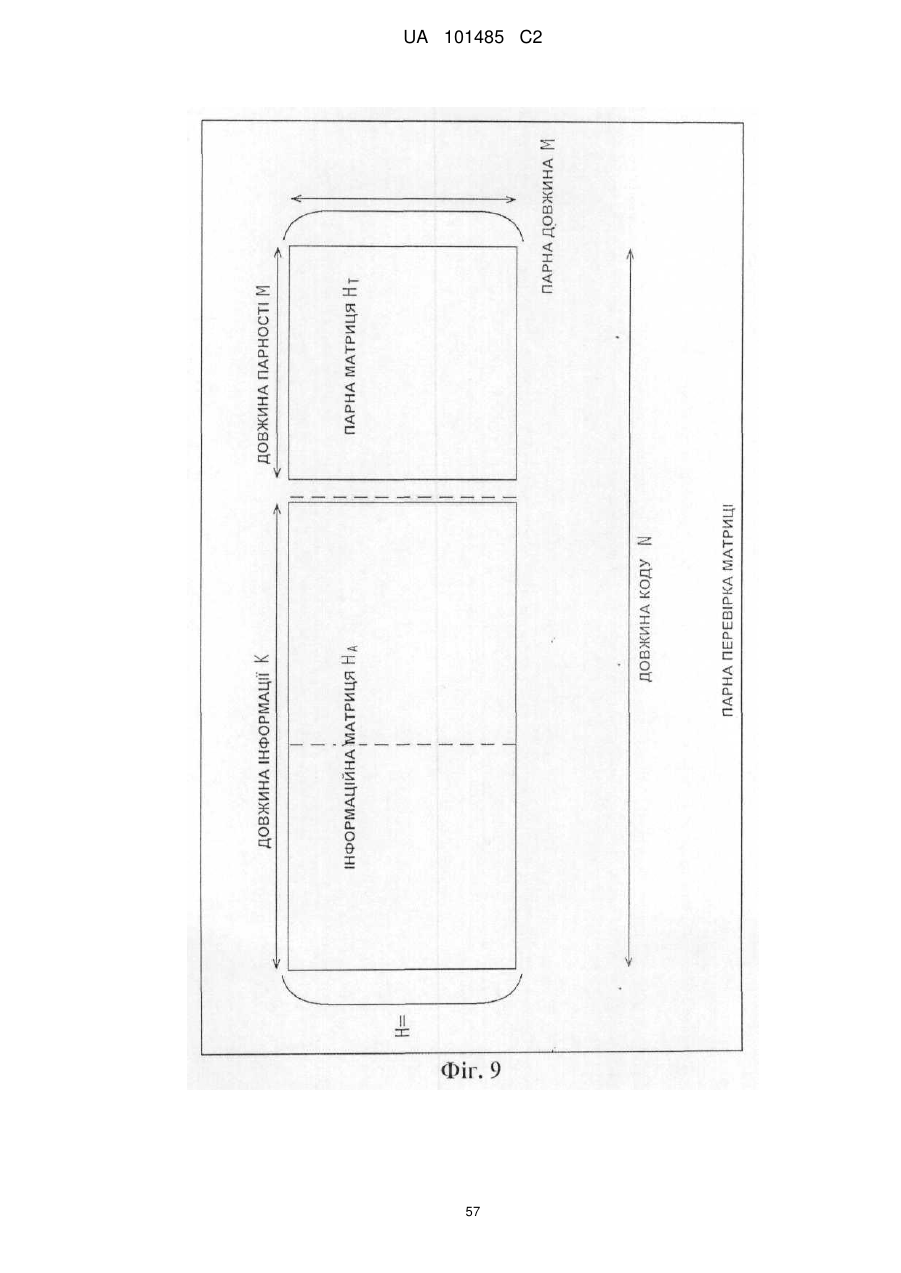

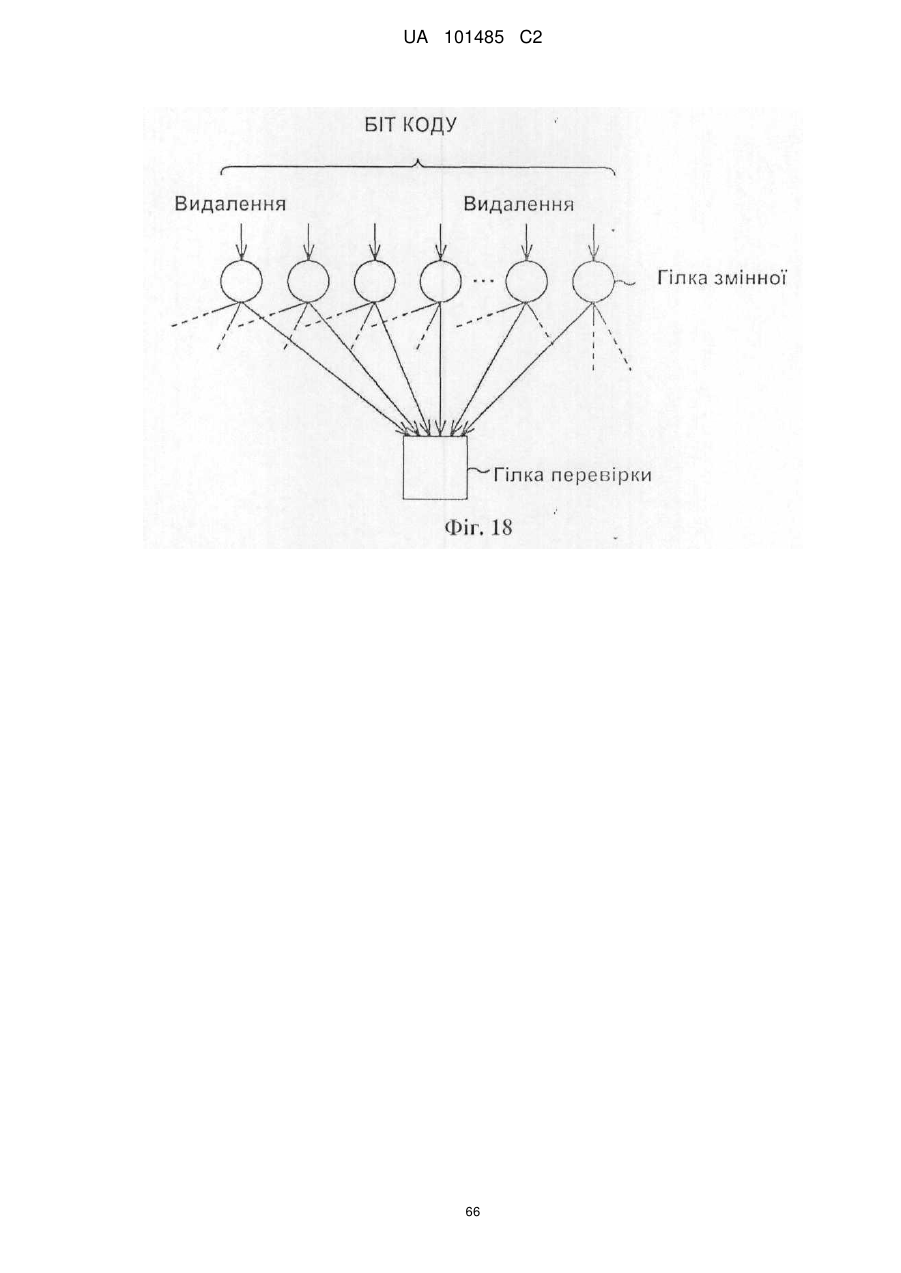

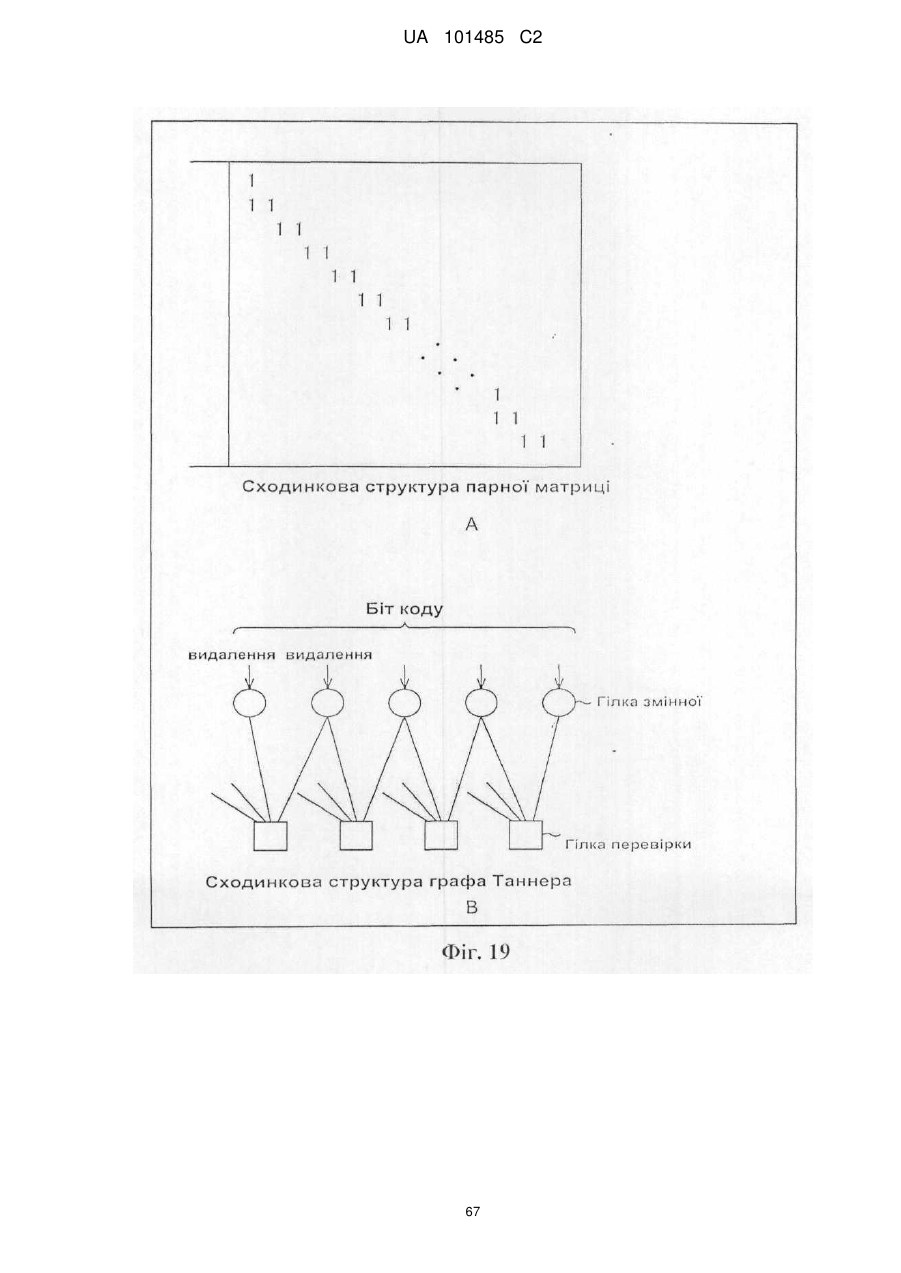

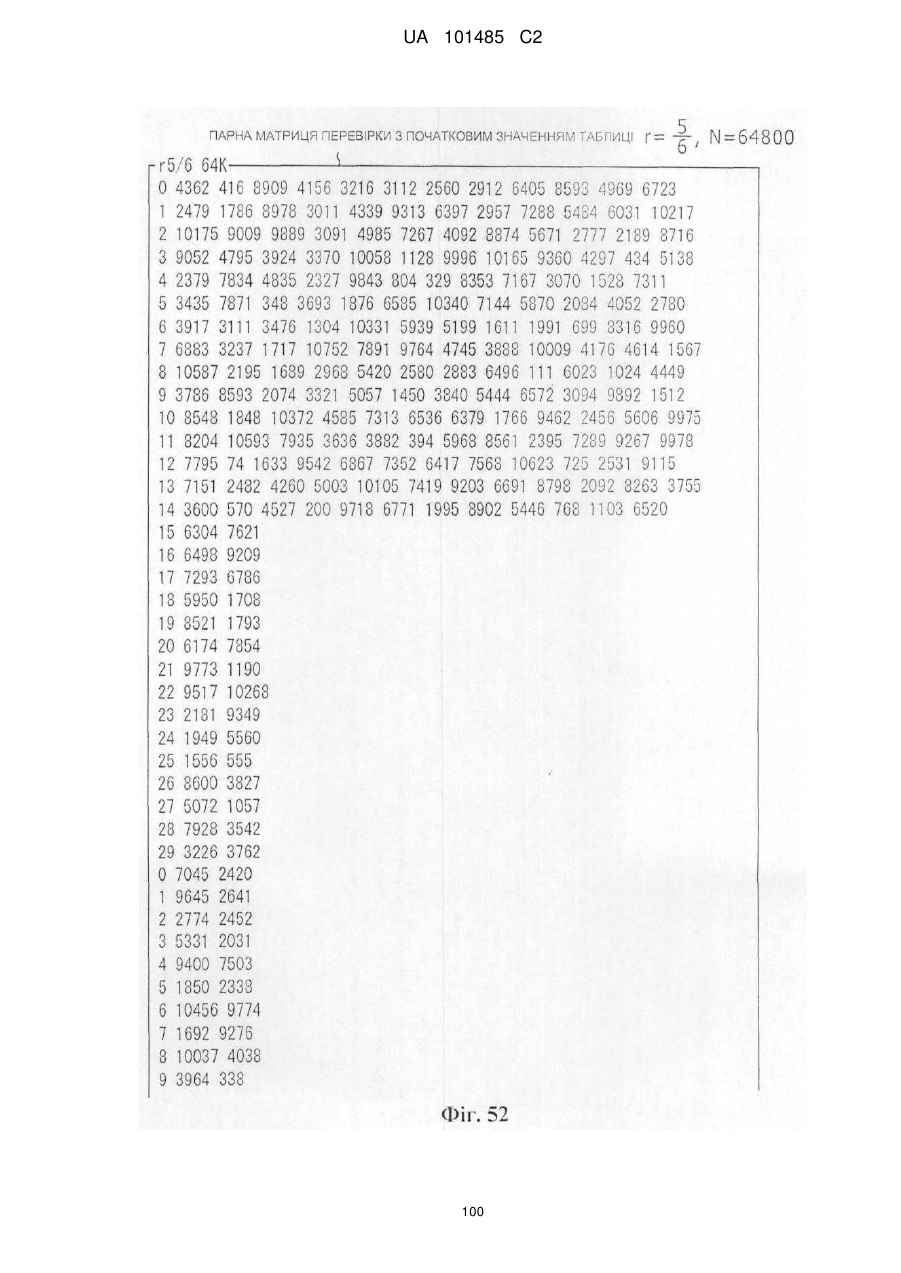

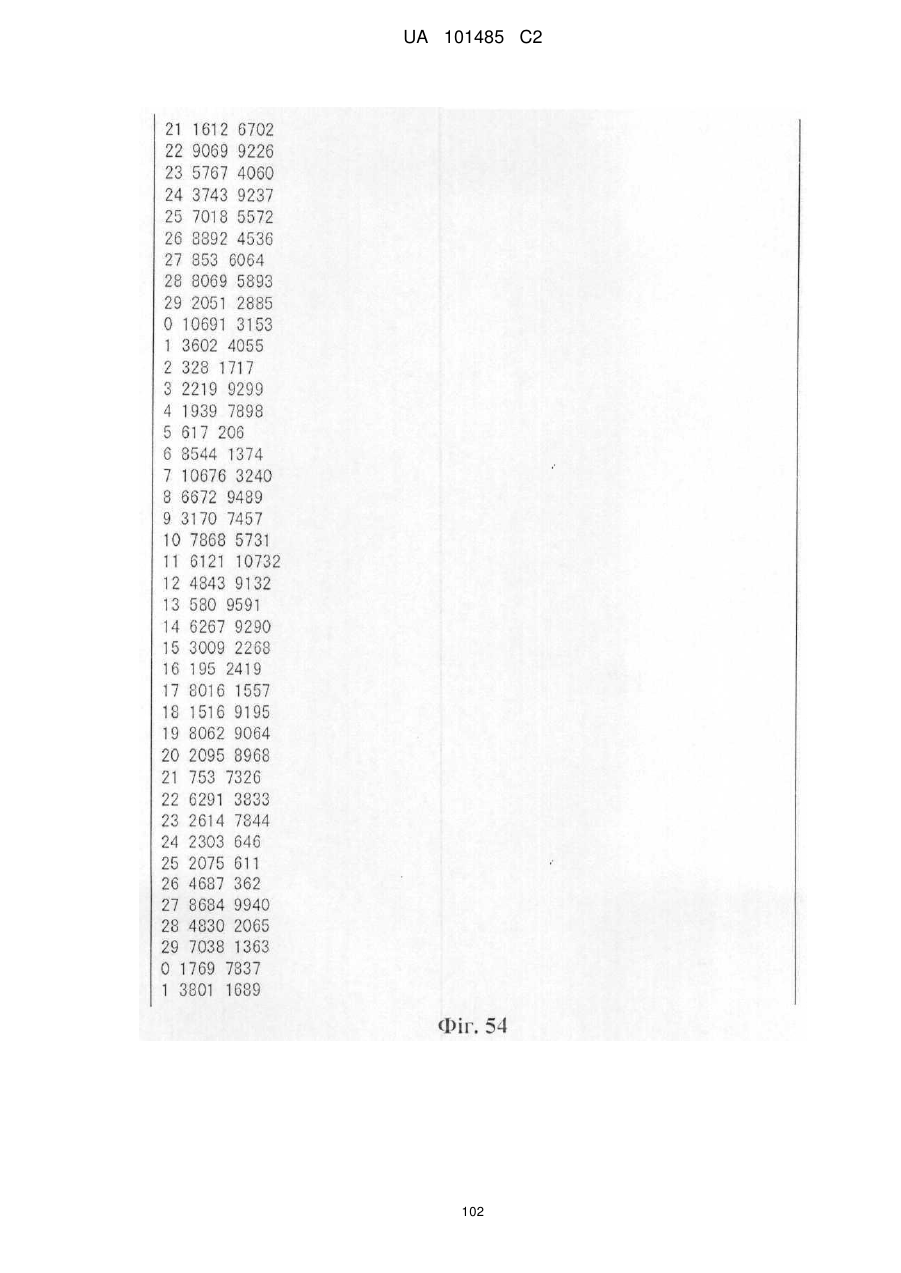

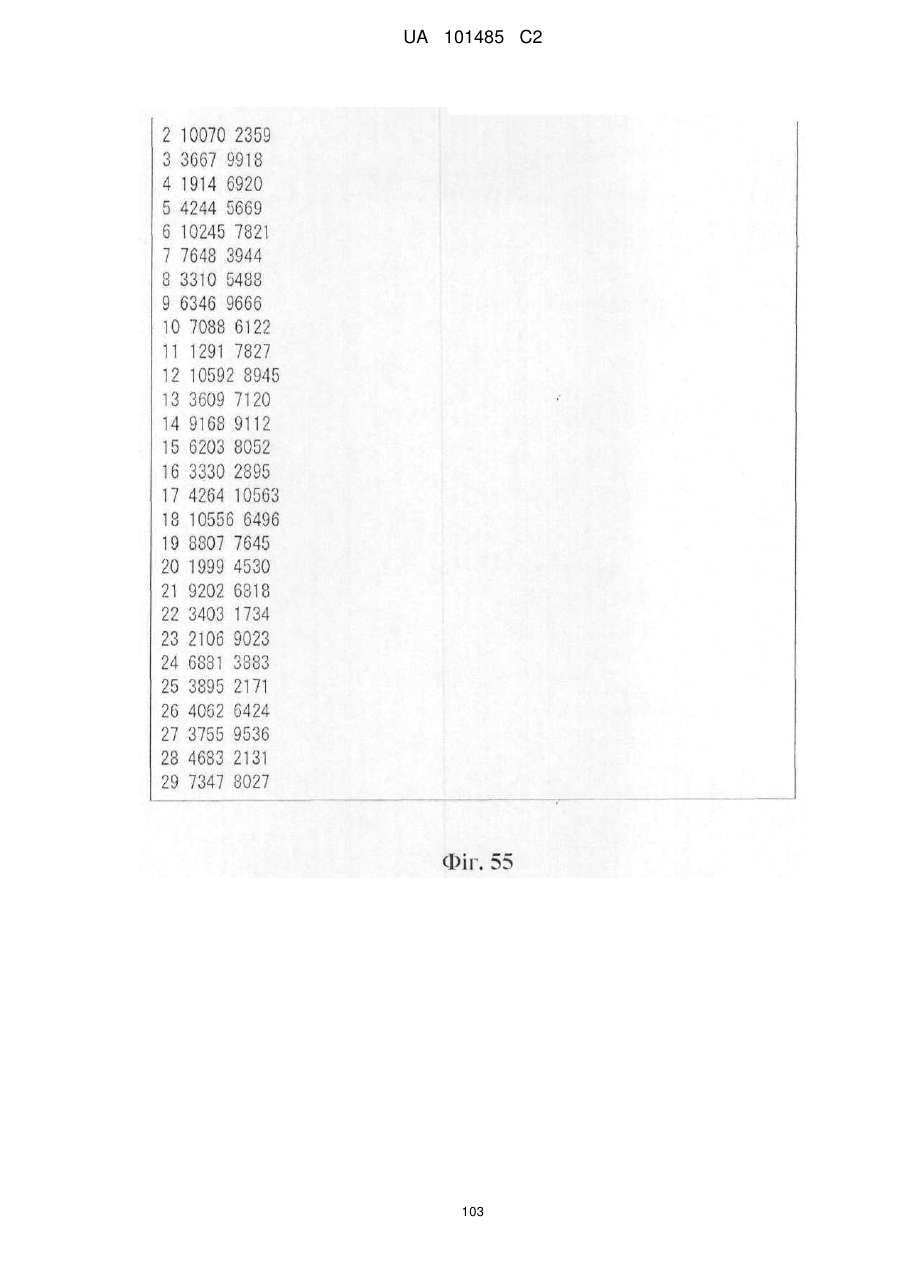

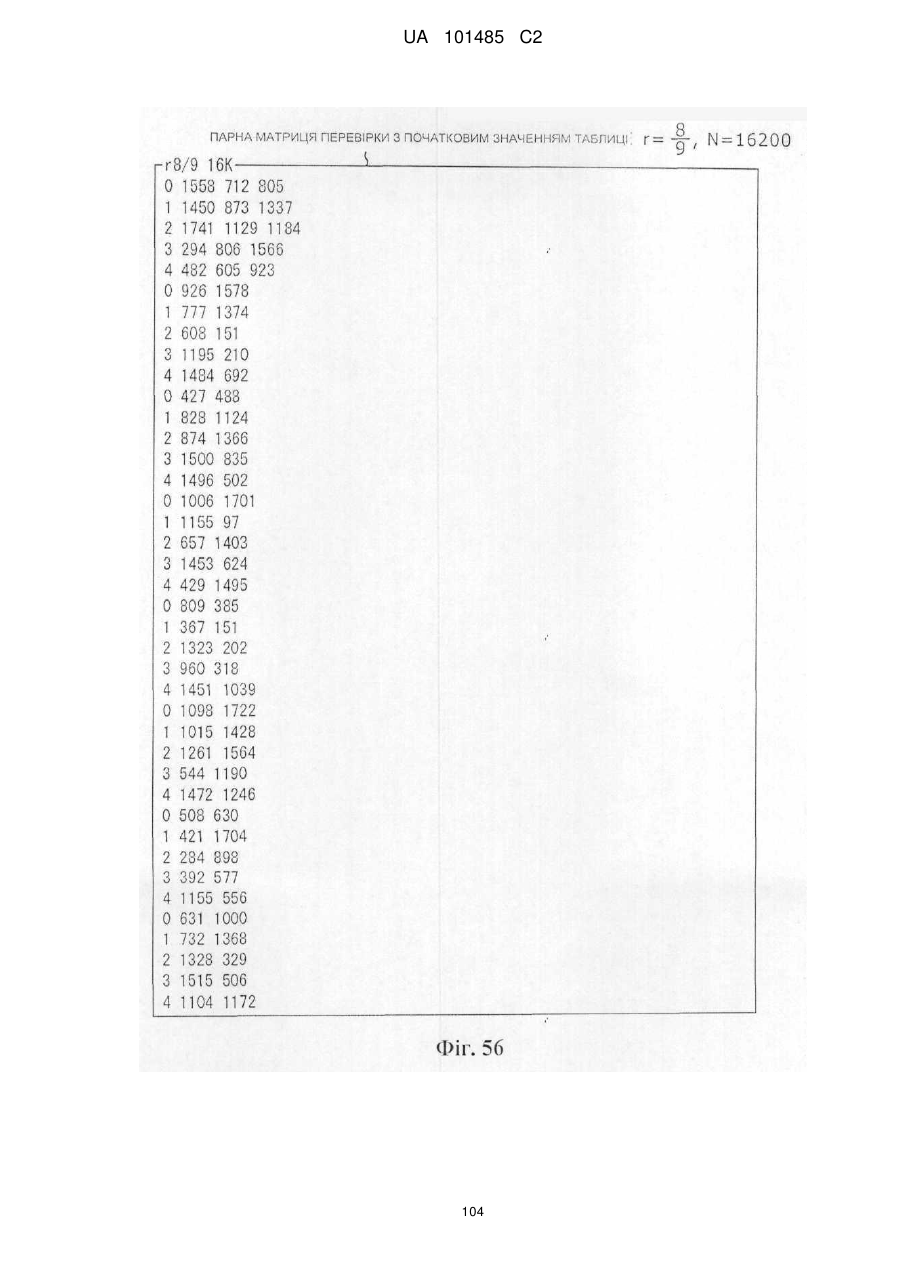

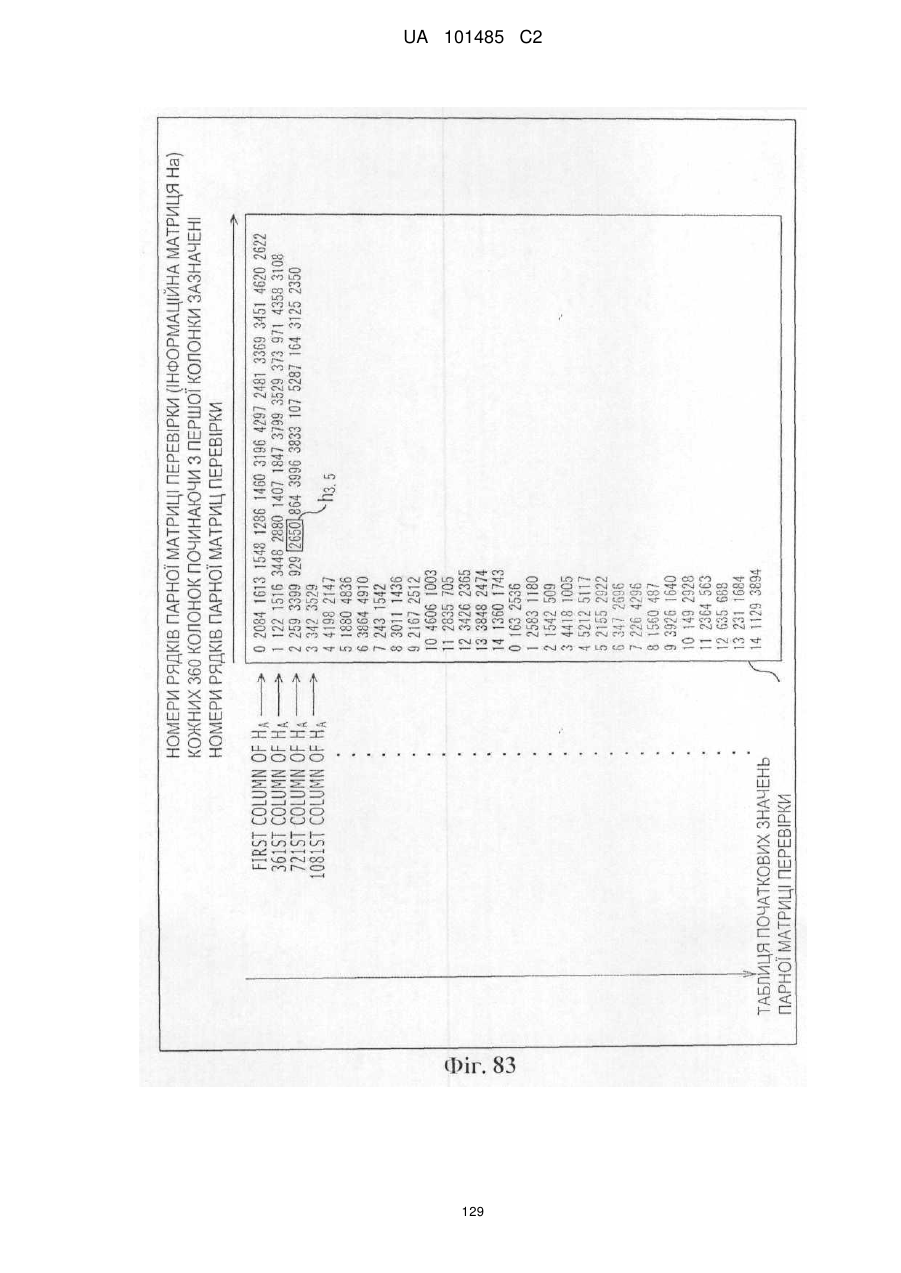

1. Пристрій обробки даних, який виконує перемежовування даних, що містить: засіб перемежовування парності, призначений для перемежовування парності, що полягає в перемежовуванні бітів парності коду низької щільності з контролем парності (LDPC), отриманого шляхом виконання кодування LDPC, відповідно до матриці перевірки на парність, в якому матриця парності, яка являє собою частину, що відповідає бітам парності коду LDPC, має ступеневу структуру, індивідуально відносно положень інших бітів парності.

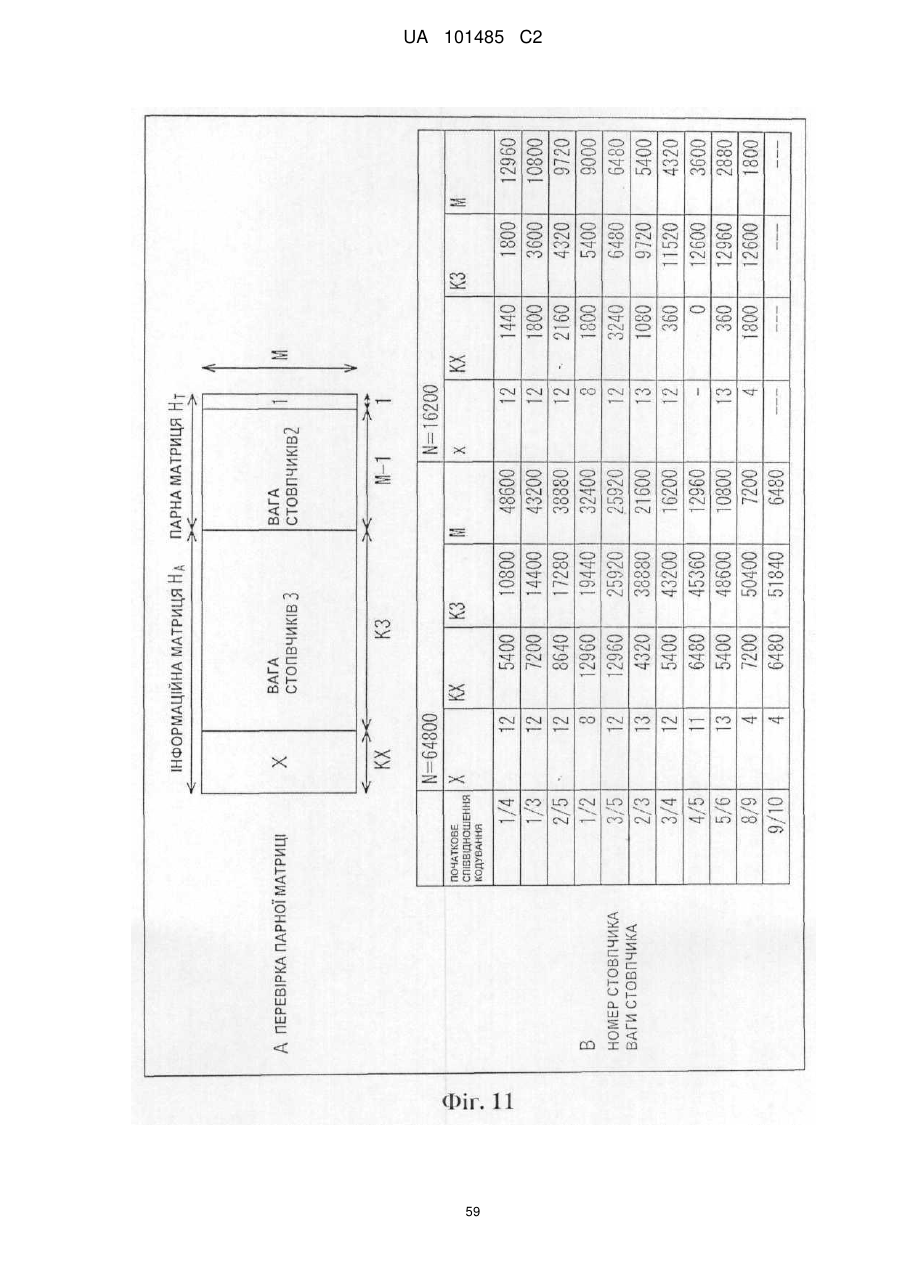

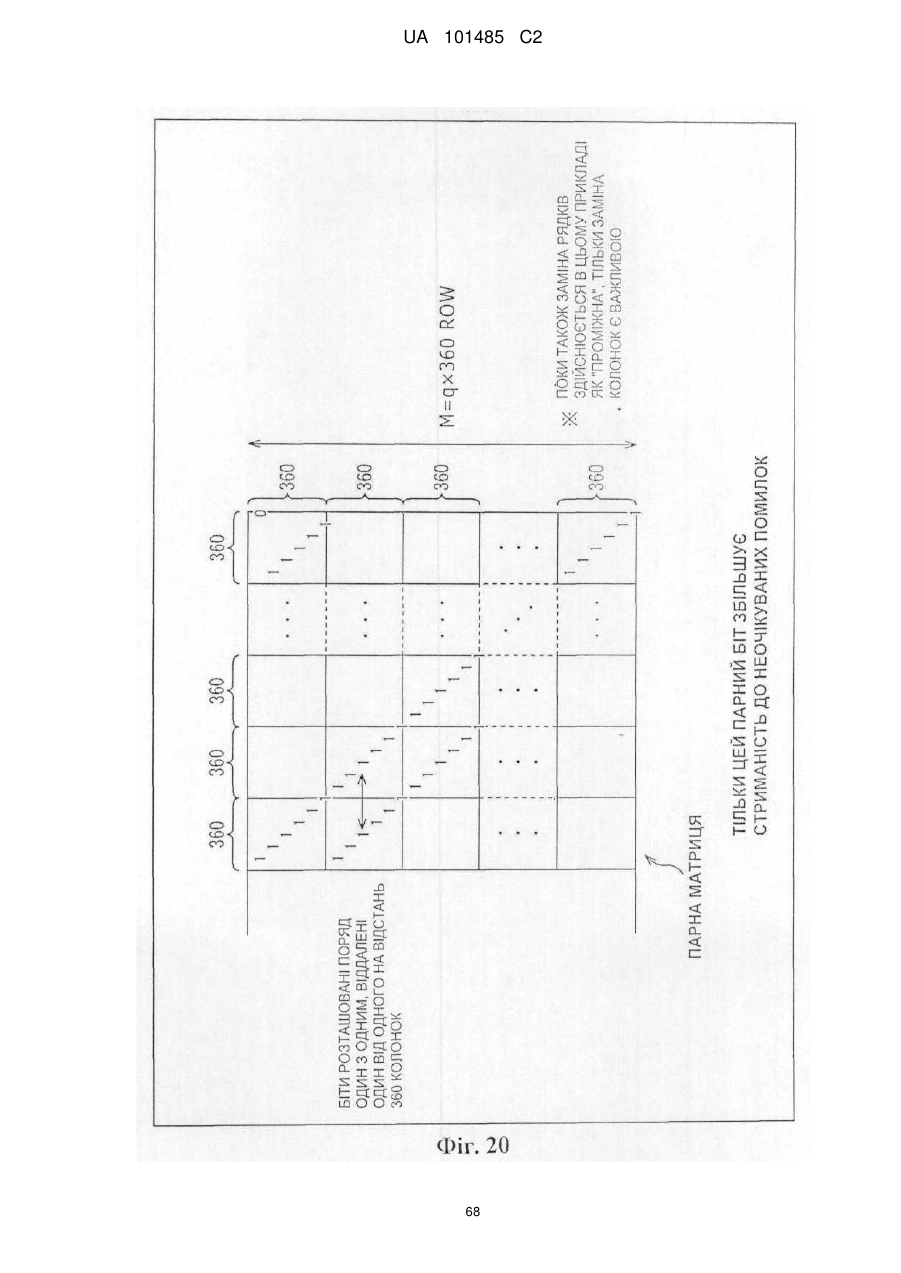

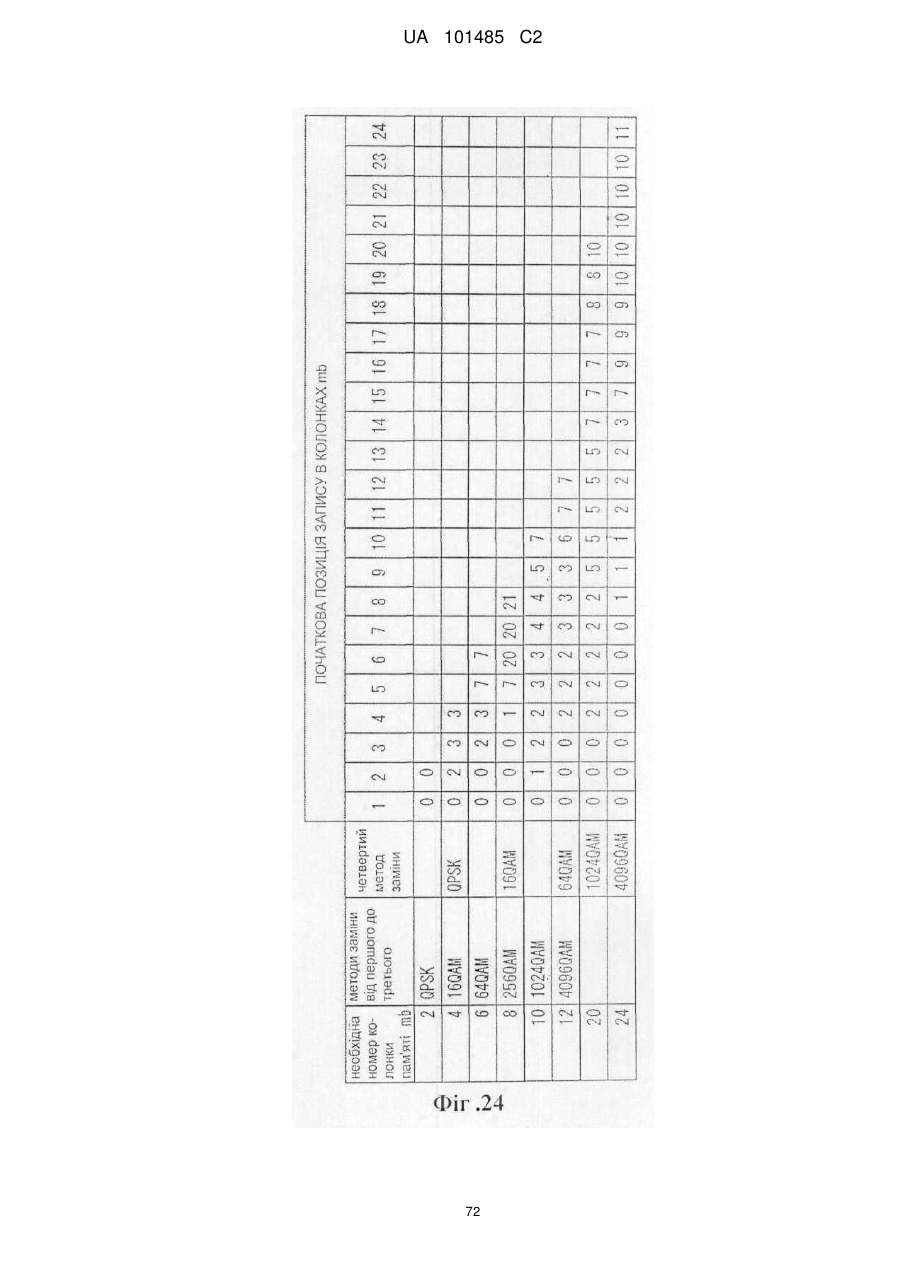

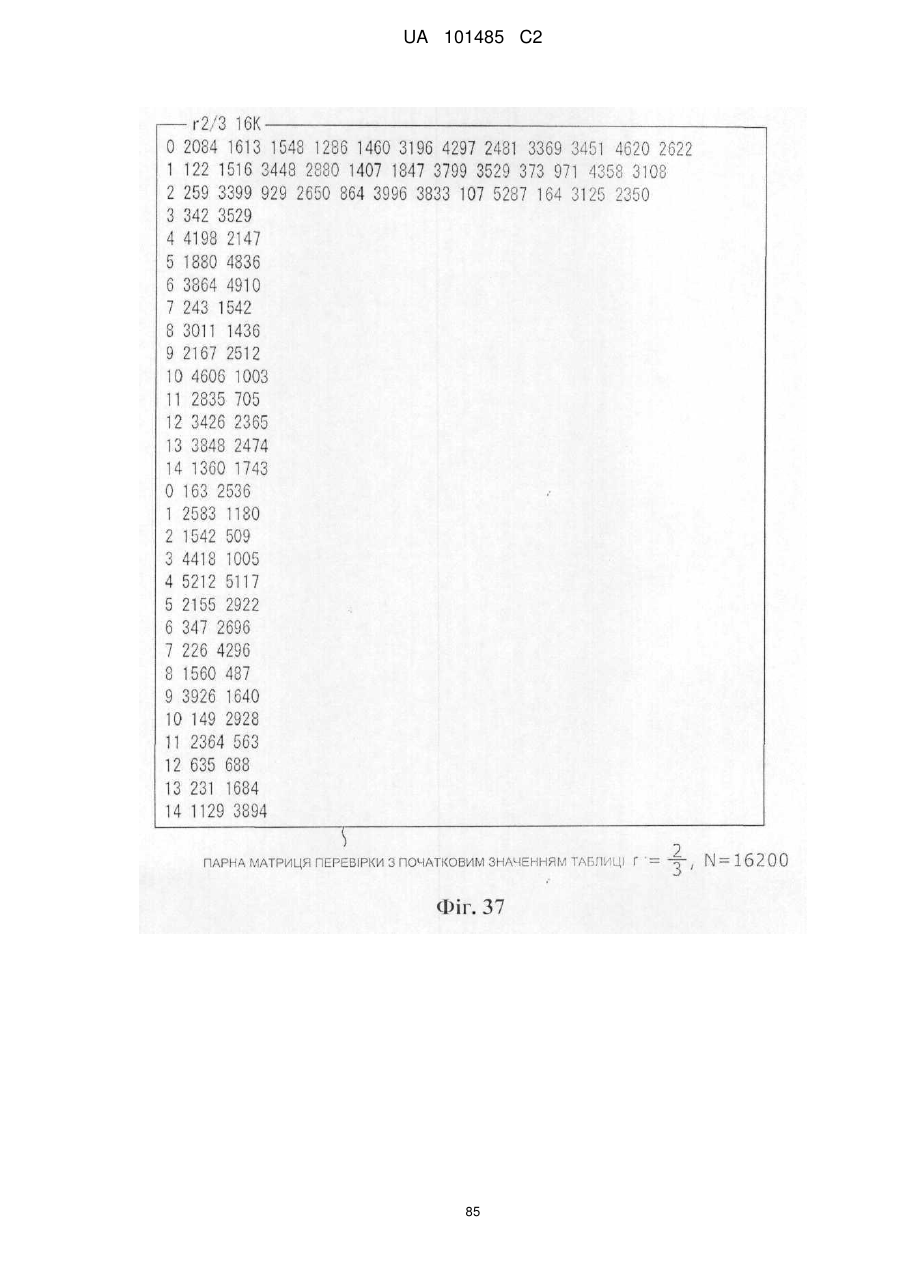

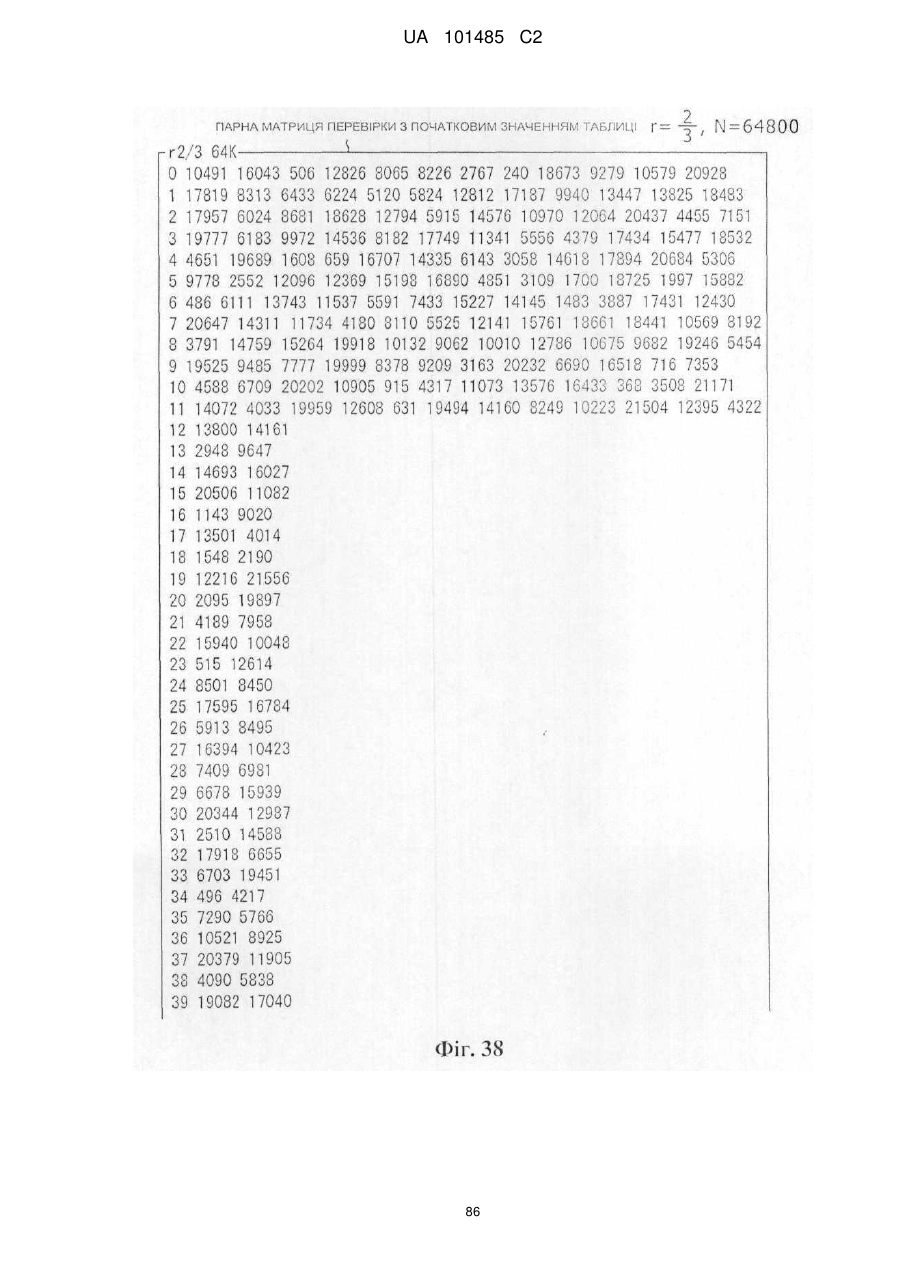

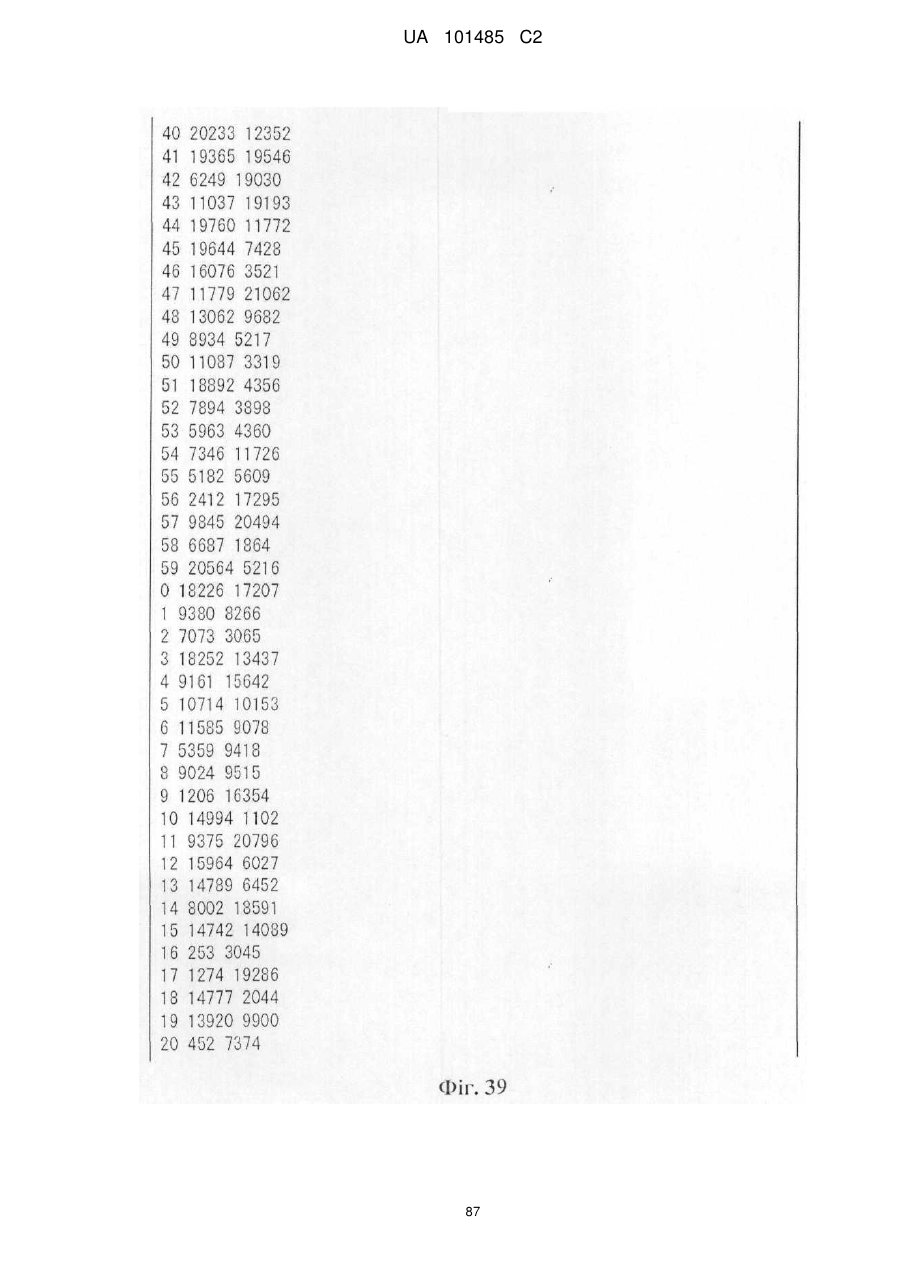

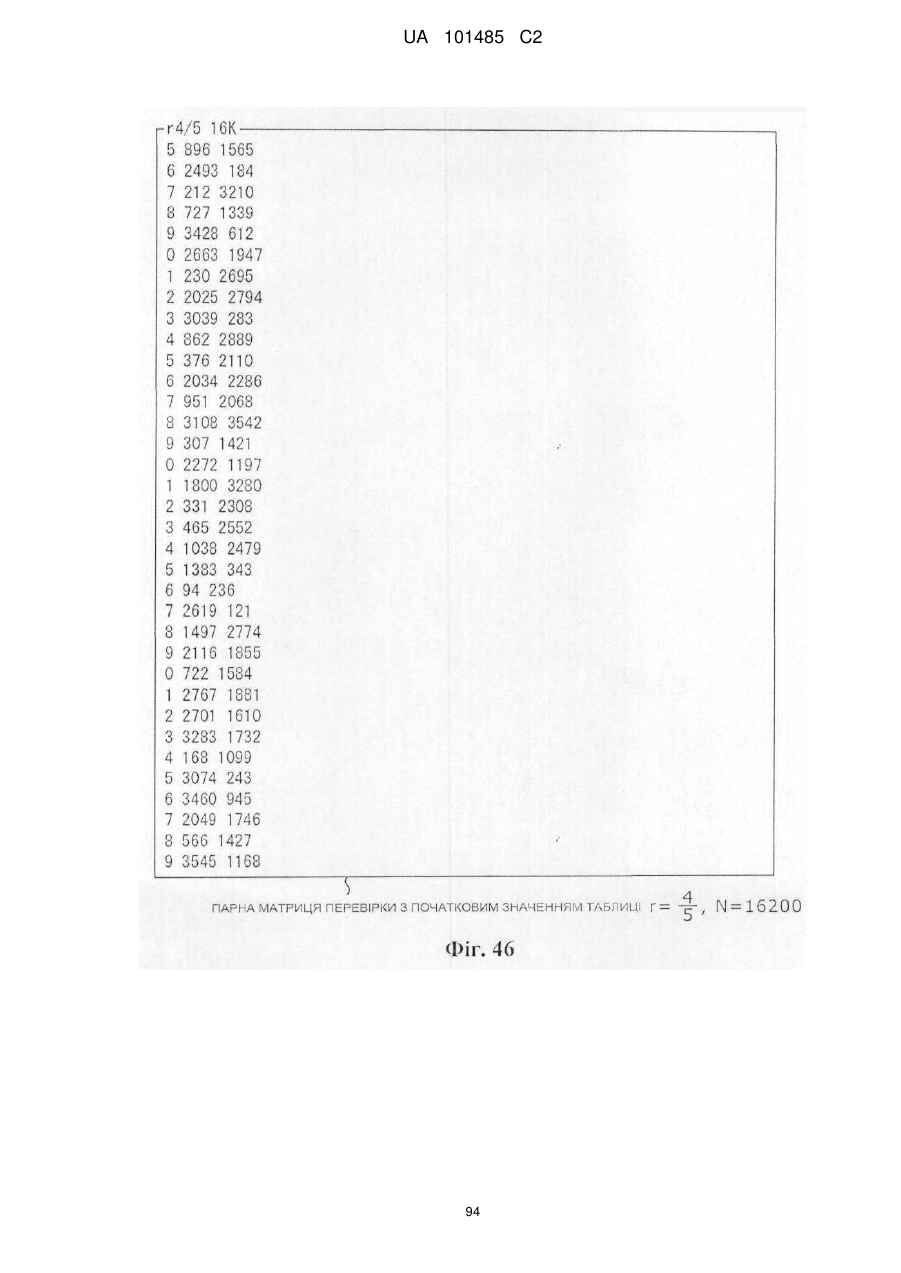

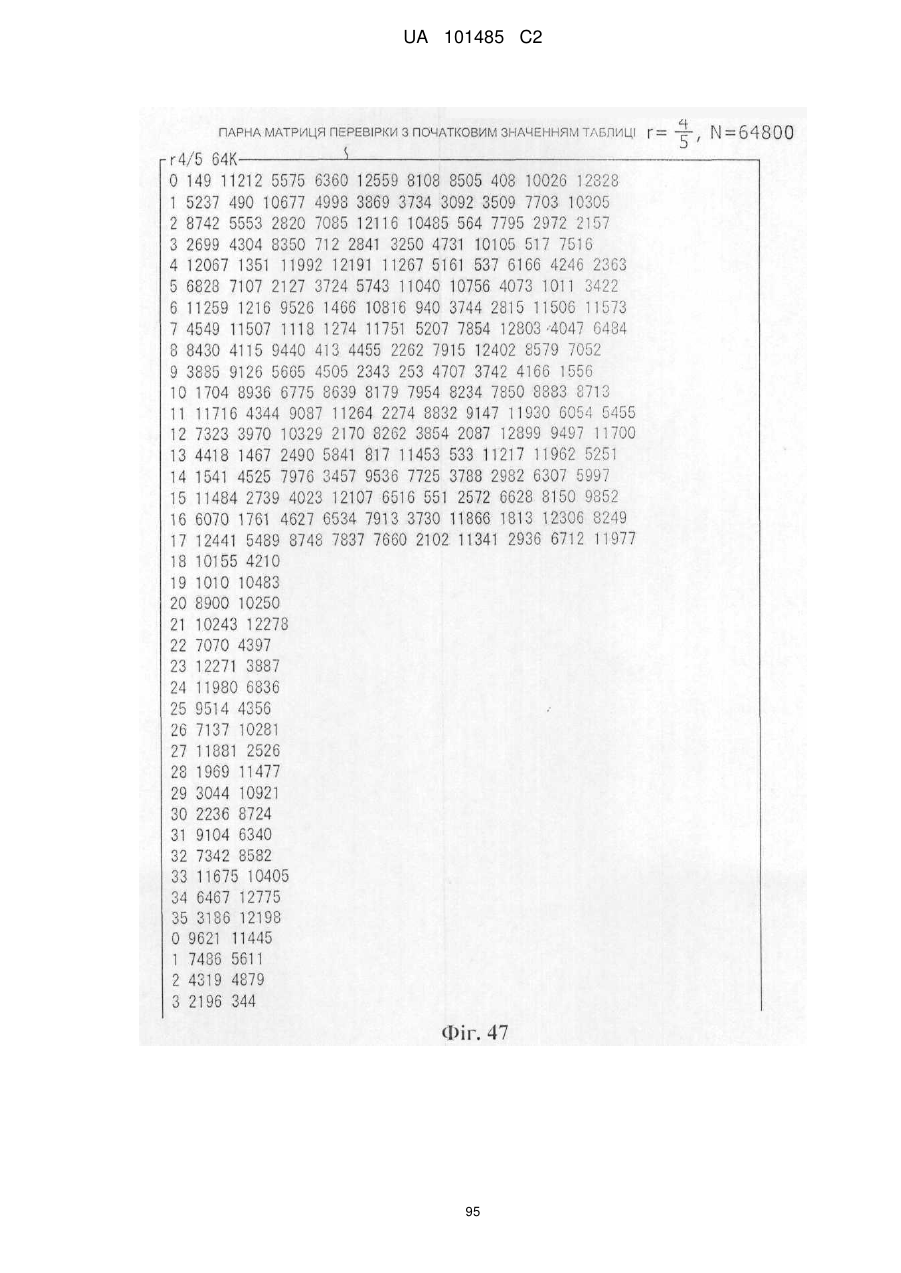

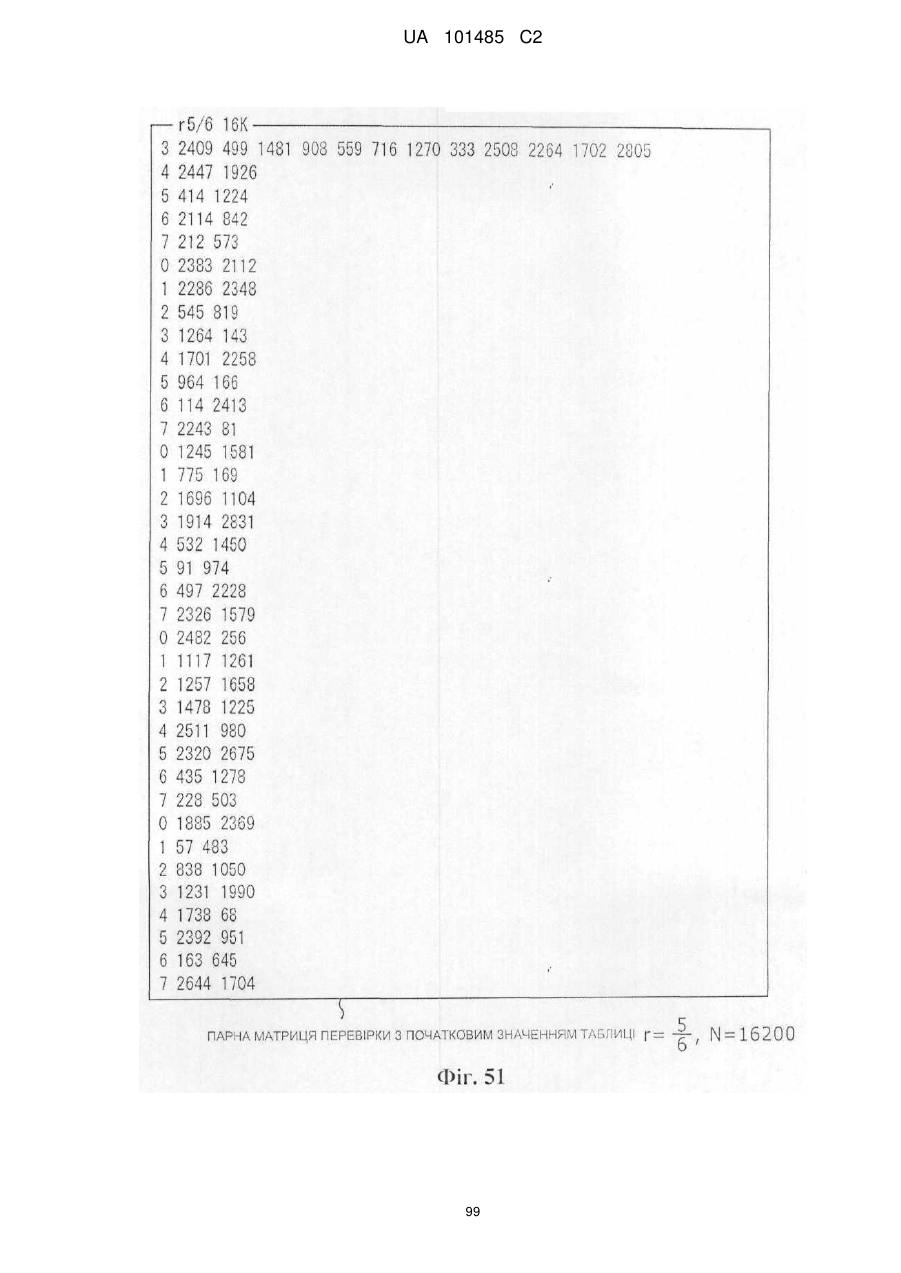

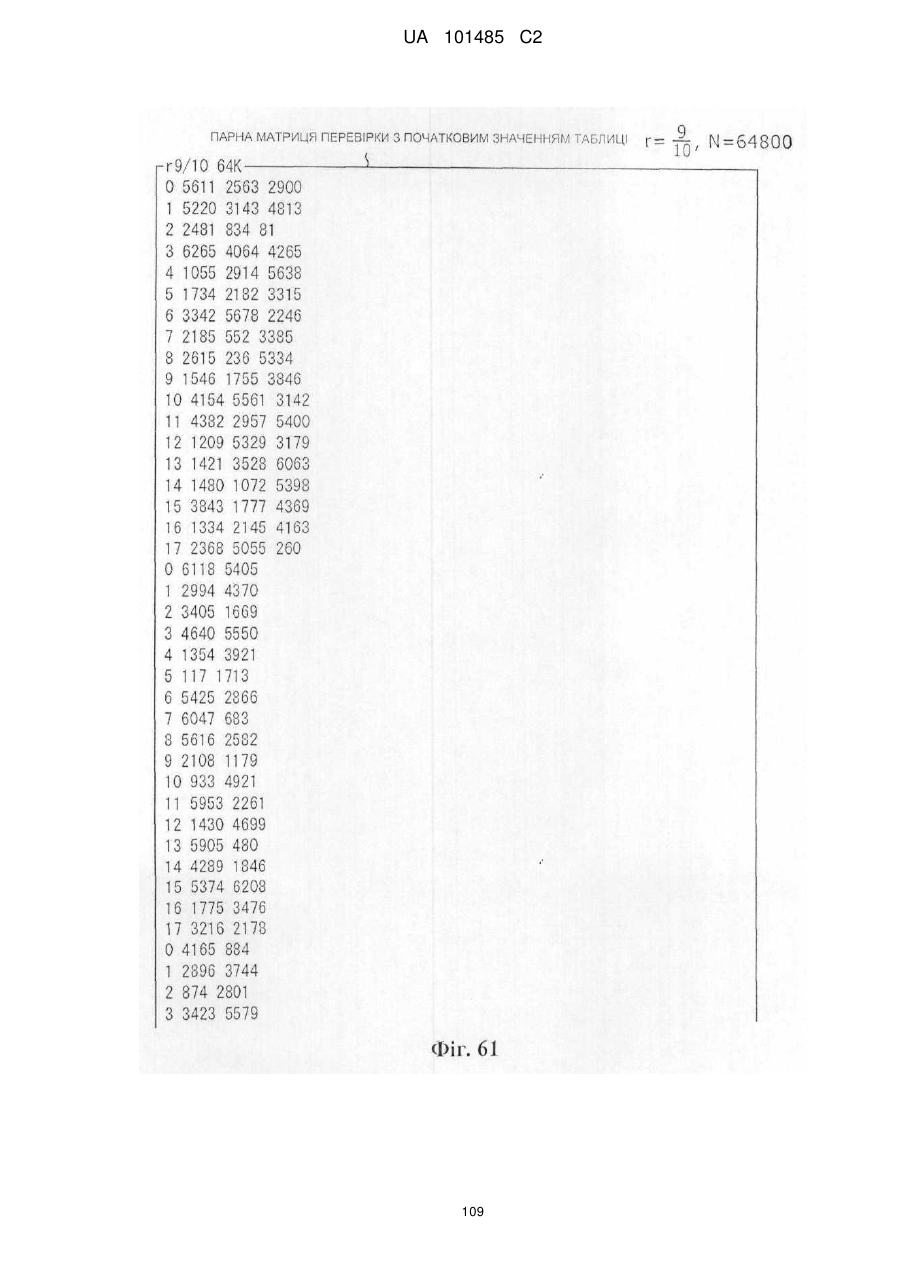

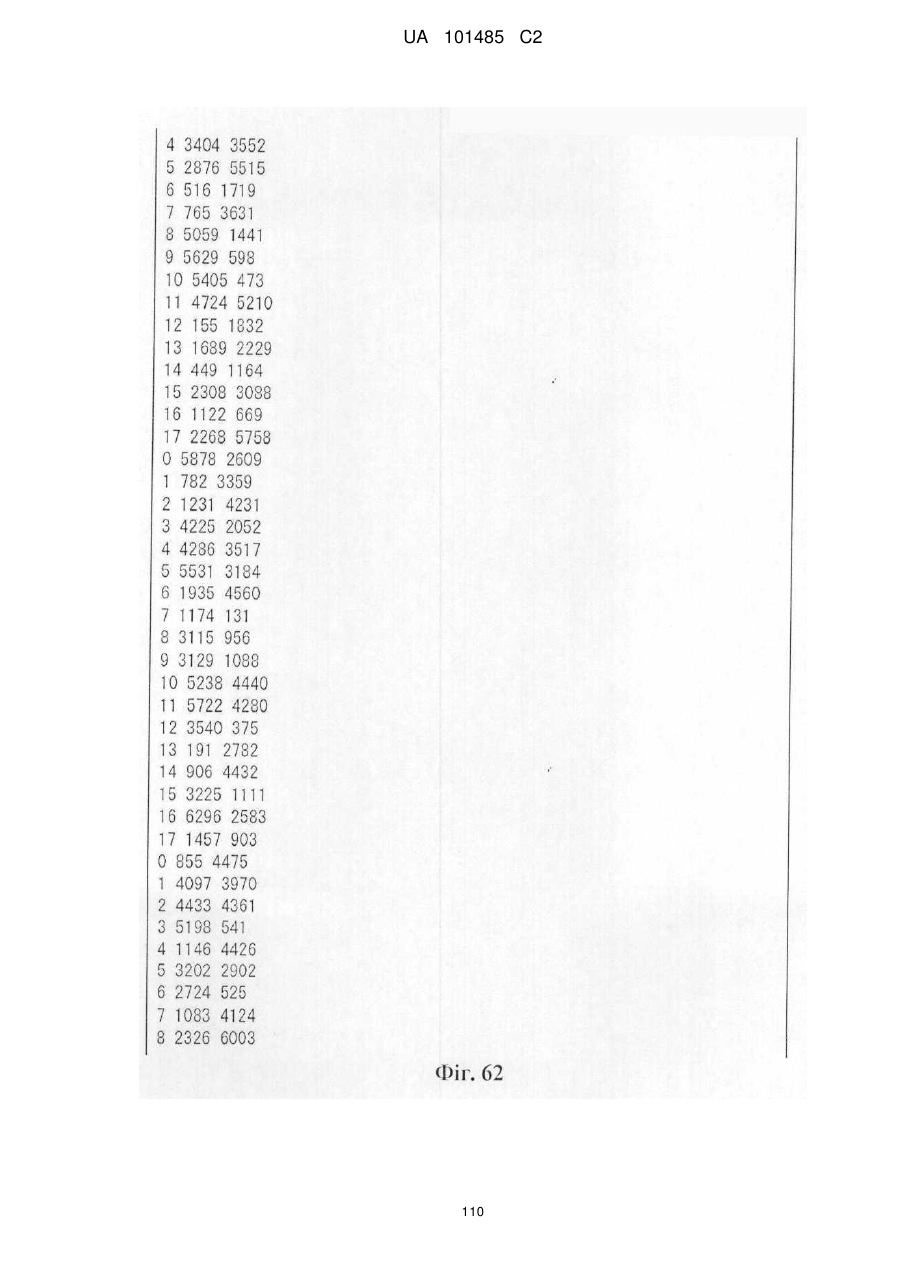

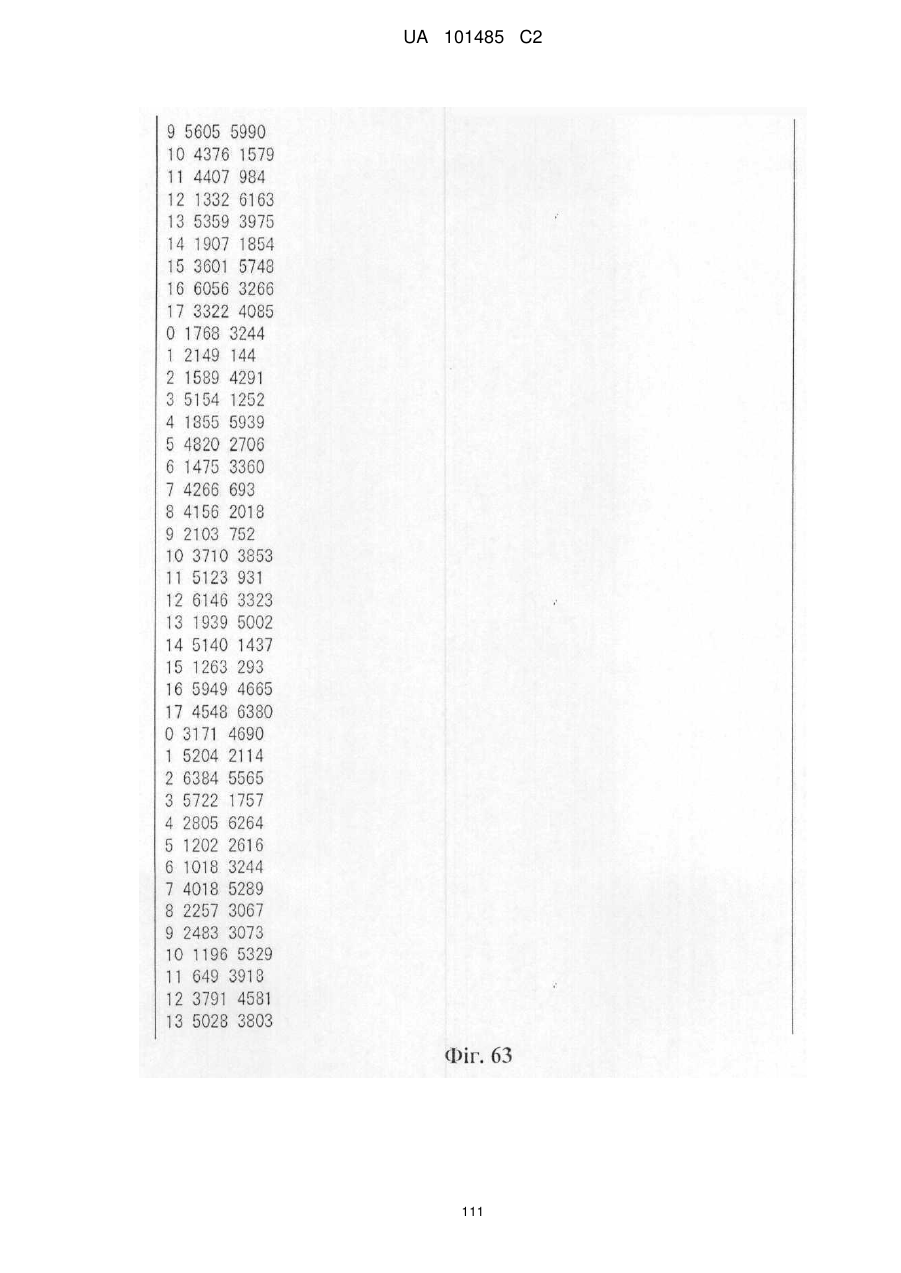

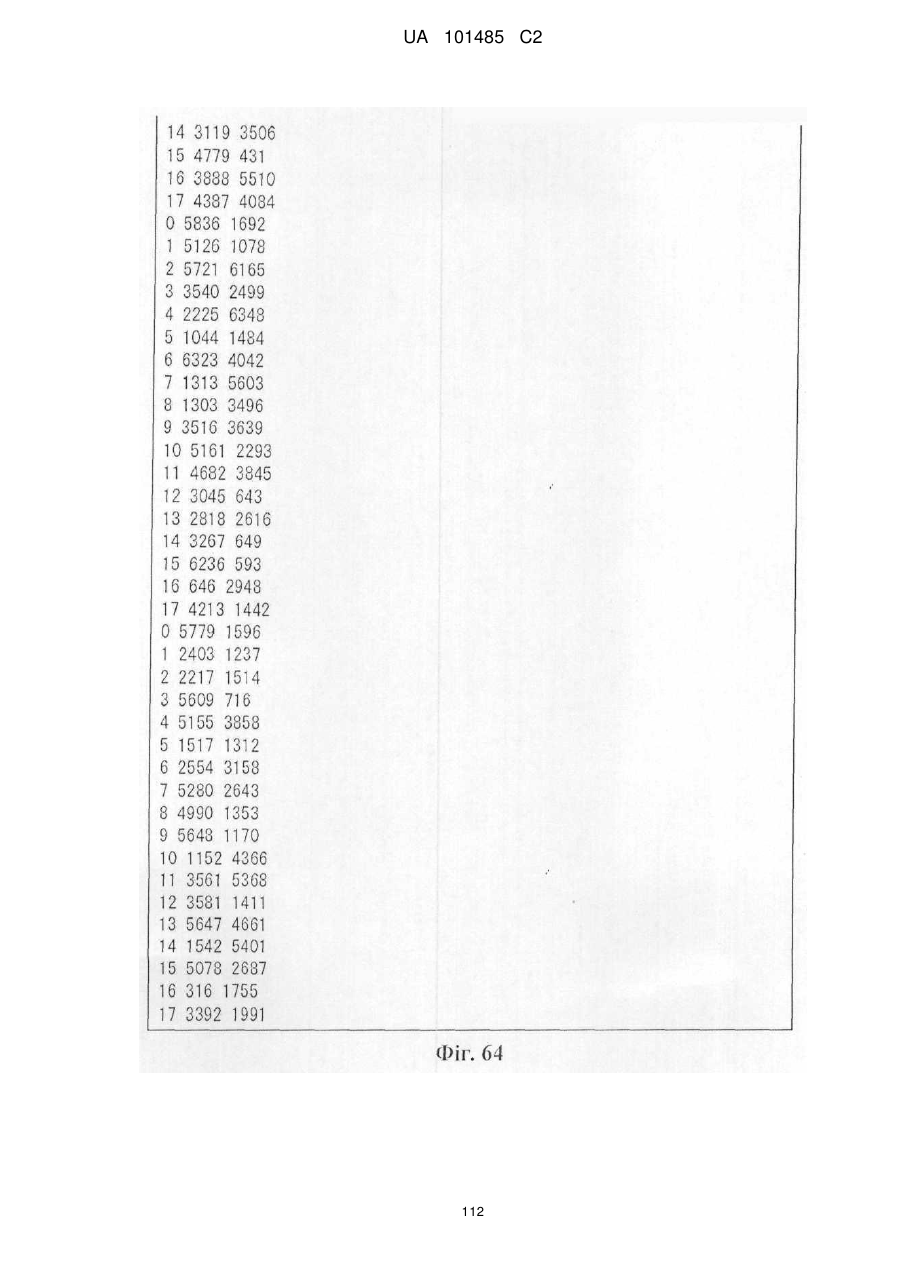

2. Пристрій обробки даних за п. 1, який відрізняється тим, що кількість Μ бітів для бітів парності коду LDPC має значення, що не є простим числом; і, де два дільники кількості Μ бітів для бітів парності, крім 1 і М, добуток яких дорівнює кількості Μ бітів парності, представлені як Ρ і q, кількість бітів для інформаційних бітів коду LDPC представлена як K,

ціле число, що дорівнює або більше за 0, але менше за Р, представлене як х, і інше ціле число, що дорівнює або більше за 0, але менше q, представлене як у, згаданий засіб перемежовування парності виконує перемежовування K+qx+y+1-ого кодового біта з бітів парності (біти від K+1-ого до K+М-ого кодових бітів коду LDPC) в положення K+Ру+х+ 1-ого кодового біта.

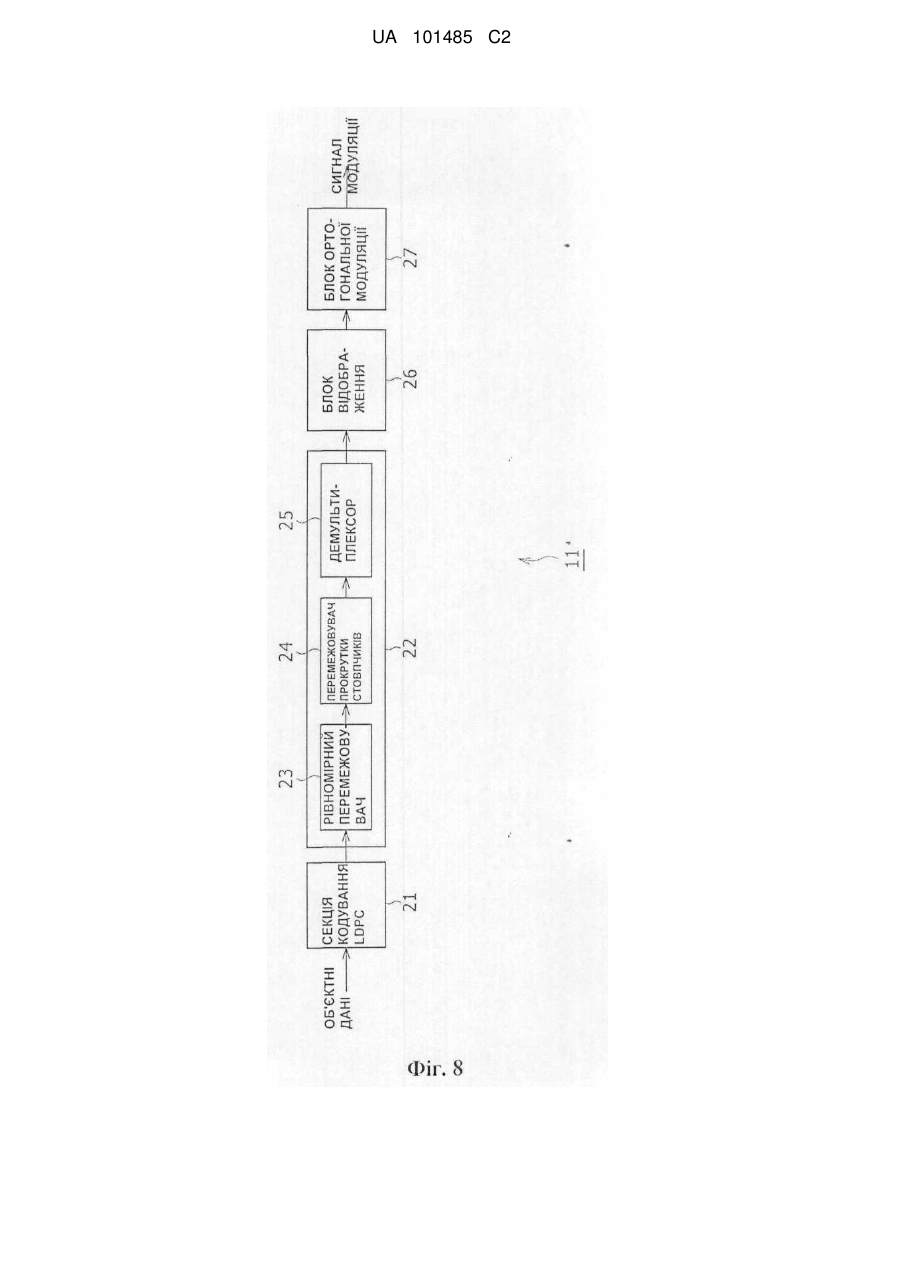

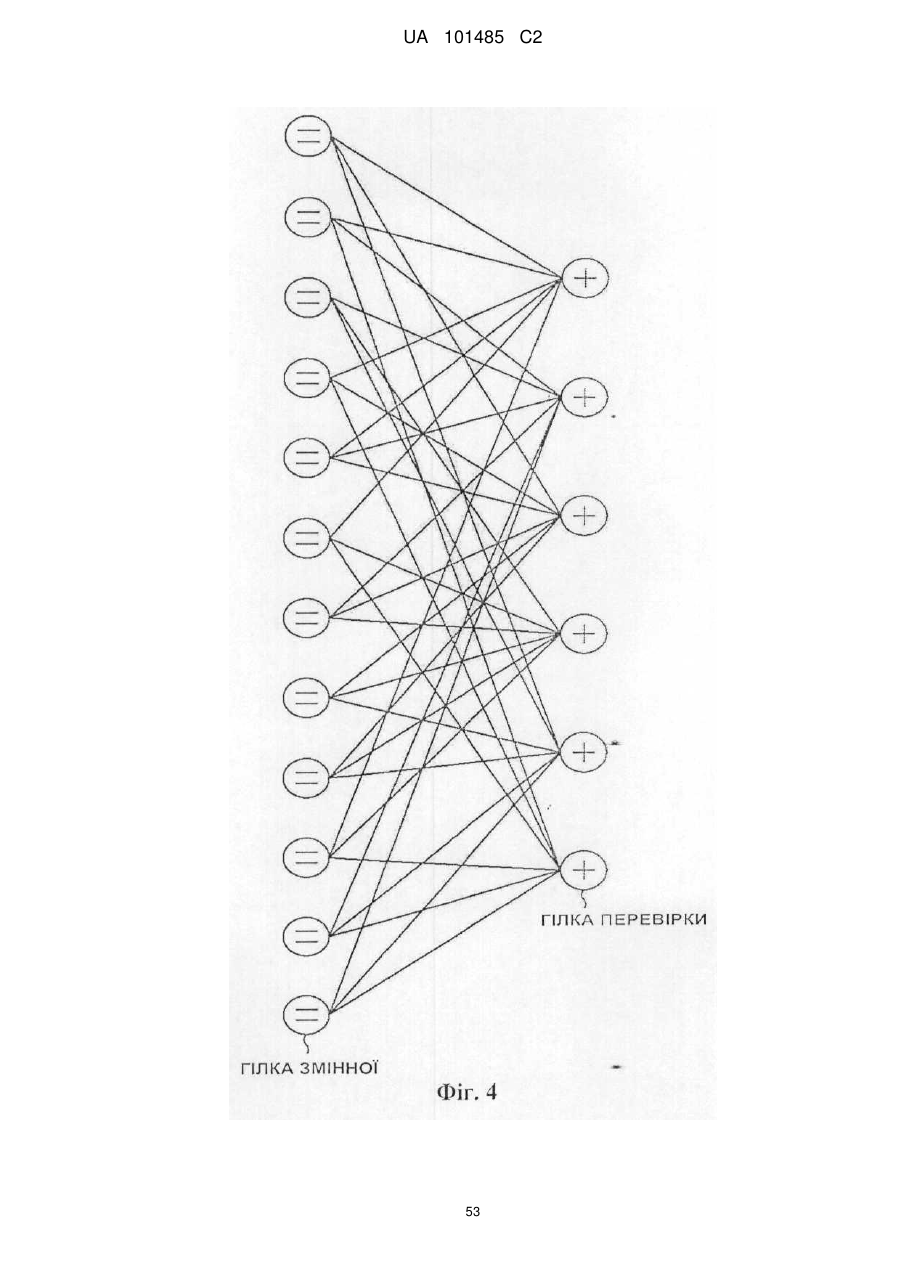

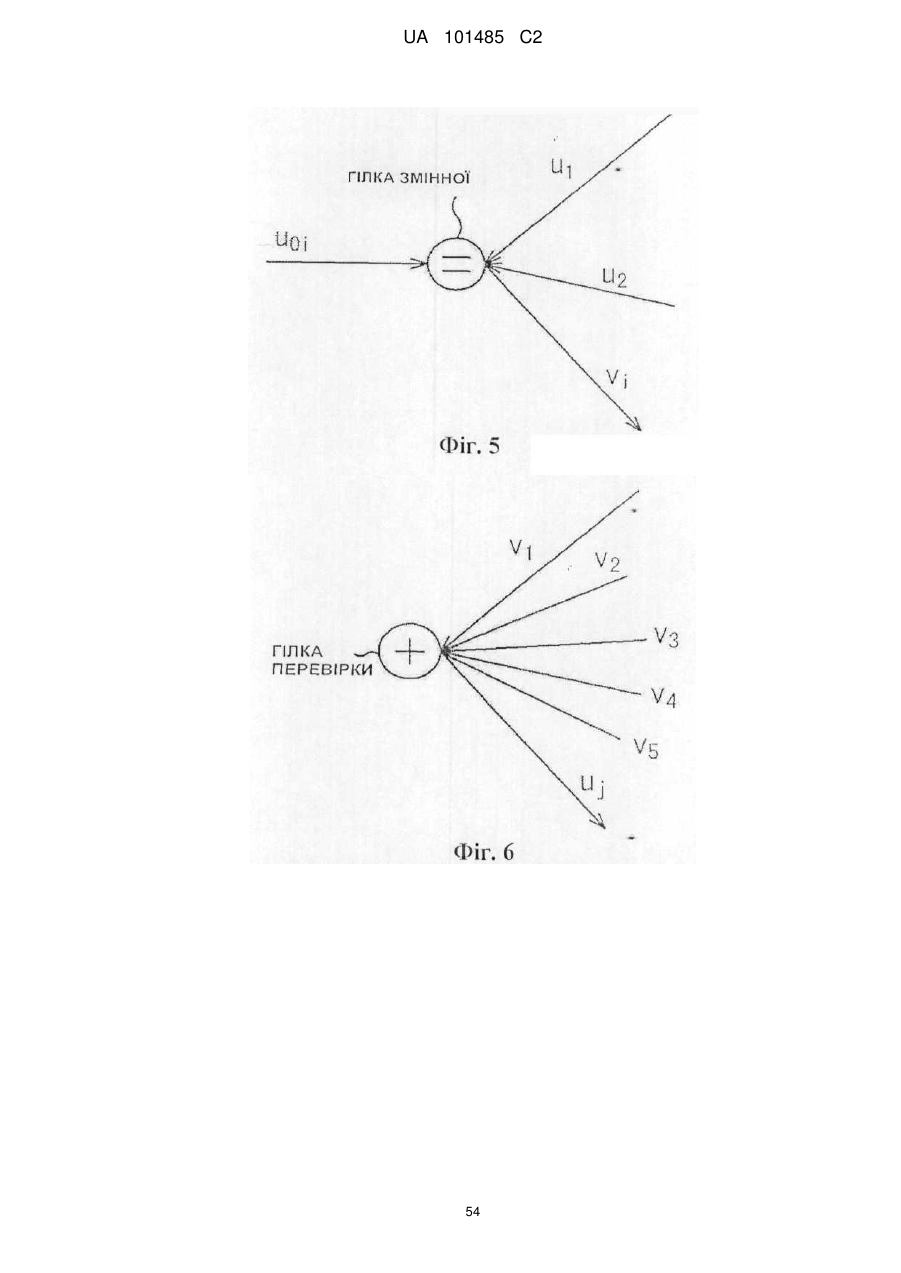

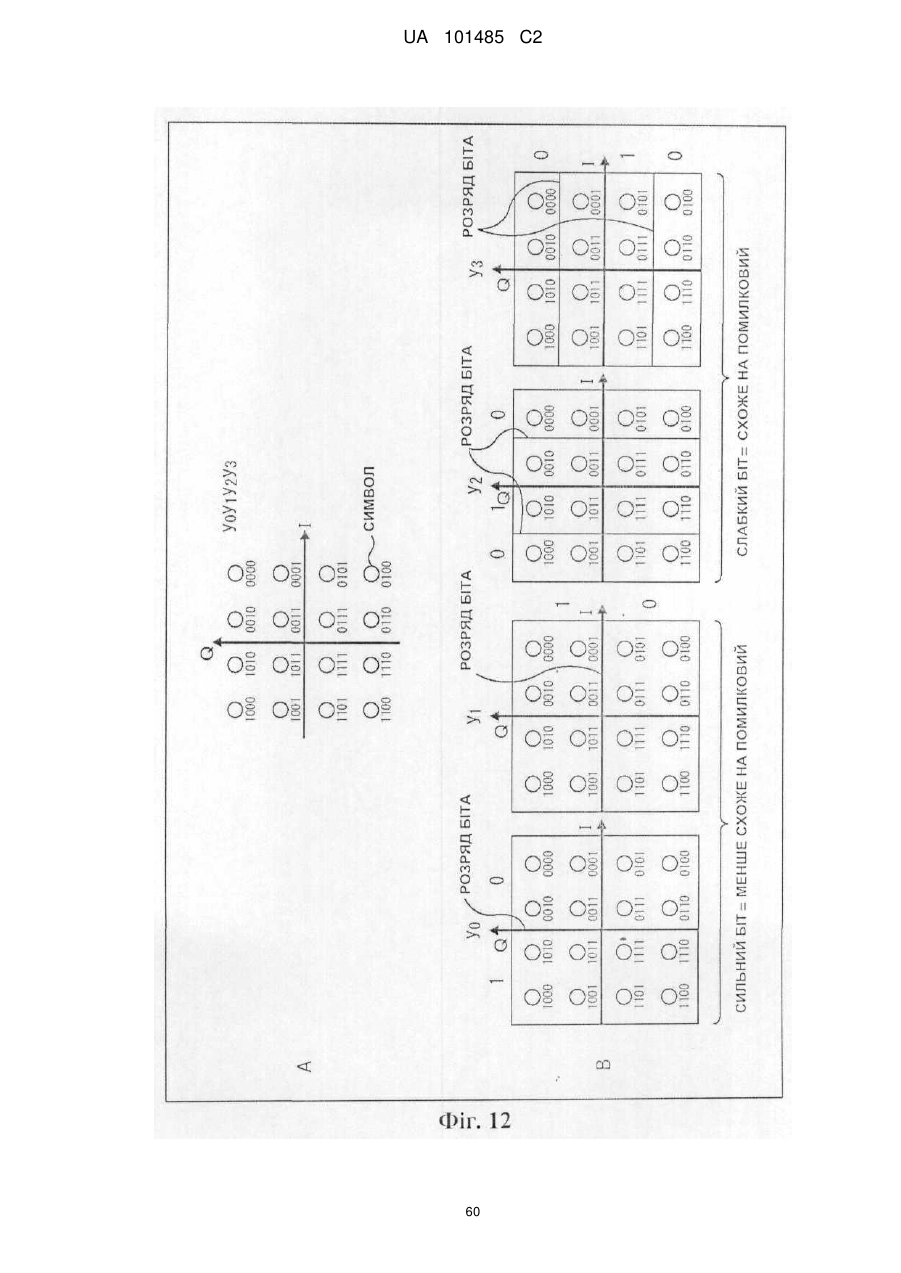

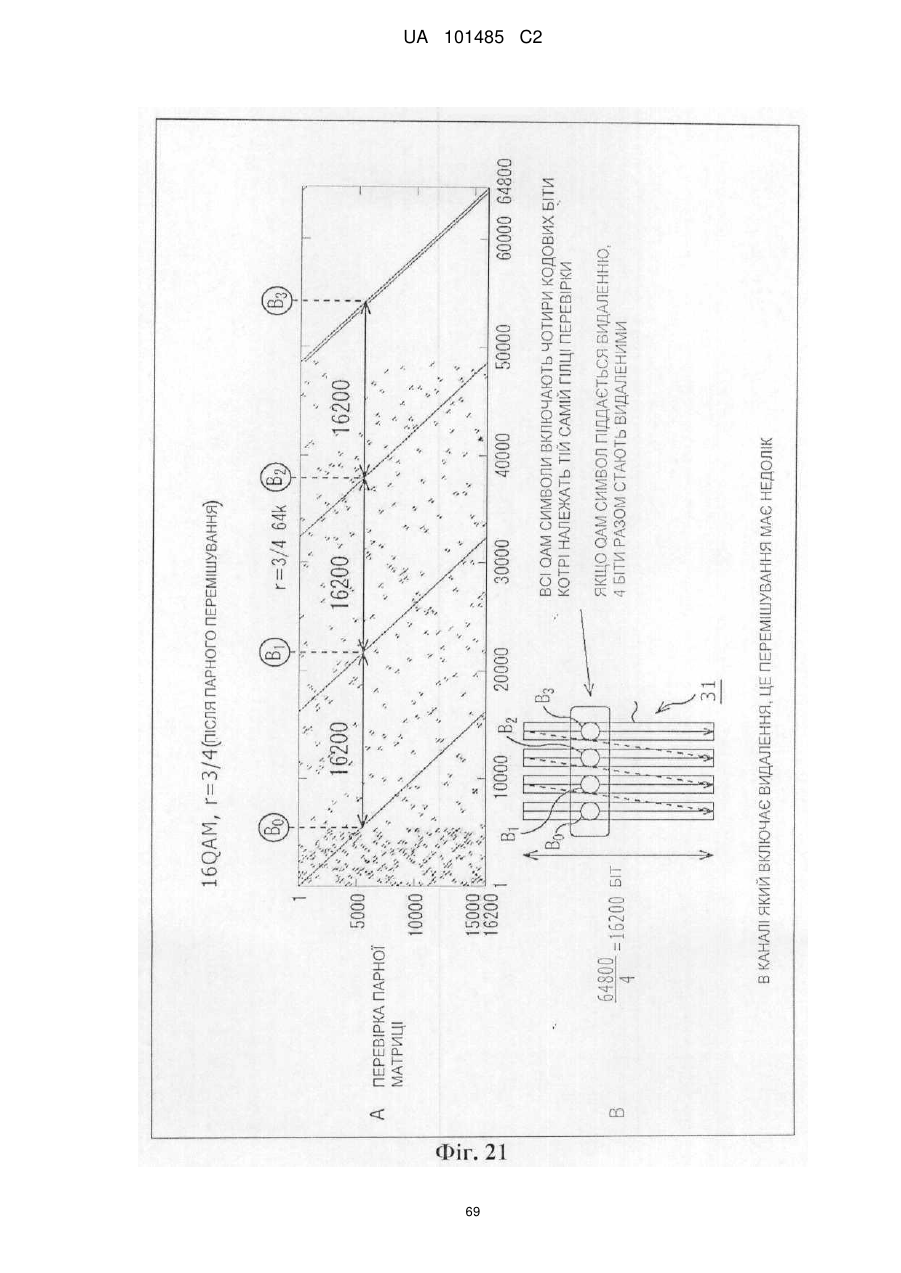

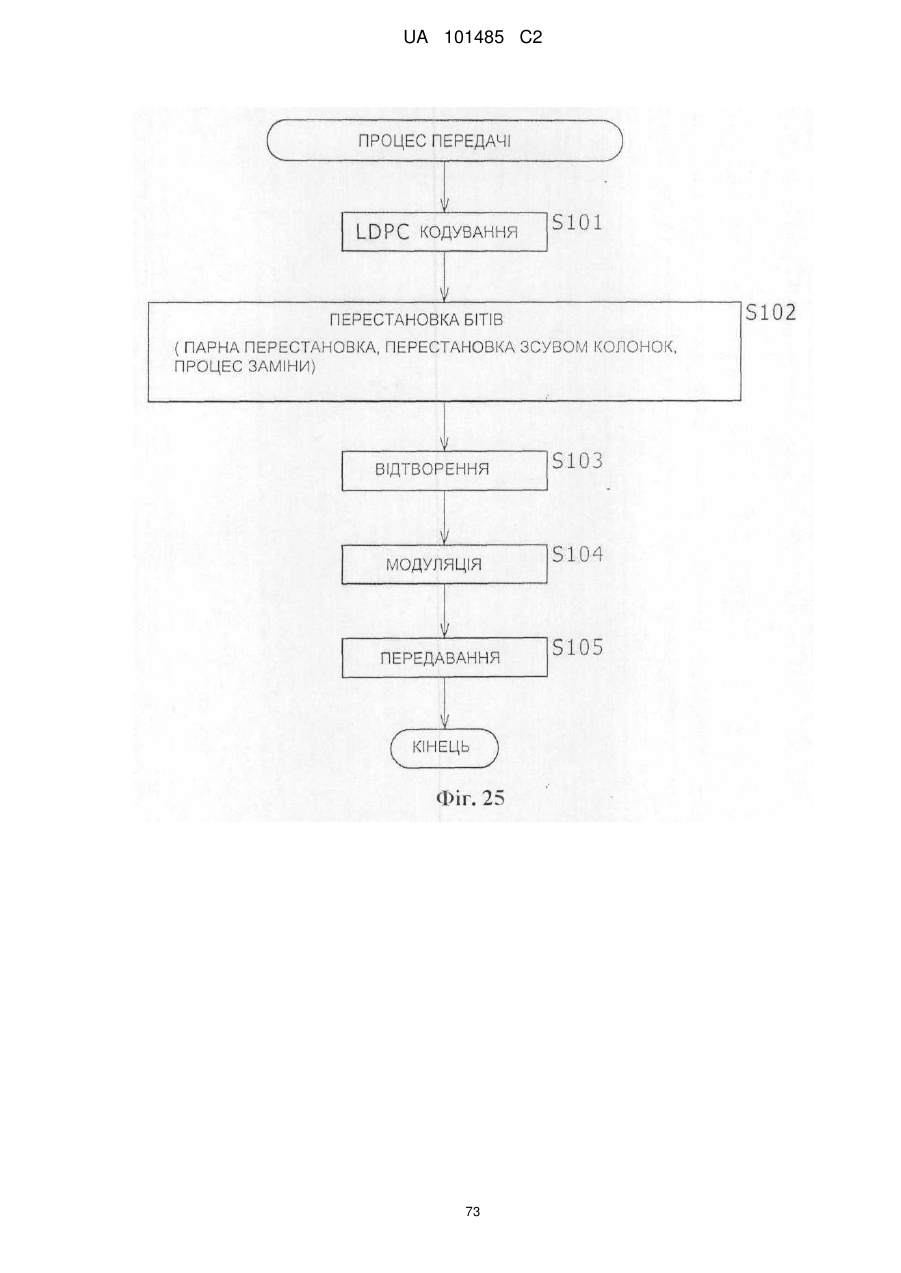

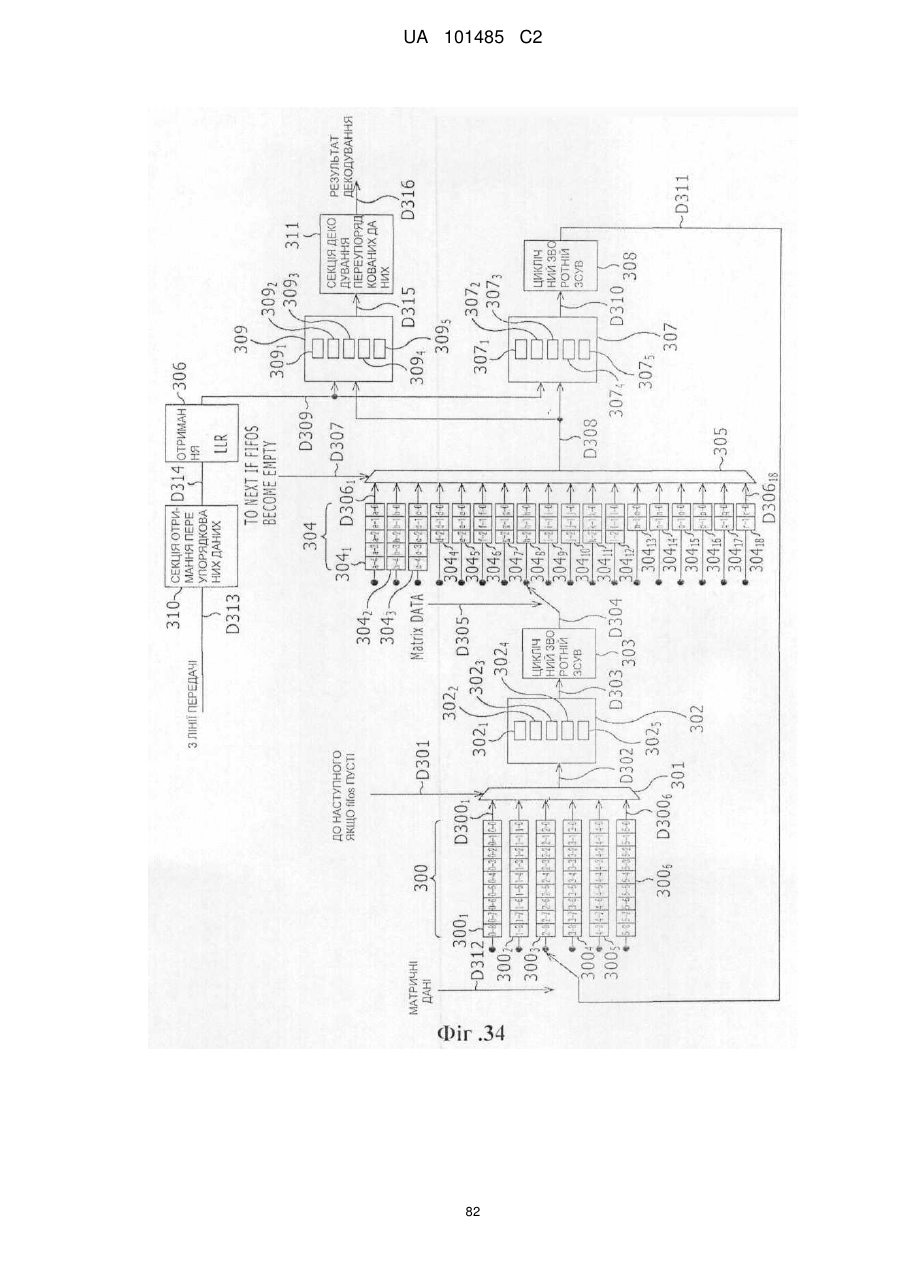

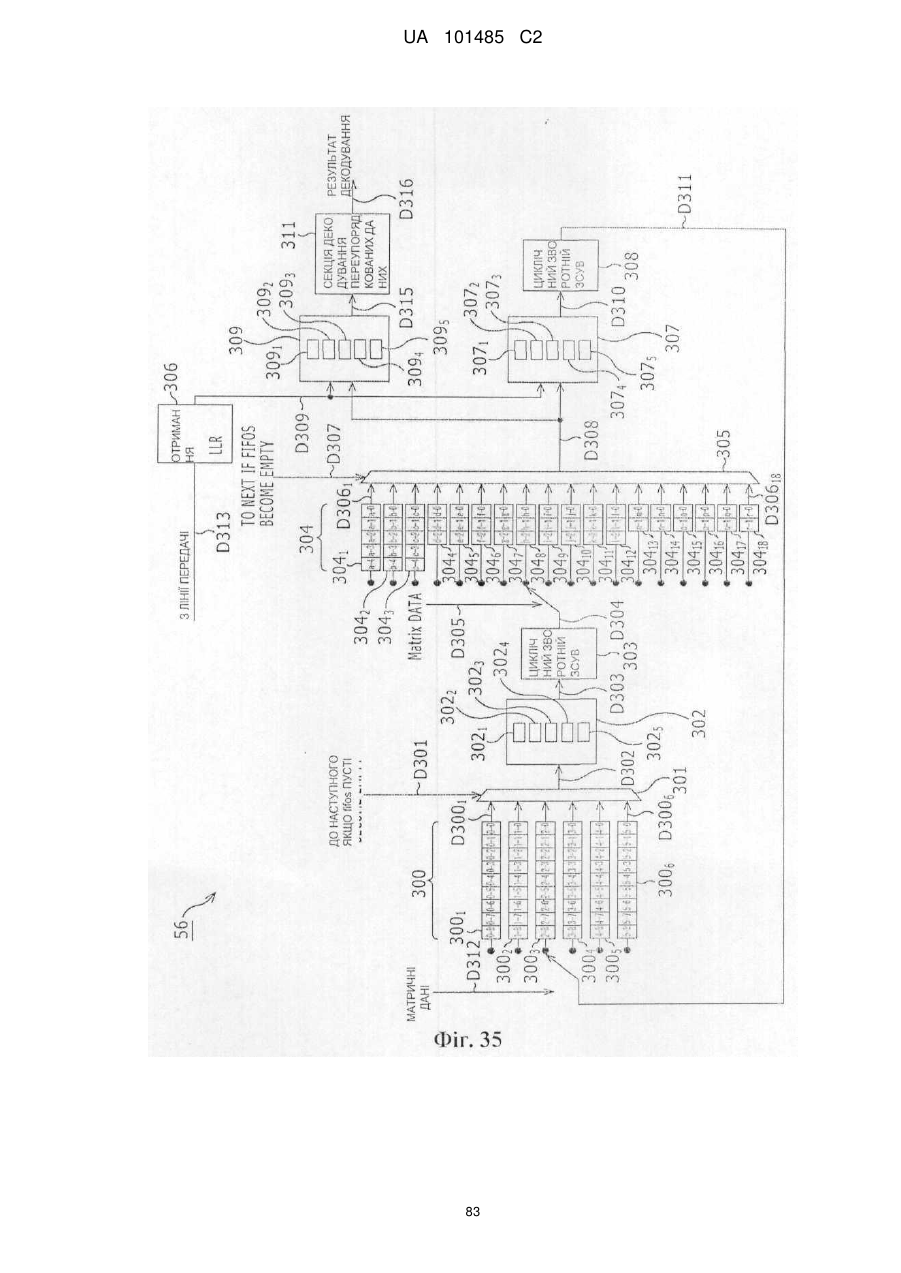

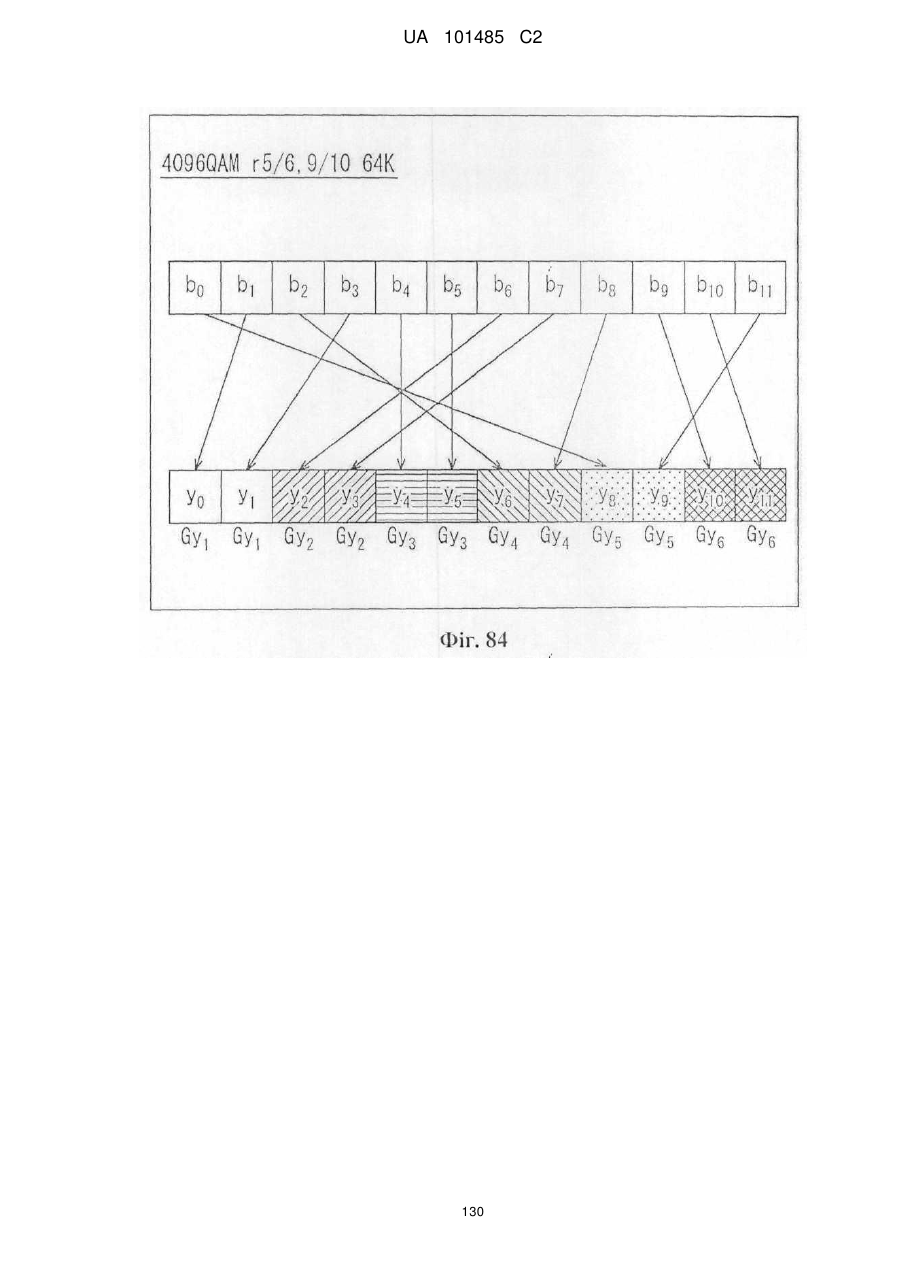

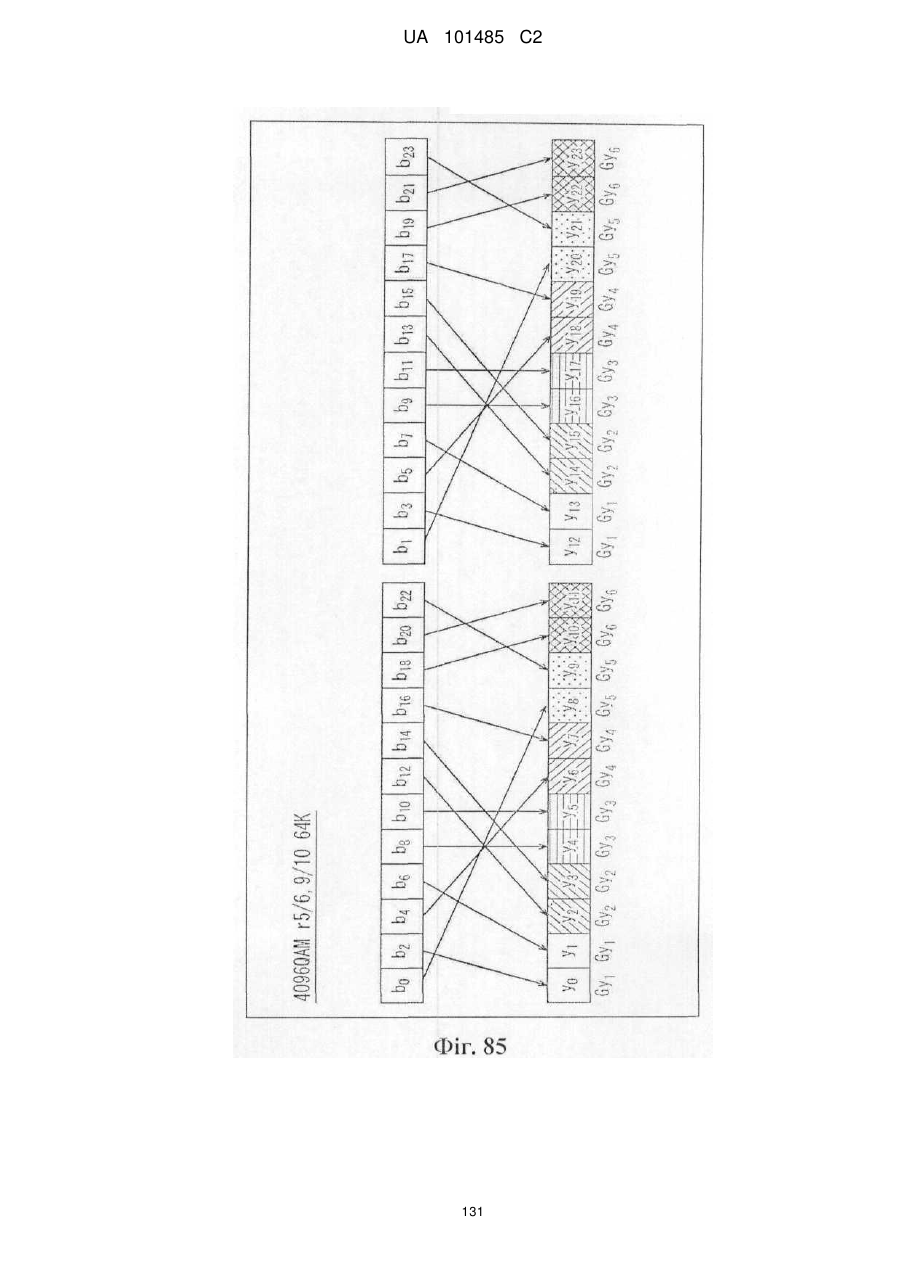

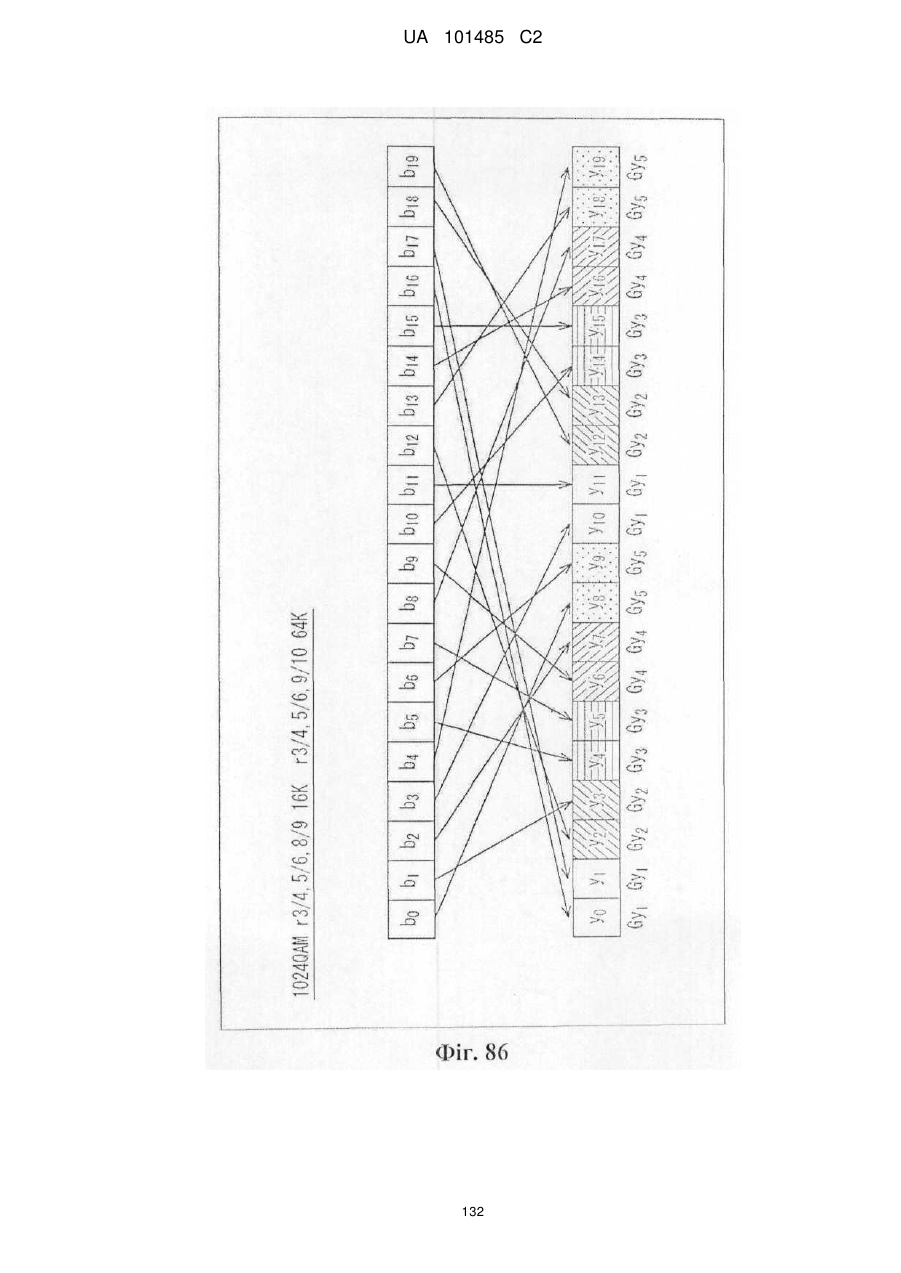

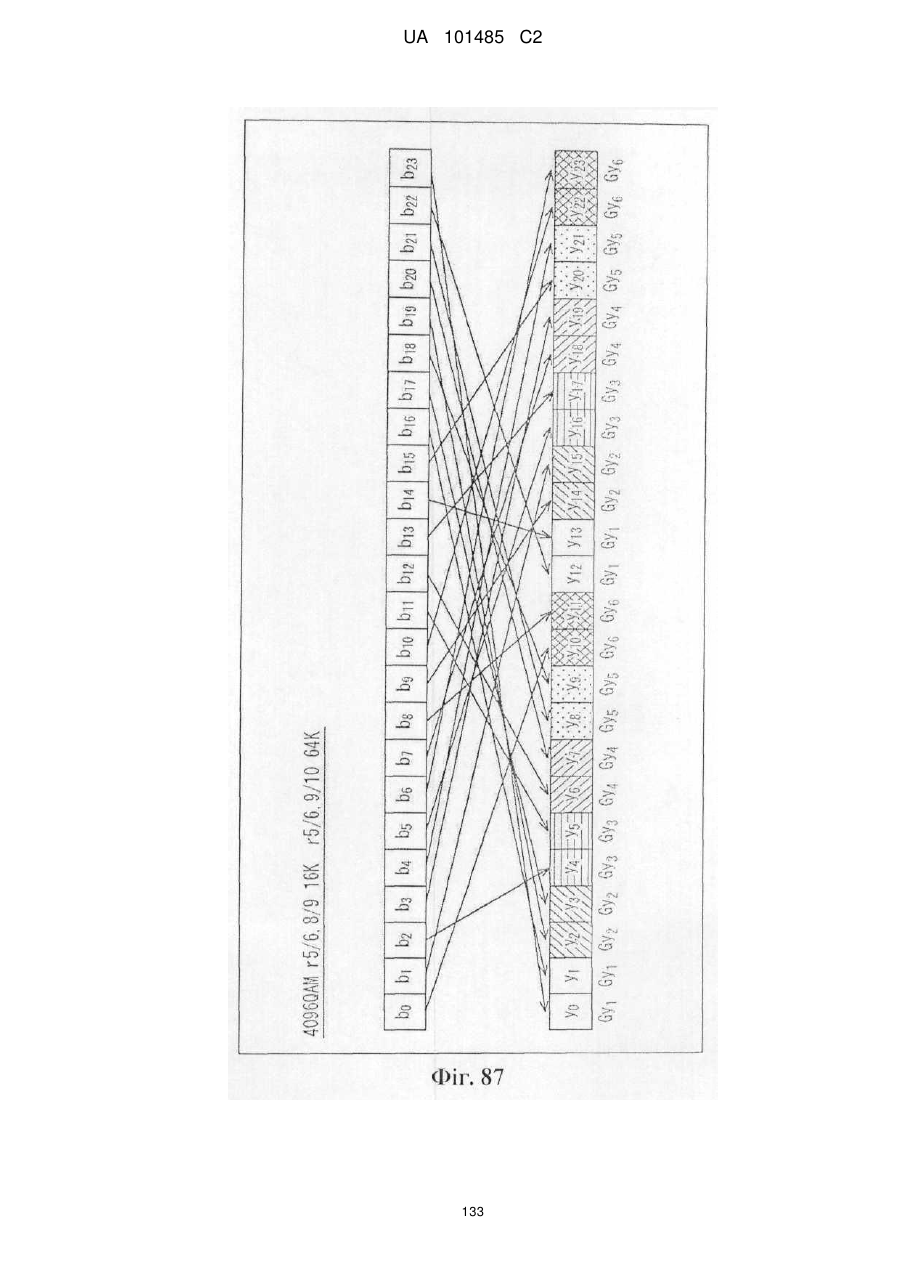

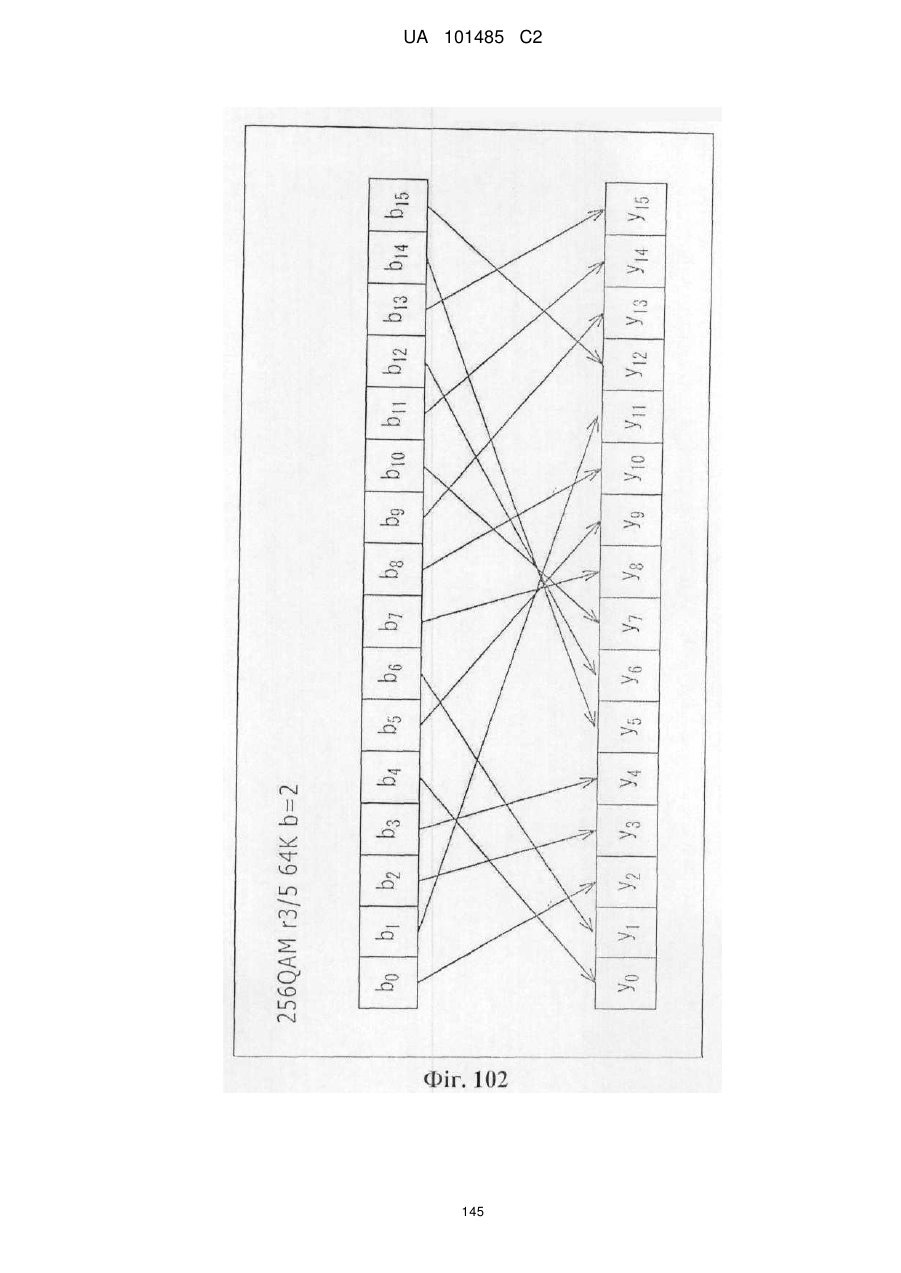

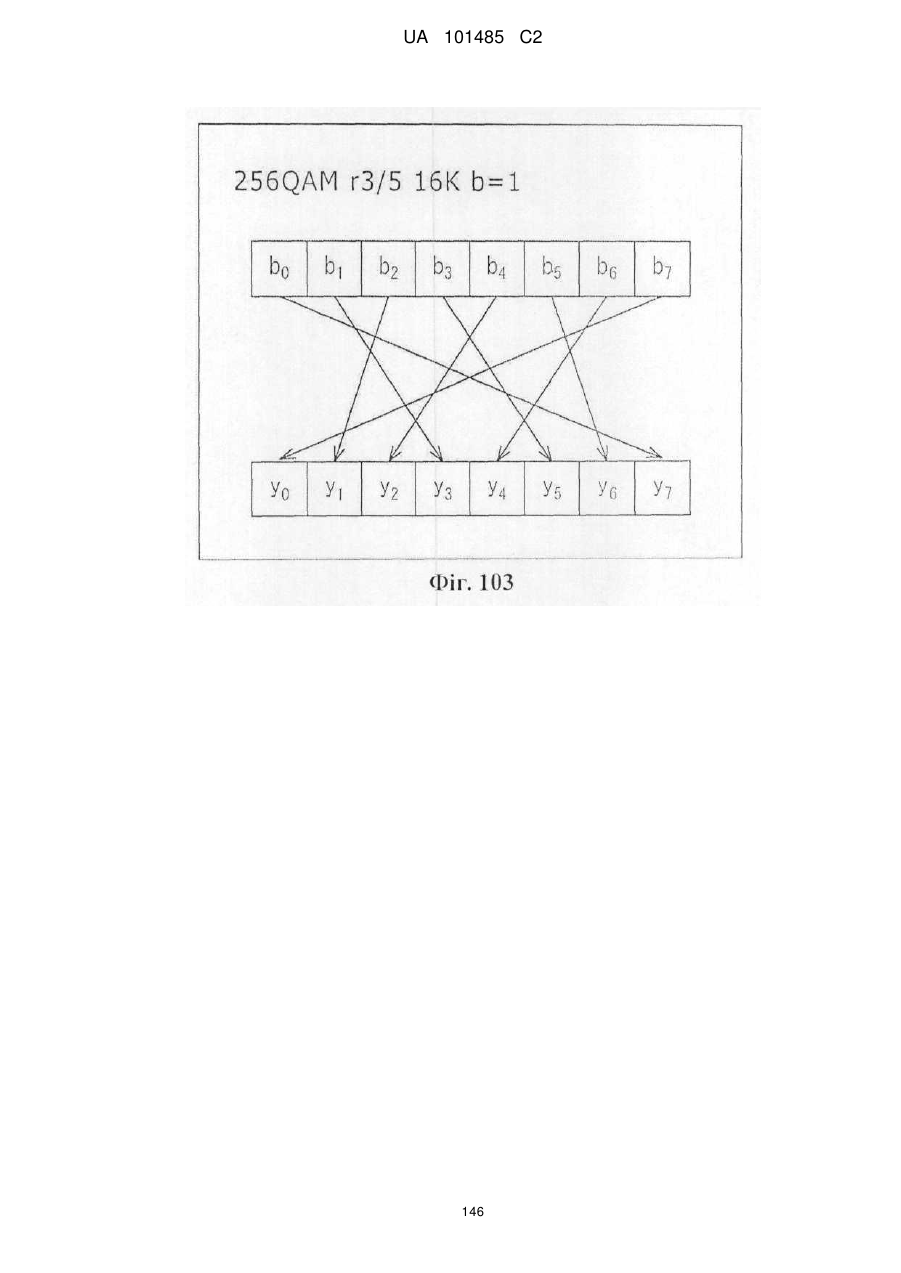

3. Пристрій обробки даних за п. 2, який відрізняється тим, що додатково містить засіб зміни компонування, призначений для виконання процесу зміни компонування, у випадку, коли код LDPC передають таким чином, що два або більше з кодових бітів коду LDPC передають як один символ, для зміни компонування кодових бітів коду LDPC після перемежовування парності таким чином, що множина кодових бітів, що відповідають значенню 1 і включені в один довільний рядок матриці перевірки на парність, не будуть включені в один символ.

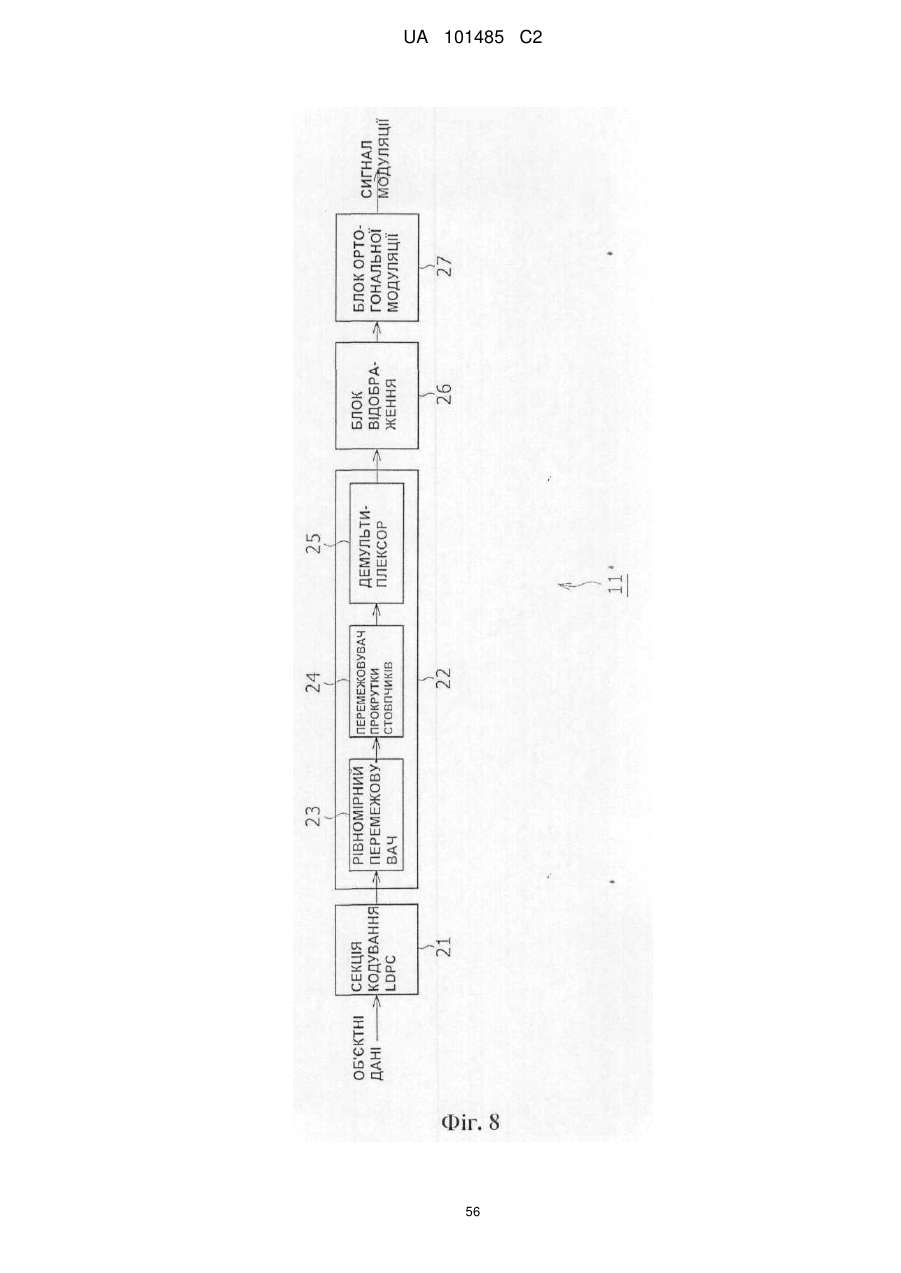

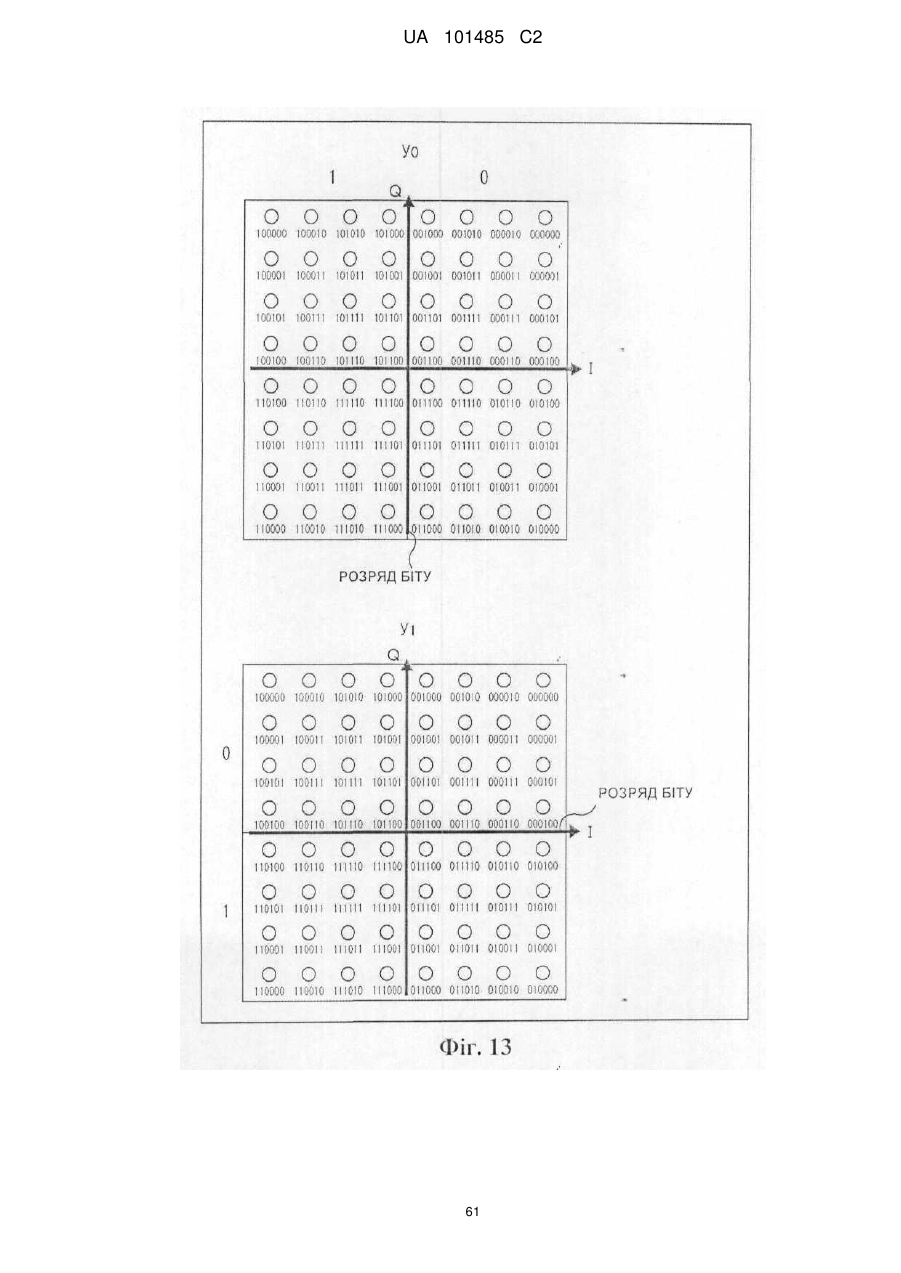

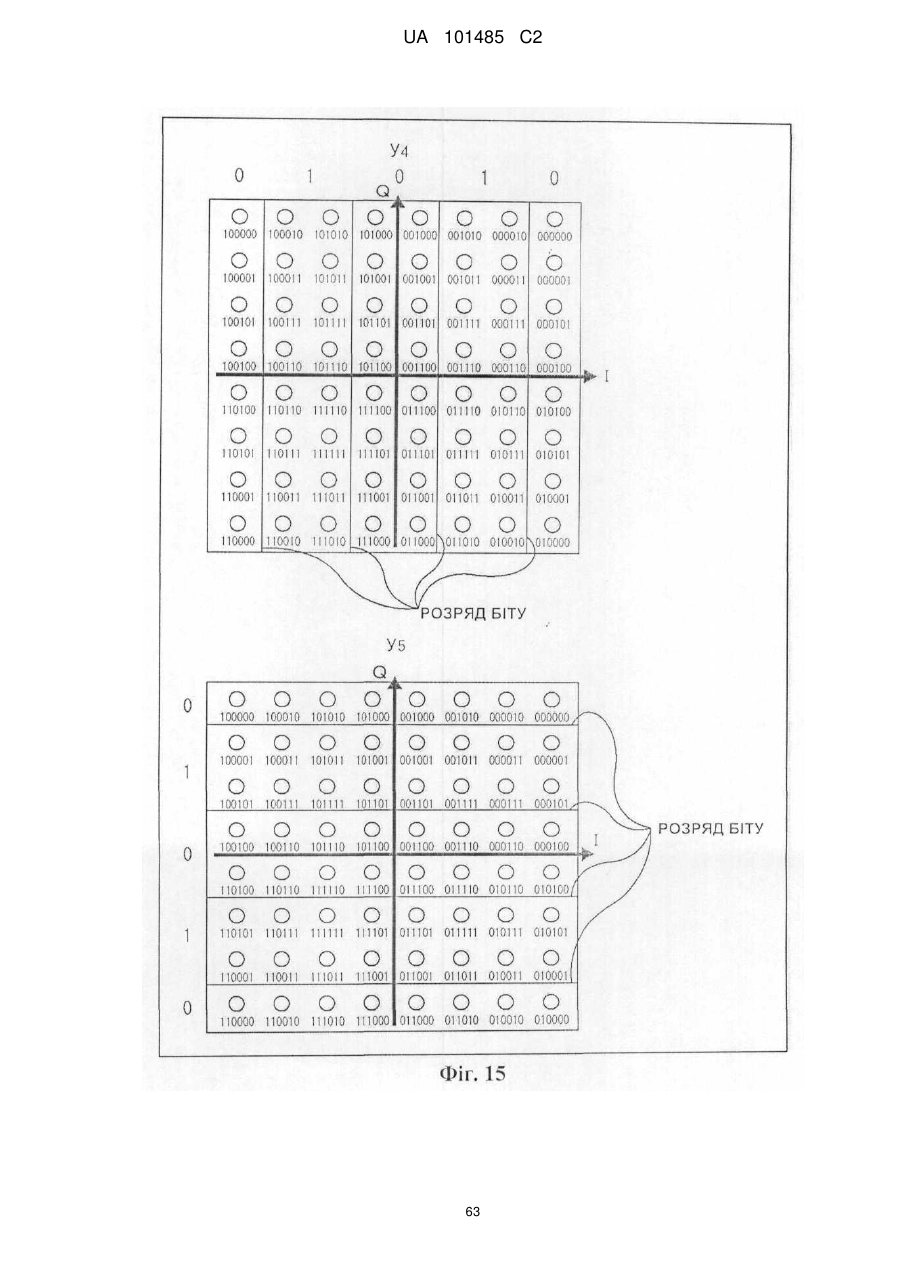

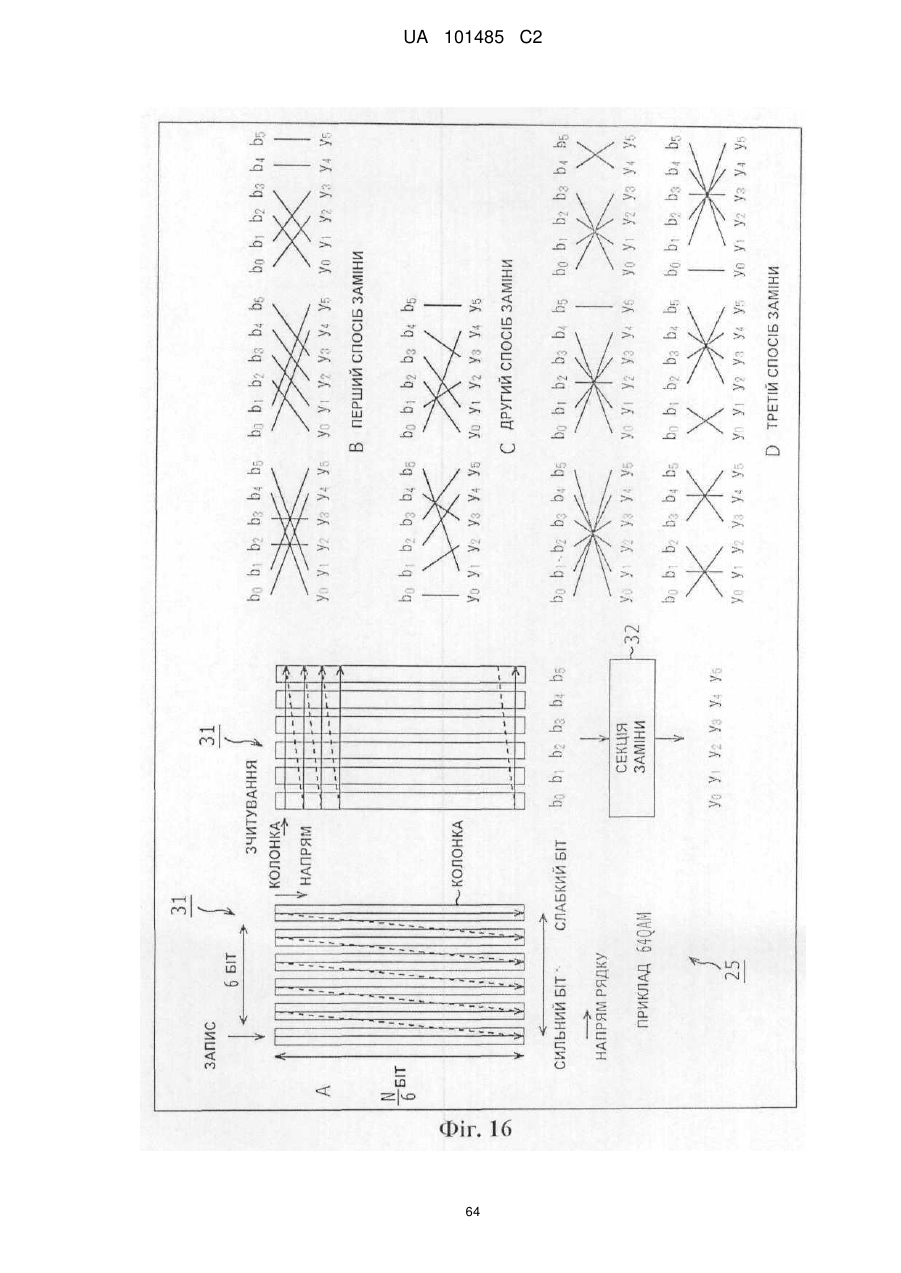

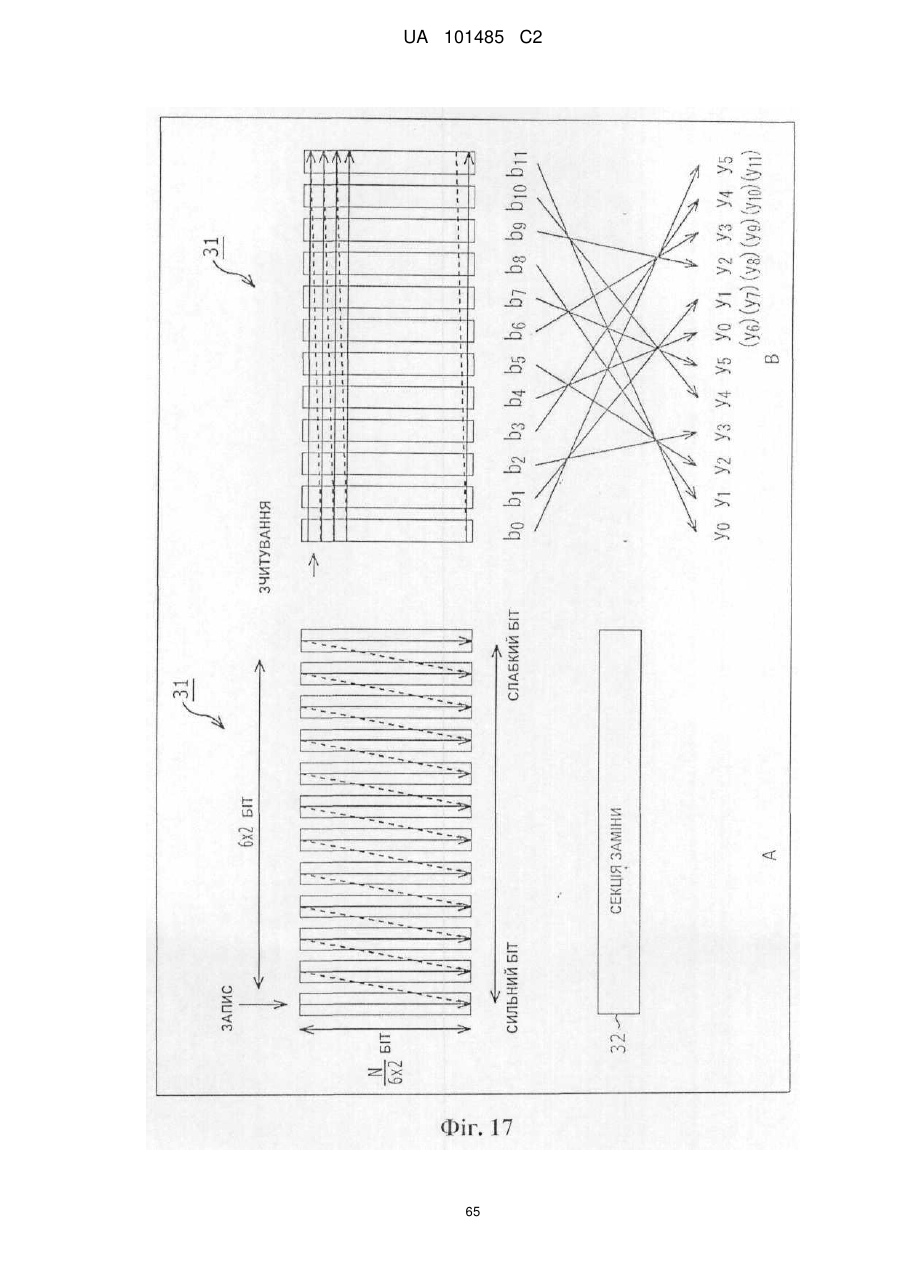

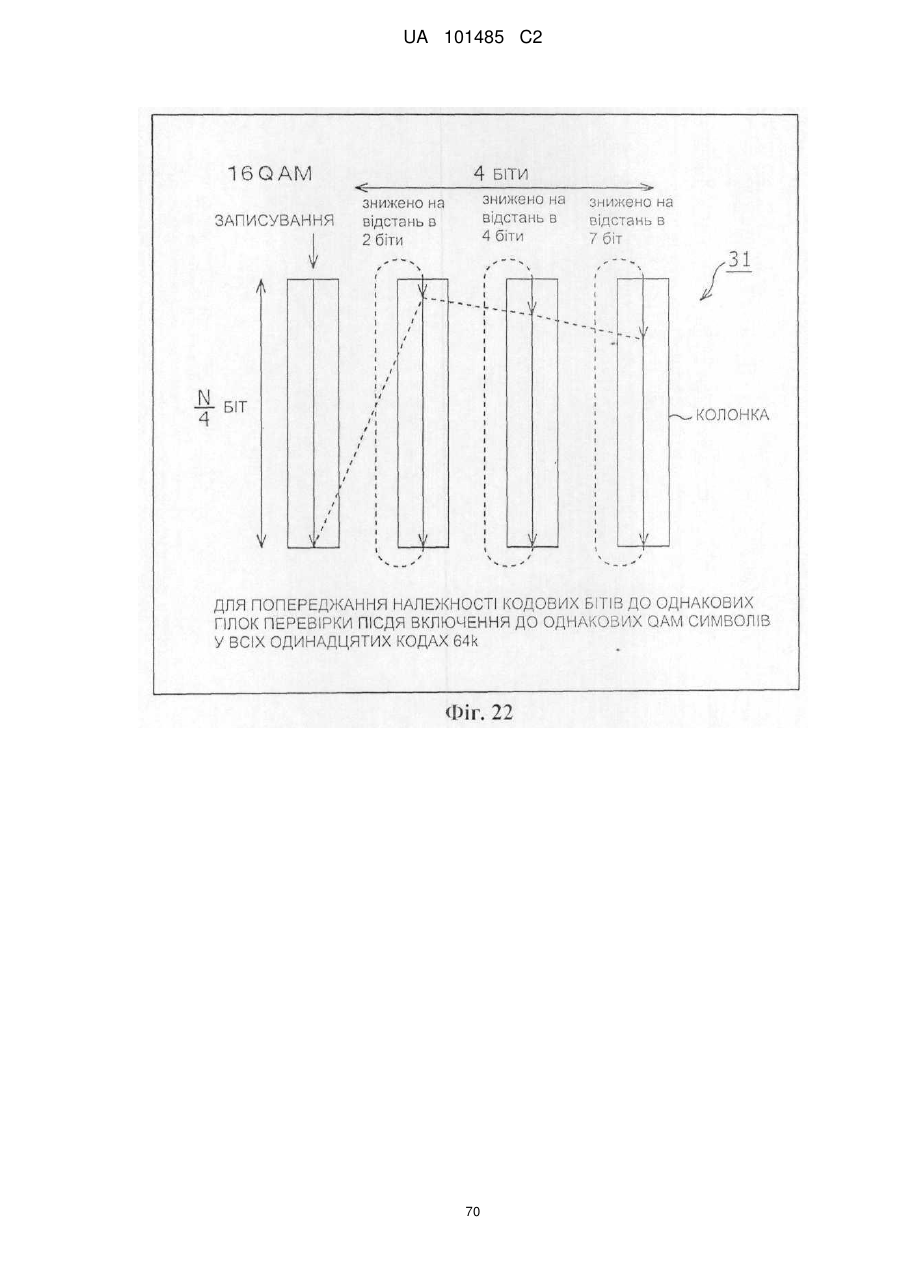

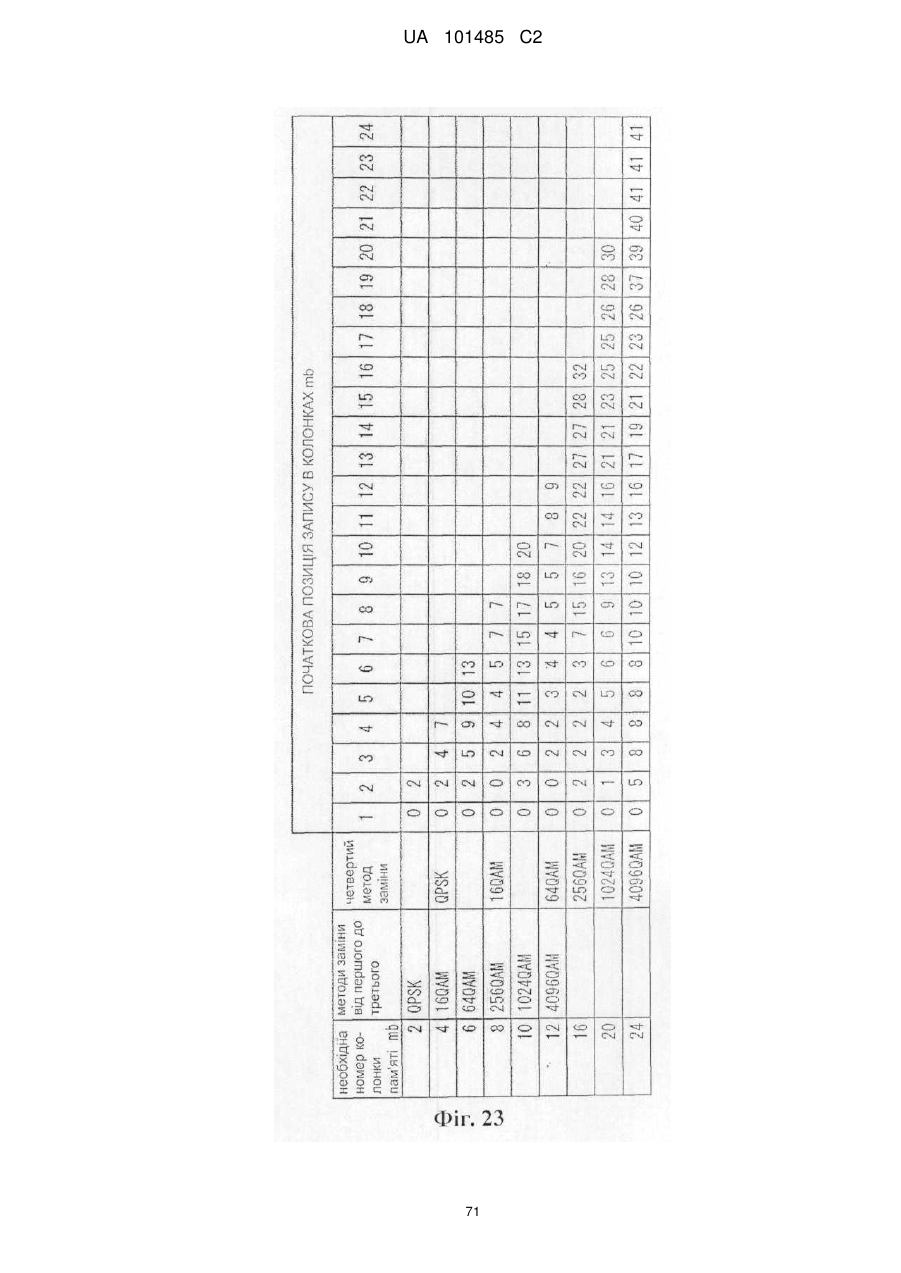

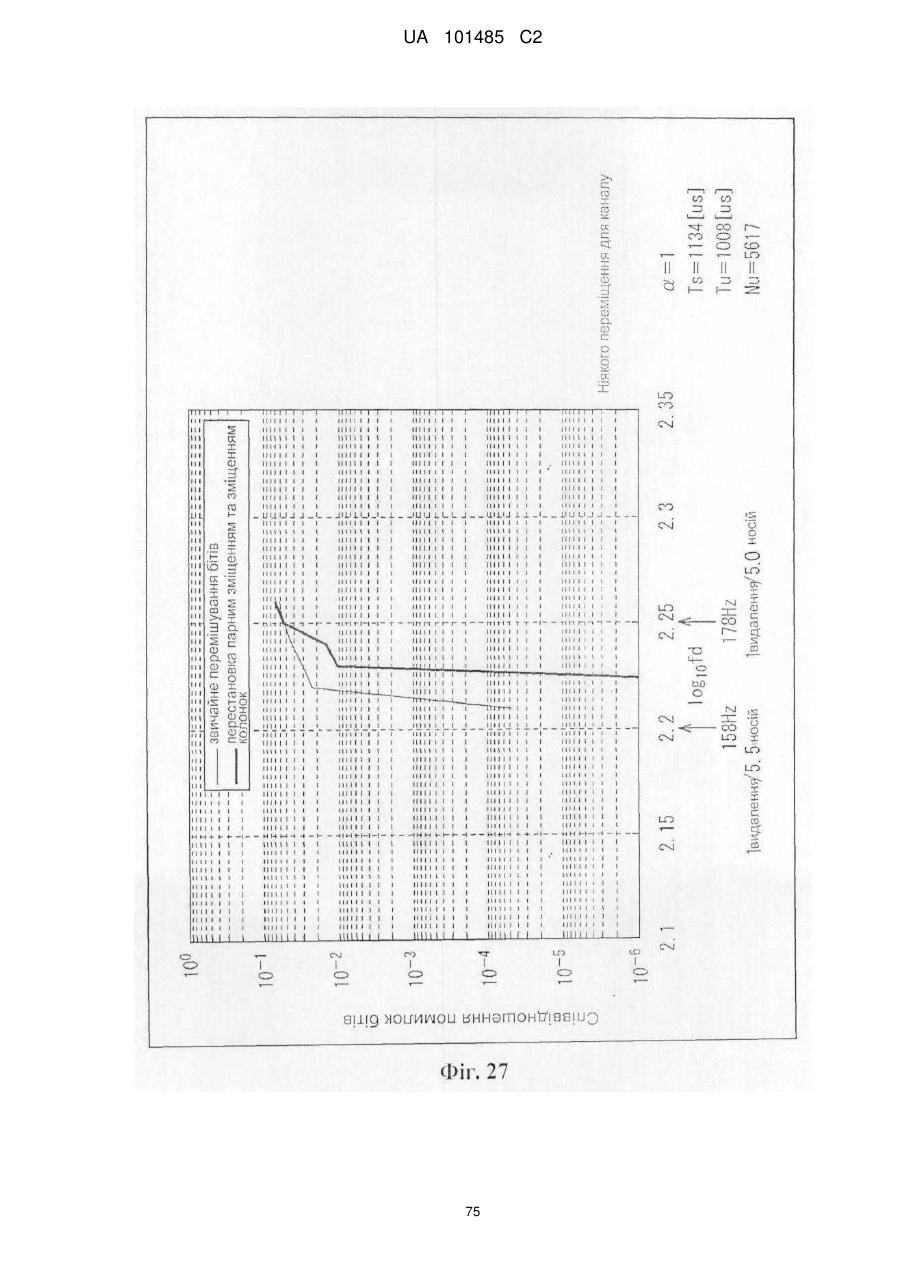

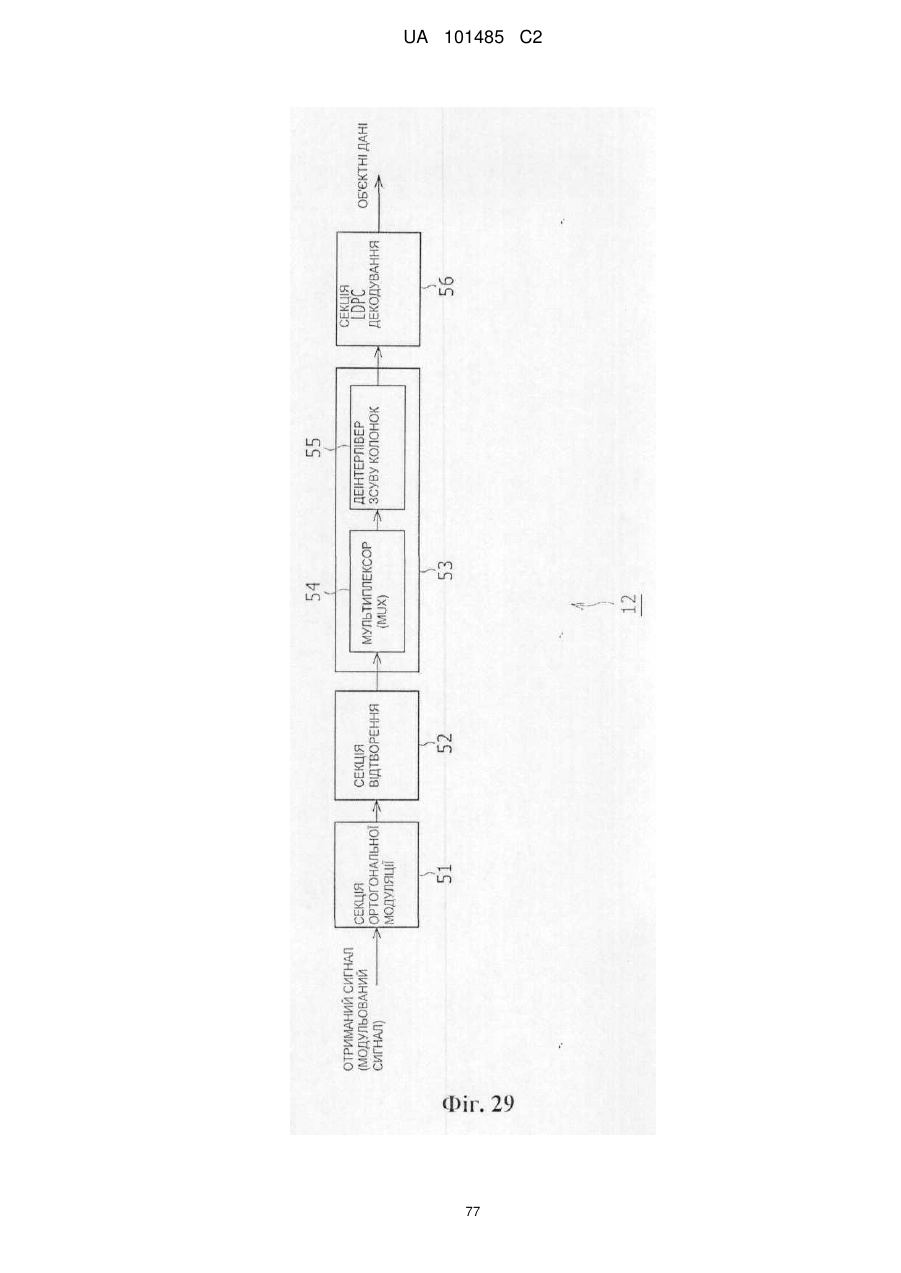

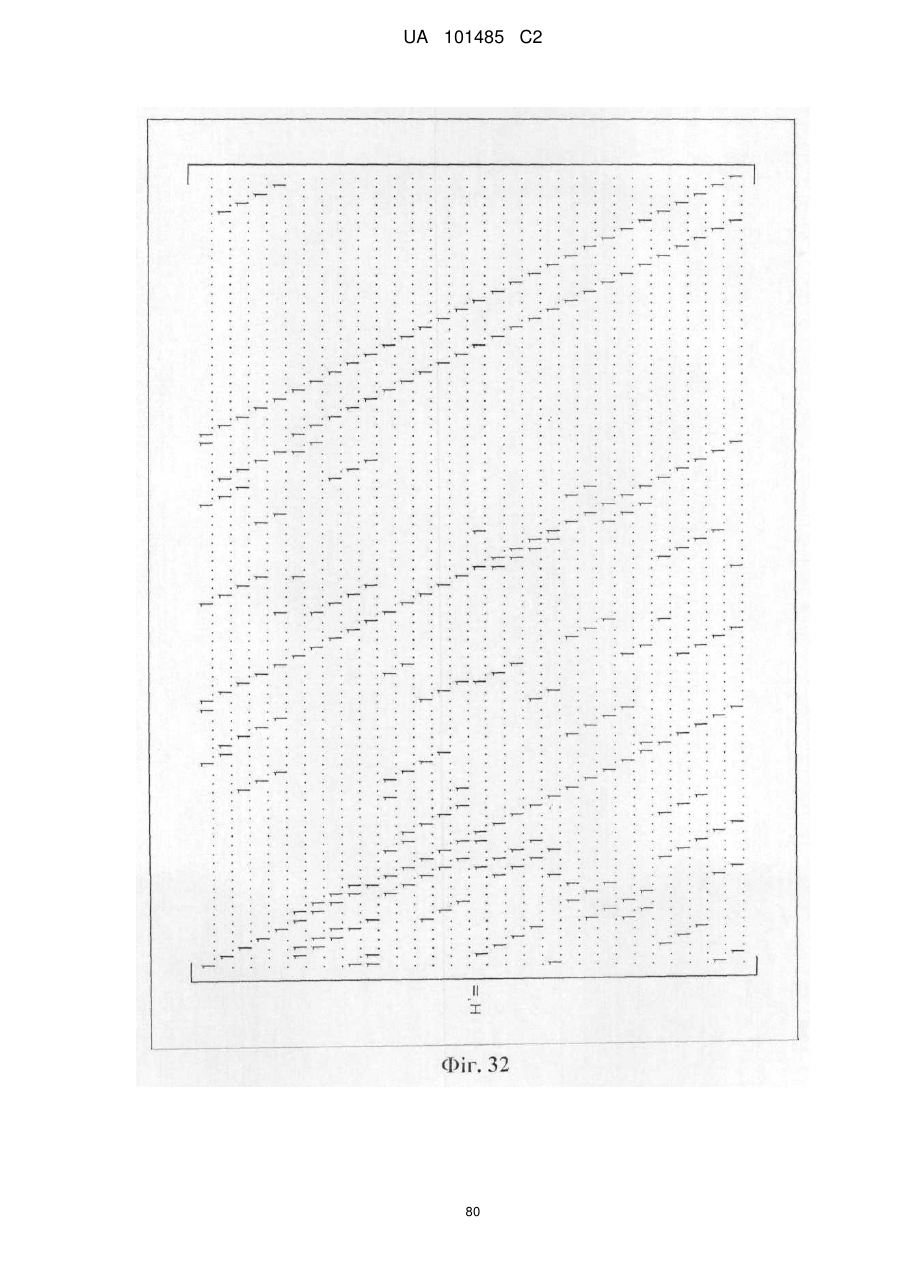

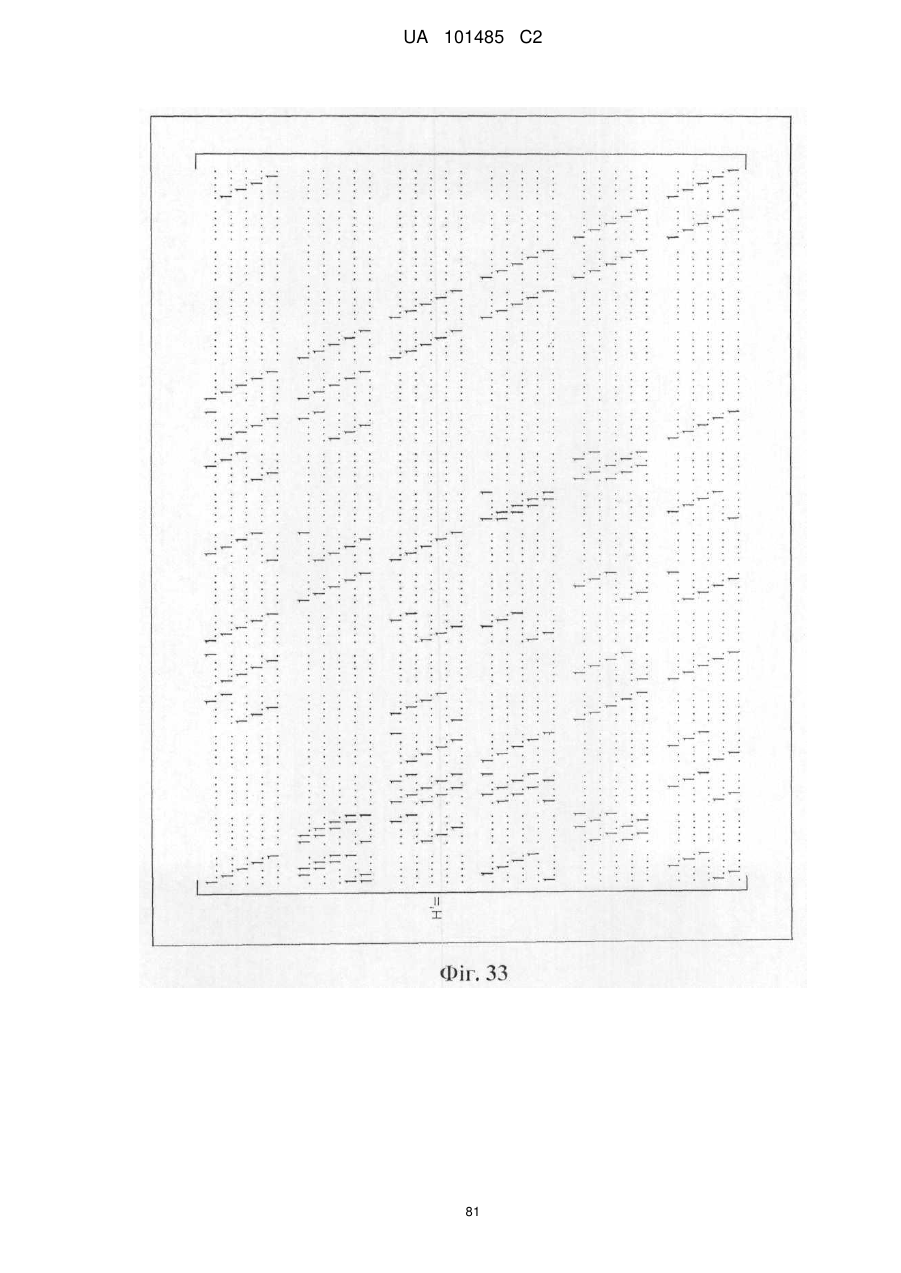

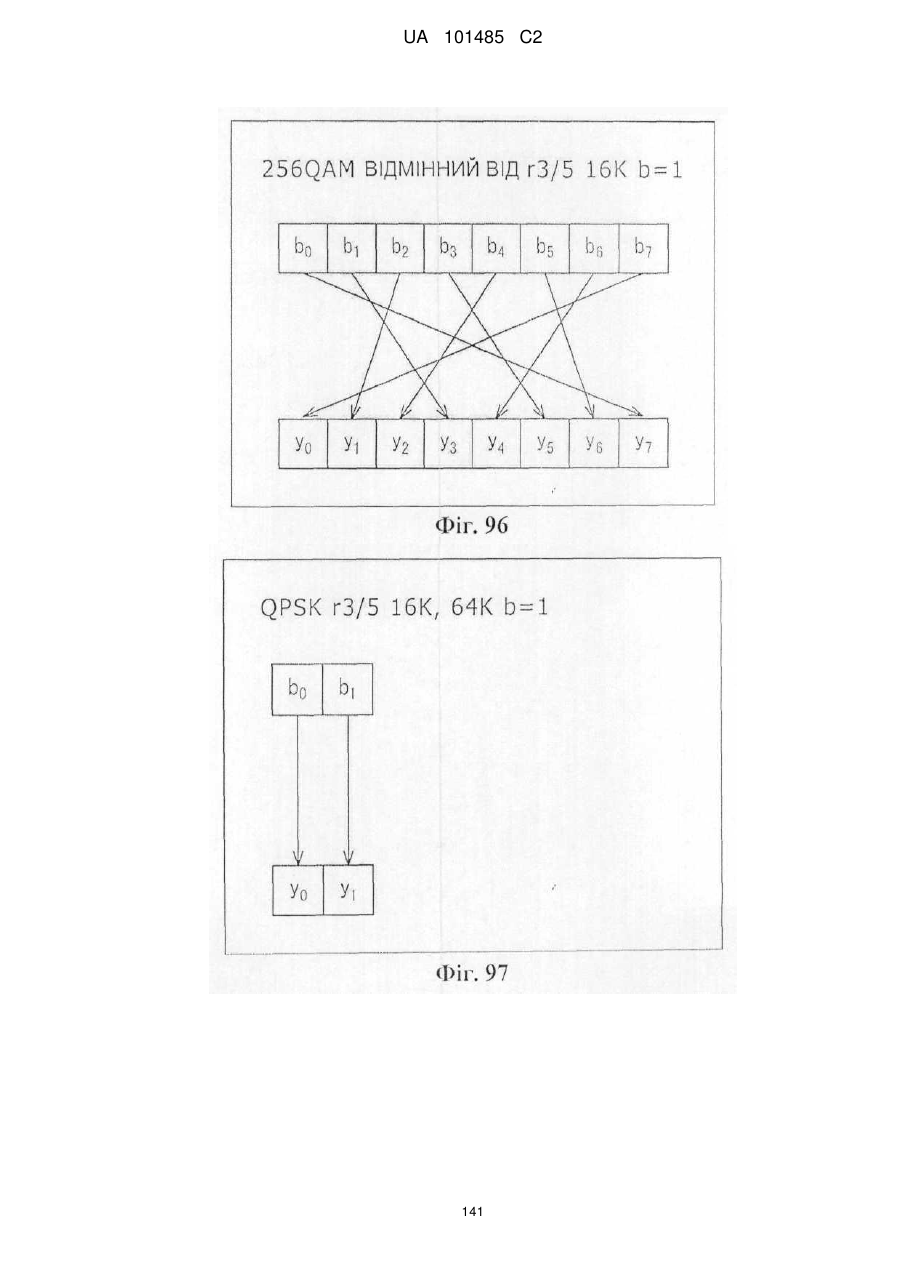

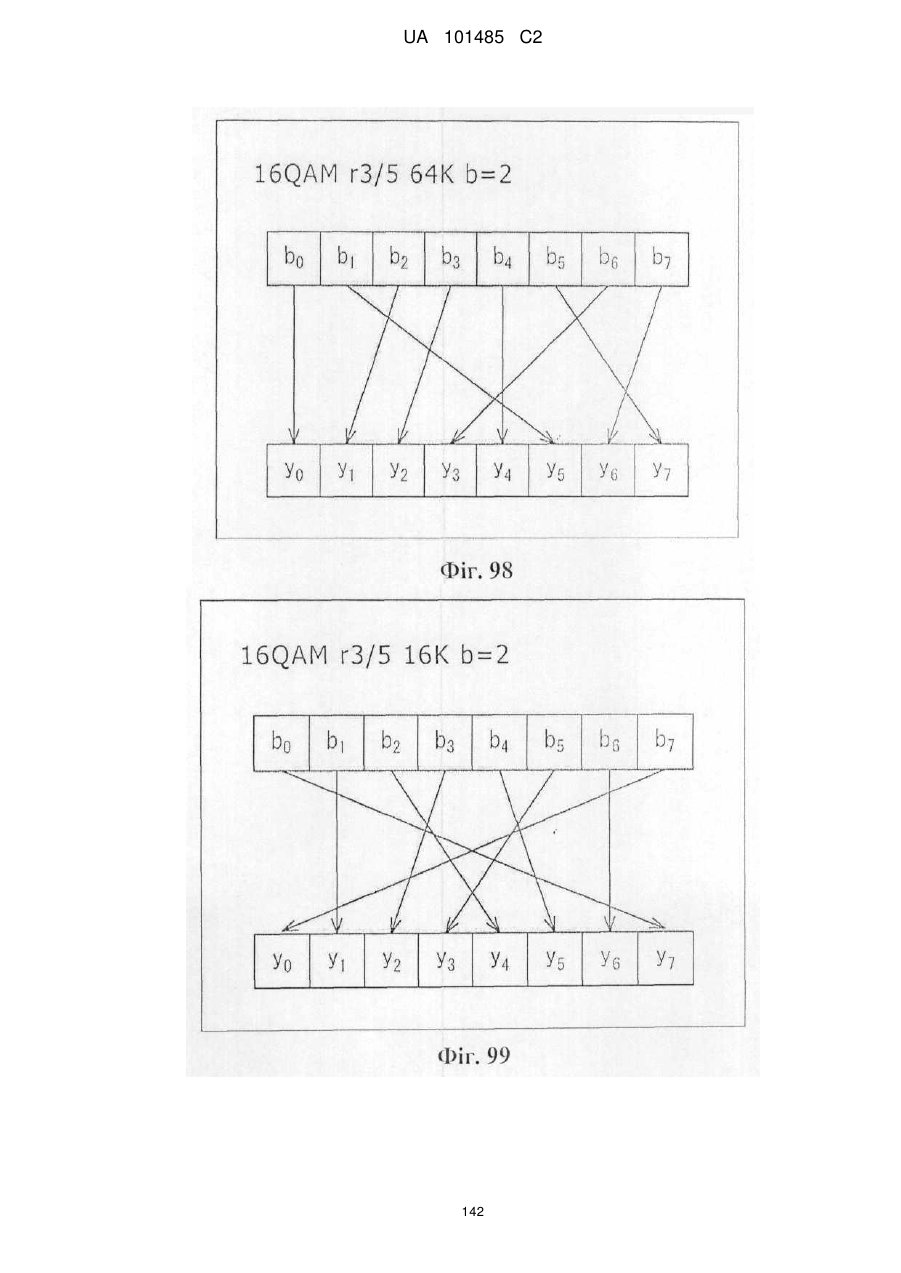

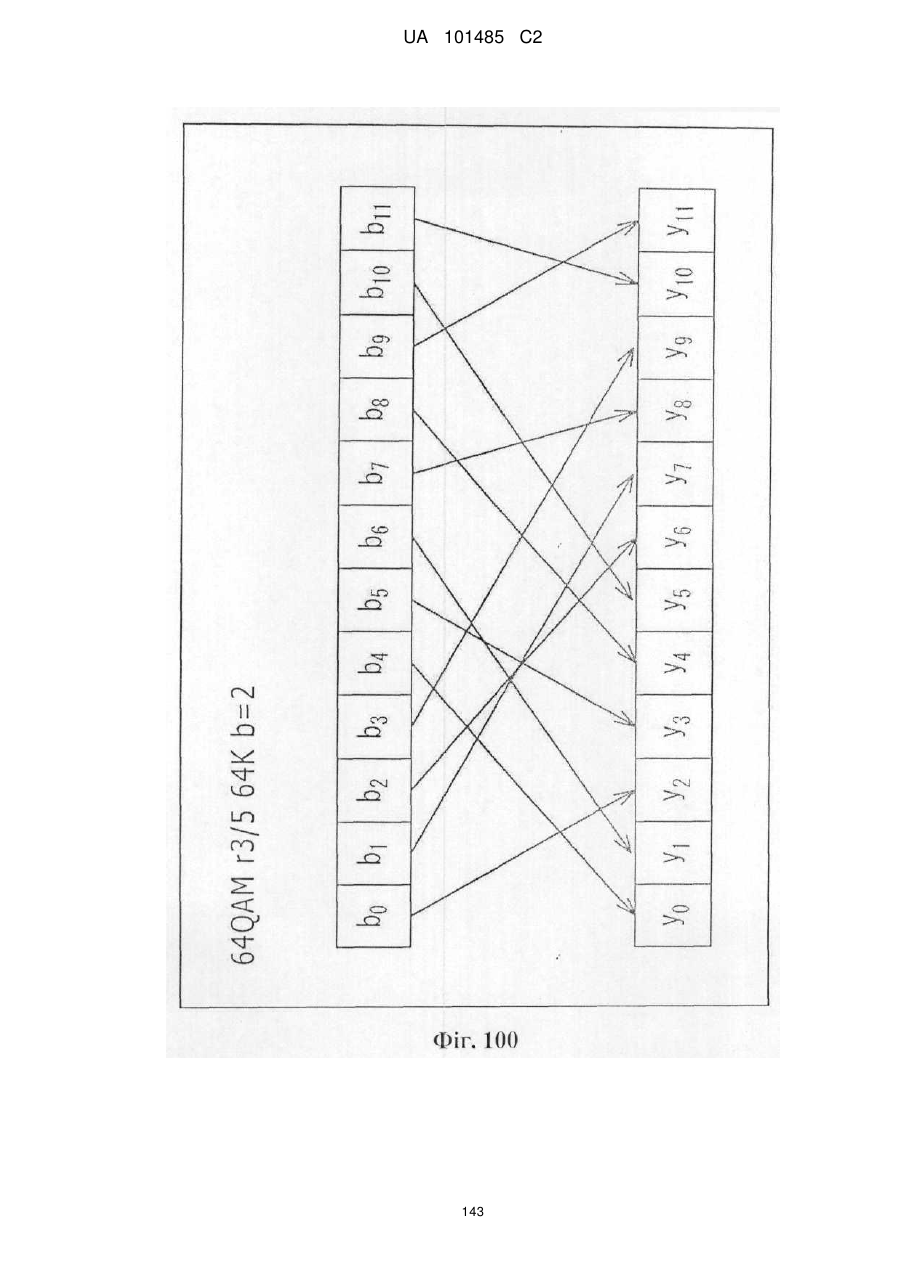

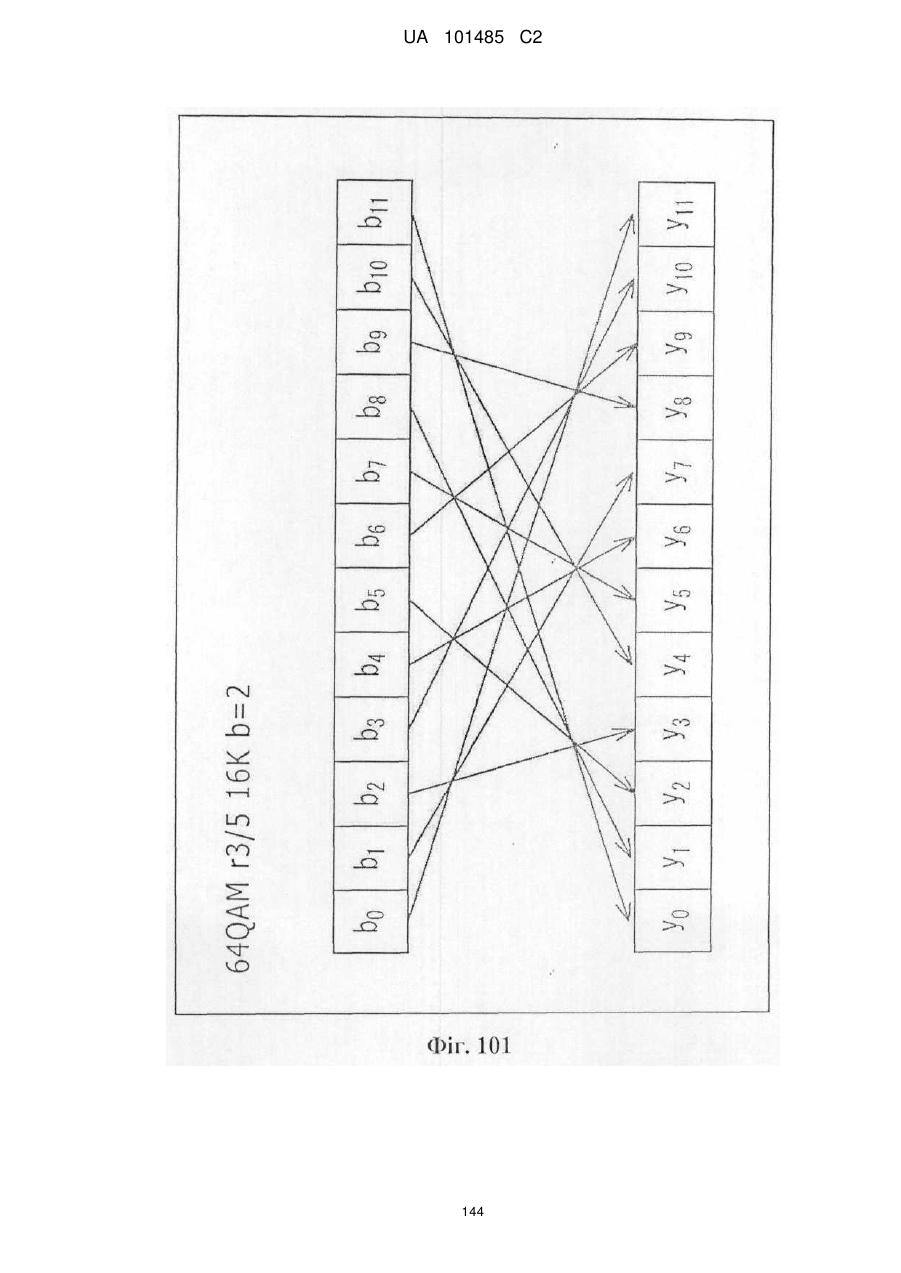

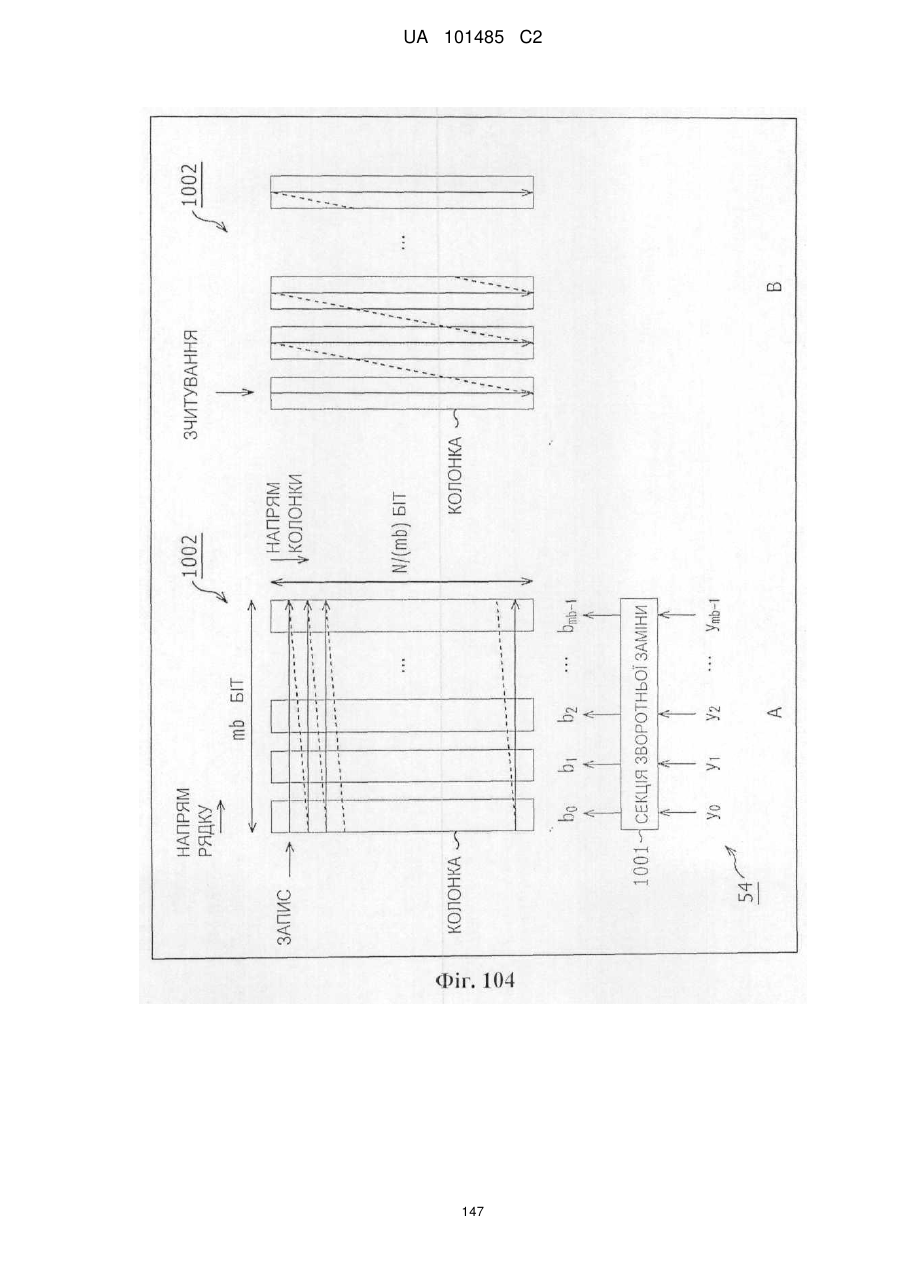

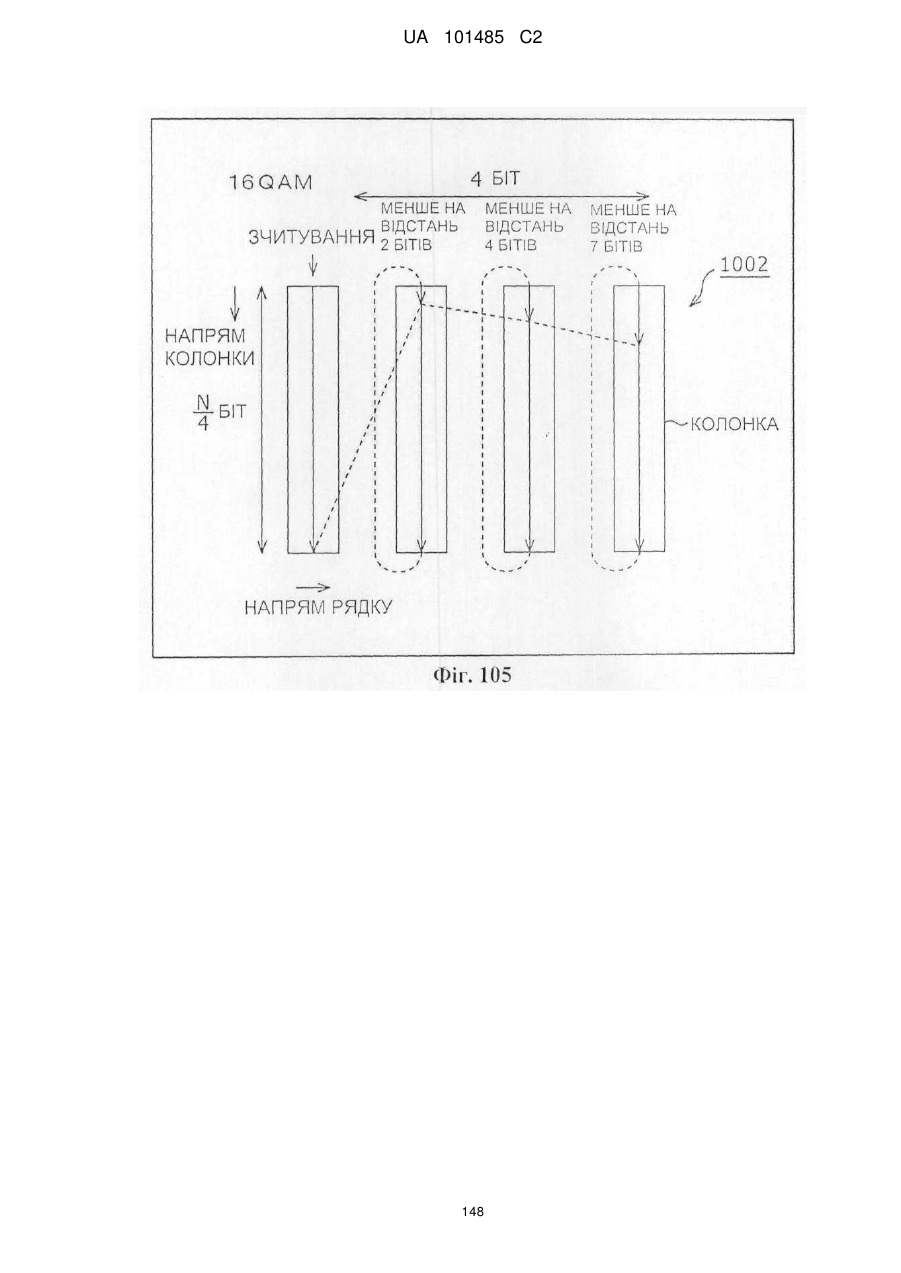

4. Пристрій обробки даних за п. 2, який відрізняється тим, що код LDPC являє собою код LDPC, в якому інформаційна матриця, яка являє собою частину матриці перевірки на парність коду LDPC, що відповідає інформаційним бітам коду LDPC, має циклічну структуру; і згаданий пристрій обробки даних додатково містить засіб зміни компонування, призначений для виконання перемежовування прокрутки стовпчиків, для зміни, у випадку, коли символ сформований з кодових бітів коду LDPC, записаних в напрямку стовпчиків засобу зберігання, для зберігання цих кодових бітів коду LDPC у напрямку рядка й у напрямку стовпчика й зчитування в напрямку рядка, вихідного положення запису, коли кодові біти коду LDPC записані в напрямку стовпчика згаданого засобу зберігання змінюють для кожного зі стовпчиків згаданого засобу зберігання, як процес зміни компонування для зміни компонування кодових бітів коду LDPC.

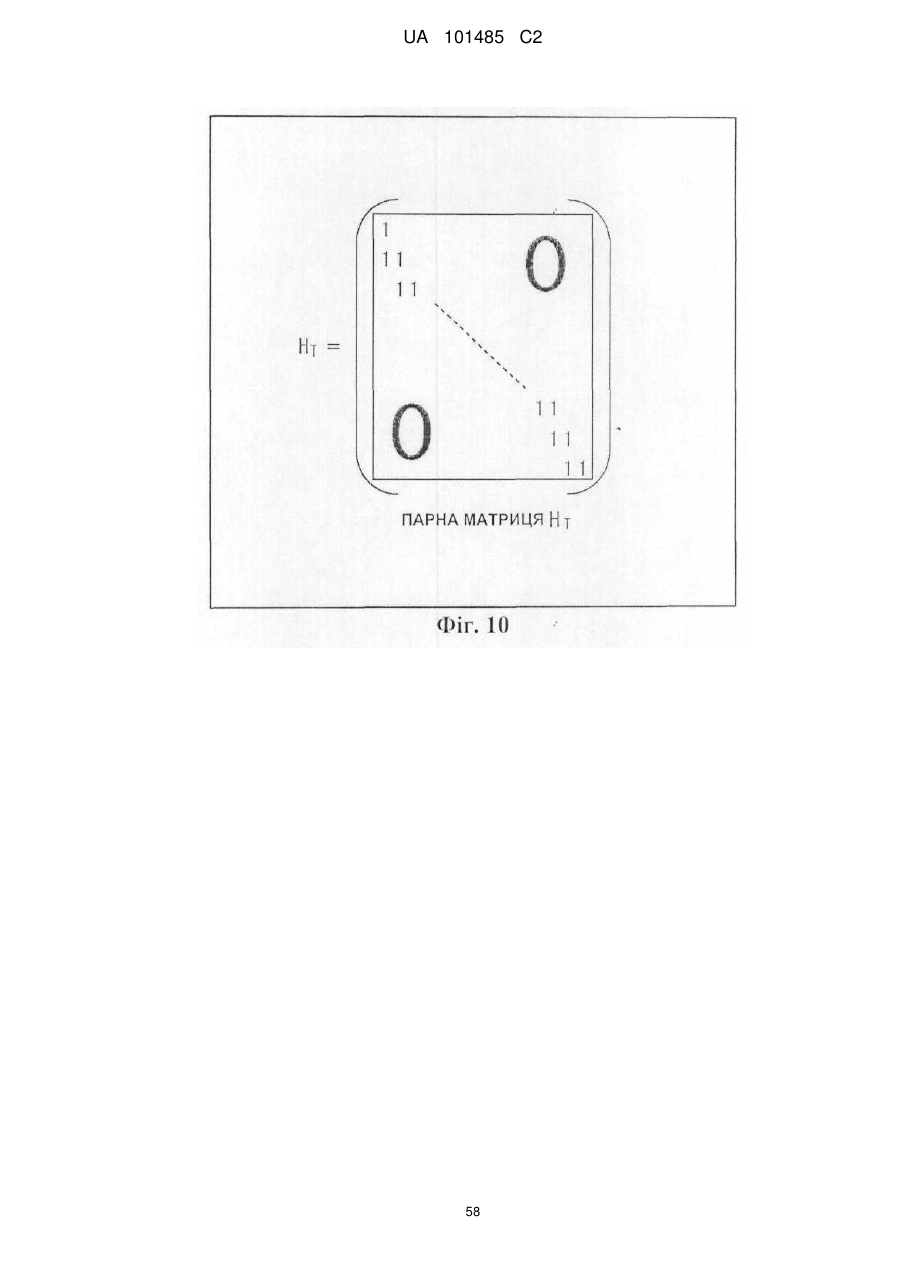

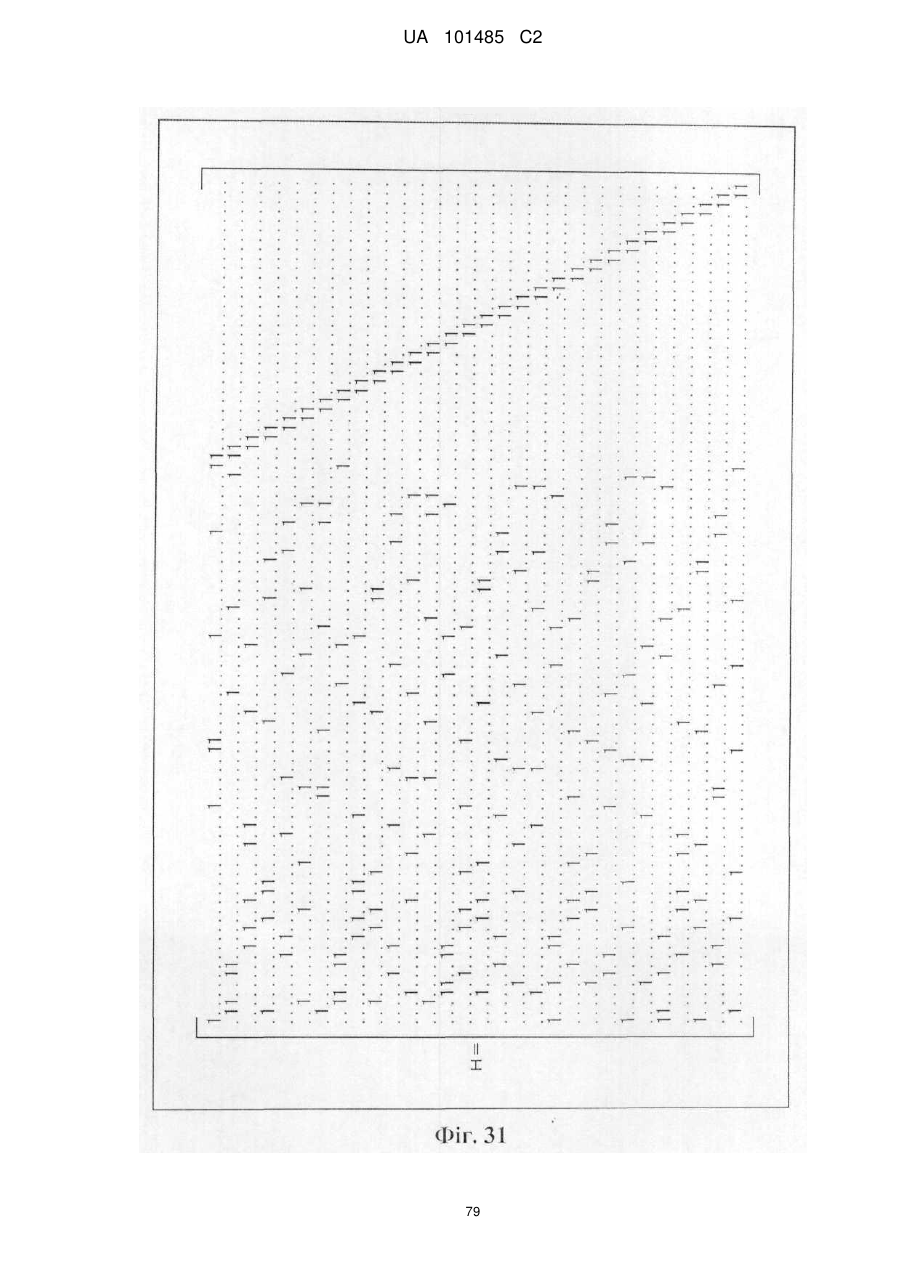

5. Пристрій обробки даних за п. 4, який відрізняється тим, що матриця парності в матриці перевірки на парність коду LDPC має псевдоциклічну структуру, у якій матриця парності має частину, що має циклічну структуру, за винятком деякої її частини, цю структуру одержують шляхом застосування заміни рядків, що відповідає перемежуванню парності.

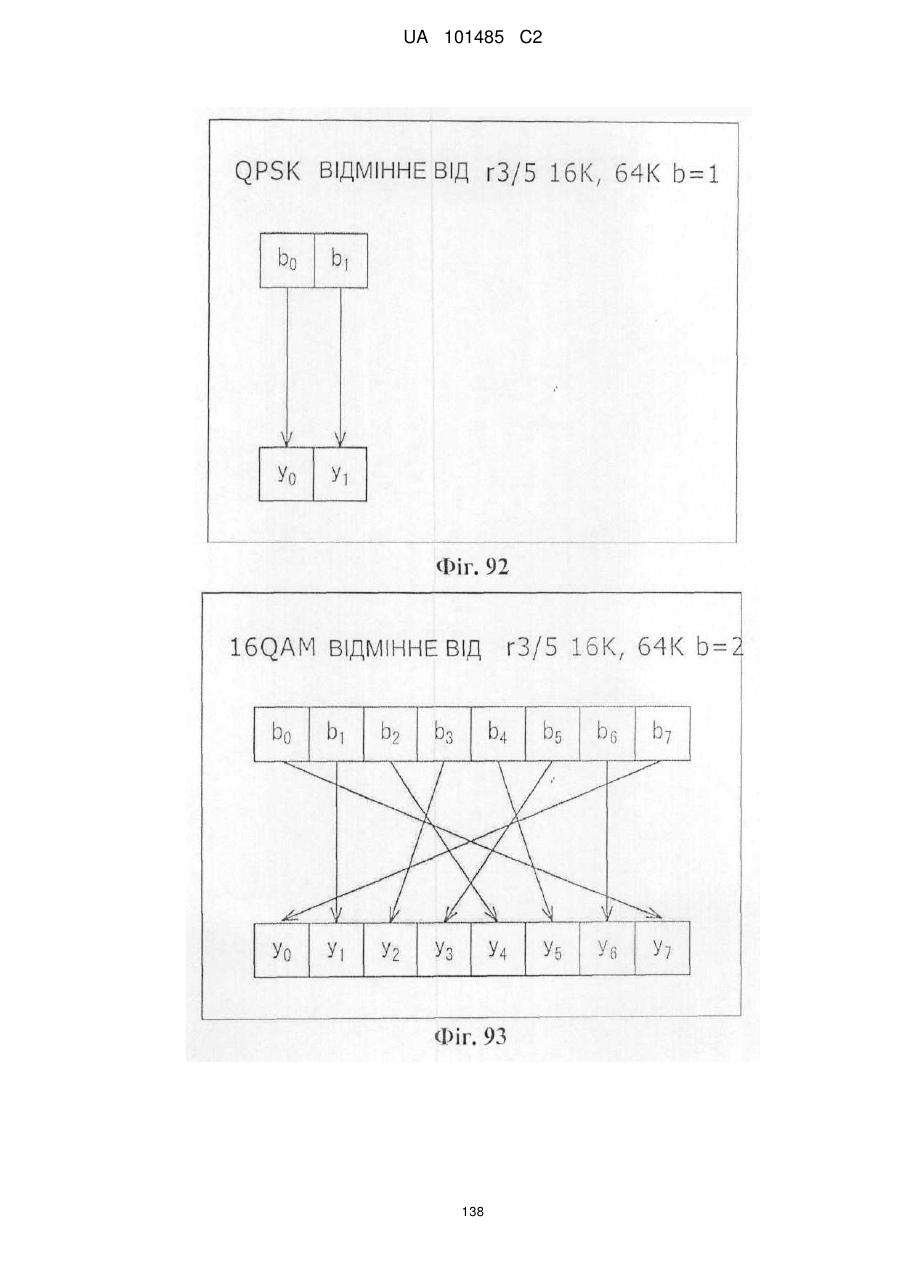

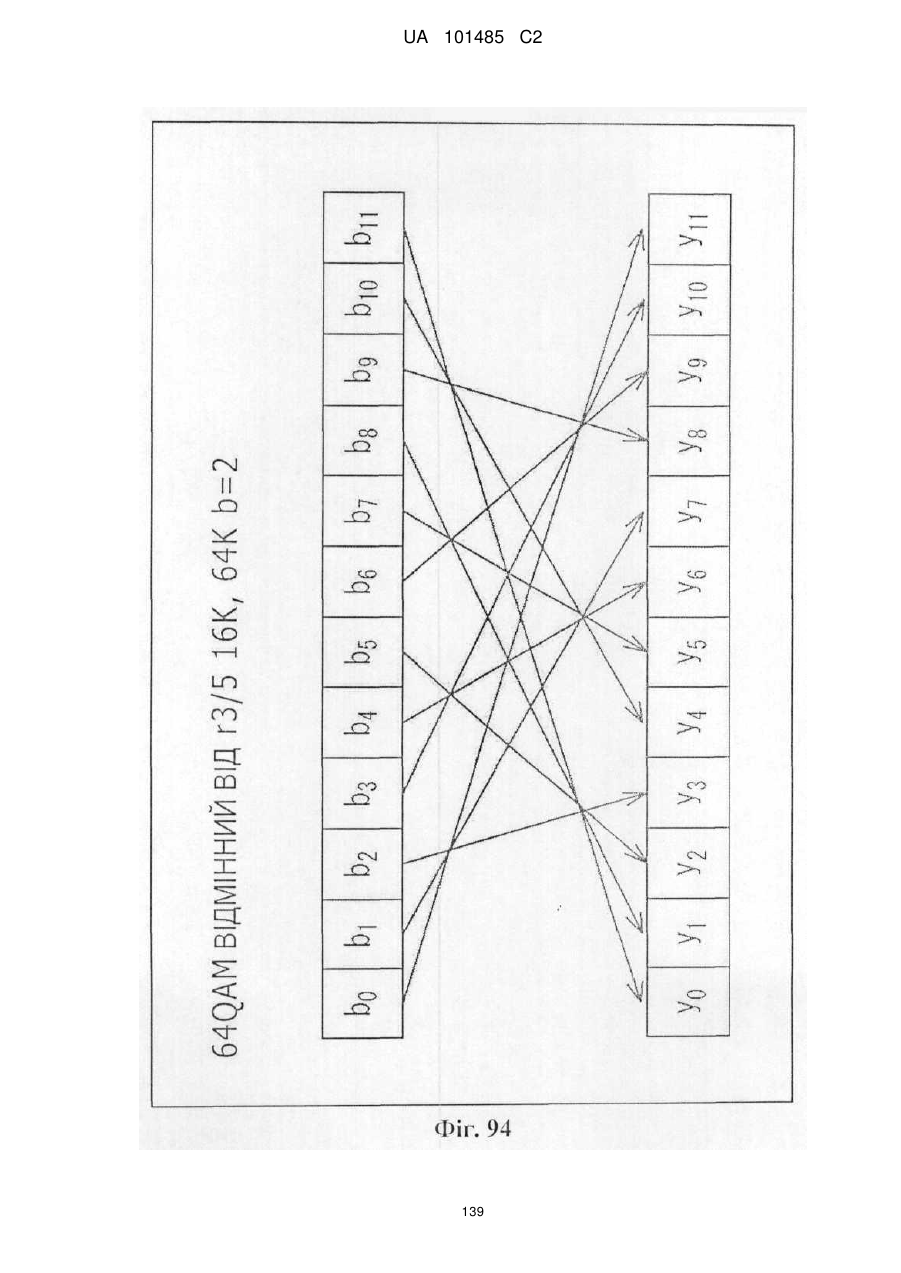

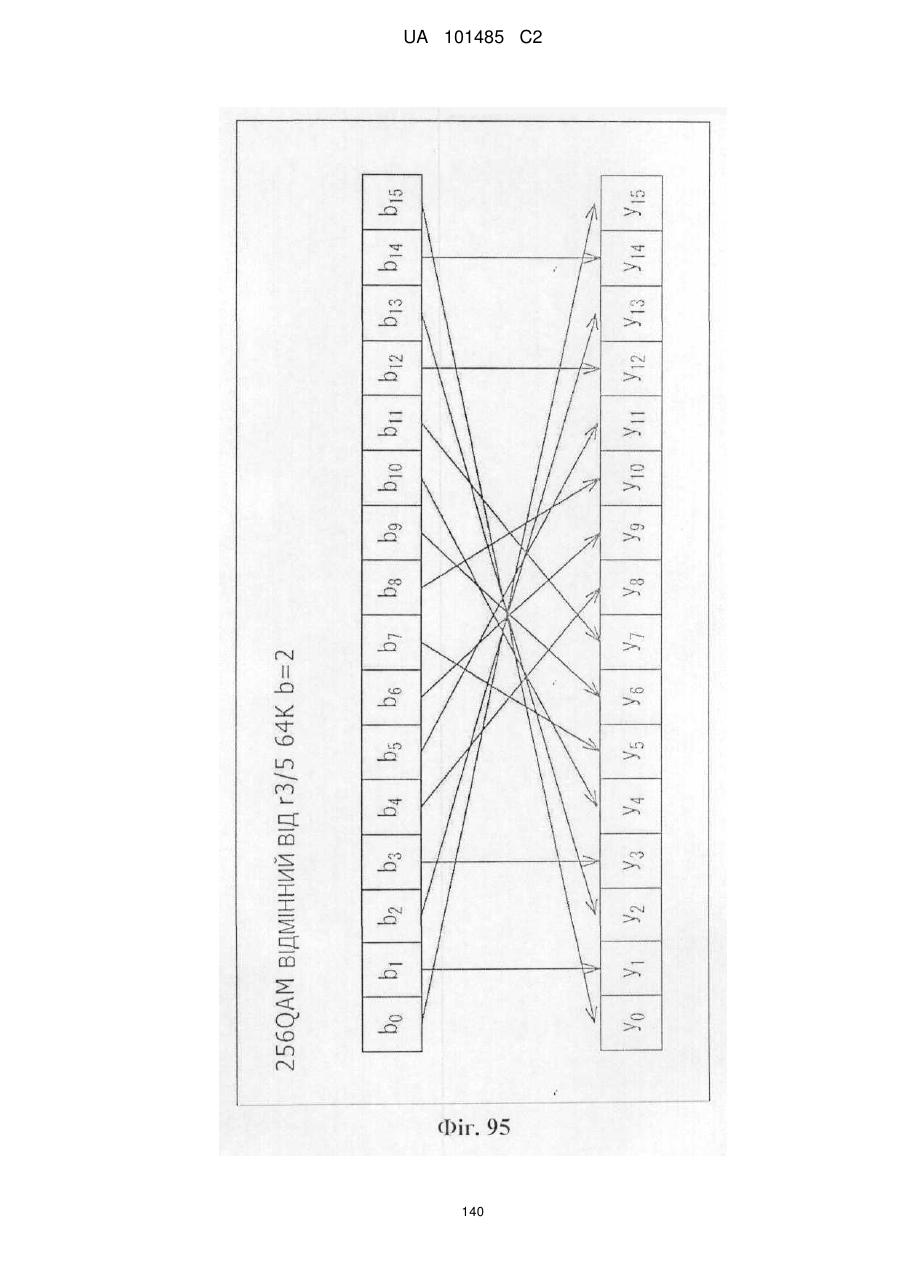

6. Пристрій обробки даних за п. 5, який відрізняється тим, що у випадку, коли один символ сформований з m кодових бітів коду LDPC, і коли довжина коду для коду LDPC становить N бітів, і задане додатне ціле число представлене як b, згаданий засіб зберігання зберігає mb бітів у напрямку рядка й зберігає N/(mb) бітів у напрямку стовпчика; кодові біти коду LDPC, записують у напрямку стовпчика згаданого засобу зберігання, після чого кодові біти зчитують у напрямку рядка, mb кодових бітів, зчитаних в напрямку рядка згаданого засобу зберігання, перетворюють в b символів.

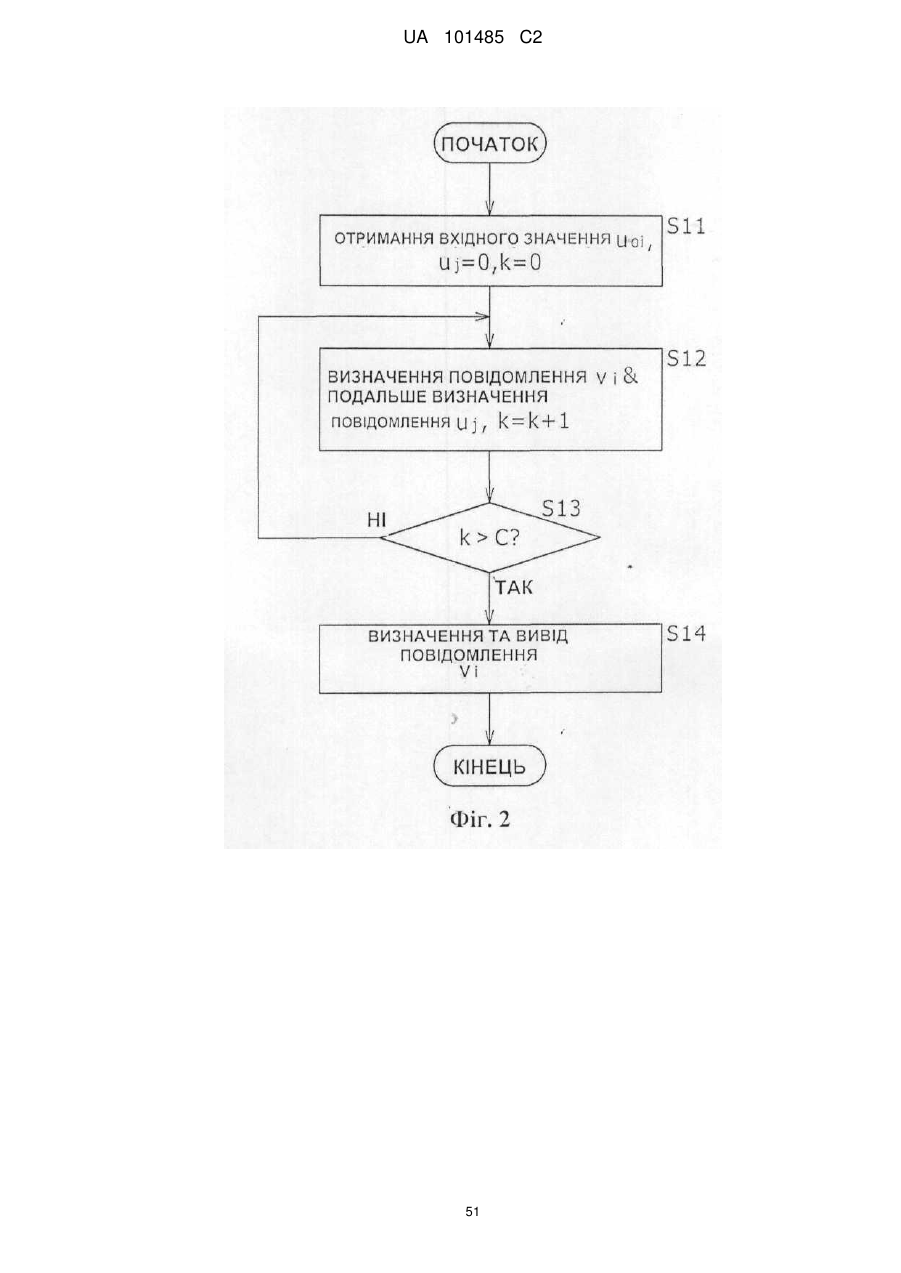

7. Спосіб обробки даних для пристрою обробки даних, який виконує перемежовування даних, що містить: етап, що виконується пристроєм обробки даних, що полягає у виконанні перемежовування парності, що полягає в перемежовуванні бітів парності коду LDPC, отриманого в результаті виконання кодування LDPC відповідно до матриці перевірки на парність, в якому матриця парності, яка являє собою частину, що відповідає бітам парності коду LDPC (низької щільності з контролем парності), має ступеневу структуру, індивідуально відносно положень інших бітів парності.

Текст