Процесор з семантичним контролем

Номер патенту: 88486

Опубліковано: 26.10.2009

Автори: Чертков Георгій Миколайович, Конорев Борис Михайлович, Манжос Юрій Семенович, Харченко Вячеслав Сергійович

Формула / Реферат

Процесор з семантичним контролем, що містить блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконуючого модуля та блок управління шиною, перший вхід-вихід якого є вхід-виходом процесора, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконуючого модуля, а через другу шину даних - з другим вхід-виходом блока комунікаційних регістрів, вхід-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістра ознак, відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами регістру ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами блоків регістрів загального призначення та тимчасових регістрів, а також блока комунікаційних регістрів, вихід якого з'єднаний з другим входом додавача адреси, перший та другий виходи блока тимчасових регістрів з'єднані відповідно з першим та другим інформаційними входами арифметико-логічного пристрою, вихід ознак якого з'єднаний з першим інформаційним входом регістра ознак, який відрізняється тим, що додатково має блоки регістрів тимчасових семантичних ознак і семантичних даних, оперативний запам'ятовуючий пристрій, постійні запам'ятовуючі пристрої результатів ділення, функції та результатів обчислення квадрата, додавач-віднімач, додавач даних, дешифратор команд, лічильники команд, адитивних команд, типів, кількості типів і опитування типів, реверсивний лічильник зсуву, зсувачі чисельника, знаменника, аргументу квадратора та результату квадратора, регістри ймовірності адитивних команд, ймовірності семантичних типів, операнду додавача даних і проміжних даних, блок порівняння, мультиплексори адреси, типів, чисельника і знаменника, демультиплексор, тригер, перший, другий, третій та четвертий елементи І, перший та другий елементи АБО, перший, другий та третій елементи НІ, причому відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з входами блока регістрів тимчасових семантичних ознак і блока регістрів семантичних даних, вхід-вихід якого через другу шину даних з'єднаний з входом-виходом блока регістрів тимчасових семантичних ознак, перший та другий виходи якого з'єднані відповідно з першим і другим інформаційними виходами додавача-віднімача, вихід якого з'єднаний з другою шиною даних, перший та другий виходи блока регістрів тимчасових семантичних ознак та вихід лічильника опитування типів з'єднані відповідно з першим-третім інформаційними входами мультиплексора адреси, вихід якого з'єднаний з входом адреси оперативного запам'ятовуючого пристрою, вихід якого з'єднаний з інформаційним входом лічильника типів та першим інформаційним входом мультиплексора типів, перший та другий виходи блока регістрів тимчасових семантичних ознак з'єднані відповідно з першим та другим входами блока порівняння, вихід якого з'єднаний з першим входом першого елемента І, вихід якого з'єднаний з першим входом елемента АБО, вихід якого з'єднаний з другим інформаційним входом регістра ознак, вихід блока черги інструкцій з'єднаний зі входом дешифратора команд, перший вихід якого з'єднаний з керуючим входом додавача-віднімача, другий вихід - з другим входом першого елемента АБО, третій вихід - з другим входом першого елемента І та керуючим входом лічильника адитивних команд, вихід якого з'єднаний з першим інформаційним входом мультиплексора чисельника, вихід якого з'єднаний з інформаційним входом зсувача чисельника, вихід зсувача чисельника з'єднаний з першим входом постійного запам'ятовуючого пристрою результатів ділення, вихід якого з'єднаний з інформаційними входами регістрів ймовірності адитивних команд та ймовірності семантичних типів, виходи яких з'єднані відповідно з першим та другим входами постійного запам'ятовуючого пристрою функції, вихід якого з'єднаний з третім інформаційним входом регістру ознак, відповідні виходи другої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами лічильників опитування типів, команд, типів та кількості типів, мультиплексорів адреси, типів та оперативного запам'ятовуючого пристрою, установчими входами зсувачів результату квадратора та аргументу квадратора, третім входом третього елемента І, рахунковим входом тригера та другим входом четвертого елемента І, обнулюючим входом реверсивного лічильника зсуву, відповідні виходи третьої групи виходів блока управління виконуючого модуля з'єднані з обнулюючими входами оперативного запам'ятовуючого пристрою та лічильників опитування типів, команд, адитивних команд, типів та кількості типів, вихід лічильника типів з'єднаний з інформаційним входом оперативного запам'ятовуючого пристрою, вихід лічильника кількості типів з'єднаний з другим інформаційним входом мультиплексора типів, вихід якого з'єднаний з інформаційним входом зсувача аргументу квадратора, вихід якого з'єднаний зі входом постійного запам'ятовуючого пристрою обчислення квадрата, вихід якого з'єднаний з інформаційним входом зсувача результату квадратора, вихід якого з'єднаний з інформаційним входом демультиплексора, перший вихід якого з'єднаний з першим інформаційним входом мультиплексора знаменника, вихід якого з'єднаний з інформаційним входом зсувача знаменника, вихід якого з'єднано з другим входом постійного запам'ятовуючого пристрою результатів ділення, другий вихід - через перший елемент Ш, з'єднаний з першим входом другого елемента І, вихід якого з'єднаний з входами керування зсувом зсувачів знаменника та чисельника, вихід лічильника команд з'єднаний з другим інформаційним входом мультиплексора знаменника, а другий вихід демультиплексора з'єднано з першим інформаційним входом додавача даних, вихід якого з'єднано з інформаційним входом регістра проміжних даних, вихід якого з'єднаний з інформаційним входом регістра операнду додавача даних та другим інформаційним входом мультиплексора чисельника, вихід регістра операнду додавача даних з'єднано з другим входом додавача даних, другий вихід зсувача аргументу квадратора з'єднаний через другий елемент НІ з першим входом третього елемента І, вихід якого з'єднаний з входом керування зсувом зсувача аргументу квадратора та додавальним входом реверсивного лічильника зсуву, перша група виходів якого з'єднана з групою входів другого елемента АБО, вихід якого з'єднано з першим входом четвертого елемента І, вихід якого з'єднаний зі входом керування зсувом зсуавача результату квадратора, другий вихід реверсивного лічильника зсуву з'єднано через третій елемент НІ з другим входом третього елемента І, вихід тригера з'єднано з віднімаючим входом реверсивного лічильника зсуву, а відповідні виходи четвертої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами демультиплексора, мультиплексорів чисельника, знаменника, регістрів ймовірності адитивних команд, ймовірності семантичних типів, операнду додавача даних і проміжних даних, обнулюючим входом регістра операнду додавача даних, установчими входами зсувачів знаменника та чисельника.

Текст

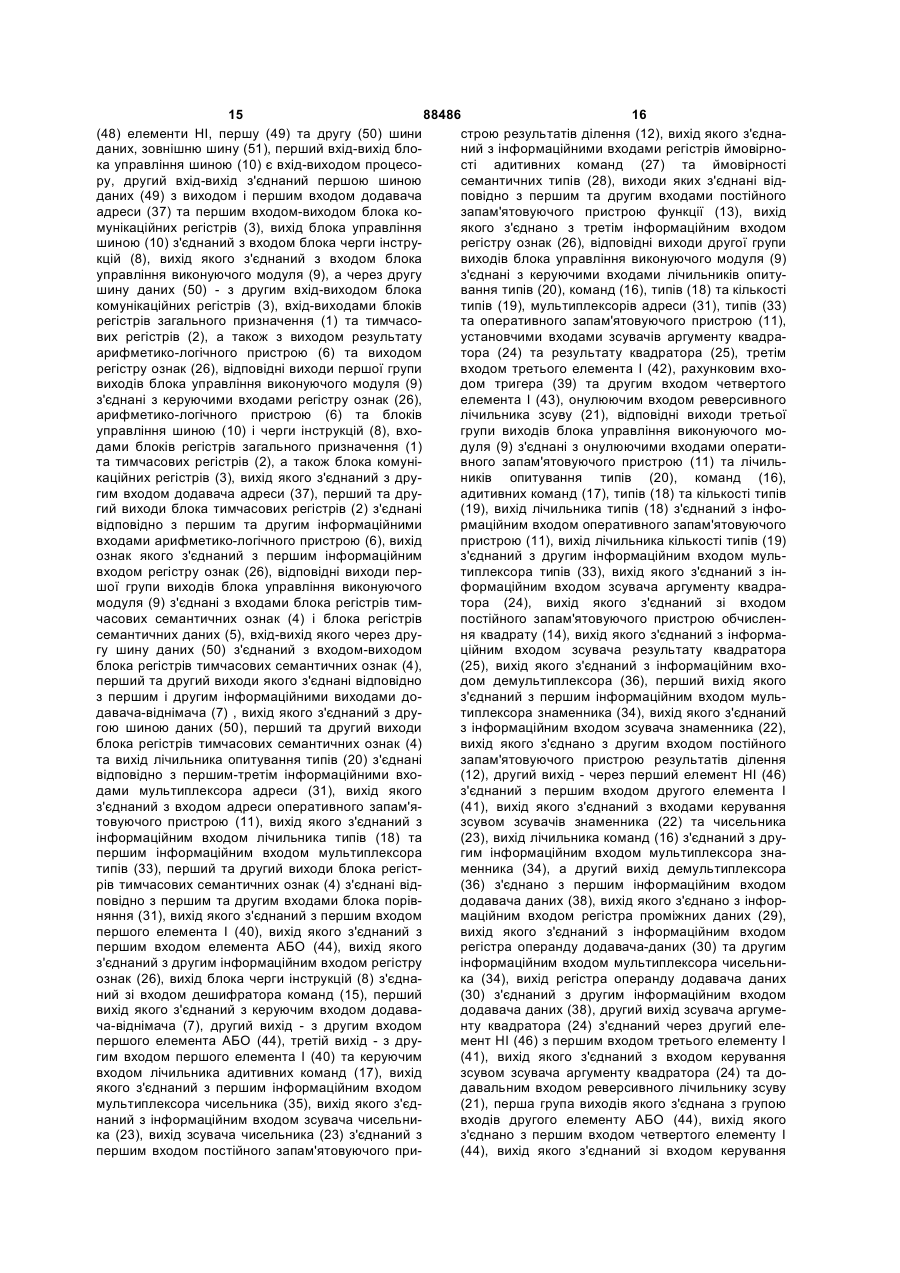

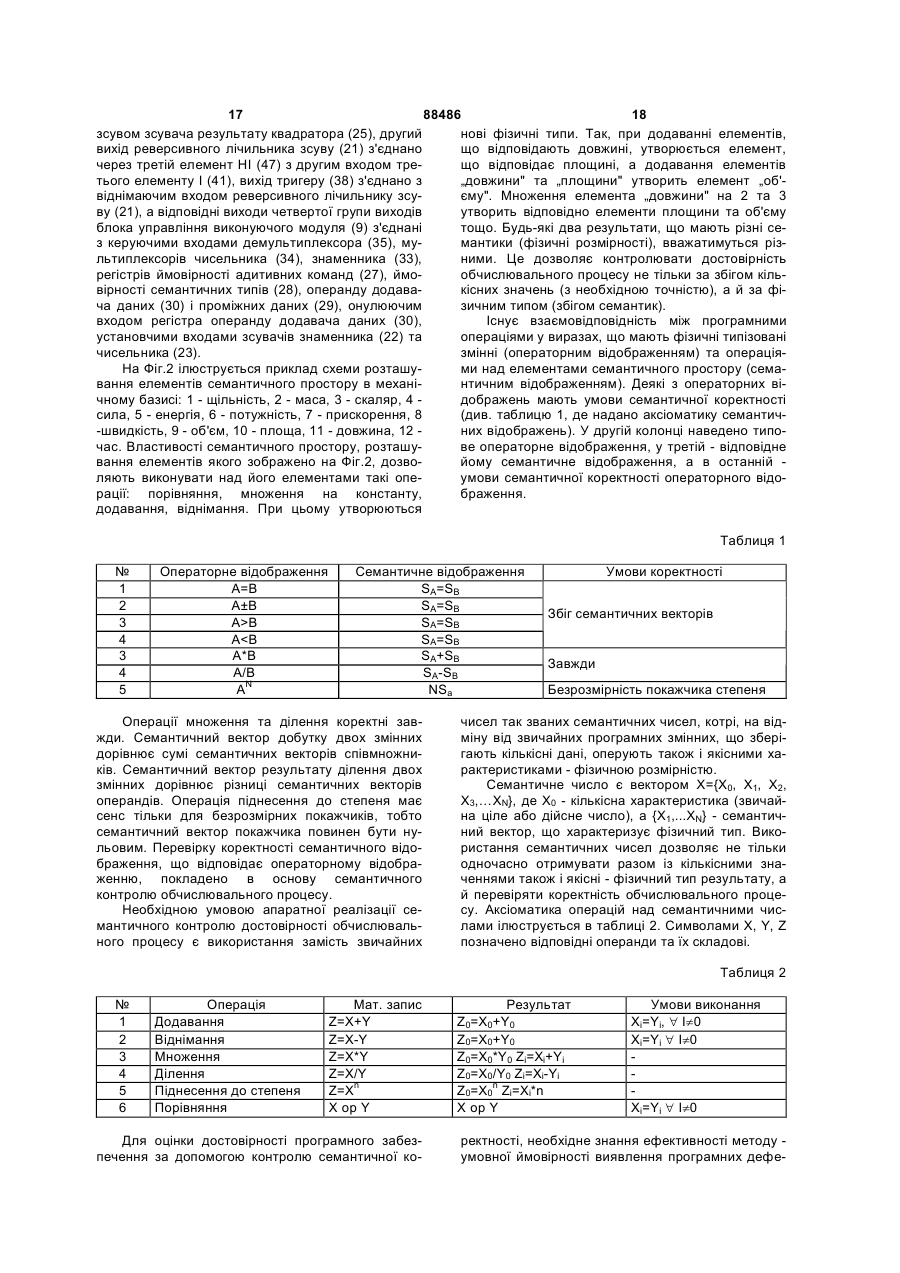

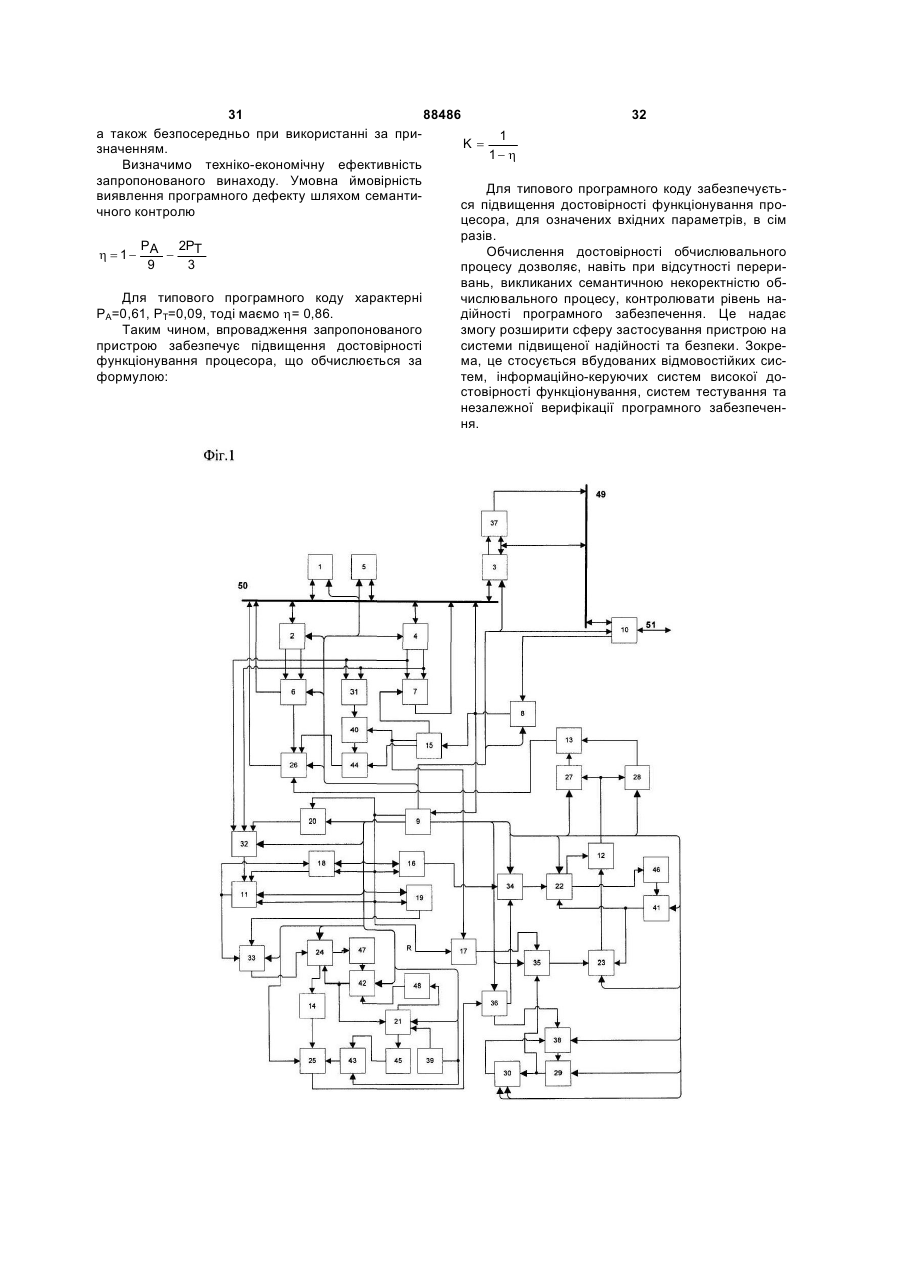

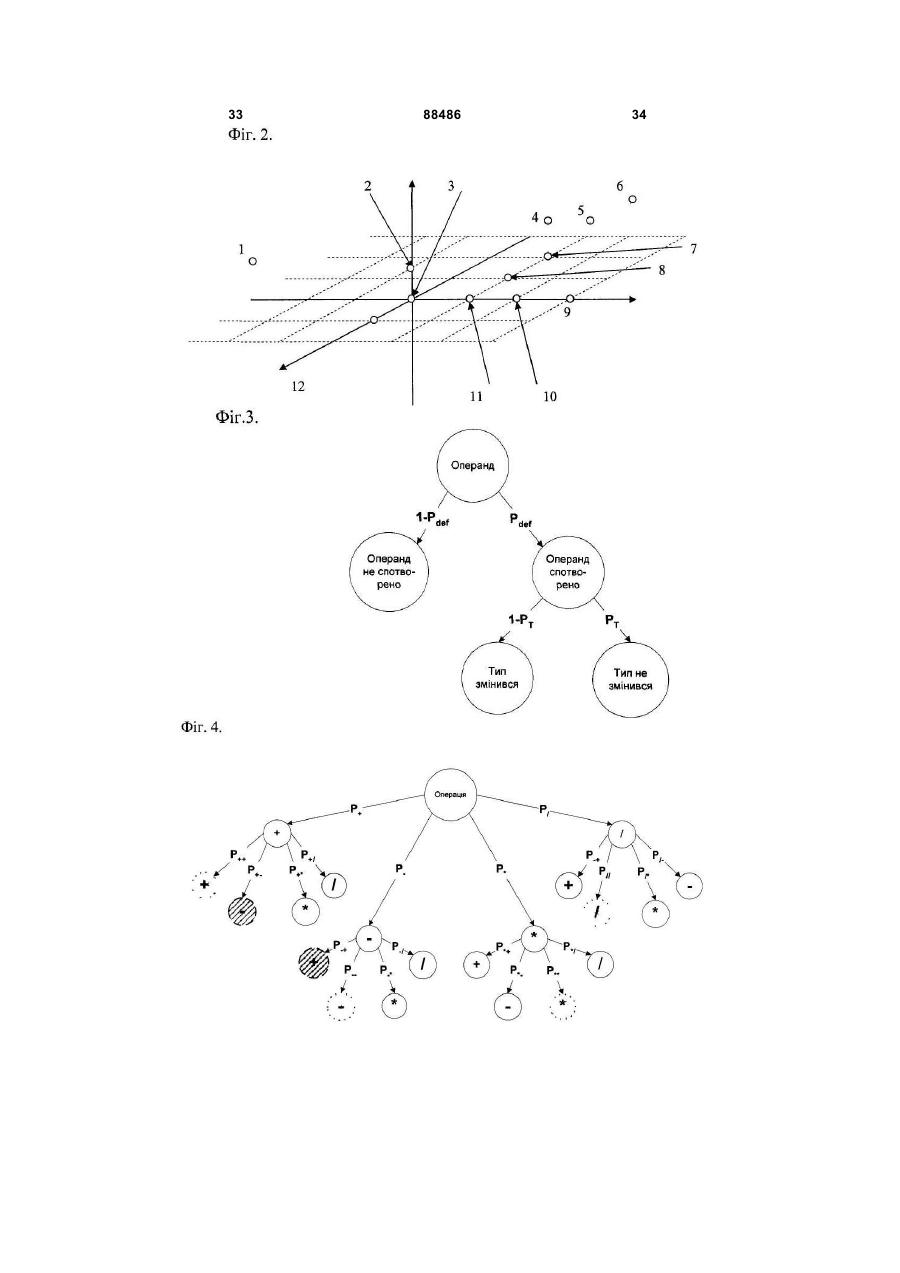

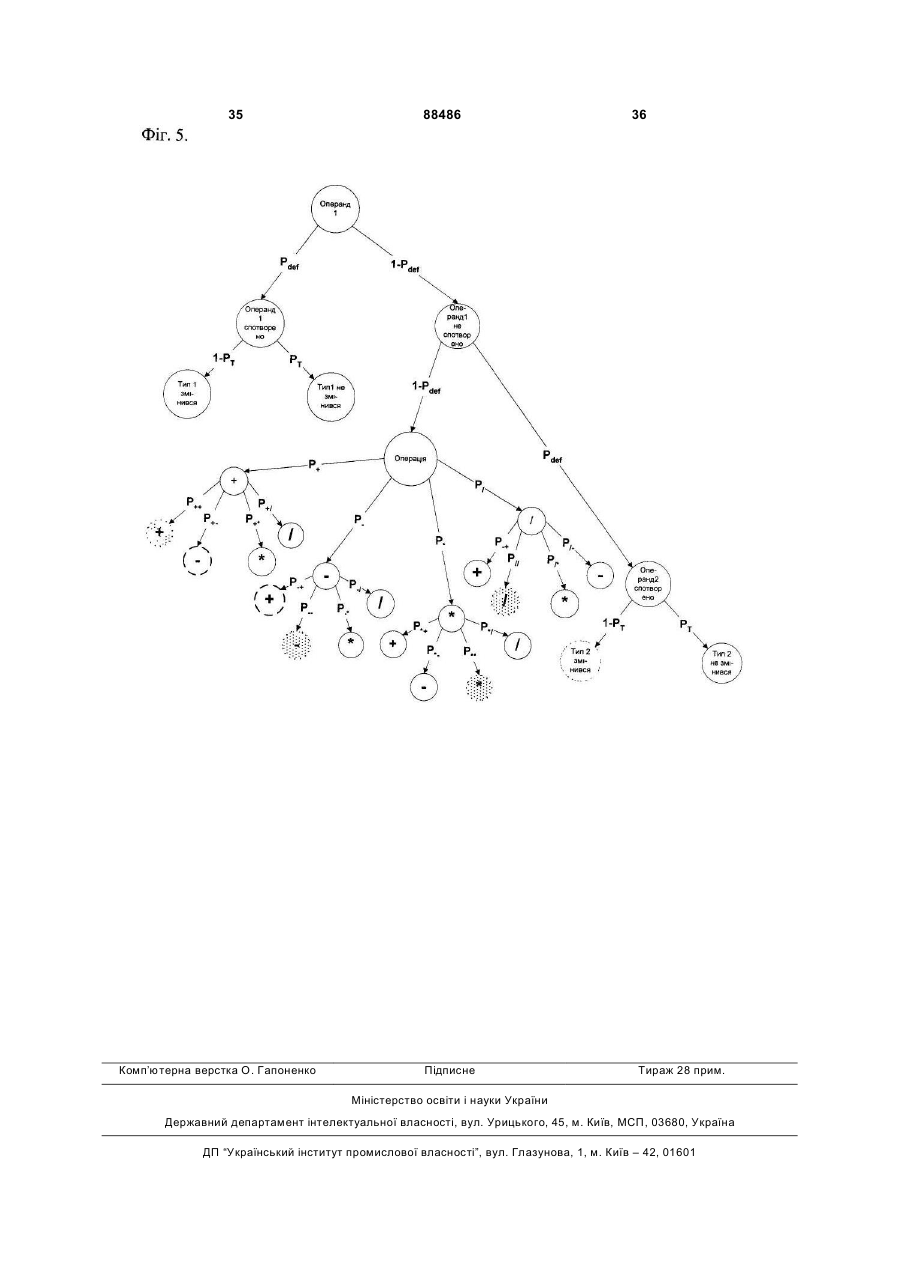

Процесор з семантичним контролем, що містить блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконуючого модуля та блок управління шиною, перший вхід-вихід якого є вхід-виходом процесора, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконуючого модуля, а через другу шину даних - з другим вхід-виходом блока комунікаційних регістрів, вхід-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістра ознак, відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами регістру ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами блоків регістрів загального призначення та тимчасових регістрів, а також блока комунікаційних регістрів, вихід якого з'єднаний з другим входом додавача адреси, перший та другий виходи блока тимчасових регістрів з'єднані відповідно з першим та дру 2 (19) 1 3 88486 4 гим входом першого елемента АБО, третій вихід шим інформаційним входом мультиплексора зназ другим входом першого елемента І та керуючим менника, вихід якого з'єднаний з інформаційним входом лічильника адитивних команд, вихід якого входом зсувача знаменника, вихід якого з'єднано з з'єднаний з першим інформаційним входом мульдругим входом постійного запам'ятовуючого притиплексора чисельника, вихід якого з'єднаний з строю результатів ділення, другий вихід - через інформаційним входом зсувача чисельника, вихід перший елемент Ш, з'єднаний з першим входом зсувача чисельника з'єднаний з першим входом другого елемента І, вихід якого з'єднаний з входапостійного запам'ятовуючого пристрою результатів ми керування зсувом зсувачів знаменника та чиділення, вихід якого з'єднаний з інформаційними сельника, вихід лічильника команд з'єднаний з входами регістрів ймовірності адитивних команд другим інформаційним входом мультиплексора та ймовірності семантичних типів, виходи яких знаменника, а другий вихід демультиплексора з'єднані відповідно з першим та другим входами з'єднано з першим інформаційним входом додавапостійного запам'ятовуючого пристрою функції, ча даних, вихід якого з'єднано з інформаційним вихід якого з'єднаний з третім інформаційним вховходом регістра проміжних даних, вихід якого з'єддом регістру ознак, відповідні виходи другої групи наний з інформаційним входом регістра операнду виходів блока управління виконуючого модуля додавача даних та другим інформаційним входом з'єднані з керуючими входами лічильників опитумультиплексора чисельника, вихід регістра операвання типів, команд, типів та кількості типів, мульнду додавача даних з'єднано з другим входом дотиплексорів адреси, типів та оперативного западавача даних, другий вихід зсувача аргументу м'ятовуючого пристрою, установчими входами квадратора з'єднаний через другий елемент НІ з зсувачів результату квадратора та аргументу квапершим входом третього елемента І, вихід якого дратора, третім входом третього елемента І, рахуз'єднаний з входом керування зсувом зсувача арнковим входом тригера та другим входом четвергументу квадратора та додавальним входом реветого елемента І, обнулюючим входом рсивного лічильника зсуву, перша група виходів реверсивного лічильника зсуву, відповідні виходи якого з'єднана з групою входів другого елемента третьої групи виходів блока управління виконуюАБО, вихід якого з'єднано з першим входом четвечого модуля з'єднані з обнулюючими входами ртого елемента І, вихід якого з'єднаний зі входом оперативного запам'ятовуючого пристрою та лічикерування зсувом зсувача результату квадратора, льників опитування типів, команд, адитивних кодругий вихід реверсивного лічильника зсуву з'єдманд, типів та кількості типів, вихід лічильника нано через третій елемент НІ з другим входом типів з'єднаний з інформаційним входом оператитретього елемента І, вихід тригера з'єднано з відвного запам'ятовуючого пристрою, вихід лічильнинімаючим входом реверсивного лічильника зсуву, ка кількості типів з'єднаний з другим інформаційа відповідні виходи четвертої групи виходів блока ним входом мультиплексора типів, вихід якого управління виконуючого модуля з'єднані з керуюз'єднаний з інформаційним входом зсувача аргучими входами демультиплексора, мультиплексоменту квадратора, вихід якого з'єднаний зі входом рів чисельника, знаменника, регістрів ймовірності постійного запам'ятовуючого пристрою обчисленадитивних команд, ймовірності семантичних типів, ня квадрата, вихід якого з'єднаний з інформаційоперанду додавача даних і проміжних даних, обним входом зсувача результату квадратора, вихід нулюючим входом регістра операнду додавача якого з'єднаний з інформаційним входом демульданих, установчими входами зсувачів знаменника типлексора, перший вихід якого з'єднаний з перта чисельника. Винахід належить до обчислювальної техніки і може бути використаний при розробці засобів обробки та контролю даних в інформаційноаналітичних та інформаційно-керуючих системах підвищеної надійності, зокрема, при проектуванні вбудованих відмовостійких систем, систем тестування, верифікації тощо. Відомий пристрій для контролю арифметикологічних пристроїв (авторське свідоцтво СРСР №1815639, кл. G 0611/00, 1993), що має блок порівняння, додавач, чотири мультиплексори. Недоліком цього пристрою є обмежені функціональні можливості, оскільки він не забезпечує контроль семантичного змісту даних, що обробляються, та контроль достовірності обчислювального процесу. Відомий пристрій для ділення (авторське свідоцтво СРСР №1667077, G06F11/00, 7/52, 1991), що містить групу додавачів, вузли згортки за модулем два, два блоки порівняння. Недоліком цього пристрою є низька достовірність функціонування. Вона обмежена через те, що правильність виконання операцій контролюється тільки за рахунок перевірки даних на парність. Відомий процесор з семантичним контролем (заявка на винахід №а200512335 від 12.12.2005), який має центральний та додатковий арифметичний пристрій, оперативний запам'ятовуючий пристрій даних, постійний запам'ятовуючий пристрій команд, лічильник команд, послідовний порт обміну, блок регістрів керування, мультиплексори даних і адреси, шину команд і шину даних. Цей пристрій, що побудований на базі архітектури сигнального процесора TMS32025, здійснює контроль семантичної коректності. Але, по-перше, засоби контролю цього пристрою жорстко спеціалізовані під обробку сигнальної інформації, що суттєво звужує сферу доцільного використання; по-друге, достовірність функціонування обмежена тільки виявленням факту порушення семантичної коректності без оперативного оцінювання ступеня 5 88486 6 довіри до результатів контролю при невиявленні го є вхід-вихідом процесору, другий вхід-вихід порушень. з'єднаний першою шиною даних з виходом і перНайбільш близьким до пропонованого є прошим входом додавача адреси та першим входомцесор, що має блок регістрів загального признавиходом блока комунікаційних регістрів, вихід блочення, блок комунікаційних регістрів, блок тимчака управління шиною з'єднаний з входом блока сових регістрів, арифметико-логічний пристрій, черги інструкцій, вихід якого з'єднаний з входом регістр ознак, додавач адреси, блок черги інструкблока управління виконуючого модуля, а через цій, блок управління виконуючого модуля та блок другу шину даних - з другим вхід-виходом блока управління шиною, перший вхід-вихід якого є вхідкомунікаційних регістрів, вхід-виходами блоків ревихідом процесору, другий вхід-вихід з'єднаний гістрів загального призначення та тимчасових регіпершою шиною даних з виходом і першим входом стрів, а також з виходом результату арифметикододавача адреси та першим входом-виходом блологічного пристрою та виходом регістру ознак, ка комунікаційних регістрів, вихід блока управління відповідні виходи першої групи виходів блока шиною з'єднаний з входом блока черги інструкцій, управління виконуючого модуля з'єднані з керуювихід якого з'єднаний з входом блока управління чими входами регістру ознак, арифметиковиконуючого модуля, а через другу шину даних - з логічного пристрою та блоків управління шиною і другим вхід-виходом блока комунікаційних регістчерги інструкцій, входами блоків регістрів загальрів, вхід-виходами блоків регістрів загального приного призначення та тимчасових регістрів, а також значення та тимчасових регістрів, а також з вихоблока комунікаційних регістрів, вихід якого з'єднадом результату арифметико-логічного пристрою ний з другим входом додавача адреси, перший та та виходом регістру ознак, відповідні виходи пердругий виходи блока тимчасових регістрів з'єднані шої групи виходів блока управління виконуючого відповідно з першим та другим інформаційними модуля з'єднані з керуючими входами регістру входами арифметико-логічного пристрою, вихід ознак, арифметико-логічного пристрою та блоків ознак якого з'єднаний з першим інформаційним управління шиною і черги інструкцій, входами бловходом регістру ознак, згідно з винаходом додатків регістрів загального призначення та тимчасоково має блоки регістрів тимчасових семантичних вих регістрів, а також блока комунікаційних регістознак і семантичних даних, оперативний запам'ярів, вихід якого з'єднаний з другим входом товуючий пристрій, постійні запам'ятовуючі придодавача адреси, перший та другий виходи блока строї результатів ділення, функції та результатів тимчасових регістрів з'єднані відповідно з першим обчислення квадрату, додавач-віднімач, додавач та другим інформаційними входами арифметикоданих, дешифратор команд, лічильники команд, логічного пристрою, вихід ознак якого з'єднаний з адитивних команд, типів, кількості типів і опитупершим інформаційним входом регістру ознак вання типів, реверсивний лічильник зсуву, зсувачі [80С186ЕА/80С188ЕА Microprocessor User's чисельника, знаменника, аргументу квадратора та Manual. Intel Corporation Literature Sales P.O. Box результату квадратора, регістри ймовірності ади7641 Mt. Prospect, IL 60056-7641. - с. 2-2, fig. 2-1]. тивних команд, ймовірності семантичних типів, Недоліком цього пристрою є низька достовіроперанду додавача даних, проміжних даних, блок ність функціонування, обумовлена обмеженістю порівняння, мультиплексори адреси, типів, чисеможливостей засобів контролю процесора. Контльника і знаменника, демультиплексор, тригер, роль функціонування процесора може виконуваперший, другий, третій та четвертий елементи І, тися тільки програмними засобами. Це призводить перший та другий елементи АБО, перший, другий до збільшення ймовірності помилок другого роду, та третій елементи НІ, причому відповідні виходи тобто невиявлення часткової втрати працездатнопершої групи виходів блока управління виконуючості внаслідок збоїв апаратних засобів, або прояву го модуля з'єднані з входами блока регістрів тимдефектів програмного забезпечення [див. Харченчасових семантичних ознак і блока регістрів семако B.C. та ін. Основи діагностики цифрових сиснтичних даних, вхід-вихід якого через другу шину тем. Підручник. Міносвіти та науки України. 2004. даних з'єднаний з входом-виходом блока регістрів С. 56-66]. Програмна реалізація засобів контролю тимчасових семантичних ознак, перший та другий потребує додаткових витрат часу, що знижує опевиходи якого з'єднані відповідно з першим і другим ративність контролю і продуктивність процесора у інформаційними виходами додавача-віднімача, цілому. вихід якого з'єднаний з другою шиною даних, перВ основу винаходу покладено завдання вдосший та другий виходи блока регістрів тимчасових коналення процесору шляхом підвищення достосемантичних ознак та вихід лічильника опитування вірності функціонування за рахунок реалізації опетипів з'єднані відповідно з першим-третім інфорративного семантичного контролю процесу маційними входами мультиплексора адреси, вихід обробки даних, а також визначення кількісної хаякого з'єднаний з входом адреси оперативного рактеристики - ймовірності відсутності програмних запам'ятовуючого пристрою, вихід якого з'єднаний дефектів та незареєстрованих збоїв. з інформаційним входом лічильника типів та перПоставлене завдання вирішується тим, що шим інформаційним входом мультиплексора типів, процесор з семантичним контролем програмного перший та другий виходи блока регістрів тимчасозабезпечення, який містить блок регістрів загальвих семантичних ознак з'єднані відповідно з перного призначення, блок комунікаційних регістрів, шим та другим входами блока порівняння, вихід блок тимчасових регістрів, арифметико-логічний якого з'єднаний з першим входом першого елемепристрій, регістр ознак, додавач адреси, блок чернта І, вихід якого з'єднаний з першим входом елеги інструкцій, блок управління виконуючого модуля мента АБО, вихід якого з'єднаний з другим інфорта блок управління шиною, перший вхід-вихід якомаційним входом регістру ознак, вихід блока черги 7 88486 8 інструкцій з'єднаний зі входом дешифратора коквадратора та додавальним входом реверсивного манд, перший вихід якого з'єднаний з керуючим лічильнику зсуву, перша група виходів якого з'єдвходом додавача-віднімача, другий вихід - з друнана з групою входів другого елементу АБО, вихід гим входом першого елемента АБО, третій вихід якого з'єднано з першим входом четвертого елез другим входом першого елемента І та керуючим менту І, вихід якого з'єднаний зі входом керування входом лічильника адитивних команд, вихід якого зсувом зсувача результату квадратора, другий з'єднаний з першим інформаційним входом мульвихід реверсивного лічильника зсуву з'єднано четиплексора чисельника, вихід якого з'єднаний з рез третій елемент НІ з другим входом третього інформаційним входом зсувача чисельника, вихід елементу І, вихід тригеру з'єднано з віднімаючим зсувача чисельника з'єднаний з першим входом входом реверсивного лічильнику зсуву, а відповідпостійного запам'ятовуючого пристрою результатів ні виходи четвертої групи виходів блока управлінділення, вихід якого з'єднаний з інформаційними ня виконуючого модуля з'єднані з керуючими вховходами регістрів ймовірності адитивних команд дами демультиплексора, мультиплексорів та ймовірності семантичних типів, виходи яких чисельника, знаменника, регістрів ймовірності з'єднані відповідно з першим та другим входами адитивних команд, ймовірності семантичних типів, постійного запам'ятовуючого пристрою функції, операнду додавача даних і проміжних даних, онувихід якого з'єднано з третім інформаційним вхолюючим входом регістра операнду додавача дадом регістру ознак, відповідні виходи другої групи них, установчими входами зсувачів знаменника та виходів блока управління виконуючого модуля чисельника. з'єднані з керуючими входами лічильників опитуЗапропонований процесор з семантичним конвання типів, команд, типів та кількості типів, мультролем має новий склад елементів та нову органітиплексорів адреси, типів та оперативного запазацію зв'язків між ними, які забезпечують нові техм'ятовуючого пристрою, установчими входамим нічні властивості винаходу. Технічним зсувачів результату квадратора та аргументу кварезультатом, який при цьому досягається, є піддратора, третім входом третього елемента І, рахувищення достовірності функціонування. нковим входом тригера та другим входом четверСутність винаходу полягає в тому, що у процетого елемента І, онулюючим входом реверсивного сорі реалізується метод контролю функціонування лічильника зсуву, відповідні виходи третьої групи за рахунок оперативної перевірки правильності виходів блока управління виконуючого модуля виконання операцій шляхом аналізу коректності з'єднані з онулюючими входами оперативного заперетворень розмірностей даних, що обробляютьпам'ятовуючого пристрою та лічильників опитуся, та визначення умовної ймовірності відсутності вання типів, команд, адитивних команд, типів та семантичних дефектів, обумовлених дефектами кількості типів, вихід лічильника типів з'єднаний з програмного забезпечення, невиявленими апаратінформаційним входом оперативного запам'ятоними збоями та відмовами. Тобто внаслідок ввевуючого пристрою, вихід лічильника кількості типів дення додаткових елементів та їх зв'язків додаткоз'єднаний з другим інформаційним входом мульво контролюється семантична коректність типлексора типів, вихід якого з'єднаний з інформапрограмного забезпечення та визначається достоційним входом зсувача аргументу квадратора, вірність обчислювального процесу. вихід якого з'єднаний зі входом постійного запаСемантичний контроль достовірності обчисм'ятовуючого пристрою обчислення квадрату, вилювального процесу базується на розгляді харакхід якого з'єднаний з інформаційним входом зсутеристик функціональності інформаційно-керуючих вача результату квадратора, вихід якого з'єднаний систем у так званому семантичному просторі [Маз інформаційним входом демультиплексора, пернжос Ю.С. Семантический контроль программного ший вихід якого з'єднаний з першим інформаційобеспечения систем критического применения // ним входом мультиплексора знаменника, вихід Авіаційно-космічна техніка і технологія. - Харків: якого з'єднаний з інформаційним входом зсувача Нац. аерокосм. ун-т „Харк. авіац. ін-т", 2002. - Вип. знаменника, вихід якого з'єднано з другим входом 34. - С. 207-212]. Достовірність обчислювального постійного запам'ятовуючого пристрою результатів процесу, тобто умовна ймовірність відсутності седілення, другий вихід - через перший елемент HI мантичних дефектів обчислюється за допомогою з'єднаний з першим входом другого елемента І, методів теорії ймовірностей на підставі статистичвихід якого з'єднаний з входами керування зсувом них характеристик програмного коду [Манжос Ю.С. зсувачів знаменника та чисельника, вихід лічильОценка эффективности независимой верификаника команд з'єднаний з другим інформаційним ции программного обеспечения // Авіаційновходом мультиплексора знаменника, а другий викосмічна техніка і технологія. - Харків: Нац. аерохід демультиплексора з'єднано з першим інфоркосм. ун-т „Харк. авіац. ін-т", 2004. -№7. - С.210маційним входом додавача даних, вихід якого 214]. Семантичний простір - n-вимірний метричний з'єднано з інформаційним входом регістра проміжпростір, що складається із множини X елементів, них даних, вихід якого з'єднаний з інформаційним кожний з яких відповідає фізичному типу. Кожному входом регістра операнда додавача даних та друз елементів семантичного простору відповідає гим інформаційним входом мультиплексора чисесемантичний вектор, проведений із початку коорльника, вихід регістру операнду додавача даних динат. Координати вектора відповідають розмірз'єднано з другим інформаційним входом додаваності фізичного типу обраної системи одиниць. ча даних другий вихід зсувача аргументу квадраБазисом семантичного простору є n незалежних тора з'єднаний через другий елемент HI з першим (ортогональних) векторів одиничної довжини, кожвходом третього елементу І, вихід якого з'єднаний ний з яких відповідає одній з основних одиниць з входом керування зсувом зсувача аргументу обраної системи одиниць. Так для системи оди 9 88486 10 ниць СГС базисом є {Довжина [см]; Маса [грам]; ника, аргументу квадратора та результату квадраЧас [секунда]}. тора, регістри ймовірності адитивних команд, Умовна ймовірність виявлення програмного ймовірності семантичних типів, операнду додавадефекту шляхом семантичного контролю залежить ча-даних і проміжних даних, блок порівняння, мувід статистичних характеристик програмного коду і льтиплексори адреси, типів, чисельника і знаменданих, що обробляються, а саме: ймовірності поника, демультиплексор, тригер, перший, другий, яви адитивних операцій у потоці команд РА, ймовітретій та четвертий елементи І, перший та другий рності збереження семантичного типу даних під елементи АБО, перший, другий та третій елементи час спотворення операнду РТ та ймовірності відсуHI. Введення оперативного запам'ятовуючого тності програмних дефектів у коді P , та визнаdef пристрою та його зв'язків дозволило накопичувати чається за формулою: дані про кількість використання різних семантичних типів у коді, що виконується, завдяки тому, що æP ö на адресний вхід оперативного запам'ятовуючого P2 ç A ÷ + Pdef PT + PT пристрою надходять через мультиплексор адреси def è 3 ø h = 1семантичні вектори операндів, що зберігаються у 2 +P P блоці регістрів тимчасових семантичних ознак, def + 1 def кожний з яких містить семантичні ознаки операндів, або поточна адреса з лічильника опитування Для програмного забезпечення, що експлуатутипів. Вихід оперативного запам'ятовуючого приється, P ймовірність відсутності програмних def строю зв'язаний з інформаційним входом лічильдефектів близька до 1, а умовна ймовірність виявника типів. Кожного разу при виконанні операцій зміст відповідної комірки оперативного запам'ятоPA 2PT лення програмного дефекту: h = 1 . вуючого пристрою заноситься до лічильника типів, 9 3 де інкрементується, після чого знову заносить за Ймовірність появи адитивних операцій визнацією ж адресою до оперативного запам'ятовуючоN го пристрою. Під час формування адреси, на підчається як PA = a , де Na - кількість адитивних NS ставі семантичних ознак операндів, з кожної з складових семантичного вектору виділяється знаоперацій у коді; NS - загальна кількість операцій у ковий біт та кілька молодших розрядів. коді. Надалі до адитивних операцій будемо відноВведення лічильника опитування типів та його сити операції присвоєння, порівняння, додавання зв'язків забезпечує формування поточної семанта віднімання. тичної адреси, що необхідно для нарахування кіЙмовірність збереження семантичного типу під лькості використання всіх типів NTS. час спотворення операнду ΡT визначається за фоВведення мультиплексора адреси та його m зв'язків забезпечує під час обчислення процесормулою: PT = å PTi (1 - PTi ) . Після тотожних перером обчислення достовірності передачу на адресi =1 ний вхід оперативного запам'ятовуючого пристрою m NTi 2 або семантичних операндів, що зберігаються у творень маємо: PT = 1 - å Pn , де PTi = блоці регістрів тимчасових семантичних ознак або NTS i= 1 значення лічильника опитування типів, причому ймовірність вибору i-типу даних, де NTi - кількість вибір адреси здійснюється блоком управління виоперандів, що належать і- семантичному типу, а конуючого модулем. NTS - загальна кількість операндів. Введення блока регістрів семантичних даних Достовірність обчислювального процесу, при та їх зв'язків забезпечує можливість виконання невиявлені семантичних дефектів визначається: семантичного контролю коректності обчислювальm ного процесу паралельно із основним обчислюва2 å N Ti льним процесом. 1 NA 2 i= 1 Введення тимчасових блока регістрів тимча. h= + 2 3 9NS 3 m сових семантичних ознак та їх зв'язків забезпечує æ ö ç N ÷ тимчасове збереження семантичних векторів для ç å TS ÷ здійснення операцій порівняння у блоці порівняння èi = 1 ø та додавання/віднімання у додавачі/віднімачі. Реалізація семантичного контролю обчислюВведення блока порівняння та його зв'язків вального процесу та визначення його достовірносзабезпечує контроль збігу семантичних векторів, ті потребує використання у пристрої для перевірки що зберігаються у блоці тимчасових семантичних та обчислення семантичних та статистичних хараознак для адитивних команд. Результат порівнянктеристик програмного забезпечення: блоки регісня, що для еквівалентних семантичних векторів трів тимчасових семантичних ознак і семантичних повинен бути 1, а у іншому випадку 0, передається даних, оперативний запам'ятовуючий пристрій, на перший вхід першого елемента. постійні запам'ятовуючі пристрої результатів діВведення додавача-віднімача та його зв'язків лення, функції та результатів обчислення квадразабезпечує складання та віднімання семантичних ту, додавач-віднімач, додавач даних, дешифратор векторів, що зберігаються у блоці регістрів тимчакоманд, лічильники команд, адитивних команд, сових семантичних ознак під час семантичного типів, кількості типів і опитування типів, реверсивконтролю відповідно операцій множення та діленний лічильник зсуву, зсувачі чисельника, знамення. 11 88486 12 Введення першого елементу І та його зв'язків розрядів на які було зсунуто аргумент квадратора, забезпечує формування логічної одиниці під час що зберігається у відповідному зсувачі, формувиконання семантично-коректних адитивних опевання сигналу, що обмежує зсув нульових даних рацій, або логічного нуля у протилежному випадку. зсувачем аргументу квадратора, а також формуВведення першого елемента АБО та його зв'явання сигналу для керування зсувачем результату зків забезпечує на підставі сигналу „Неадитивна квадратора. команда", що надходить з дешифратора команд, Введення другого елементу АбО та його зв'язта сигналу що надходить з виходу першого елеків забезпечує дозвільний сигнал на першому вхомента І, формування ознаки семантичної коректді четвертого елементу І, у разі якщо у реверсивності результату, що надходить на другий інфорному лічильнику зсуву зберігається результат маційний вхід регістру ознак. більший нуля. Введення дешифратора команд та його зв'язВведення четвертого елементу І та його зв'язків забезпечує, на підставі інструкції, що виконуків забезпечує керування зсувом даних зсувачем ється та надходить з блока черги інструкцій, форрезультату квадратора завдяки керуючим сигнамування сигналів: „Адитивна команда", що лам, що надходять з блока управління виконуючонадходить до першого елементу І та лічильника го модуля та другого елемента АБО. адитивних команд; „Неадитивна команда", що Введення тригера та його зв'язків забезпечує надходить на другий вхід елемента АБО; „Мультиділення у двічі кількості керуючих імпульсів, що плклікативна команда", що надходить на керуючий надходять на віднімаючий вхід реверсивного лічивхід додавача-віднімача. льника зсуву, що необхідно для керування зсуваВведення лічильника команд та його зв'язків чем результату квадратора, зсув якого повинен забезпечує, на підставі сигналу про вибір наступбути у двічі більшим за зсув зсувача аргументу ної команди, що надходить на керуючий вхід з сисквадратора. теми керування виконуючого модуля, формування Введення постійного запам'ятовуючого приданих про загальну кількість команд, що були вистрою обчислення квадрату та його зв'язків забезконані. печує приблизному обчисленню квадрату числа, Введення лічильника кількості типів та його що відповідає або старшим розрядам загальної зв'язків забезпечує під час визначення достовірнокількості використання всіх семантичних типів, або сті підрахування загальної кількості використання старшим розрядам кількості використання одного з різних семантичних типів. семантичних типів у програмі. Введення лічильника типів та його зв'язків заВведення зсувача результату квадратора та безпечує під час визначення достовірності підрайого зв'язків забезпечує збереження результату хування кількості використання різних семантичобчислення квадрату, що надходить з постійного них типів. Збільшення значень лічильника типів запам'ятовуючого пристрою обчислення квадрату, здійснюється синхронно зі збільшенням значення його зсуву на необхідну кількість розрядів, а також лічильника кількості типів. передачі даних до демультиплексора. Введення мультиплексора типів та його зв'язВведення лічильника адитивних команд та йоків забезпечує направлення на зсувач аргументу го зв'язків забезпечує обчислення загальної кільквадратора або загальної кількості використання кості адитивних команд. всіх семантичних типів, що зберігається у лічильВведення постійного запам'ятовуючого принику кількості типів, або кількості використання строю функції та його зв'язків забезпечує обчисодного з семантичних типів, що зберігається у лення значення функції двох аргументів, що виоперативному запам'ятовуючому пристрої. 1 1 2 значає достовірності: h(PA , S P ) = - PA + S P Введення зсувача аргументу квадратора та 3 9 3 його зв'язків забезпечує зменшення обсягу постійз необхідною точністю (дискретністю) у діапазоні ного запам'ятовуючого пристрою результатів об0..1. Аргументи функції надходять як бітові слова числення квадрату, шляхом зсуву аргументу у та розглядаються як частини адреси, а результат правий бік та передачі на постійний запам'ятовуюобчислення функції, зберігається у відповідних чий пристрій результатів обчислення квадрату комірках постійного запам'ятовуючого пристрою та тільки части старших розрядів. надходить до відповідних бітів регістру ознак реВведення другого елементу Ні та його зв'язків зультату. забезпечує можливість зсуву даних у зсувачі аргуВведення регістру ймовірності адитивних коменту квадратора до тих пір, доки старший розряд манд та його зв'язків забезпечує збереження стане міститиме одиницю. ршої частини адреси для постійного запам'ятовуВведення третього елементу І та його зв'язків ючого пристрою функції, що надходить з виходу забезпечує керування зсувом даних, що зберігапостійного запам'ятовуючого пристрою результатів ються у зсувачі аргументу квадратора, завдяки ділення. керуючим сигналам, що надходять з блока управВведення регістру ймовірності семантичних ління виконуючого модуля та через третій елемент типів та його зв'язків забезпечує збереження моНі з реверсивного лічильника зсуву. лодшої частини адреси для постійного запам'ятоВведення третього елементу Ні та його зв'язвуючого пристрою функцій, що надходить з виходу ків забезпечує передачу на третій елемент І сигпостійного запам'ятовуючого пристрою результатів налу, що обмежує зсув нульових даних у зсувачі ділення. аргументу квадратора. Введення мультиплексора знаменника та його Введення реверсивного лічильника зсуву та зв'язків забезпечує вибір знаменника для обчисйого зв'язків забезпечує підрахування кількості 13 88486 14 нти чисельника надходять на перший вхід додаваm ча даних, а знаменник - на мультиплексор знаменå N2 Ti NA ника. i =1 лення: PA = , SP = , що надходять Введення додавача даних та його зв'язків за2 NS æm ö ç N ÷ m ç å TS ÷ безпечує підрахування суми å N2 на підставі Ti è i =1 ø i= 1 відповідно з лічильнику команд, або демультиплексора та передаються до зсувача знаменника. елементів суми N 2 , що надходять з демультиTi Введення мультиплексора чисельника та його плексора та регістра операнду додавача даних. зв'язків забезпечує вибір чисельників, що надхоВведення регістра проміжних даних та його дять відповідно з лічильнику адитивних команд зв'язків забезпечує, завдяки керуючому сигналу, або регістру проміжних даних та передаються до що надходить з блока управління виконуючого зсувача чисельника. модуля, збереження проміжного значення суми Введення постійного запам'ятовуючого приm строю результату ділення та його зв'язків забезпеå N2 та її передачі на інформаційні входи мульчує ділення двох аргументів, що надходять з зсуTi i= 1 вачів чисельника та знаменника. Кожний з типлексора та регістра операндів додавача даних. аргументів розглядається як частина адреси поВведення регістра операнду додавача даних стійного запам'ятовуючого пристрою, результат та його зв'язків забезпечує, завдяки керуючим сигрезультата ділення, що зберігається з необхідною налам, що надходять з блока управління виконуюточністю надходить до регістрів ймовірностей адичого модуля, онулення початкового значення суми тивних команд та семантичних типів. на початку обчислень, збереження та передачу на Введення зсувача знаменника та його зв'язків вхід додавача проміжного результату, що був обзабезпечує зменшення обсягу постійного запам'ячислений додавачем даних, та зберігався у регісттовуючого пристрою результату ділення завдяки рі проміжних даних. паралельному зсуву даних, що зберігаються у зсуТаким чином, введення зазначених елементів вачах знаменника та чисельника до появи одиниці та обумовлених ними зв'язків забезпечує не тільки у старшому розряді знаменника, для чого другий оперативний семантичний контроль програмного вихід зсувача знаменника з'єднаний з першим забезпечення, але виявлення порушень внаслідок елементом Ні, а відповідна кількість інформаційзбоїв та відмов апаратних і програмних засобів та них розрядів зсувача знаменника з'єднана з друкількісне визначення достовірності програмного гим входом постійного запам'ятовуючого пристрою забезпечення. результата ділення. На Фіг.1 надано функціональну схему приВведення зсувача чисельника та його зв'язків строю. забезпечує зменшення обсягу постійного запам'яПроцесор з семантичним контролем (Фіг.1) товуючого пристрою результату ділення завдяки має блок регістрів загального призначення (1), паралельному зсуву даних, що зберігаються у зсублок тимчасових регістрів (2), блок комунікаційних вачах знаменника та чисельника до появи одиниці регістрів (3), блок регістрів тимчасових семантичу старшому розряді знаменника, для чого відповіних ознак (4), блок регістрів семантичних даних дна кількість інформаційних розрядів зсувача зна(5), арифметико-логічний пристрій (6), додавачменника з'єднана з першим входом постійного віднімач (7), блок черги інструкцій (8), блок управзапам'ятовуючого пристрою результата ділення. ління виконуючого модуля (9), блок управління Введення першого елементу НІ та його зв'язків шиною (10), оперативний запам'ятовуючий призабезпечує формування керуючих сигналів для стрій (11), постійний запам'ятовуючий пристрій зсуву даних у зсувачах чисельника та знаменника. результатів ділення (12), постійний запам'ятовуюВведення другого елементу І та його зв'язків чий пристрій функції (13), постійний запам'ятовуюзабезпечує формування керуючих сигналів для чий пристрій результатів обчислення квадрату зсувачів чисельника та знаменника, на підставі (14), дешифратор команд (15), лічильник команд сигналів керування, що надходять з блока управ(16), лічильник адитивних команд (17), лічильник ління виконуючого модуля та першого елемента типів (18), лічильників кількості типів (19), лічильHI. ник опитування типів (20), зсувач знаменника (22), Введення демультиплексора та його зв'язків зсувач чисельника (23), зсувач аргументу квадразабезпечує надсилання результатів обчислення тора (24), зсувач результату квадратора (25), реквадратів, що надходять з зсувача результату гістр ознак (26), регістр ймовірностей адитивних квадратора та необхідні при обчисленні як елемекоманд (27), регістр ймовірностей семантичних нтів суми, так і знаменника у формулі: типів (28), регістр проміжних даних (29), регістр m операнда додавача даних (30), блок порівняння å N2 Ti (31), мультиплексор адреси (32), мультиплексор i = 1 . Напрямок надсилання визначаSP= типів (33), мультиплексом знаменника (34), муль2 æm ö типлексом чисельника (35), демультиплексор (36), ç N ÷ додавач адреси (37), додавач даних (38), тригер ç å TS ÷ i è= 1 ø (39), перший (40), другий (41), третій (42) та четвертий (43) елементи І, перший (44) та другий (45) ється сигналом керування, що надходить з блока елементи АБО, перший (46), другий (47) та третій управління виконуючого модуля, при чому елеме 15 88486 16 (48) елементи HI, першу (49) та другу (50) шини строю результатів ділення (12), вихід якого з'єднаданих, зовнішню шину (51), перший вхід-вихід блоний з інформаційними входами регістрів ймовірнока управління шиною (10) є вхід-виходом процесості адитивних команд (27) та ймовірності ру, другий вхід-вихід з'єднаний першою шиною семантичних типів (28), виходи яких з'єднані відданих (49) з виходом і першим входом додавача повідно з першим та другим входами постійного адреси (37) та першим входом-виходом блока козапам'ятовуючого пристрою функції (13), вихід мунікаційних регістрів (3), вихід блока управління якого з'єднано з третім інформаційним входом шиною (10) з'єднаний з входом блока черги інструрегістру ознак (26), відповідні виходи другої групи кцій (8), вихід якого з'єднаний з входом блока виходів блока управління виконуючого модуля (9) управління виконуючого модуля (9), а через другу з'єднані з керуючими входами лічильників опитушину даних (50) - з другим вхід-виходом блока вання типів (20), команд (16), типів(18) та кількості комунікаційних регістрів (3), вхід-виходами блоків типів (19), мультиплексорів адреси (31), типів (33) регістрів загального призначення (1) та тимчасота оперативного запам'ятовуючого пристрою (11), вих регістрів (2), а також з виходом результату установчими входами зсувачів аргументу квадраарифметико-логічного пристрою (6) та виходом тора (24) та результату квадратора (25), третім регістру ознак (26), відповідні виходи першої групи входом третього елемента І (42), рахунковим вховиходів блока управління виконуючого модуля (9) дом тригера (39) та другим входом четвертого з'єднані з керуючими входами регістру ознак (26), елемента І (43), онулюючим входом реверсивного арифметико-логічного пристрою (6) та блоків лічильника зсуву (21), відповідні виходи третьої управління шиною (10) і черги інструкцій (8), вхогрупи виходів блока управління виконуючого модами блоків регістрів загального призначення (1) дуля (9) з'єднані з онулюючими входами оператита тимчасових регістрів (2), а також блока комунівного запам'ятовуючого пристрою (11) та лічилькаційних регістрів (3), вихід якого з'єднаний з друників опитування типів (20), команд (16), гим входом додавача адреси (37), перший та друадитивних команд (17), типів (18) та кількості типів гий виходи блока тимчасових регістрів (2) з'єднані (19), вихід лічильника типів (18) з'єднаний з інфовідповідно з першим та другим інформаційними рмаційним входом оперативного запам'ятовуючого входами арифметико-логічного пристрою (6), вихід пристрою (11), вихід лічильника кількості типів (19) ознак якого з'єднаний з першим інформаційним з'єднаний з другим інформаційним входом мульвходом регістру ознак (26), відповідні виходи пертиплексора типів (33), вихід якого з'єднаний з іншої групи виходів блока управління виконуючого формаційним входом зсувача аргументу квадрамодуля (9) з'єднані з входами блока регістрів тимтора (24), вихід якого з'єднаний зі входом часових семантичних ознак (4) і блока регістрів постійного запам'ятовуючого пристрою обчисленсемантичних даних (5), вхід-вихід якого через друня квадрату (14), вихід якого з'єднаний з інформагу шину даних (50) з'єднаний з входом-виходом ційним входом зсувача результату квадратора блока регістрів тимчасових семантичних ознак (4), (25), вихід якого з'єднаний з інформаційним вхоперший та другий виходи якого з'єднані відповідно дом демультиплексора (36), перший вихід якого з першим і другим інформаційними виходами доз'єднаний з першим інформаційним входом мульдавача-віднімача (7) , вихід якого з'єднаний з друтиплексора знаменника (34), вихід якого з'єднаний гою шиною даних (50), перший та другий виходи з інформаційним входом зсувача знаменника (22), блока регістрів тимчасових семантичних ознак (4) вихід якого з'єднано з другим входом постійного та вихід лічильника опитування типів (20) з'єднані запам'ятовуючого пристрою результатів ділення відповідно з першим-третім інформаційними вхо(12), другий вихід - через перший елемент HI (46) дами мультиплексора адреси (31), вихід якого з'єднаний з першим входом другого елемента І з'єднаний з входом адреси оперативного запам'я(41), вихід якого з'єднаний з входами керування товуючого пристрою (11), вихід якого з'єднаний з зсувом зсувачів знаменника (22) та чисельника інформаційним входом лічильника типів (18) та (23), вихід лічильника команд (16) з'єднаний з друпершим інформаційним входом мультиплексора гим інформаційним входом мультиплексора знатипів (33), перший та другий виходи блока регістменника (34), а другий вихід демультиплексора рів тимчасових семантичних ознак (4) з'єднані від(36) з'єднано з першим інформаційним входом повідно з першим та другим входами блока порівдодавача даних (38), вихід якого з'єднано з інфорняння (31), вихід якого з'єднаний з першим входом маційним входом регістра проміжних даних (29), першого елемента І (40), вихід якого з'єднаний з вихід якого з'єднаний з інформаційним входом першим входом елемента АБО (44), вихід якого регістра операнду додавача-даних (30) та другим з'єднаний з другим інформаційним входом регістру інформаційним входом мультиплексора чисельниознак (26), вихід блока черги інструкцій (8) з'єднака (34), вихід регістра операнду додавача даних ний зі входом дешифратора команд (15), перший (30) з'єднаний з другим інформаційним входом вихід якого з'єднаний з керуючим входом додавадодавача даних (38), другий вихід зсувача аргумеча-віднімача (7), другий вихід - з другим входом нту квадратора (24) з'єднаний через другий елепершого елемента АБО (44), третій вихід - з друмент НІ (46) з першим входом третього елементу І гим входом першого елемента І (40) та керуючим (41), вихід якого з'єднаний з входом керування входом лічильника адитивних команд (17), вихід зсувом зсувача аргументу квадратора (24) та доякого з'єднаний з першим інформаційним входом давальним входом реверсивного лічильнику зсуву мультиплексора чисельника (35), вихід якого з'єд(21), перша група виходів якого з'єднана з групою наний з інформаційним входом зсувача чисельнивходів другого елементу АБО (44), вихід якого ка (23), вихід зсувача чисельника (23) з'єднаний з з'єднано з першим входом четвертого елементу І першим входом постійного запам'ятовуючого при(44), вихід якого з'єднаний зі входом керування 17 88486 18 зсувом зсувача результату квадратора (25), другий нові фізичні типи. Так, при додаванні елементів, вихід реверсивного лічильника зсуву (21) з'єднано що відповідають довжині, утворюється елемент, через третій елемент НІ (47) з другим входом трещо відповідає площині, а додавання елементів тього елементу І (41), вихід тригеру (38) з'єднано з „довжини" та „площини" утворить елемент „об'віднімаючим входом реверсивного лічильнику зсуєму". Множення елемента „довжини" на 2 та 3 ву (21), а відповідні виходи четвертої групи виходів утворить відповідно елементи площини та об'єму блока управління виконуючого модуля (9) з'єднані тощо. Будь-які два результати, що мають різні сез керуючими входами демультиплексора (35), мумантики (фізичні розмірності), вважатимуться різльтиплексорів чисельника (34), знаменника (33), ними. Це дозволяє контролювати достовірність регістрів ймовірності адитивних команд (27), ймообчислювального процесу не тільки за збігом кільвірності семантичних типів (28), операнду додавакісних значень (з необхідною точністю), а й за фіча даних (30) і проміжних даних (29), онулюючим зичним типом (збігом семантик). входом регістра операнду додавача даних (30), Існує взаємовідповідність між програмними установчими входами зсувачів знаменника (22) та операціями у виразах, що мають фізичні типізовані чисельника (23). змінні (операторним відображенням) та операціяНа Фіг.2 ілюструється приклад схеми розташуми над елементами семантичного простору (семавання елементів семантичного простору в механінтичним відображенням). Деякі з операторних вічному базисі: 1 - щільність, 2 - маса, 3 - скаляр, 4 дображень мають умови семантичної коректності сила, 5 - енергія, 6 - потужність, 7 - прискорення, 8 (див. таблицю 1, де надано аксіоматику семантич-швидкість, 9 - об'єм, 10 - площа, 11 - довжина, 12 них відображень). У другій колонці наведено типочас. Властивості семантичного простору, розташуве операторне відображення, у третій - відповідне вання елементів якого зображено на Фіг.2, дозвойому семантичне відображення, а в останній ляють виконувати над його елементами такі опеумови семантичної коректності операторного відорації: порівняння, множення на константу, браження. додавання, віднімання. При цьому утворюються Таблиця 1 № 1 2 3 4 3 4 5 Операторне відображення А=В А±В А>В А

ДивитисяДодаткова інформація

Назва патенту англійськоюProcessor with semantic control

Автори англійськоюManzhos Yurii Semenovych, Kharchenko Viacheslav Serhiiovych, Konorev Borys Mykhailovych, Chertkov Heorhii Mykolaiovych

Назва патенту російськоюПроцессор с семантическим контролем

Автори російськоюМанжос Юрий Семенович, Харченко Вячеслав Сергеевич, Конорев Борис Михайлович, Чертков Георгий Николаевич

МПК / Мітки

МПК: G06F 11/00

Мітки: процесор, семантичним, контролем

Код посилання

<a href="https://ua.patents.su/18-88486-procesor-z-semantichnim-kontrolem.html" target="_blank" rel="follow" title="База патентів України">Процесор з семантичним контролем</a>