Формувач імпульсів управління для блокованого тиристора

Номер патенту: 31913

Опубліковано: 15.12.2000

Автори: Остренко Віктор Сергійович, Міщенко Олександр Васильович, Алексєєв Олександр Генадійович, Андрієнко Петро Дмитрович

Текст

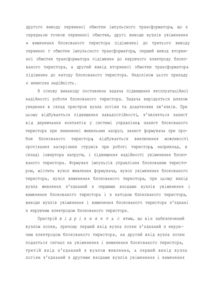

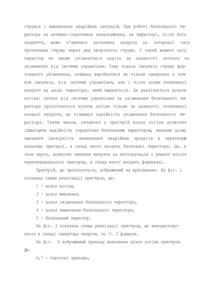

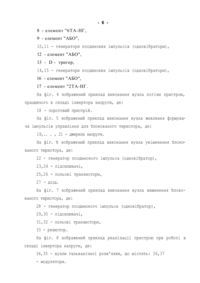

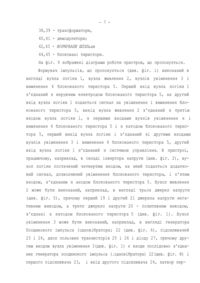

МПЇ^ Н 02 Ml /08 ФОРМУВАЧ ІМПУЛЬСІВ УПРАВЛІННЯ ДЛЯ БЛОКОВАНОГО ТИРИСТОРА Винахід відноситься до галузі силової перетворювальної техніки і може бути використаний у системах управління перетворювальних приладів на блокованих тиристорах, наявність реактивних складових і різноманітні режими роботи навантаження яких вимагають підвищення надійності комутації цих тиристорів. Відомо пристрій (см. "Формирователи импульсов управления двухоперационными тиристорами'УВулатов О. Г, , Жеглов А. В. , Одынь 0. В. , Акияма Я //Электротехника, N1, 1996г. Стр. 44, рис. 5)3 який містить вузол увімкнення блокованого тиристора, вузол вимкнення блокованого тиристора і вузол живлення, причому перший і другий ЕИходи вузла живлення підімкнені відповідно до першого і другого входів вузла увімкнення блокованого тиристора, третій і четвертий виходи вузла живлення підімкнени відповідно ДО першого і другого входа вузла вимкнення блокованого тиристора, виходи вузлів увімкнення і вимкнення блокованого тиристора підімкнені до керуючого електроду блокованого тиристора, а п'ятий вихід вузла живлення підімкнений до катоду блокованого тиристора. Недоліком цього приладу є невисока надійність. Відомо пристрій, вибраний в якості прототипу (див. Схема управления управляющим электродом запираемого тиристора, заявка Японії N87-59548), що містить вузол живлення, вузол увімкнення блокованого тиристора, вузол вимкнення блокованого тиристора і імпульсний трансформатор, причому вихід вузла живлення підімкненийдо входів вузлів увімкнення і вимкнення блокованого тиристора, і до першого виводу первинної обмотки імпульсного трансформатора, перші виводи вузлів увімкнення і вимкнений блокованого тиристора лідзмкиени до другого виводу первинної обмотки імпульсного трансформатора, що є середньою точкою первинної обмотки, другі виводи вузлів увімкнення » вимкнення блокованого тиристора підімкнені до третього виводу первинно г обмотки імпульсного трансформатора, перший вивод вторинної обмотки трансформатора підімкнен до керуючого електроду блокованого тиристора, а другий вивід вторинної обмотки трансформатора підімкнен до катоду блокованого тиристора. Недоліком цього приладу є невисока надійність. В основу винаходу поставлена задача підвищення експлуатаційної надійності роботи блокованого тиристора. Задача вирішується шляхом уведення в склад пристрою вузла логіки та додаткових зв'язків. При цьому відбувається підвищення завадостійкості, з'являється захист від деремчання контактів у системі управління захист блокованого , тиристора при зникненні живильних напруг, захист формувача при пробою блокованого тиристора , відбувається виключення можливості протікання наскрізних струмів при роботі тиристора наприклад, в , складі інвертора напруги, і підвищення надійності увімкнення блокованого тиристора. Формувач імпульсів управління блокованим тиристором, містить вузол живлення формувача, вузол увімкнення блокованого тиристора, вузол вимкнення блокованого тиристора, при цьому вихід вузла живлення з'єднаний з першими входами вузлів увімкнення і вимкнення блокованого тиристора і з катодом блокованого тиристора, виходи вузлів увімкнення і вимкнення блокованого тиристора з'єднані з керуючим електродом блокованого тиристора. Пристрій в і д р і з н я е т ь с ятим, що він забезпечений вузлом лопки, причому перший вхід вузла лопки з'єднаний з керуючим електродом блокованого тиристора, на другий вхід вузла лопки подається сигнал на увімкнення і вимкнення блокованого тиристора, третій вхід з'єднаний з вузлом живлення, а перший вихід вузла логіки з'єднаний з другими входами вузлів увімкнення і вимкнення -зблокованого тиристора, другий вихід вузла логіки править для сигналізації пробитого стану блокованого тиристора. Пристрій, що використовується в інверторі напруги, в і д р і з н я е т ь с я тим, що вузол логіки забезпечений четвертим і п'ятим входами причому , четвертий вхід править для подачи сигналу, що дозволяє увімкнення блокованого тиристора, при повному закритті другого блокованого тиристора, який знаходиться у цій же фазі інвертора і управляється від другого формувача імпульсів управління а п'ятий вхід вузла , логіки з'єднаний з анодом блокованого тиристора. Підвищення завадостійкості досягається тим, що вузол логіки чутливий до зміни сигналу на його вході тільки у малі інтервали часу, що заздалегідь задаються. Початок цих інтервалів синхронизується вузлом логіки по передньому і по задньому фронту сигналу що , надходить від системи управління. Завада, що прийшла на вхід вузла логіки поза цим проміжком часу, не вплине на подальшу роботу формувача. Таким чином, уведення вузла логіки підвищує завадостійкість формувача. Захист від деренчання контактів реалізується уведенням обмеження на мінімальний час знаходження тиристора в увімкненому або вимкнутому стані. При перехідних процесах увімкнення або вимкнення приладу у ньому виділяється значна кількість теплоти що , призводить до локального перегріву напівпровідникової структури . Процес вирівнювання температури займає деякий інтервал часу Якщо . наступний процес увімкнення або вимкнення почнеться до завершення процесу вирівнювання температури напівпровідникової структури, то це може призвести до різкого г і підвищення через декілька таких циклів увімкнення - вимкнення та виходу тиристора з ладу Для . відвертання цього необхідно витримувати мінімальний час знаходження тиристора в увімкненому і вимкнутому стані Якщо в системі уп. равління виникне деренчання контактів або на сигнал управління , блокованим тиристором накладеться завада, то це не призведе до - A збільшення частоти комутації і виходу тиристора з ладу При . увімкненні або вимкненні перетворювального приладу а також при , пропаданні живильних напруг, рівні живильних напруг змінюються від нуля до номінальних, або навпаки. При цьому може відбутися ситуація, коли енергії, запасеної в вузлі живлення, виявиться достатньо для увімкнення блокованого тиристора, але недостатньо для закриття. Знаходження у провідному стані блокованого тиристора на інтервалі часу, коли прилад повинен бути закритий, може притягти за собою виникнення різноманітних аварійних процесів. Вузлом логіки відстежуются рівні живильних напруг, і при зниженні гх нижче заданого рівня, вузлом логіки на вузли увімкнення і вимкнення блокованого тиристора подається сигнал на вимкнення приладу Після вимкнення . тиристора, він підтримується в блокованому стані незалежно від , сигналів, ідо надходять від системи управління, до відновлення рівня живильних напруг. При пробої блокованого тиристора вузлом логіки видається , відповідний сигнал системі управління, і блокуються імпульси, що надходять від неї. Це дозволяє уникнути роботи вузлів увімкнення і вимкнення блокованого тиристора, що генерують потужні імпульси управління, на пробитий тиристор, у якого, після пробою, керуючий електрод закорочений з катодом. Виключення протікання наскрізних струмів при роботі тиристора, що управляється, наприклад, в складі інвертора напруги, забезпечується слідуючим чином. На четвертому вході вузла логіки з'являється сигнал високого рівня тільки тоді , коли інший тиристор, що знаходиться, наприклад, в цій же фазі інвертора, повністю закриється. Сигнал високого рівня є одним з дозволяючих для проходження через вузол логіки сигналу на увімкнення. Тому вузлом логіки буде пропущений сигнал на увімкнення тиристора тільки при повному закритті іншого тиристора, який знаходиться в цій же фазі інвертора, що дозволяє уникнути протікання наскрізних струмів і виникнення аварійних ситуацій. При роботі блокованого тиристора на активно-індуктивне навантаження, на тиристорі, після його закриття, може з'явитися негативна напруга на інтервалі часу протекания струму через дюд зворотного струму. У такий момент часу тиристор не зможе увімкнутися навіть за наявності сигналу на увімкнення від системи управління. Тому подача імпульса струму форсованого увімкнення, повинна вироблятися не тільки синхронно з появою імпульсу, від системи управління, але і після появи позитивної напруги на аноді тиристора, який вмикається. Це реалізується вузлом логіки: сигнал від системи управління на увімкнення блокованого ти ристора пропускається вузлом логіки тільки за наявності позитивної анодної напруги, що підвищує надійність увімкнення блокованого тиристора. Таким чином, уведення у пристрій вузла логіки дозволяє ЇЛдвиїдити надійність управління блокованим тиристором, завдяки цьому зменшити імовірність виникнення аварійних процесів в перетворю вальному пристрої, в склад якого входять блоковані тиристори. Це, в свою чергу, дозволяє знизити витрати на експлуатацію і ремонт всього перетворювального пристрою, в склад якого входять формувачі. Пристрій, що пропонується, зображений на кресленнях. На фіг. 1 показана схема реалізації пристрою, де: 1 - вузол логіки, 2 - вузол живлення, 3 - вузол увімкнення блокованого тиристора, 4 - вузол вимкнення блокованого тиристора, 5 - блокований тиристор. На фіг. 2 показана схема реалізації пристрою, що використовується в складі інвертора напруги, по ЇЇ. 2 формули. На фіг. З зобрчжеиий приклад виконання вузлч логіки пристрою. Де: 6,7 - порогові прилади, - 6 8 - елемент "6ТА-НГ, 9 - елемент "АБО", 10,11 - генератори поодиноких імпульсів (одновібратори), 12 - елемент "АБО", 13 - D - тригер, 14,15 - генератори поодиноких імпульсів (одновібратори), 16 - елемент "АБО", 17 - елемент "2ТА-НГ. На фіг. 4 зображений приклад виконання вузла логіки пристрою, працюючого в складі інвертора напруги, де: 18 - пороговий пристрій. На фіг. 5 зображений приклад виконання вузла живлення формувача імпульсів управління для блокованого тиристора, де: 19,.. . , 21 - джерела напруги. На фіг. б зображений приклад виконання вузла увімкнення блокованого тиристора, де: 22 - генератор поодинокого імпульса (одновібратор), 23,24 - підсилювачі, 25,26 - польові транзистори, 27 - діод. На фіг. 7 зображений приклад виконання вузла вимкнення блокованого тиристора, де: 28 - генератор поодинокого імпульса (одновібратор), 29,30 - підсилювачі, 31,32 - польові транзистори, 33 - резистор. На фіг. 8 зображений приклад реалізації пристрою при роботі в складі інвертора напруги, де: 34,35 - вузли гальванічної розв'язки, що містять: 36,37 - модулятори. - 7 38,39 - трансформатори, 40,41 - демодулятори; 42,43 - ФОРМУВАЛИ ШПЗЛьав 44,45 - блоковані тиристори. На фіг. 9 зображені діаграми роботи пристрою, що пропонується. Формувач імпульсів, що пропонується (див. фіг. і) виконаний в вигляді вузла логіки 1, вузла живлення 2, вузлів увімкнення 3 і вимкнення 4 блокованого тиристора 5. Перший вхід вузла логіки 1 з'єднаний з керуючим електродом блокованого тиристора 5, на другий вхід вузла логіки 1 подається сигнал на увімкнення і вимкнення блокованого тиристора 5, вихід вузла живлення 2 з'єднаний з третім входом вузла логіки 1, з першими входами вузлів увімкнення я і вимкнення 4 блокованого тиристора 5 і з катодом блокованого тиристора 5, перший вихід вузла логіки і з'єднаний зі другими входами вузлів увімкнення 3 і вимкнення 4 блокованого тиристора 5, другий вхід вузла логіки 1 з'єднаний з системою управління. В пристрої, працюючому, наприклад, в складі інвертора напруги (див. фіг. 2), вузол логіки постачений четвертим входом, на який подається додатковий сигнал, дозволяючий увімкнення блокованого тиристора, і п'ятим входом, з'єднаним з анодом блокованого тиристора 5. Вузол живлення 2 може бути виконаний, наприклад, в вигляді трьох джерел напруги (див. фіг. 5), причому перший 19 і другий 21 джерела напруги негативним виводом, а третє джерело напруги 20 - позитивним виводом, з'єднані з катодом блокованого тиристора 5 (див. фіг. 1). Вузол увімкнення 3 може бути виконаний, наприклад, в вигляді генератора Поодинокого імпульса (одновібратора; 22 (див. фіг. 6), підсилювачей 23 і 24, двох польових транзисторів 25 і 26 і діоду 27, причому другим входом вузла увімкнення 3(див. фіг. 1) є входи послідовно з'єднаних генератора поодинокого імпульса (.одновібратора) 22(див. фіг. б) і першого підсилювача 23, і вхід другого підсилювача 24, затвор пер -8шого транзистори 25 приєднаний до виходу першого підсилювача 23, затвор другого транзистора 26 приєднаний до виходу другого підсилювача 24, витік другого транзистора 26 приєднаний до аноду діода 27, витік першого транзистора 25 і катод діоду 27 є виходом вузла увімкнення 3 (див. фіг. 1), стік першого транзистора 25 (див. фіг. 6) приєднаний до позтивного виводу першого джерела напруги 19 (див. фіг. 5), стік другого транзистора 26 (див. фіг. 6) приєднаний до позитивного виводу другого дж>рела напруги 21 (див. фіг. 5). Вузол вимкнення 4 (див. фіг. 1) може бути виконаний, наприклад, в вигляді генератора поодинокого імпульоа (одновібратора) 28 (див. фіг. 7), підсилювачеи 29 і ЗО, двох польових транзисторів 31 і 32 і резистора 33, причому другим входом вузла вимкнення 4 (див. фіг. 1) є входи послідовно з'єднаних генератора поодинокого імпульса (одновібратора} 28 (див. фіг. 7) і першого підсилювача 29, і вхід другого підсилювача ЗО, затвор першого транзистора 31 приєднаний до виходу першого підсилювача 29, затвор другого транзистора 32 приєднаний до виходу другого підсилювача ЗО, стік другого транзистора 32 приєднаний до першого виводу резистора 33, стік першого транзистора 31 і другий вивід резистора 33 є виходом вузла вимкнення 4 (див. фіг. 1), витік першого транзистора 31 (див. фіг. 7) і витік другого транзистора 32 приєднані до негативного виводу третього джерела напруги 20 (див. фіг. 5). Вузол логіки 3 (див. фіг. 1) пристрою може бути виконаний, наприклад, у вигляді порогових приладів 6,7 (див. фіг. 3), елементу "6ТА-НІ" 8, елементу "АБО" 9, генераторів поодиноких імпульсів (одновібраторів) 10,11, елементу "АБО" 12, D - тригера 13, генераторів поодиноких імпульсів (одновібраторів) 14 і 1Ь, елементу "АБО" 16, елементу "2ТА-НІ" 17, причому вхід порогового пристрою б є першим входом вузла логіки 1 (див. фіг. 1), другий вхід елементу "GTA-HI" 8 (див. фіг. 3) є другим входом вузла логіки і (див. фіг. 1), вхід порогового пристрою 7 (див. фіг. 3) є третім входом -9вузла логіки 1 (див. фіг. 1), виходи порогових приладів б і 7 (див. фіг. 3) приєднані відповідно до першого і третього входів елементу "6ТА-НІ" 8. Вихід елементу "6ТА-НІ" 8 приєднаний послідовно з одновібратором 10 і першим входом елементу "АБО" 12, до другого входу елементу "6ТА-НІ" 8 приєднані послідовно одновібратор 11 і другий вхід елементу "АБО" 12, другий вхід елементу "6ТА-НІ" 8 приєднаний до D-входу D-тригера ІЗ, вихід елементу "АБО" 12 з'єднаний з О БХОДОМ D-тригера ІЗ, інверсний вихід D-тригера ІЗ з'єднаний послідовно з одновібратором 14 і першим входом елементу "АБО" 16, а також зі другим входом елементу "АБО" 16, вихід елементу "АБО" 16 з'єднаний з першим входом елементу "2ТА-Ш" 17, інверсний вихід Dтригера ІЗ приєднаний послідовно з одновібратором 15 і другим входом елементу "2ТА-НІ" 17, а вихід елементу "2ТА-НІ" 17 є першим виходом вузла логіки 1 (див. фіг. 1). Перший і другій входи елементу "6ТА-НІ" 8 (див. фіг. 3) з'єднані відповідно с першим і другим входами елементу "АБО" 9, вихід елементу "АБО" 9 є другим виходом вузла логіки 1 (див. фіг. 1), і з'єднаний з четвертим, п'ятим і шостим входами елементу "6ТА-НІ" 8 (див. фіг. 3). В вузлі логіки пристрою, працюючого в складі інвертора напруги (див. фіг. 4), вихід елементу "АБО" 9 з'єднаний з четвертим входом елементу "6ТА-Ш" 8, п'ятий вхід елементу "6ТА-НІ" 8 є четвертим входом вузла логіки 1 (див. фіг. 2), вхід введеного порогового пристрою 18 (див. фіг. 4) є п'ятим входом вузла логіки 1 (див.фіг. 1), вихід порогового пристрою 18 (див. фіг. 4) з'єднаний з шостим входом елементу "6ТА-НГ1 8. Пристрій працює, слідуючим чином. Сигнал на увімкнення і вимкнення блокованого тиристора 5 (див. фіг. 1) надходить на другий вхід вузла лопки 1, причому увімкнення блокованого тиристора виробляється по фронту цього сигналу у момент часу 11 (див. фіг. 9), а вимкнення - по спаду у момент часу 15. Блокований тиристор 5 (див. фіг. 1)знаходиться у провідному стані на інтервалі часу від tl - 10 до t5 (див. фіг. 9), доки керуючий сигнал має високий рівень. Така логіка управління направлена на підвищення надійності перетворювального пристрою: в випадку обривання л і н і ї зв'язку з системою управління, формувачем буде виданий імпульс струму на блокування, а після цього на керуючий електрод блокованого тиристора 5 буде подана негативна напруга. Сигнал на увімкнення вузлом логіки 1 (див. фіг. 1) пропускається без затримки на вузли увімкнення 3 і вимкнення 4 в тому випадку, якшр дотримуються такі три умови: тиристор 5 не пробитий, рівні живильних напруг, що подаються вузлом живлення 2, знаходяться в заданих метх, після початку попереднього процесу увімкнення минуло не менше заздалегідь заданого проміжку часу (t5-t8) (див. фіг. 9). Для пристрою, працюючого в складі інвертора напруги (див. фіг. 2), додатково існують ще дві умови: тиристор, який знаходиться в цієї ж фазі інвертора, повинен бути замкнутий, на аноді блокованого тиристора 5 повинна бути позитивна напруга. При невиконанні хоча б одні є г з цих умов сигнал на увімкнення затримується до виконання всіх цих умов. При видаванні вузлом логіки 1 (див. фіг. 1) сигналу на увімкнення, по передньому фронту сигналу одновібратором 22 ^див. фіг. 6) генерується, а після цього посилюється підсилювачем 23 відмикаючий імпульс, який займав інтервал часу від tl до t3 (див. фіг. 9), для транзистора 25 (див. фіг. 6). Імпульс струму форсованого увімкнення тиристора 5 (див. фіг. 1), необхідно г швидкості наростання, амплітуди і тривалості, протікає що такому контуру: позитивний вивід джерела живлення 19(див. фіг. 5), стік транзистора 25 (див. фіг. б), витік транзистора 25, керуючий електрод блокованого тиристора 5 (див. фіг. 1), катод блокованого тиристора 53 негативний вивід джерела живлення 19 (див. фіг. 5). Водночас з цим, сигнал на увімкнення від вузла логіки 1 посилюється підсилювачем ?Л (див. фіг. 6). Посиленим сигналом відкривається транзистор 26 на час від tl до t5 (див. фіг. 9). Крізь керуючий електрод блокованого ти -11 ристора 5 (див. фіг. 1) створюється постійний струм управління необхідної величини. Він протікає по такому контуру: позитивнй вивід джерела живлення 21 (див. фіг. 5), стік транзистора 26 (див. фіг. 6), витік транзистора 26, діод 27, керуючий електрод блокованого тиристора 5 (див. фіг. 1), катод блокованого тиристора5, негативний вивід джерела живлення 21 (див. фіг. 5). Сигнал на вимкнення вузлом логіки 1 (див. фіг. 1) пропускається без затримки на вузли увімкнення 3 і вимкнення 4 в тому випадку, якщо після початку попереднього процесу вимкнення минуло не менше заздалегідь заданого проміжку часу , рівного (tl-t4) (див. фіг. 9). При невиконанні цієї умови, сигнал на вимкнення затримується до тих пір, доки воно не буде виконане. При видаванні вузлом логіки 1 (див. фіг. і) сигналу на вимкнення, у момент часу t4 (див. фіг. 9) посиленим сигналом замикається транзистор 26 (див. фіг. б). По спаду імпульса управління, одновібратором 28 генерується, а після цього посилюється підсилювачем 29 блокуючий імпульс, який тривається від t5 до t7 (див. фіг. 9), для транзистора 31 (див. фіг. 7). Імпульс струму форсованого вимкнення тиристора 5 (див. фіг. 1), необхідної швидкості наростання, амплітуди і тривалості, протікає по контуру: позитивний вивід джерела живлення 20 (див. фіг. 5), катод блокованого тиристора 5 (див. фіг. 1), керуючий електрод блокованого тиристора 5, стік транзистора 31 (див. фіг. 7), вит і к транзистора 31, негативний вив ід джерела живлення 19 (див. фіг. 7). Водночас з цим, сигнал на увімкнення від вузла логіки 1 (див. фіг. 1) посилюється підсилювачем ЗО (див. фіг. 7). Посиленим сигналом відкривається транзистор 32. До керуючого електроду блокованого тиристора 5 (див. фіг. 1) прикладається негативна напруга до наступного моменту увімкнення тиристора. При цьому через керуючий перехід блокованого тиристора 5 протікчє невеликий зворотний струм. Він протікає по контуру: позитивний вивід джерела живлення 20 (див. фіг. 5), катод блокованого тиристора 5 (див. фіг. 1) , керуючий - 12 електрод блокованого тиристора 5, резистор 33 (див. фіг. 7), стік транзистора 32, витік транзистора 32, негативний вивід джерела живлення 20 (див. фіг. 5). Відзнака роботи формувача імпульсів управління, працюючого в складі інвертора напруги (див. фіг. 2), полягає в тому, що ще один сигнал, що дозволяє увімкнення блокованого тиристора, подається на четвертий вхід вузла логіки тільки тоді, коли, наприклад, тиристор 44 (див. фіг. 8), який знаходиться в цієї ж фазі інвертора, повністю закриється. Потенціал катода цього тиристора стане вище потенціалу керуючого електрода. Крізь гальваничну розв'язку 35, минувши моду лятор 37, трансформатор 39 і демодулятор 41, іде сигнал високого рівня. Сигнал високого рівня є одним з сигналів, що дозволяють про ходження крізь вузол логіки формувача 43 сигналу на увімкнення бло кованого тиристора 45. Тому формувачем 43 буде увімкнений тиристор 45 тільки при повному закритті тиристора 44, який знаходиться в цій фазі інвертора, що дозволяє уникнути протікання наскрізних струмів. Аналогічно, формувачем 42 буде увімкнено тиристор 44 тільки тоді, коли тиристор 45 повністю закриється, і сигнал про це крізь галь ванічну розв'язку 34, минувши модулятор 36, трансформатор 38 і де модулятор 40, мине на вузол логіки формувача 34. Ще одна відзнака роботи цього пристрою (див. фіг. 2) полягає в тому, що сигнал на увімкнення блокованого тиристора 5 буде пропущений вузлом логіки тільки за наявності на аноді блокованого тиристора 5, з'єднаного з п'ятим входом вузла логіки, позитивної напруги. Вузол логіки пристрою, що пропонується, працює, слідуючим чином. На другий вхід елементу "6ТА-НІ" 8 (див. фіг. 3), інформаційний D-вхід D-тригера ІЗ і вхід одновібратора 11 подається сигнал на увімкнення блокованого тиристора 5 (див. фіг. 1). На виході порогового пристрою 6 (див. фіг. 3) з'являється логічна одиниця в тому випадку , якщо керуючий електрод блокованого тиристора 5 (див. фіг. 1) має - 13 негативний потенціал. Якщо тиристор 5 не пробитий, то на інтервалі вимкнутого стану t5-t9 (див. фіг. yj на вхід порогового пристрою б (див. фіг. 3) подається негативна напруга і на перший вхід елементу "бТА-Ш" 8 подається логічна одиниця, що є однім з сигналів, що дозволяють увімкнення блокованого тиристора 5 (див. фіг. 1). Якщо тиристор 5 пробитий, то на інтервалі вимкнутого стану його керуючий перехід має нізький імпеданс, напруга на вході порогового пристрою 6 (див. фіг. 3) дорівнює нулю, і на перший вхід елементу "бТА-Ш" 8 подається логічний нуль, що забороняє наступну подачу імпульсів увімкнення. На виході порогового пристрою 7 з'являється логічна одиниця в тому випадку, якщо рівні живильних напруг знаходяться в заданих межах, і логічний нуль в противному випадку. Коли на другому вході елементу "6ТА-НГ1 8, і на першому вході елементу "АБО" 9 є сигнал, відповідний непровідному стану тиристора 5 (див. фіг. 1) (логічний нуль), а на виході порогового пристрою б (див. фіг. 3) і другому вході елементу "АБО" 9 є також логічний нуль, що протягом цього періоду означає пробій блокованого тиристора то на виході , елементу "АБО" 9, з'єднаного з четвертим, п'ятим і шостим входами елементу "6ТА-НГ 1 8 і що є другим виходом вузла логіки і (.див. фіг. 1), з'являється логічний нуль, який блокує проходження сигналу на увімкнення блокованого тиристора 5. Таким чином відбувається діагностика пробитого стану блокування , сигналів на увімкнення і сигналізація про пробій блокованого тиристора 5. За наявності всіх дозволяючих сигналів на входах елементу "6ТА-Ш" 8 (див. фіг. 3), з його виходу знімається про інвертований сигнал (див. фіг. 9). Одновібраторами 10 і 11 (див. фіг. 3), при появі на їхніх входах негативнного перепаду, генеруються поодинокі імпульси позитивної полярності заданої тривалості. Імпульс тривалістю від tl до tg (див. фіг. 9) генерується одновібратором 10 (див. фіг. 3) при проходженні крізь елемент "6ТА-НІ" 8 сигналу на увімкнення блокова - 14 ного тиристора 5 (див. фіг. 1) . Імпульс тривалістю від t5 до t6 (див. фіг. 9) генерується одновібратором 11 (див. фіг. 4) при надходженні від системи управління сигналу на вимкнення блокованого тиристора 5 (див. фіг. 1). Елементом "АБО" 12 (див. фіг. 3) ці імпульси об'єднуються і подаються на тактовий С-вхід D-тригера ІЗ. По позитивному рівню цих сигналів данні з інформаційного D-входу D-тригера, з'єднаного з третім входом елементу "6ТА-НІ" 8, подаються на інверсний вихід D-тригера ІЗ. Одновібратором 14, при появі на його вході позитивного перепаду напруги, генерується поодинокий імпульс позитивної полярності тривалістю від to до 18 (див. фіг. 9), а одновібратором 15 (див. фіг. 3), при появі на його вході негативного перепаду напруги, генерується імпульс негативної полярності тривалістю від tl до t4 (див. фіг. 9). Тривалість імпульсів, що генеруються одновіОраторами 14 і 15, визначає мінімальний час знаходження блокованого тиристора 5 (див. фіг. 1) в непровідному і провідному стані. Так, якщо сигнал на увімкнення блокованого тиристора 5 з'явився на інверсному виході D-тригера ІЗ (див.фіг.3) раніше, ніж закінчився імпульс, що генерується одновібратором 14, він не мине на вихід елементу "АБО" 16 до закінчення цього імпульса. Аналогічно, якщо сигнал на вимкнення блокованого тиристора 5 (див. фіг. 1) з'явився на інверсному виході D-тригера ІЗ (див. фіг. 3) раніше, н і ж закінчився імпульс, що генерується одновібратором 15, він не мине на вихід елементу "2ТА-Ш" 17 до закінчення цього імпульс а. Відзнака роботи вузла логіки пристрою 35 (див. фіг. 8), \ю входить в склад інвертора напруги, полягає у тому, що додаються дьа сигнала, що дозволяють проходження керуючого сигнала крізь вузол логіки. На п'ятому вході елементу "6ТА-НІ" 8 (див. фіг. 4) вузла логіки пристрою 35 (див. фіг. 8), працюючого в складі інвертора напруги, з'являється логічна одиниця, при закритті іншого тиристора - 15 44, який знаходиться в цієї же фазі інвертора. Ця логічна одиниця дозволяє проходження сигналу на увімкнення блокованого тиристора 45. На виході порогового пристрою 18 (див. фіг. 4) з' являється логічна одиниця в тому випадку, якщо на його вхід, з яким з'єднаний анод блокованого тиристора 5 (див. фіг. 2), подається позитивна нап руга. Ця логічна одиниця з що подається на шостий вхід елементу "6ТА-НІ" 8 (див. фіг. 4), є також однім з дозволяючих сигналів на увімкнення блокованого тиристора 5 (див. фіг. 2). Таким чином, ПІСЛЯ вступу вузла логіки в склад формувача імпульсів управління для блокованого тиристора відбувається підвищення завадостійкості формувача, з'являється захист від деренчання контактів у системі управління, захист при зниканні живильної напруги, захист формувача при пробої блокованого тиристора; при роботі тиристора, наприклад, в складі інвертора напруги, відбувається виключення можливості надійності протікання увімкнення функцій призводить до наскрізних блокованого струмів і підвищення тиристора Реалізація . підвищення надійності роботи імпульсів управління для блокованого тиристора. даних формувача -/6 Формувач імпульсів управління для блокованого тиристора би хід 2. Фіг і би хід І 6л ід 5 бил ід 1 ~Е~ж\дЦ блід S fr (Pi і 2 АБТОрИ: П. Д. Андріенко О. В. МЩЄНКО В. С. Остренко О. Г. Алексеев •Іормувач імпульсів управління для блокованого тиристора 12 S , 6х,дз. 10 ґ І І\ с /з D M I7 /5 9 Фіг З І2 6хід 6 бхіді Ik 10 ha tf / D 7 6хід5 13 бых. ід 2. 9 m Ф/г Автори: IL Д. Андріенко О. В. Мі щенко В. С. Остренко О. Г. Алексеев Формувач імпульсів управління для блокованого тиристора Q о 19 Ю

ДивитисяДодаткова інформація

Назва патенту англійськоюControl pulse former for locked thyristor

Автори англійськоюAndriienko Petro Dmytrovych, Mischenko Oleksandr Vasyliovych, Ostrenko Viktor Serhiiovych, Aleksieiev Oleksandr Hennadiovych

Назва патенту російськоюФормирователь импульсов управления для блокированного тиристора

Автори російськоюАндриенко Петр Дмитриевич, Мищенко Александр Васильевич, Остренко Виктор Сергеевич, Алексеев Александр Геннадьевич

МПК / Мітки

МПК: H02M 1/08

Мітки: імпульсів, блокованого, формувач, управління, тиристора

Код посилання

<a href="https://ua.patents.su/20-31913-formuvach-impulsiv-upravlinnya-dlya-blokovanogo-tiristora.html" target="_blank" rel="follow" title="База патентів України">Формувач імпульсів управління для блокованого тиристора</a>

Попередній патент: Препаратдля боротьби з хворобами плодових культур

Наступний патент: Пристрій для очищення стічних вод

Випадковий патент: Борона роторна навісна