Пристрій для спряження двох магістралей

Номер патенту: 324

Опубліковано: 30.04.1993

Автори: Коваль Микола Олексійович, Сердюк Юрій Авксентійович

Текст

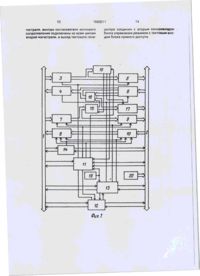

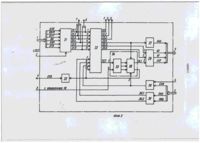

Изобретение относится к вычислительной технике и обеспечивает возможность подключения к вычислительному комплексу с МПИ периферийных устройств, использу ющих системный интерфейс ОШ и возможность работы этих устройств в программном режиме, в режиме прерывания, согласно четырехуровневой системе прерываний МПИ, а также в режиме прямого доступа к памяти, причем работающие в этом режиме периферийные устройства на ОШ имеют доступ ко всему 22-разрядному адресному пространству МПИ. Целью изобретения является расширение области применения. Устройство содержит первые и вторые приемники и передатчики адреса данных и блоки управления режимом захвата первой магистрали, блок прямого доступа, блок отработки прерывания, регистр расширения адреса, селектор адреса, буфер данных, сумматор адреса, генератор синхросигналов и согласователь волнового сопротивления. 24 ил. 1Л с Иэобретение относится к вычислительной технике и предназначено для обеспечения использования в составе вычислительных комплексов с магистральным параллельным интерфейсом (МПИ) периферийных устройств, использующих интерфейс "общая шина" (ОШ). Целью изобретения является обеспечение подключения к вычислительному комплексу с МПИ любых периферийных устройств, использующих интерфейс ОШ, с возможностью доступа периферийных устройств на ОШ, работающих в режиме прямого доступа к памяти, ко всему 22-разрядному адресному пространству МПИ. В качестве периферийных устройств могут использоваться устройства расширения и согласования с другими интерфейсами. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок управления режимом; на фиг. 3 - узел управления обменом блока управления режимом; на фиг. 4 -формирователь временных интервалов и управляющих сигналов блока управления режимом; на фиг. 5 - временные диаграммы операции записи в режиме "Задатчик на МПИ"; на фиг. 6 - временные диаграммы операции чтения в режиме "Задатчик на МПИ"; на фиг. 7 - временные диаграммы операции записи регистра расширения адреса; на фиг. 8-временные диаграммы операции чтения регистра расширения адреса; на фиг. 9 - блок захвата первой магистрали; на фиг. 10 - узел арбитража передачи управления; на фиг. 11 -триггер режима работы; на фиг- 12 - временные диаграммы операции.по захвату МПИ устройством на ОШ; на фиг. 13 - блок прямого доступа; на фиг. 14 о О 1660011 узел запуска блока прямого доступа; на фиг. Блок 13 содержит (фиг. 13): приемники 15 - цепочка триггероа формирователя вре39 секции управления передачей данных менных интервалов и управляющих сигнаОШ, передатчик 40 сигнала "Синхронизалов блока прямого доступа; на фиг. 16 ция исполнителя", узел 41 запуска, формикомбинационный узел формирователя вре- 5 роеатель 42 временных интервалов и менных интервалов и управляющих сигнауправляющих сигналов, который состоит из лов блока прямого доступа; на фиг. 17 цепочки 43 триггеров и узла 44 комбинацивременные диаграммы операции записи в онного, приемник 45 сигнала "Ответ устройрежиме "Задатчик нз ОШ"; на фиг. 18 ства", передатчики 46 шины обмена временные диаграммы операции чтения в 10 информации МПИ. режиме "Задатчик на ОШ"; на фиг. 19 адресные зоны ОШ и МПИ; на фиг. 20 Блок 14 отработки прерываний содералгоритм преобразования адреса ОШ в 22жит (фиг. 21): передатчики 47 сигналов "Заразрядный адрес МПИ; на фиг 21 - блок прос на прерывание", приемники 48 отработки прерывания; на фиг. 22 -узел пре- 15 сигналов "Запрос на прерывание", приемобразования запросов передачи ОШ в заник 49 и передатчик 50 сигнала "Разрешепросы прерывания МПИ; на фиг. 23 - узел ние прерывания", приемник 51 сигнала контроля обработки вектора прерывания; "Чтение данных", передатчик 52 сигнала' на фиг. 24 - временные диаграммы опера"Ответ устройства", узел 53 преобразования ции отработки прерывания. 20 запросов передачи ОШ в запросы прерывания МПИ, узел 54 арбитража приоритета прерывания, узел 55 контроля обработки Устройство содержит следующие функвектора прерывания, приемники 56 сигнациональные узлы для связи первой магистлов "Запрос передачи", передатчики 57 сиграли 1 (магистрального параллельного интерфейса) и второй магистрали 2 (интер- 25 налов "Разрешение передачи", приемники 58 секции арбитража приоритетов ОШ, пефейса общая шина, фиг. 1); первый приемредатчик 59 сигнала "Синхронизация исполник 3 адреса, первый передатчик 4 адреса, нителя". вторые передатчик 5 и приемник 8 адреса, первые приемник 7 и передатчик 8 данных, Генератор 19, осуществляющий синхровторые передатчик 9 и приемник 10 данных, 30 низацию блоков 11 и 13,выполнен на быстблок 11 управления режимом, блок 12 захвародействующей интегральной микросхеме та первой магистрали, блок 13 прямого до(например, микросхема К531ЛАЗ) и стабиступа, блок 14 отработки прерывания, лизирован кварцевым резонатором. регистр 15 расширения адреса, селектор 16 Генератор 19 имеет рабочую частоту 20 адреса, буфер 17 данных, сумматор 18 адре- 35 МГц, определяющую наиболее часто требуса, тактовый генератор 19, согласоеэтель 20 емую обоими интерфейсами дискретность волнового сопротивления. временных интервалов при обмене сигналаблок 11 содержит (фиг. 2): приемники ми по интерфейсам, равную 50 не. 21 шины управления обменом МПИ, пеСогласователь 20 волнового сопротивредатчик 22 сигнала "Ответ устройства", 40 ления ОШ представляет собой реэисторные узел 23 управления обменом, формироделители напряжения. ватель 24 временных интервалов и управВ режиме "Задатчик на МПИ" обмен ляющих сигналов, который состоит из информацией с регистрами периферийного цепочки 25 триггеров и узла 26 комбинаустройства на ОШ происходит через приемционного, передатчик 27 сигнала "Заняник и передатчик адреса 3. 5, приемники и то", передатчики 23 секции управления передатчики данных 7 - 1 0 под управлением передачей данных ОШ, приемник 29 сигблока 11. нала "Синхронизация исполнителя", приПри работе устройства в этом режиме емники 30 секции арбитража возможны следующие ситуации: приоритетов ОШ. 1) адресуется периферийное устройство 50 Блок 12 содержит (фиг. 9): приемники 31 наОШ; секции арбитража приоритетов ОШ. пере2) адресуется периферийное устройство датчиг 32 сигнала "Разрешение прямого дона МПИ; ступа", передатчики 33 секции управления 3) адресуется регистр 15 расширения состоянием систем ОШ, узел 34 арбитража адреса; 55 передачи управления, триггер 35 режима, 4) тайм-аут. передатчики 36 шины передачи управления Работа блока 11 разрешается при сброМПИ, приемник 37 сигнала "Разрешениезашенном триггере 35 режима работы. Состохвата магистрали", приемники 38 вспомогаяние блока 11 определяется сигналами МПИ тельной шины МПИ. "ВУ". "ПЗП". "ОБМ", "ДЧТ", "ДЗП" и "ОТВ" 1660011 принятыми приемником 21, а также сигналами ОШ "СХИ", "ЗАН" и "ПВБ", принятыми npneMHHKjMH 29 и 30. Блок 11 начинает работу по сигналам шины управления обменом МПИ при отсут- 5 ствии на ОШ сигналов "ЗАН" и "ПВБ". После приема сигнала "ОБМис МПИ приемниками 21 узел 23 управления обмена вырабатывает сигнал, разрешающий стробирование адреса в приемнике 3 и выдачу ею через 10 передатчик 5, кроме того, в узле 23 блока 11 фиксируется признак операции и признак адресации внешнего устройства, принятые приемником 21. Далее блок 11 ожидает появления на МПИ сигнала "ДЧТ" или "ДЗП". 15 В случае выполнения задатчиком на МПИ операции записи (фиг. 5), приняв сигнал "ДЗП", узел 23 сигналом на выходе разрешает прием данных в приемнике 7 и выдачу их через передатчик 9, устанавлива- 20 ет на ОШ сигнал "ЗАН" через передатчик 27, разрешает выдачу на ОШ кода операции через передатчик 28, а также разрешает работу формирователя 24. Формирователь 24 с минимальной за- 25 держкой, требуемой интерфейсом ОШ (150 не), формирует сигнал "СХЗ" через передатчик 28. Если устройство на ОШ опознало обращение и установило сигнал "СХИ". то блок 30 11 снимает сигнал "СХЗ" с ОШ, а затем через передатчик 22 устанавливает сигнал "ОТВ" на МПИ через минимальное время (75 не), согласно протоколу ОШ. После завершения операции задатчи- 35 ком на МПИ (снятии сигналов управления обменом "ОБМ" и "ДЗП") блок 11 снимает сигнал "ЗАН", освобождая ОШ. и сигнал "ОТВ", освобождая МПИ. При операции чтения (фиг. А) блок 11, 40 приняв сигнал "ДЧТ", устанавливает сигнал "ЗАН" через передатчик 27, разрешает выдачу на ОШ адреса через передатчики 5, кода операции через передатчики 28, а также разрешает работу 45 формирователя 24. Формирователь 24 с задержкой, требуемой интерфейсом ОШ (150 не), формирует сигнал "СХЗ через передатчик 28. Если устройство на ОШ опознало обра- 50 щение и установило данные для чтения и сигнал "СХИ", то блок 11с минимальной задержкой (75 не), требуемой протоколом ОШ, стробирует данные, принятые через приемник 10, с ОШ в передатчике 8 и разре- gg шает их выдачу на МПИ, снимает сигнал "СХЗ" с ОШ, а затем через передатчик 22 устанавливает сигнал "ОТВ" на МПИ. Через минимальное время (75 не), согласно прото колу ОШ, блок 11 разрешает снятие с ОШ адреса и управления. После завершения операции задатчиком на МПИ (снятия сигналов управления обменом "ОЬМ" и "ДЧТ") блок 11 снимает сигнал "ЗАН", освобождая ОШ, разрешает снятие данных сигнала, освобождая МПИ. Если адресуется не устройство на ОШ, а устройство на МПИ (блок 11 не получил сигнал "СХИ", а принял сигнал "ОТВ") или произошел тайм-аут на МПИ (процессор не получил сигнал "ОТВ"), то после снятия задатчиком на МПИ сигналов управления обменом "ОБМ" и "ДЧТ" или "ДЗП" блок 11 производит завершение операции согласно протоколу ОШ, снимая сигналы "СХЗ", "ЗАН", и управления "У0" и "У1", разрешая снятие адреса и данных (при операции записи). Если адресуется регистр 15 расширения адреса, то селектор 16 адреса опознает это обращение, а также дешифрирует тип операции. При операции записи (фиг. 7) по первому выходу селектора 16 данные с выходов приемника 7 стробируются в регистре 15. а по третьему выходу селектора 16 на втором входе приемника 29 появляется сигнал, эквивалентный сигналу "СХИ", далее завершение работы выполняется аналогично операции записи регистра устройства на ОШ. При операции (фиг. 8) чтения по второму выходу селектора 16 разрешается выдача содержимого регистра 15 через буфер 17 на подшину данных ОШ, а по третьему выходу селектора 16 на втором входе приемника 29 появляется сигнал, эквивалентный сигналу "СХИ". Далее завершение работы выполняется аналогично операции чтения регистра устройства на ОШ. -Операция МПИ "Чтение с модификацией" разбивается блоком 11 на две операции - операцию чтения и операцию записи, выполняемые согласно описанному алгоритму за один захват шины (сигнал "ЗАН" во время всей операции остается установленным). Работа устройства в режиме "Задатчик наОШ". Для перехода в режим "Задатчик на ОШ" периферийное устройство на ОШ должно получить управление магистралью МПИ. В исходном состоянии триггер 35 режима сброшен, а узел 34 арбитража передачи управления блока 12 захвата МПИ разрешает трансляцию сигнала "РЗМ" с входа приемника 37 на выход передатчика 36. Работа блока 12 захвата МПИ по передаче управления (фиг. 12) начинается с уста 1660011 новки на ОШ сигнала "ЗПД1 т —£ — 5 ли? 11 -*: ЗАН $ 1. L4 * • • і; 4 23.2 23.3 23Л 23.5 23.6 1 23.7 1 4 90 ^ 0 г Э К —р/ > > Э —> CD СП О о к 4 29 генератяра 19 г 30.1 NT— —і 30 _# „ /755 • Фиг. 2 1660011 23 29 I Л21.6 С 21.1 C2U-5 с 21.2-ї 23.S. 'M2S.2 tj с 30.2 сЗО.1 8 С21.3 4С21Л с 24.2 ю 27 ШиаЗ.5 1Л с 19 с W на 28 О—і с 29 & нй22, 23 ФигЛ 1660011 "ITS/"прину Прі/нимае/ідіе Впише >75нс т X запись слова 28 150нс 28 29 23.1 23.2 v ' Ьм Фиг. 5 х: 1660011 ftr_ 22 /7 аи л ml Фиг.$ 17 принимаемые данные У(С * 211 2U 22 >25нс запись Sadma х запись слова фиг. 7 * 1660011 га 200 нс ••25K 21.1 22 «л ?25HC »* /77 V X X 7 28 777 s Фиг.в /755 Ї.1 31.1 31 эй.г Jf.Z 35 зи J/.J зь СЯ.2 35.1 Л JW JS.Z 37 32 г АСП 38.1 33 за U. 38.3 * Фи&.9 38 tin і /и; /и =у 1660011 наЗВ наЗВ нйЗІ . C21.2 5 на 36 Фиг. 10 35 ! 6 р Фиг, 1І 1660011 зд 37 36 46 5 -у WVCV 31.1 32 / \ У 31.231.3. 39.1 3S.1 оте ІЗП 43.І MJ WT ш. tf.5. из і У/ газ 42» Фаг. ІЗ ш язв 1660011 с 45 1 С35.1І Фаг, Щ еШ I с 19 д в 2 | Гбз.5 4X1 43 Фиг. 15 С39.2 ± СШ _ СМ.2 на 46 сЗб.1 L С 39.3 А сШ 1 42.5 Фаг, 16 1660011 V Y 1660011 150нс 46 48 www 45 39.1—/ VOOOv -v -v \\\\\ // . Адресная зона мпи 53 61 Адресная зона ОШ 4 J г ч Z і 256 К Saum 1д-разряднш 22-разряо ныи адрес 1660011 Регистр расширения адреса I О Адрес с 0Ш 17 15 /4 / 0 х Адрес на ППИ 21 20 19 18 | 17 16 • • •1 0 15 Фиг. 20 ЗПРй \sms S&1 56.Z 56.3 53.Z $3.3 wg Т№\ 48.3 W ШТ. 1 m 502 57 pus PffT ПРО 55.1 МЧТ. ОТВ 52 SI m 55 J85 58.Z 55Л Ш, Фаг. if 1660011 S3 с 56.1 С 56.2 с 56.3 С56А 53.1 53.2 53.3 53А Фиг. 22 Г СЯ1 I ss 1" пі С58.1 4 С61 I CS8.Z I 552 на tЩ 52,59 Фе/г.23 1660011 \ 31. 49 >75нс У 52 І125НС 8\ 5657 вектор Х X s 58 Л. 10 SB. 5955.2 Фиг. Редактор М.Циткинз Составитель А.Засорин Техред М.Моргентал Корректор Т.Палий Заказ 1847 Тираж 410 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for conjugation of two pipelines

Автори англійськоюSerdiuk Yurii Avksentiiovych, Koval Mykola Oleksiiovych

Назва патенту російськоюУстройство для спряжения двух магистралей

Автори російськоюСердюк Юрий Авксентьевич, Коваль Николай Алексеевич

МПК / Мітки

МПК: G06F 13/00

Мітки: спряження, пристрій, двох, магістралей

Код посилання

<a href="https://ua.patents.su/20-324-pristrijj-dlya-spryazhennya-dvokh-magistralejj.html" target="_blank" rel="follow" title="База патентів України">Пристрій для спряження двох магістралей</a>

Попередній патент: Пристрій управління машиною для контактного стикового зварювання оплавленням

Наступний патент: Стабілізатор з залежною комутацією вихідної напруги постійного струму

Випадковий патент: Вимикач навантаження