Інтелектуальна розподілена система пам’яті з кільцевою шиною

Номер патенту: 99164

Опубліковано: 25.07.2012

Автори: Палагін Олександр Васильович, Тихонов Борис Михайлович, Єлісєєва Олена Володимирівна, Яковлєв Юрій Сергійович

Формула / Реферат

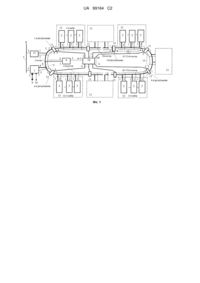

1. Інтелектуальна розподілена система пам'яті з кільцевою шиною, що містить системний контролер пам'яті, множину N блоків інтелектуальної пам'яті, кільцеву шину, що складається з кільцевої шини даних і кільцевої шини керування, блок керування кільцевою шиною, локальну шину даних, системний ввід/вивід даних, системний ввід/вивід керуючих сигналів, при цьому перший ввід/вивід системного контролера з'єднаний із системним вводом/виводом керуючих сигналів, другий ввід/вивід з'єднаний із системним вводом/виводом даних, третій ввід/вивід з'єднаний з локальною шиною даних, яка відрізняється тим, що в кільцеву шину введені n керованих секторних роздільників кільцевої шини на n секторів, загальні для кільцевої шини даних і кільцевої шини керування, при цьому множина із N блоків інтелектуальної пам'яті розділяються також на секторні набори, кількість яких визначається як (n-1), кількість блоків інтелектуальної пам'яті в кожному секторному наборі визначається як N/(n-1), вузол керування секторними роздільниками, блок службових функцій системи пам'яті, при цьому перший ввід/вивід і-го секторного роздільника з'єднаний з і-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з (і+1)-м сектором кільцевої шини даних, третій ввід/вивід з'єднаний з і-м сектором кільцевої шини керування, четвертий ввід/вивід з'єднаний з (і+1)-м сектором кільцевої шини керування, де 1≤і≤n, кожний j-й ввід/вивід вузла керування секторними роздільниками з'єднаний з п'ятим вводом/виводом відповідного j-гo секторного роздільника, де 1≤j≤n, (n+1) ввід/вивід з'єднаний із третім вводом/виводом блока керування кільцевою шиною, перший ввід/вивід блока керування кільцевою шиною з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини керування, перший ввід/вивід кожного m-го блока інтелектуальної пам'яті, де 1≤m≤N/(n-1), у кожному k-му секторному наборі з'єднаний з відповідним (k+1)-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з відповідним (k+1)-м сектором кільцевої шини керування, де 1≤k≤n-1, перший ввід/вивід блока службових функцій з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини керування, третій ввід/вивід з'єднаний з локальною шиною даних, четвертий ввід/вивід системного контролера з'єднаний з першим сектором кільцевої шини даних, п'ятий ввід/вивід з'єднаний з першим сектором кільцевої шини керування.

2. Інтелектуальна розподілена система пам'яті з кільцевою шиною за п. 1, яка відрізняється тим, що блок інтелектуальної пам'яті (БІП) містить кільцеву шину, що складається з кільцевої шини даних і кільцевої шини керування, розділену s керованими секторними роздільниками, загальними для кільцевої шини даних і кільцевої шини керування, на s секторів, блок керування кільцевою шиною БІП, вузол керування секторними роздільниками БІП, множину із Т банків інтелектуальної пам'яті, розділену на (s-1) секторних наборів, де кожний секторний набір містить T/(s-1) банків інтелектуальної пам'яті, контролер сектора, локальну шину керування, ведучий процесор з кеш-пам'яттю, локальну шину ведучого процесора, блок службових функцій БІП, контролер БІП, ввід/вивід даних БІП, ввід/вивід керуючих сигналів БІП, при цьому перший ввід/вивід r-го секторного роздільника з'єднаний з r-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з (r+1)-м сектором кільцевої шини даних, третій ввід/вивід з'єднаний з r-м сектором кільцевої шини керування, четвертий ввід/вивід з'єднаний з (r+1)-м сектором кільцевої шини керування, де 1≤r≤s, перший ввід/вивід блока керування кільцевою шиною БІП з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини керування, третій ввід/вивід з'єднаний з (s+1) вводом/виводом вузла керування секторними роздільниками БІП, кожний p-й ввід/вивід вузла керування секторними роздільниками з'єднаний з п'ятим вводом/виводом відповідного p-го секторного роздільника, де 1≤p≤s, перший ввід/вивід кожного q-гo банку інтелектуальної пам'яті, де 1≤q≤T/(s-1), у кожному v-му секторному наборі з'єднаний з відповідним (v+1)-м сектором кільцевої шини даних, перший ввід/вивід кожного контролера в кожному v-му секторі з'єднаний з відповідним (v+1)-м сектором кільцевої шини керування, другі вводи/виводи всіх банків інтелектуальної пам'яті й другий ввід/вивід контролера сектора в кожному v-му секторі з'єднані відповідно з локальною шиною сектора, де 1≤v≤s-1, перший ввід/вивід ведучого процесора з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини керування, третій ввід/вивід з'єднаний з локальною шиною ведучого процесора, перший ввід/вивід блока службових функцій з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевою шиною керування, третій ввід/вивід з'єднаний з локальною шиною ведучого процесора, перший ввід/вивід контролера БІП з'єднаний з вводом/виводом керуючих сигналів БІП, другий ввід/вивід з'єднаний з вводом/виводом даних БІП, третій ввід/вивід з'єднаний з локальною шиною даних ведучого процесора, четвертий ввід/вивід з'єднаний з першим сектором кільцевої шини даних, п'ятий ввід/вивід з'єднаний з першим сектором кільцевої шини керування.

3. Інтелектуальна розподілена система пам'яті з кільцевою шиною за п. 1, яка відрізняється тим, що кожний секторний набір блоків інтелектуальної пам'яті (БІП) додатково містить локальну шину даних, причому перший ввід/вивід кожного блока інтелектуальної пам'яті з'єднаний з відповідним сектором кільцевої шини даних, другий ввід/вивід кожного блока інтелектуальної пам'яті з'єднаний з відповідним сектором кільцевої шини керування, треті вводи/виводи кожного блока інтелектуальної пам'яті з'єднані з локальною шиною даних.

4. Інтелектуальна розподілена система пам'яті з кільцевою шиною за п. 1 або п. 2, яка відрізняється тим, що вузол керування секторними роздільниками містить n дворозрядних регістрів, розділених на n/2w лінійок, кожна лінійка містить w регістрів, де n - кількість секторних роздільників, розрядність (n+1) вводу/виводу вузла керування секторними роздільниками дорівнює (2w+4), n тригерів, розділених на n/2w лінійок, кожна лінійка містить 2w тригерів, перший, третій і четвертий набори з 2w схем "І", другий набір з n схем "І", набір з (n-4w) схем "2І-АБО", розділених на (n-4w)/2w лінійок, (n+1) вводів/виводів вузла керування секторними роздільниками, причому перші входи кожної α-схеми першого набору схем "І" з'єднані з α-елементом (n+1) вводу/виводу вузла керування секторними роздільниками, де 1≤α≤2w, другі входи з'єднані з (2w+1) елементом (n+1) вводу/виводу вузла керування секторними роздільниками, вихід кожної (2α-1) схеми "І" першого набору з'єднаний з першим входом α-го регістра першої лінійки тригерів, вихід кожної 2α-схеми "І" першого набору з'єднаний із другим входом α-го регістра, де 1≤α≤w, перший і другий виходи α-го регістра γ-ї лінійки з'єднані з першим і другим входами α-го регістра (γ+1) лінійки, де 1≤γ<(n/2w)-1, третій вихід кожного з регістрів з'єднаний з першим входом відповідної схеми "І" другого набору, другі входи всіх схем "І" другого набору з'єднані з (2w+2) елементом (n+1) вводу/виводу вузла керування секторними роздільниками, вихід кожної η-ї схеми "І" другого набору з'єднаний з η-м вводом/виводом вузла керування секторними роздільниками, де 1≤η≤n, перші входи схем "І" третього набору й перші входи всіх схем "2І-АБО" з'єднані з відповідним вводом/виводом вузла керування секторними роздільниками, другі входи схем "І" третього набору й другі входи всіх схем "2I-АБО" з'єднані з (2w+3) елементом (n+1) вводу/виводу вузла керування секторними роздільниками, вихід кожної μ-ї схеми "І" третього набору з'єднаний із входом μ-го тригера першої лінійки тригерів, де 1≤μ≤2w, вихід кожного μ-го тригера в λ-й лінійці тригерів з'єднаний із третім входом μ-ї схеми "2І-АБО" в λ-й лінійці, де 1≤λ≤(n/2w)-1, четвертий вхід усіх схем "2І-АБО" з'єднаний з (2w+4) елементом (n+1) вводу/виводу вузла керування секторними роздільниками, вихід кожного μ-го тригера в (n/2w) лінійці з'єднаний з першим входом μ-ї схеми "І" четвертого набору, другі входи μ-ї схеми "І" четвертого набору з'єднані з (2w+4) елементом (n+1) вводу/виводу вузла керування секторними роздільниками, вихід кожної μ-ї схеми "І" четвертого набору з'єднаний з μ-м елементом (n+1) вводу/виводу вузла керування секторними роздільниками.

5. Інтелектуальна розподілена система пам'яті з кільцевою шиною за п. 1 або п. 2, яка відрізняється тим, що кожний секторний роздільник системи містить перший (d+e) розрядний регістр, другий дворозрядний регістр, набір схем "2І-АБО", що містить (d+e) елементів, набір схем "І", що містить 2(d+e) елементів, де d - розрядність шини даних, е - розрядність шини керування, п'ять вводів/виводів секторного роздільника, при цьому перші входи схеми "І" кожної зі схем "2І-АБО" від першої до d-ї з'єднані з першим вводом/виводом секторного роздільника, перші входи перших схем "І" кожної зі схем "2І-АБО" від (d+1)-ї до (d+e)-ї з'єднані із третім вводом/виводом секторного роздільника, перші входи других схем "І" кожної зі схем "2І-АБО" від першої до d-ї з'єднані із другим вводом/виводом секторного роздільника, перші входи других схем "І" кожної зі схем "2І-АБО" від (d+1)-ї до (d+e)-ї з'єднані із четвертим вводом/виводом секторного роздільника, другі входи перших схем "І" кожної зі схем "2І-АБО" від першої до (d+e)-ї з'єднані з першим виходом другого регістра, другі входи других схем "І" кожної зі схем "2І-АБО" від першої до (d+e)-ї з'єднані із другим виходом другого регістра, вихід ε кожної схеми "2І-АБО" з'єднаний з відповідним ε-м входом першого регістра, де 1≤ε≤(d+e), перші входи кожної (2θ-1) і 2θ схем "І" з'єднані з θ виходом першого регістра, другі входи кожної непарної схеми "І" з'єднані з першим виходом другого регістра, другі входи кожної парної схеми "І" з'єднані із другим виходом другого регістра, вихід кожної непарної схеми "І" від першої до 2d з'єднаний із другим вводом/виводом секторного роздільника, вихід кожної непарної схеми "І" від 2d до 2(d+e) з'єднаний із четвертим вводом/виводом секторного роздільника, вихід кожної парної схеми "І" від першої до 2d з'єднаний з першим вводом/виводом секторного роздільника, вихід кожної парної схеми "І" від 2d до 2(d+e) з'єднаний із третім вводом/виводом секторного роздільника, вхід другого регістра з'єднаний з п'ятим вводом/виводом секторного роздільника, вхід тригера стану з'єднаний із четвертим вводом/виводом секторного роздільника, вихід тригера стану з'єднаний з п'ятим вводом/виводом секторного роздільника.

6. Інтелектуальна розподілена система пам'яті з кільцевою шиною за п. 1, яка відрізняється тим, що блок службових функцій містить вузол керування службовими функціями системи пам'яті, вузол розподілу адресного простору всієї пам'яті системи по блоках інтелектуальної пам'яті (БІП), вузол розміщення даних по розподілених адресних просторах БІП, вузол розділення програми користувача на частини і розміщення їх по процесорах БІП, перший інтерфейс для вводу/виводу даних і кодів адреси, другий інтерфейс для вводу/виводу керуючих сигналів, перший вхід/вихід блока службових функцій, з'єднаний з першим сектором кільцевої шини даних, другий вхід/вихід, з'єднаний з першим сектором кільцевої шини керування, третій вхід/вихід, підключений до локальної шини, при цьому перший вхід/вихід блока службових функцій з'єднаний з першим входом/виходом даних першого інтерфейсу, другий вхід/вихід якого з'єднаний з першим входом/виходом даних вузла розподілу пам'яті, другий вхід/вихід сигналів керування якого з'єднаний відповідно з першими входами/виходами сигналів керування вузла розміщення даних, вузла розділення додатків і з першим входом/виходом другого інтерфейсу, другий вхід/вихід якого з'єднаний з другим входом/виходом блока службових функцій і з першим входом/виходом вузла керування службовими функціями, другі входи/виходи якого з'єднані з третім входом/виходом блока службових функцій, при цьому третій вхід/вихід вузла керування службовими функціями з'єднаний з третім входом/виходом вузла розподілу пам'яті, четвертий вхід/вихід сигналів керування якого з'єднаний з четвертим входом/виходом вузла керування службовими функціями, п'ятий вхід/вихід даних якого з'єднаний з другим входом/виходом вузла розміщення даних, третій вхід/вихід сигналів керування якого з'єднаний з шостим входом/виходом вузла керування, сьомий вхід/вихід даних якого з'єднаний з другим входом/виходом вузла розділення додатків, третій вхід/вихід сигналів керування якого з'єднаний з відповідним восьмим входом/виходом вузла керування службовими функціями, четвертий вхід/вихід даних вузла розміщення даних і четвертий вхід/вихід даних вузла розділення додатків з'єднані з третім входом/виходом даних першого інтерфейсу.

Текст