Мережний програмований контролер

Номер патенту: 79363

Опубліковано: 11.06.2007

Автори: Фурман Ілля Олександрович, Радченко Станіслав Станіславович

Формула / Реферат

Мережний програмований контролер, який містить схему порівняння, блоки пам'яті станів та команд, вузол логічного керування, лічильник адреси та блок пам'яті переходів, перший вхід якого з'єднаний з першим входом контролера, який підключений також до першого входу схеми порівняння, до другого входу якої підключений перший вихід блока пам'яті станів, перший вхід якого з'єднаний з першим входом блока пам'яті команд та з виходом лічильника адреси, перший вхід якого є другим входом контролера, другий вхід лічильника адреси з'єднаний з першим виходом блока пам'яті переходів, другий вихід якого підключений до першого входу вузла логічного керування, до другого входу якого підключений вихід схеми порівняння, а до третього входу підключений другий вихід блока пам'яті станів, перший і другий виходи вузла логічного керування підключені відповідно до третього та четвертого входів лічильника адреси, вихід блока пам'яті команд є першим виходом контролера, який відрізняється тим, що введено модуль зв'язку, при цьому перший вхід контролера підключений до першого входу модуля зв'язку, перший вихід якого підключений до третього входу схеми порівняння, другий вихід модуля зв'язку підключений до другого входу блока пам'яті переходів, а третій вихід модуля зв'язку є другим виходом контролера, перший вихід контролера з'єднаний з третім входом блока пам'яті переходів та з другим входом модуля зв'язку, третій вхід якого є третім входом контролера.

Текст

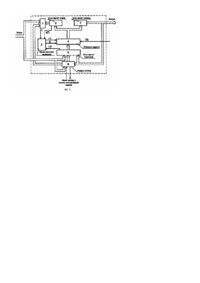

дії. Винахід належить до автоматики, а точніше - до пристроїв логічного керування об'єктами дискретної циклічної Відомий програмований логічний контролер [а.с. 1302242 СРСР, 30.12.85, G05В19/18, опубл.07.04.97. Бюл. №13], що містить блоки пам'яті станів та команд, схему порівняння та лічильник адреси, перший вхід якого є першим входом пристрою, вихід лічильника адреси є першим виходом пристрою та з'єднаний з адресними входами блоків пам'яті станів та команд, інформаційний вихід блока пам'яті станів підключений до першого входу схеми порівняння, другий вхід якої є др угим входом пристрою, другим виходом якого є перший (інформаційний) вихід блоку пам'яті команд. Аналог забезпечує програмне керування об'єктами як з детермінованою так і з випадковою послідовністю виконуваних операцій, однак має суттєвий недолік, а саме при будуванні контролерних мереж на основі аналогу деякі блоки стають незадіяними (надмірними), крім того, застосовується метод аналізу умов переходів, реалізація якого зв'язана з підвищеними апаратними витратами. Найбільш близьким за сукупністю ознак до пропонуємого винаходу є мережний програмований контролер [37651 A, G05В19/18, опубл.15.05.2001, Бюл. №4], який містить схему порівняння, блоки пам'яті станів та команд, вузол логічного керування, лічильник адреси та блок пам'яті переходів, вхід якого з'єднаний з першим входом пристрою, який підключений також до першого входу схеми порівняння, до другого входу якої підключений перший вихід блоку пам'яті станів, перший вхід якого з'єднаний з першим входом блоку пам'яті команд та з виходом лічильника адреси, перший вхід якого є другим входом пристрою, другий вхід лічильника адреси з'єднаний з першим виходом блоку пам'яті переходів, другий ви хід якого підключений до першого входу вузла логічного керування, до другого входу якого підключений вихід схеми порівняння, а до третього входу підключений другий вихід блоку пам'яті станів, перший і другий виходи вузла логічного керування підключені відповідно до третього та четвертого входів лічильника адреси, вихід блоку пам'яті команд є першим виходом пристрою. У прототипі ліквідовані недоліки аналогу у частині надмірності апаратних витрат. Причини, які перешкоджають досягненню прототипом очікуваного технічного результату, полягають у наступному: контролерна мережа за прототипом може функціонувати лише за схемою: 1 ведучий + n ведених, що обмежує можливість побудови розподілених мереж керування з використанням контролерів, кожен з яких має однакові функціональні можливості роботи в мережі, неекономічний (багатопровідний) зв'язок між контролерами, відсутність можливості під’єднання до інших обчислювальних та керуючих систем за допомогою стандартних інтерфейсів, обмежена довжина каналу зв'язку по ШД. В основу винаходу поставлено задачу вдосконалення структури мережного програмованого контролера шляхом введення до нього нових блоків та зв'язків, що дають можливість усунути недоліки прототипу. Реалізація поставленої задачі досягається тим, що у мережний програмований контролер, який містить схему порівняння, блоки пам'яті станів та команд, вузол логічного керування, лічильник адреси та блок пам'яті переходів, вхід якого з'єднаний з першим входом пристрою, який підключений також до першого входу схеми порівняння, до другого входу якої підключений перший вихід блоку пам'яті станів, перший вхід якого з'єднаний з першим входом блоку пам'яті команд та з виходом лічильника адреси, перший вхід якого є другим входом пристрою, другий вхід лічильника адреси з'єднаний з першим виходом блоку пам'яті переходів, др угий ви хід якого підключений до першого входу вузла логічного керування, до другого входу якого підключений вихід схеми порівняння, а до третього входу підключений другий вихід блоку пам'яті станів, перший і другий виходи вузла логічного керування підключені відповідно до третього та четвертого входів лічильника адреси, вихід блоку пам'яті команд є першим виходом пристрою, введено модуль зв'язку, при цьому перший вхід пристрою підключений до першого виходу модуля зв'язку, др угий вихід якого підключений до першого входу блоку пам'яті переходів, а третій вихід модуля зв'язку є др угим ви ходом пристрою, перший вихід пристрою з'єднаний з третім входом блоку пам'яті переходів та з другим входом модуля зв'язку, третій вхід якого є третім входом пристрою. Введення вказаних відрізняючих ознак винаходу дозволяє усунути неекономічний (багатопровідний) зв'язок між контролерами, також дозволяє можливість під’єднання до інших обчислювальних та керуючих систем за допомогою стандартних інтерфейсів. При будуванні контролерних мереж на основі пропонуємого пристрою застосовується такий принцип їх будування, при якому контролерна мережа являє собою розподілену мережу керування з використанням контролерів, кожен з яких має однакові функціональні можливості роботи в мережі. На Фіг. наведена блок-схема запропонованого пристрою. Пристрій містить схему порівняння 1, вузол логічного керування 2, блок пам'яті станів 3, лічильник адреси 4, блок пам'яті переходів 5, модуль зв'язку 6 та блок пам'яті команд 7, вхід блоку пам'яті переходів 5 з'єднаний з першим входом пристрою, який підключений також до першого входу схеми порівняння 1, до другого входу якої підключений перший вихід блоку пам'яті станів 3, перший вхід якого з'єднаний з першим входом блоку пам'яті команд 7 та з виходом лічильника адреси 4, перший вхід якого є другим входом пристрою, другий вхід лічильника адреси 4 з'єднаний з першим виходом блоку пам'яті переходів 5, другий вихід якого підключений до першого входу вузла логічного керування 2, до другого входу якого підключений вихід схеми порівняння 1, а до третього входу підключений другий вихід блоку пам'яті станів 3, перший і другий виходи вузла логічного керування 2 підключені відповідно до третього та четвертого входів лічильника адреси 4, вихід блоку пам'яті команд 7 є першим виходом пристрою, перший вхід пристрою підключений до першого входу модуля зв'язку 6, перший вихід якого підключений до третього входу схеми порівняння 1, другий вихід модуля зв'язку 6 підключений до другого входу блоку пам'яті переходів 5, а третій вихід модуля зв'язку 6 є другим ви ходом пристрою, перший вихід пристрою з'єднаний з третім входом блоку пам'яті переходів 5 та з другим входом модуля зв'язку 6, третій вхід якого є третім входом пристрою. Блок 3 пам'яті станів та блок 7 пам'яті команд призначені для зберігання програми (яка у загальному випадку складається із k підпрограм) керування циклом роботи обслуговуємого об'єкта. Програма керування циклом у запропонованому контролері являє собою послідовність рядків, кожний з яких складається з двох частин: 1) комбінації команд на вмикання та вимикання m механізмів, 2) комбінації станів, в які повинні прийти n датчиків у результаті спрацьовування m механізмів, при цьому до блока 7 пам'яті команд записується послідовність комбінацій команд на вмикання та вимикання механізмів, а до блока 3 пам'яті станів – послідовність комбінацій станів, до яких повинні прийти датчики, які фіксують положення механізмів в результаті виконання відповідних команд. Адресація блоків 3 та 7 здійснюється паралельно за допомогою лічильника адреси 4. Блок 5 пам'яті переходів призначений для зберігання та відпрацьовування програми вибору початкових адрес підпрограм, які записані у блоках 3 та 7 пам'яті станів та команд. Схема порівняння 1 призначена для паралельного (одночасного) порівняння комбінацій фактичних станів датчиків циклу з їх очікуваними значеннями, які записані в і-му рядку блока 3 пам'я ті станів. Вузол логічного керування 2 в залежності від комбінації сигналів на його входах здійснює логічне керування роботою лічильника адреси 4. Модуль зв'язку 6 призначений для забезпечення роботи пристрою у розподілених промислових мережах, а також для підключення до інших обчислювальних та керуючих систем. Запропонований пристрій може бути реалізований, наприклад, на програмованих логічних інтегральних схемах (ПЛІС) з застосуванням автоматизованої системи проектування (САПР) MAX+PLUS II. Мережний програмований контролер паралельної дії працює таким чином. Встановлення пристрою у початковий стан здійснюється за допомогою зовнішнього імпульсного сигналу початкового встановлення ПВ, який обнуляє лічильник адреси. Процес відпрацьовування керуючої програми складається з двох етапів: 1) аналізу комбінацій станів датчиків умов переходів (станів зовнішнього середовища) та формування початкової адреси підпрограми; 2) власне відпрацьовування вибраної підпрограми, причому аналіз станів зовнішнього середовища здійснюється паралельно та незалежно від відпрацьовування підпрограми. В останньому рядку кожної підпрограми а також у нульовому рядку програми записується тільки ознака кінця підпрограми КП, яка використовується як дозвіл переходу пристрою до відпрацьовування будь-якої із записаних у блоках 3 та 7 підпрограм. Вибір початкової адреси підпрограми здійснюється за допомогою блока 5 пам'яті переходів, який у разі виникнення на його вході однієї із запрограмованих комбінацій встановлює лічильник адреси до відповідного даній комбінації стану. До вузла логічного керування 2 записуються такі логічні рівняння: E × КП × ПР + ПР = А, У × КП × ПР = + 1 де ПР - ознака переривання, Е - сигнал еквівалентності з виходу схеми порівняння 1. Якщо вирішується логічне рівняння: E × КП× ПР + ПР = А , то на другому виході вузла логічного керування 2 з'являється сигнал "Адреса" ("А"), за яким лічильник адреси 4 здійснює переадресацію блоків пам'яті станів 3 та команд 7 на першу адресу вибраної підпрограми. Якщо вирішується логічне рівняння: E × КП× ПР = +1, то на першому виході вузла логічного керування 2 з'являється сигнал "+1", за яким лічильник адреси 4 адресує блоки 3 та 7 пам'яті станів та команд до наступного (і+1) рядка. Якщо на якому-небудь кроці підпрограми вийде з ладу механізм або датчик (який не приводить до аварійної ситуації), перехід до наступного рядка підпрограми не відбувається, тому що не спрацьовує схема порівняння 1. У разі виходу з ладу механізмів або датчиків можливе виникнення заборонених комбінацій станів механізмів, при яких у керуємих об'єктах можуть з'являтися аварійні ситуації, які потребують негайного втручання до процесу керування. Для реакції пристрою на аварійні ситуації один з виходів блока 5 пам'яті переходів виділений для фіксації та видачі на третій вхід вузла логічного керування 2 сигналу ознаки переривання ПР, при цьому вирішується логічне рівняння: ПР=А, у результаті чого лічильник адреси без очікування кінця відпрацьовування робочої підпрограми переадресує блоки 3 та 7 пам'яті станів та команд до початкової адреси підпрограми переривання. При роботі запропонованого пристрою в контролерній мережі сигнали про стан входів і виходів інши х контролерів з каналу зв'язку через третій вхід пристрою за допомогою модуля зв'язку подаються на третій вхід схеми порівняння, а сукупність сигналів про стан входів і виходів даного контролера за допомогою модуля зв'язку через другий вихід пристрою передаються до інших контролерів мережі за допомогою каналу зв'язку. В якості каналу зв'язку може бути використано 2-3 провідний послідовний стандартний інтерфейс, що дозволяє організовувати канал зв'язку довжиною до 400м.

ДивитисяДодаткова інформація

Назва патенту англійськоюNetwork programmable controller

Автори англійськоюFurman Illia Oleksandrovych

Назва патенту російськоюСетевой программируемый контроллер

Автори російськоюФурман Илья Александрович

МПК / Мітки

МПК: G05B 19/05, G05B 19/18, G05B 19/04

Мітки: програмований, мережний, контролер

Код посилання

<a href="https://ua.patents.su/3-79363-merezhnijj-programovanijj-kontroler.html" target="_blank" rel="follow" title="База патентів України">Мережний програмований контролер</a>

Попередній патент: Півторавольтовий літієвий елемент

Наступний патент: Спосіб визначення питомої роботи корчування зерен кукурудзи при різних кінематичних режимах

Випадковий патент: Паливна композиція із суміші рослинних олій та дизельного палива