Пристрій та спосіб модуляції/демодуляції із обмеженням на поточний мінімальний розмір коду

Номер патенту: 49081

Опубліковано: 16.09.2002

Автори: Накамура К., Ван ден Енден Гійзберт Дж., Шухамер Іммінк Корнеліс Антоні, Наохара Т., Шін-Пуку Й., Калман Джозеф А.Х.М., Накагава Т.

Формула / Реферат

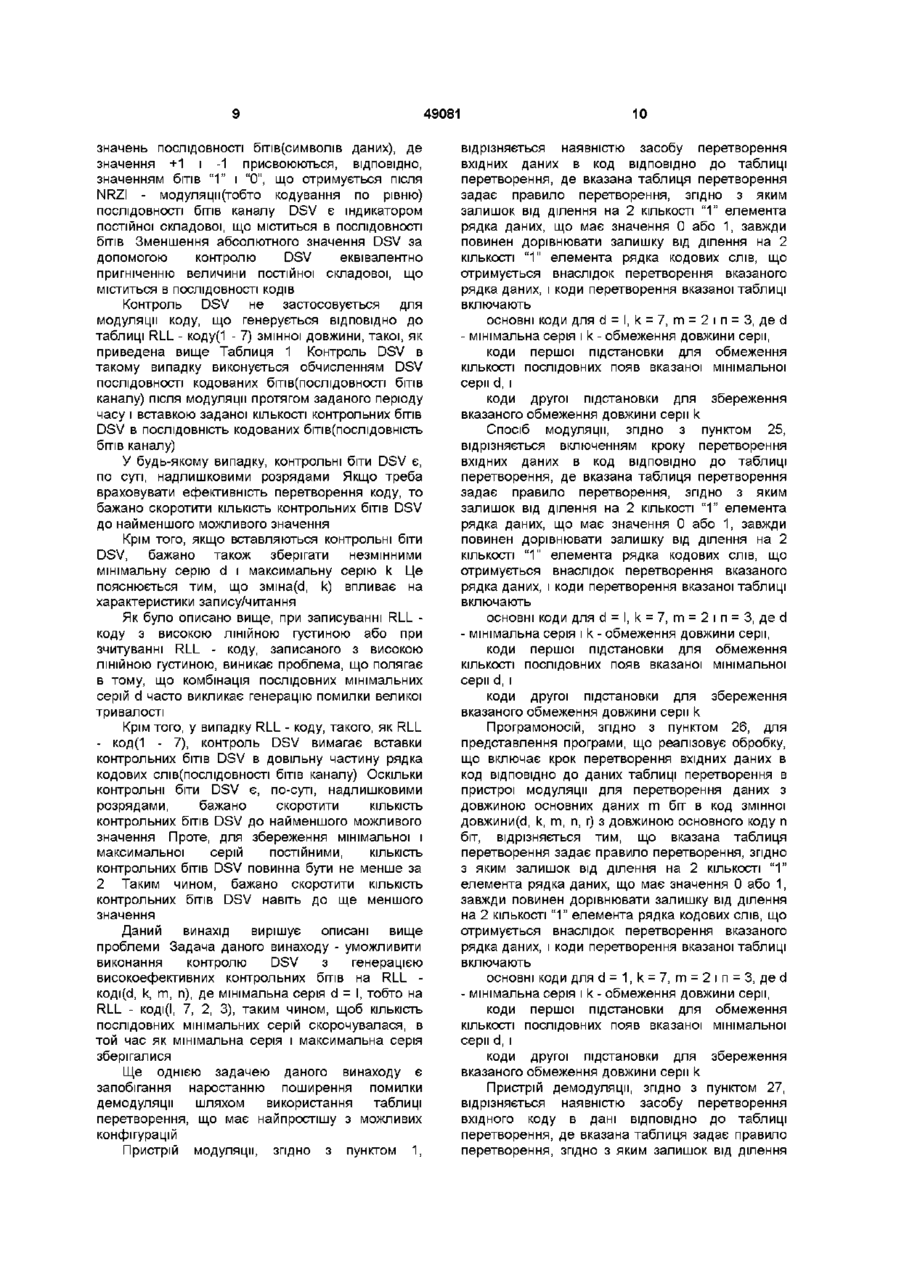

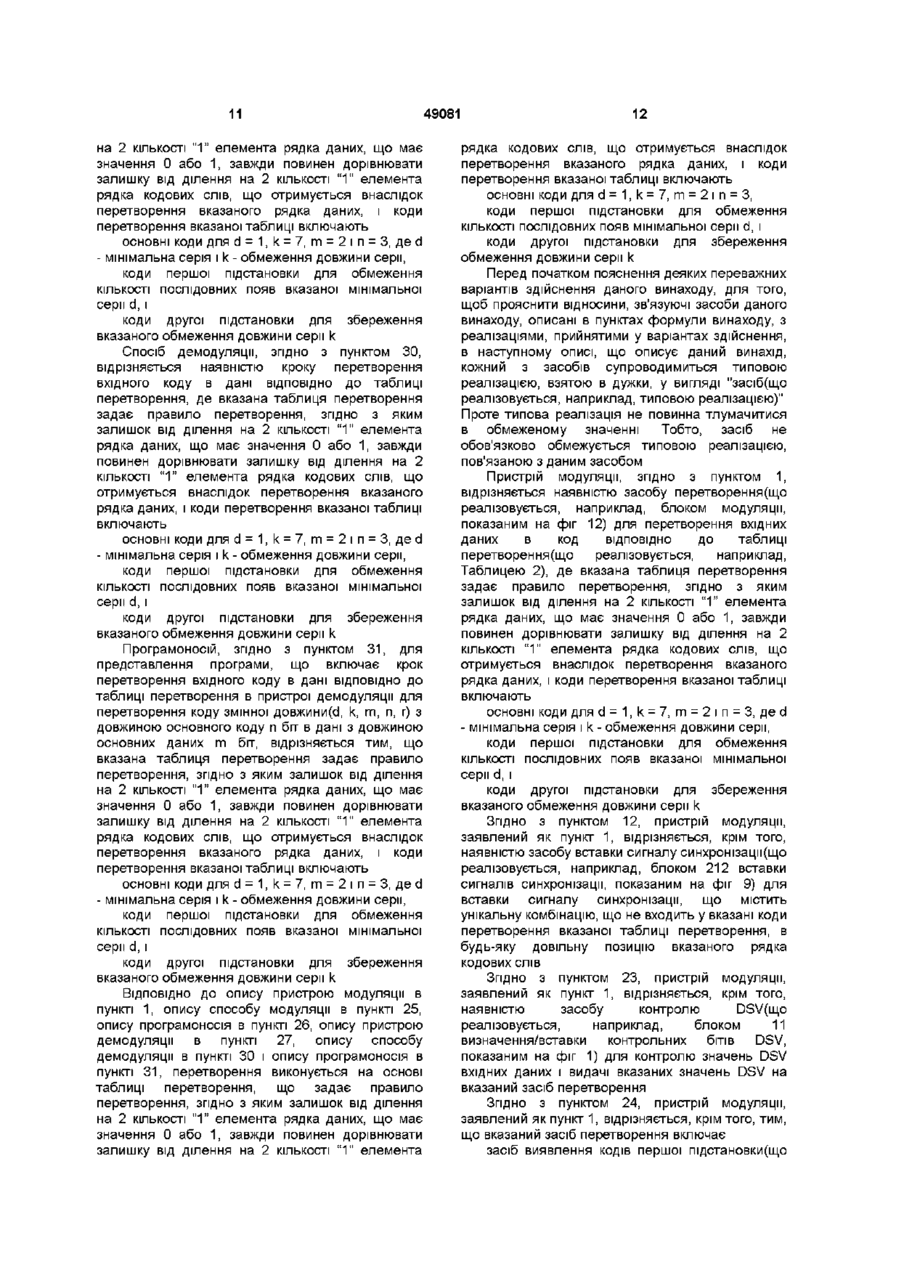

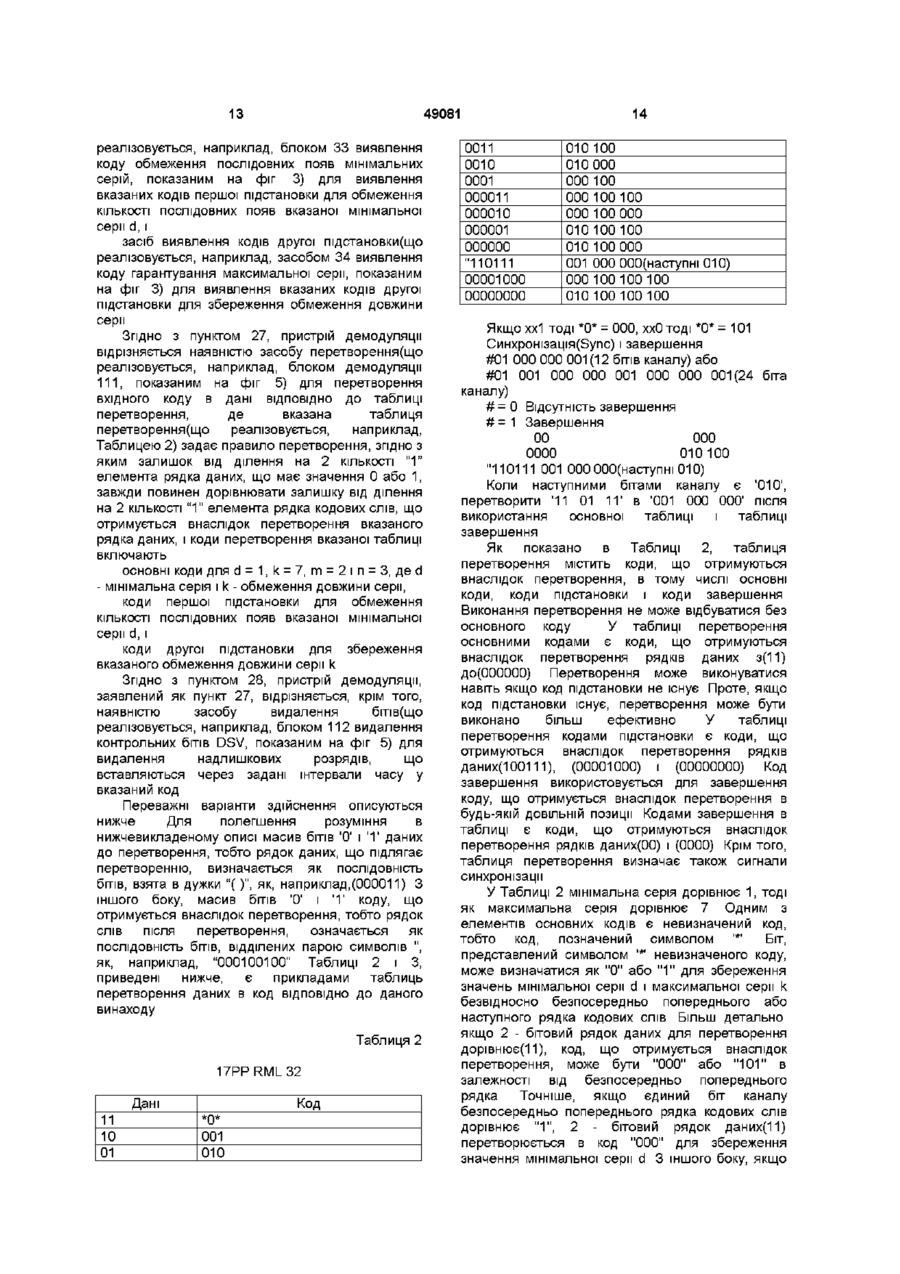

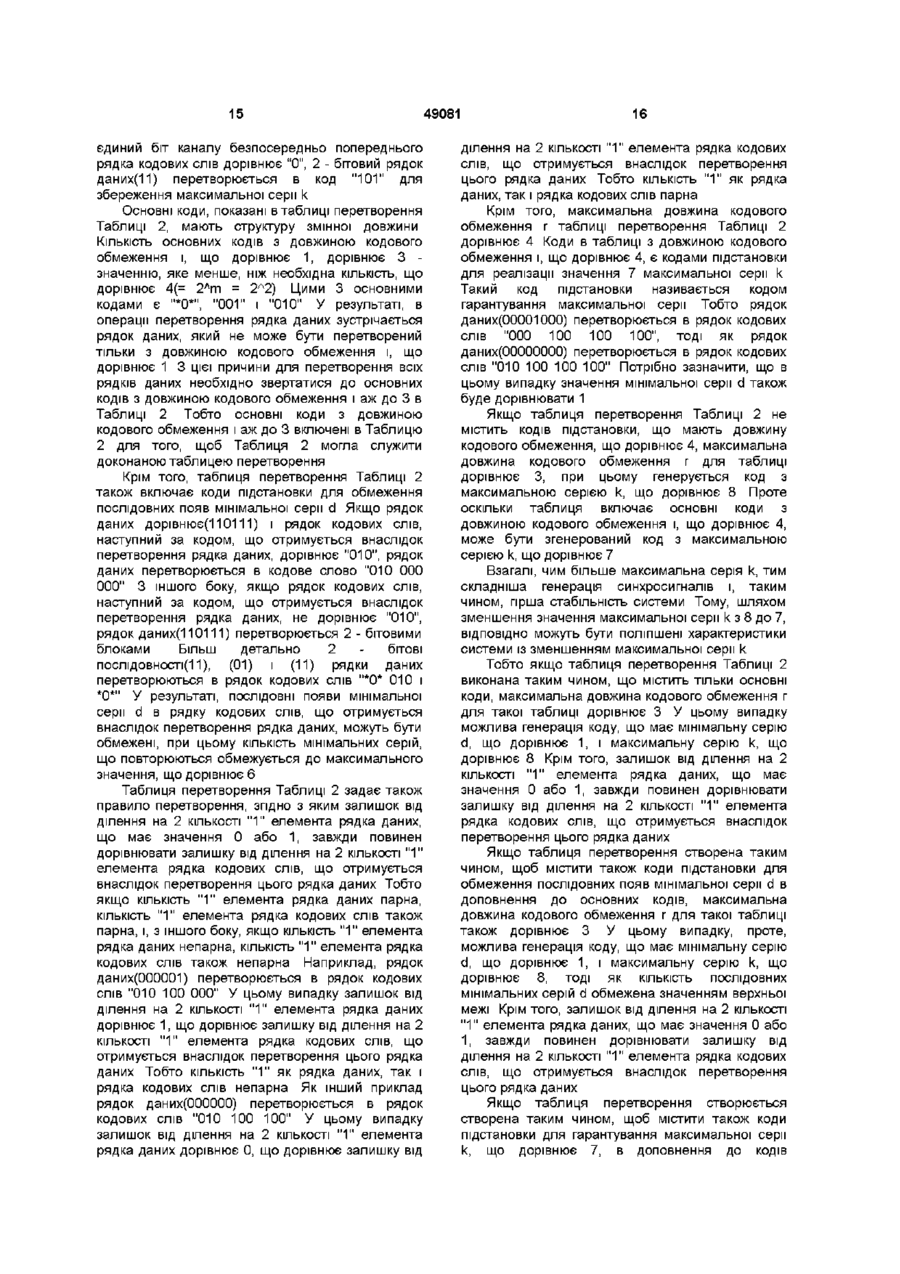

1. Пристрій модуляції для перетворення даних з довжиною основних даних m бітів в код змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів, де d є мінімальною серією і k є обмеженням довжини серії, який відрізняється тим, що включає в себе засіб перетворення вхідних даних в код відповідно до таблиці перетворення, де вказана таблиця перетворення задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=1, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

2. Пристрій модуляції за п. 1, який відрізняється тим, що кількість пар, кожна з яких складається з рядка даних і кодового рядка, що складають вказані основні коди, для довжини кодового обмеження і, що дорівнює 1, менша 4 (=2^m=2^2).

3. Пристрій модуляції за п. 1, який відрізняється тим, що вказані основні коди вказаної таблиці перетворення мають структуру змінної довжини.

4. Пристрій модуляції за п. 1, який відрізняється тим, що вказані основні коди вказаної таблиці перетворення включають код '*0*', де символ * є невизначеним кодом, який дорівнює '0', якщо безпосередньо попереднє або наступне кодове слово дорівнює '1', і '1', якщо вказане безпосередньо попереднє або наступне кодове слово дорівнює '0', при цьому мається на увазі, що вказаний код '*0*' дорівнює '000' або '101'.

5. Пристрій модуляції за п. 1, який відрізняється тим, що вказані коди перетворення вказаних таблиць перетворення включають коди, кожний з яких визначається зверненням до безпосередньо наступного рядка кодових слів або безпосередньо наступного рядка даних.

6. Пристрій модуляції за п. 1, який відрізняється тим, що вказані коди перетворення вказаних таблиць перетворення включають коди, кожний з яких визначається зверненням до безпосередньо наступного рядка кодових слів або рядка кодових слів спеціального типу.

7. Пристрій модуляції за п. 5, який відрізняється тим, що кожний з вказаних кодів, що визначається зверненням до безпосередньо наступного рядка кодових слів або безпосередньо наступного рядка даних, є вказаним кодом першої або другої підстановки.

8. Пристрій модуляції за п. 1, який відрізняється тим, що кількість пар, кожна з яких складається з рядка даних і кодового рядка, що складають вказані основні коди, для довжини кодового обмеження і, що дорівнює 1, дорівнює 4 (=2^m=2^2).

9. Пристрій модуляції за п. 1, який відрізняється тим, що для довжин кодового обмеження і, рівних 2 і більше, всі вказані коди перетворення є вказаними кодами першої і другої підстановки.

10. Пристрій модуляції за п. 1, який відрізняється тим, що вказані коди перетворення для довжини кодового обмеження і, що дорівнює 2, є кодами для збереження значення вказаної мінімальної серії d рівним 1.

11. Пристрій модуляції за п. 1, який відрізняється тим, що вказані коди перетворення вказаних таблиць перетворення включають коди, кожний з яких визначається зверненням до безпосередньо попереднього рядка кодових слів.

12. Пристрій модуляції за п. 1, який відрізняється тим, що вказаний пристрій має додатково засіб вставлення для вставлення сигналу синхронізації, що включає в себе унікальну комбінацію, що не входить у вказані коди перетворення вказаної таблиці перетворення, в будь-яку довільну позицію вказаного рядка кодових слів.

13. Пристрій модуляції за п. 12, який відрізняється тим, що вказана унікальна комбінація є комбінацією, що порушує вказану максимальну серію k.

14. Пристрій модуляції за п. 12, який відрізняється тим, що вказана унікальна комбінація є комбінацією, що зберігає вказану мінімальну серію d.

15. Пристрій модуляції за п. 12, який відрізняється тим, що унікальна комбінація у вказаному сигналі синхронізації містить одне кодове слово на її початку, що служить з'єднувальним бітом з кодовим словом, що отримується внаслідок перетворення аж до безпосередньо попередніх даних, другий біт для збереження вказаної мінімальної серії d і третій біт.

16. Пристрій модуляції за п. 12, який відрізняється тим, що вказаний сигнал синхронізації має довжину щонайменше 12 кодових слів.

17. Пристрій модуляції за п. 12, який відрізняється тим, що для сигналу синхронізації довжиною щонайменше 21 кодове слово вказаний сигнал синхронізації містить не менше за 2 комбінації з максимальною серією k, що дорівнює 8.

18. Пристрій модуляції за п. 12, який відрізняється тим, що вказані коди перетворення вказаної таблиці перетворення включають коди завершення, кожний з них для завершення вказаного коду, що отримується внаслідок перетворення.

19. Пристрій модуляції за п. 18, який відрізняється тим, що вказані коди завершення передбачені для вказаних основних кодів з довжиною кодового обмеження і, для якої кількість пар, кожна з яких складається з рядка даних і кодового рядка, що складають вказані основні коди, менша 4 (=2^m =2^2), і задають правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних.

20. Пристрій модуляції за п. 18, який відрізняється тим, що для ідентифікації вказаного коду завершення одне кодове слово на початку вказаної комбінації сигналу синхронізації, що служить з'єднувальним бітом, встановлюється в '1', коли використовується вказаний код завершення, і в '0', коли вказаний код завершення не використовується.

21. Пристрій модуляції за п. 12, який відрізняється тим, що вказана унікальна комбінація вміщена між 3 бітами на початку вказаного сигналу синхронізації і 3 бітами в кінці вказаного сигналу синхронізації, і вказані 3 біти на початку і 3 біти в кінці використовуються як перехід, що містить біти даних і з'єднувальні біти.

22. Пристрій модуляції за п. 12, який відрізняється тим, що:

перший з 3 бітів на початку вказаного сигналу синхронізації має значення, що представляє слова даних до перетворення, що розглядаються m- бітовими блоками;

другий з вказаних 3 бітів встановлюється в '1' для забезпечення вказаного сигналу синхронізації;

перший з 3 бітів в кінці вказаного сигналу синхронізації встановлюється в '0' для забезпечення вказаного сигналу синхронізації; і

другий з вказаних 3 бітів в кінці має значення, що представляє вказані слова даних до перетворення, що розглядаються m- бітовими блоками.

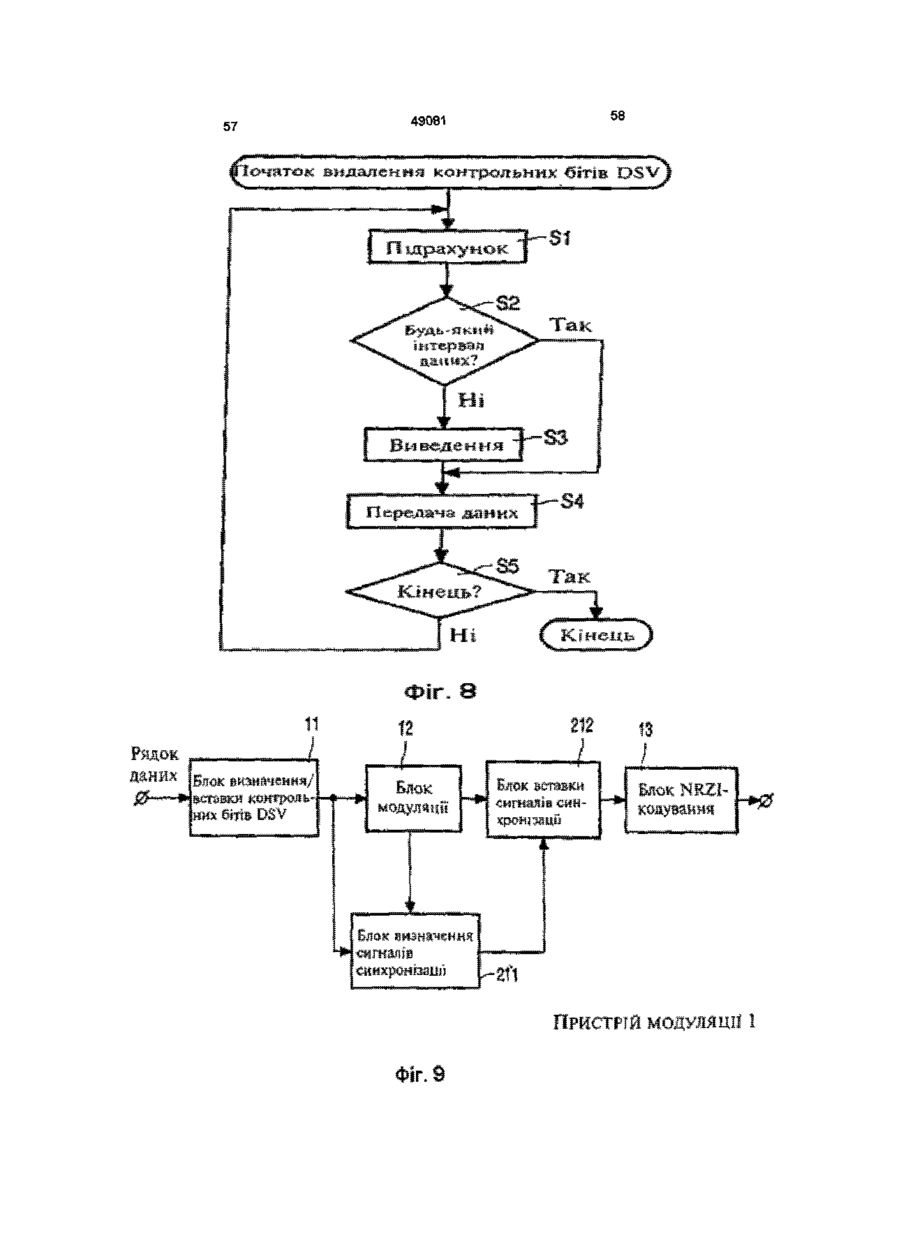

23. Пристрій модуляції за п. 1, який відрізняється тим, що вказаний пристрій додатково має засіб контролю DSV для контролю DSV вхідних даних і подачі вказаного DSV на вказаний засіб перетворення.

24. Пристрій модуляції за п. 1, який відрізняється тим, що вказаний засіб перетворення включає:

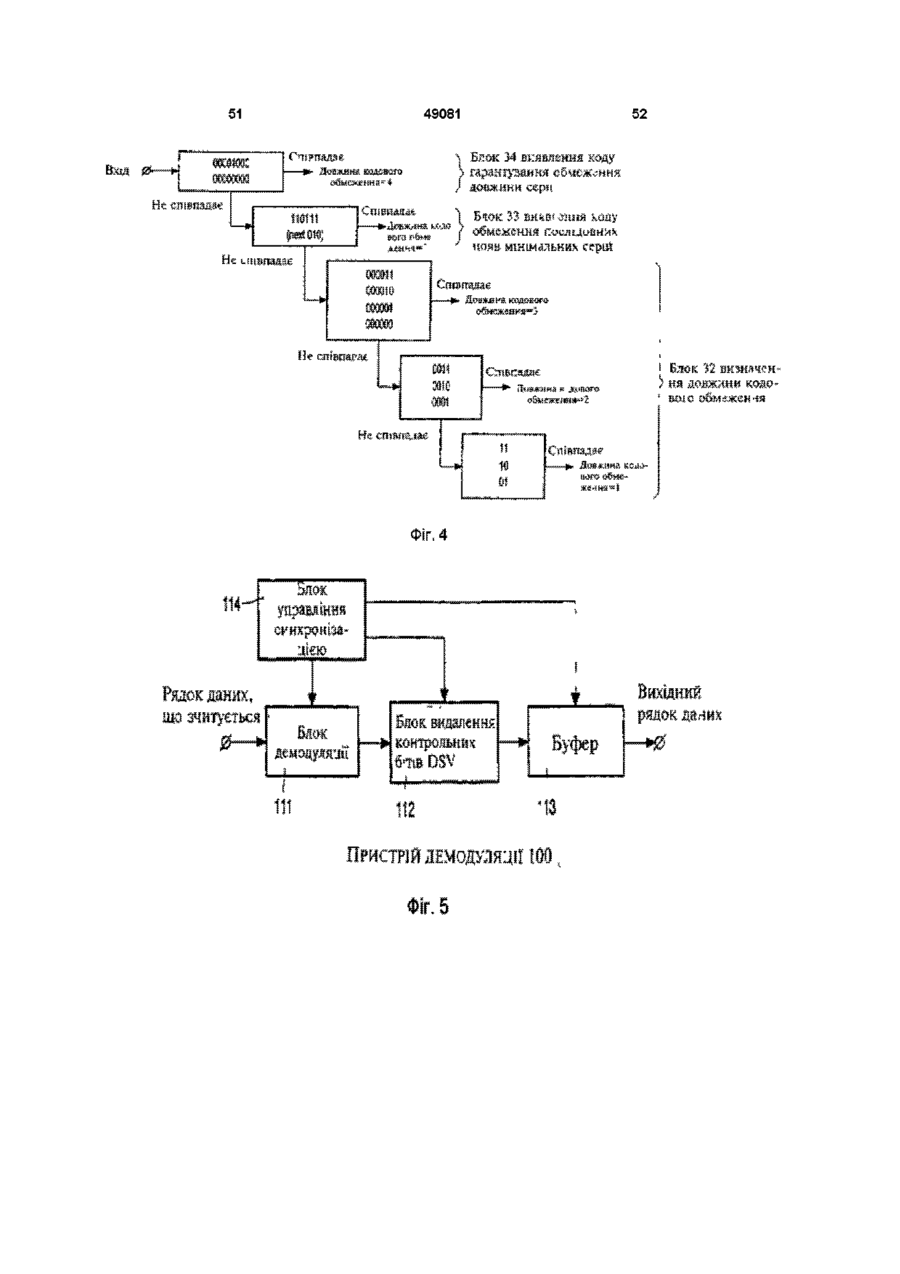

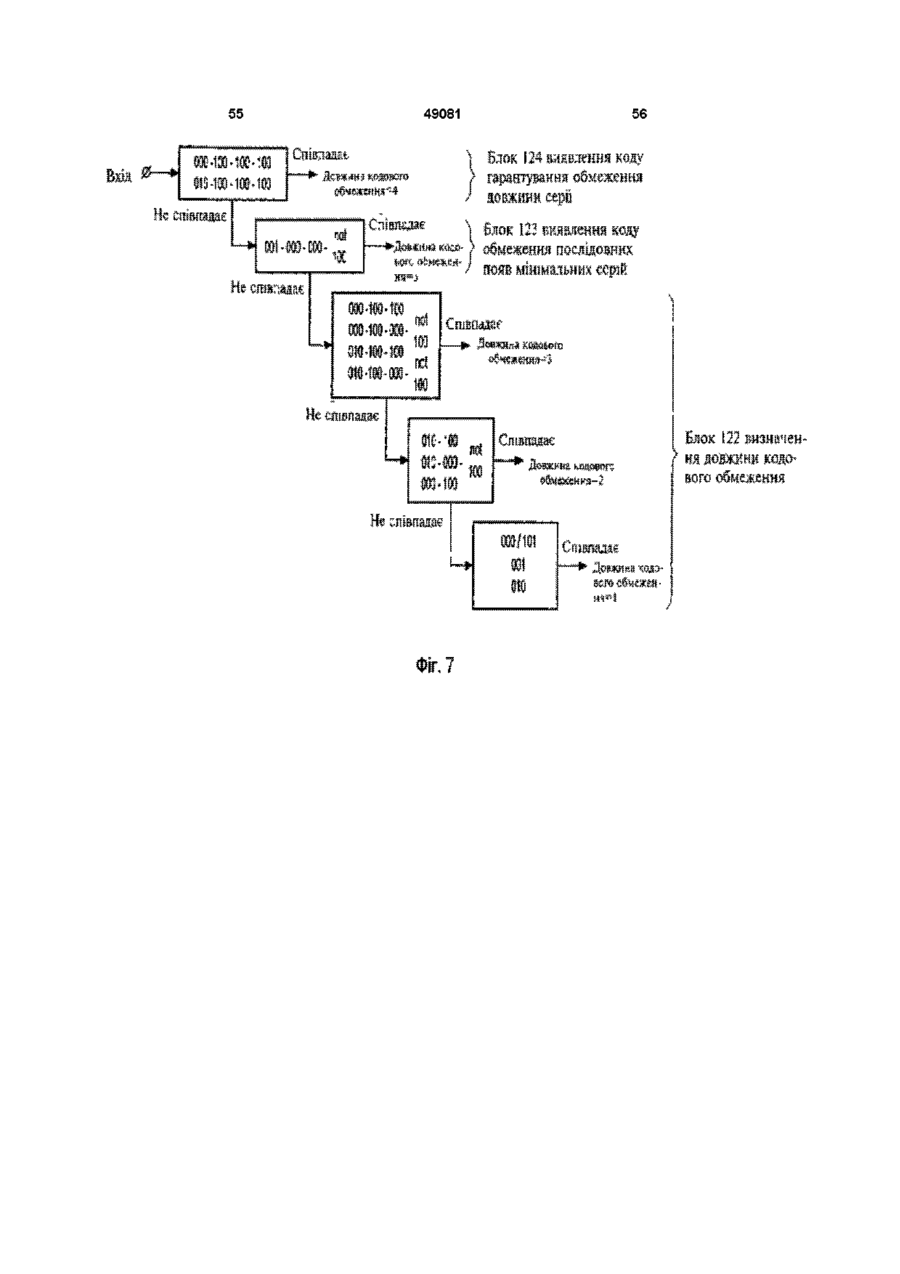

засіб виявлення кодів першої підстановки для виявлення вказаних кодів першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

засіб виявлення кодів другої підстановки для виявлення вказаних кодів другої підстановки для збереження обмеження довжини серії.

25. Спосіб модуляції для використання в пристрої модуляції для перетворення даних з довжиною основних даних m бітів в код змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів, де d - мінімальна серія і k - обмеження довжини серії, який відрізняється тим, що включає крок перетворення вхідних даних в код відповідно до таблиці перетворення, де вказана таблиця перетворення задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=l, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

26. Програмоносій для представлення програми, що реалізує обробку, що включає крок перетворення вхідних даних в код відповідно до даних таблиці перетворення в пристрої модуляції, для перетворення даних з довжиною основних даних m бітів в код змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів, де d - мінімальна серія і k - обмеження довжини серії, який відрізняється тим, що вказана таблиця перетворення задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=l, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

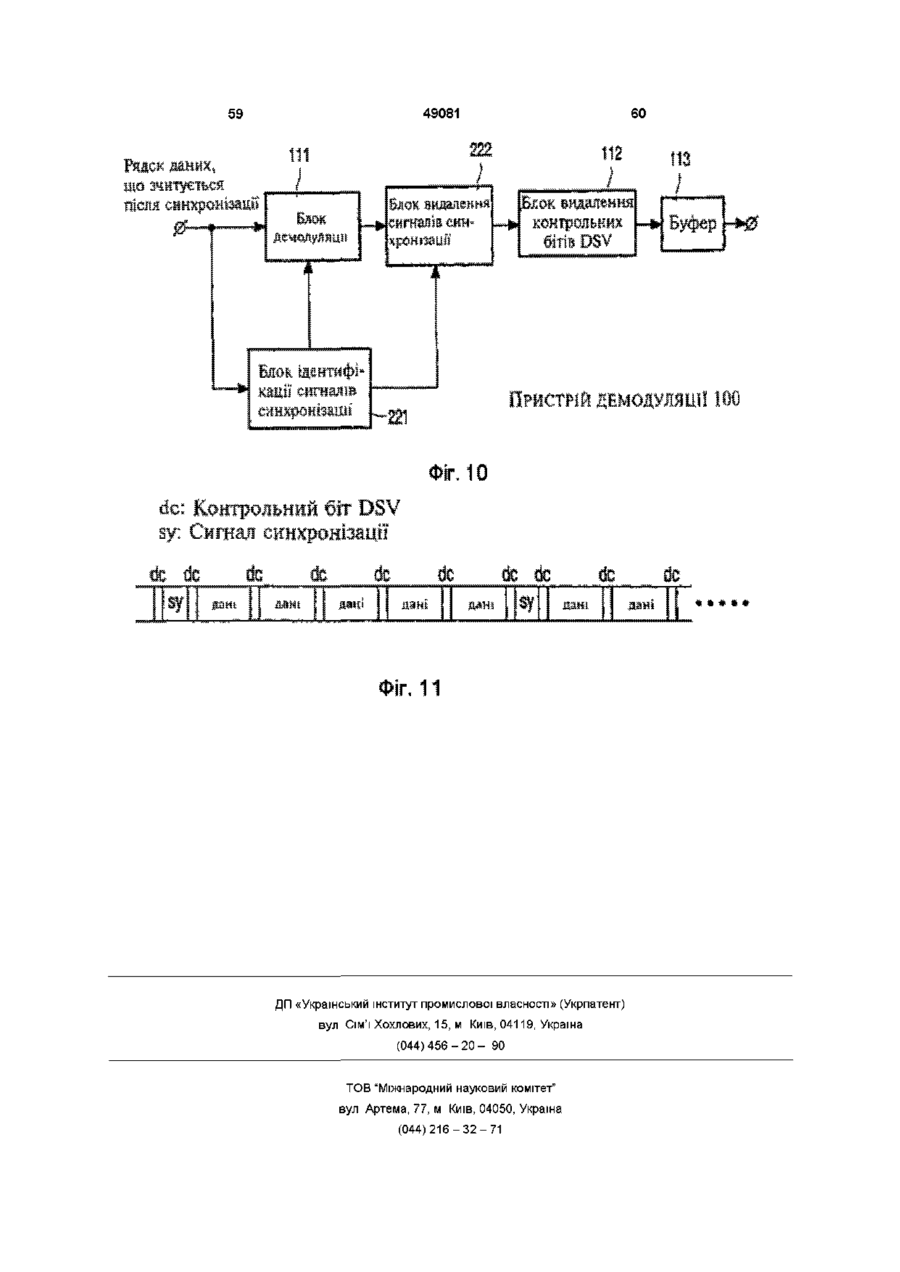

27. Пристрій демодуляції для перетворення коду змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів в дані з довжиною основних даних m бітів, де d - мінімальна серія і k - обмеження довжини серії, який відрізняється тим, що включає в себе засіб перетворення вхідного коду в дані відповідно до таблиці перетворення, де вказана таблиця задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=l, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

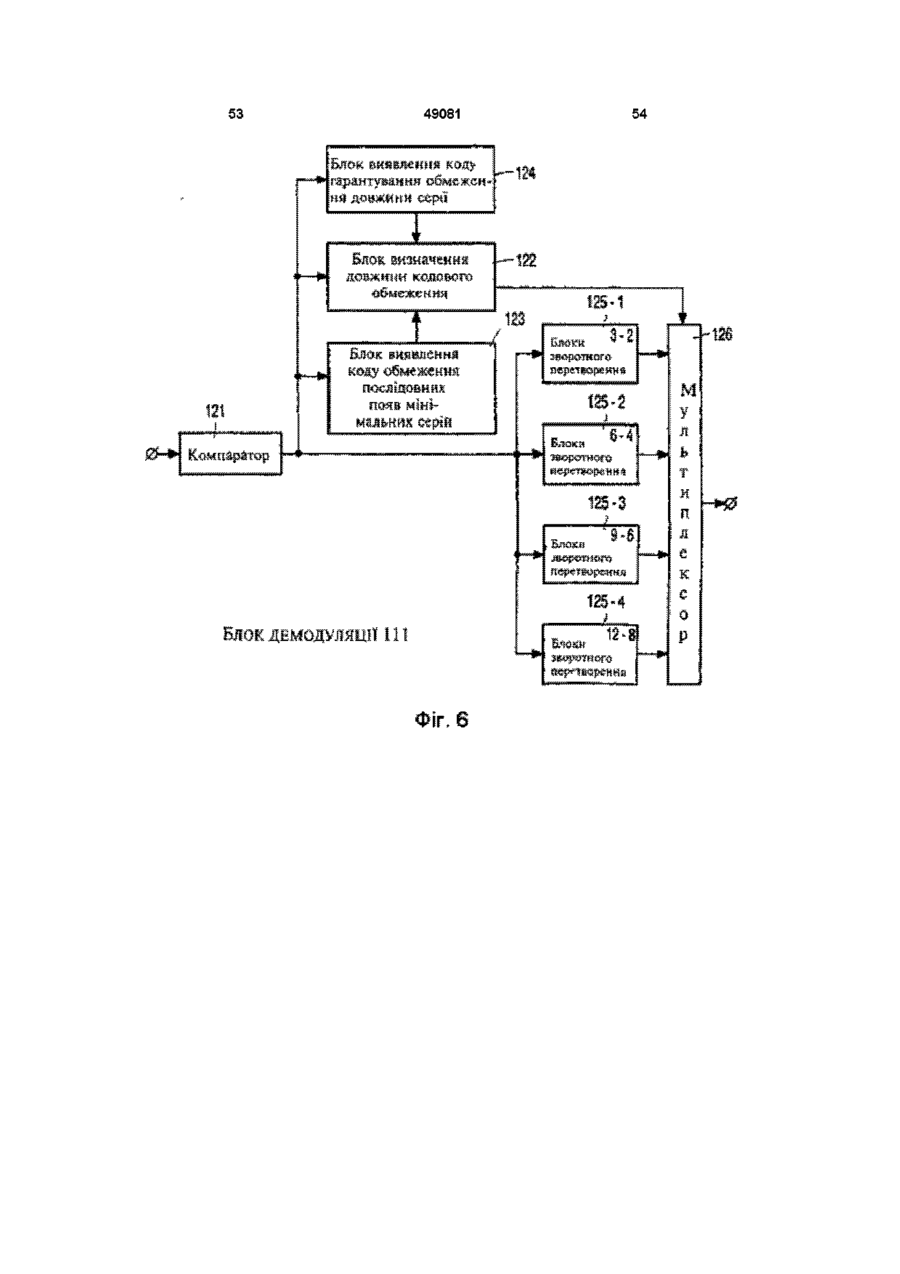

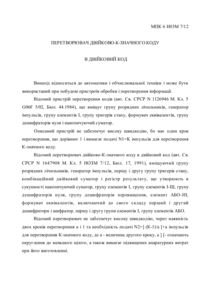

28. Пристрій демодуляції за п. 27, який відрізняється тим, що вказаний пристрій додатково має засіб видалення бітів для видалення надлишкових бітів, що вставляються через задані інтервали часу у вказаний код.

29. Пристрій демодуляції за п. 28, який відрізняється тим, що вказані надлишкові біти є бітами DSV або сигналами синхронізації.

30. Спосіб демодуляції для використання в пристрої демодуляції для перетворення коду змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів в дані з довжиною основних даних m бітів, де d - мінімальна серія і k - обмеження довжини серії, який відрізняється тим, що включає крок перетворення вхідного коду в дані відповідно до таблиці перетворення, де вказана таблиця перетворення задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=l, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

31. Програмоносій для представлення програми, що включає крок перетворення вхідного коду в дані відповідно до таблиці перетворення в пристрої демодуляції для перетворення коду змінної довжини (d, k; m, n; r) з довжиною основного коду n бітів в дані з довжиною основних даних m бітів, де d - мінімальна серія і k - обмеження довжини серії, який відрізняється тим, що вказана таблиця перетворення задає правило перетворення, згідно з яким залишок від ділення на 2 кількості "1" елемента рядка даних, що має значення 0 або 1, завжди повинен дорівнювати залишку від ділення на 2 кількості "1" елемента рядка кодових слів, що отримується внаслідок перетворення вказаного рядка даних, і коди перетворення вказаної таблиці включають:

основні коди для d=l, k=7, m=2 і n=3;

коди першої підстановки для обмеження кількості послідовних появ вказаної мінімальної серії d; і

коди другої підстановки для збереження вказаного обмеження довжини серії k.

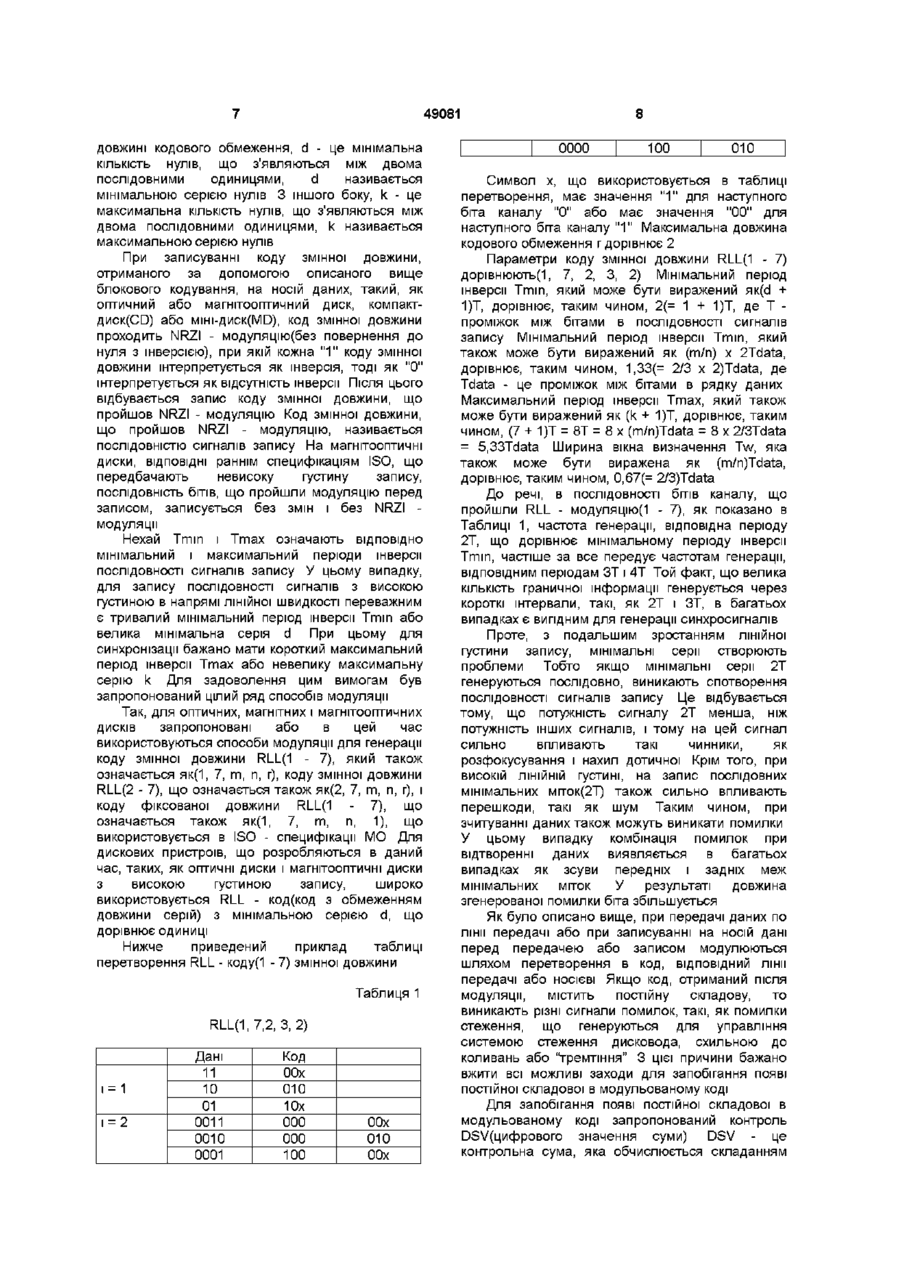

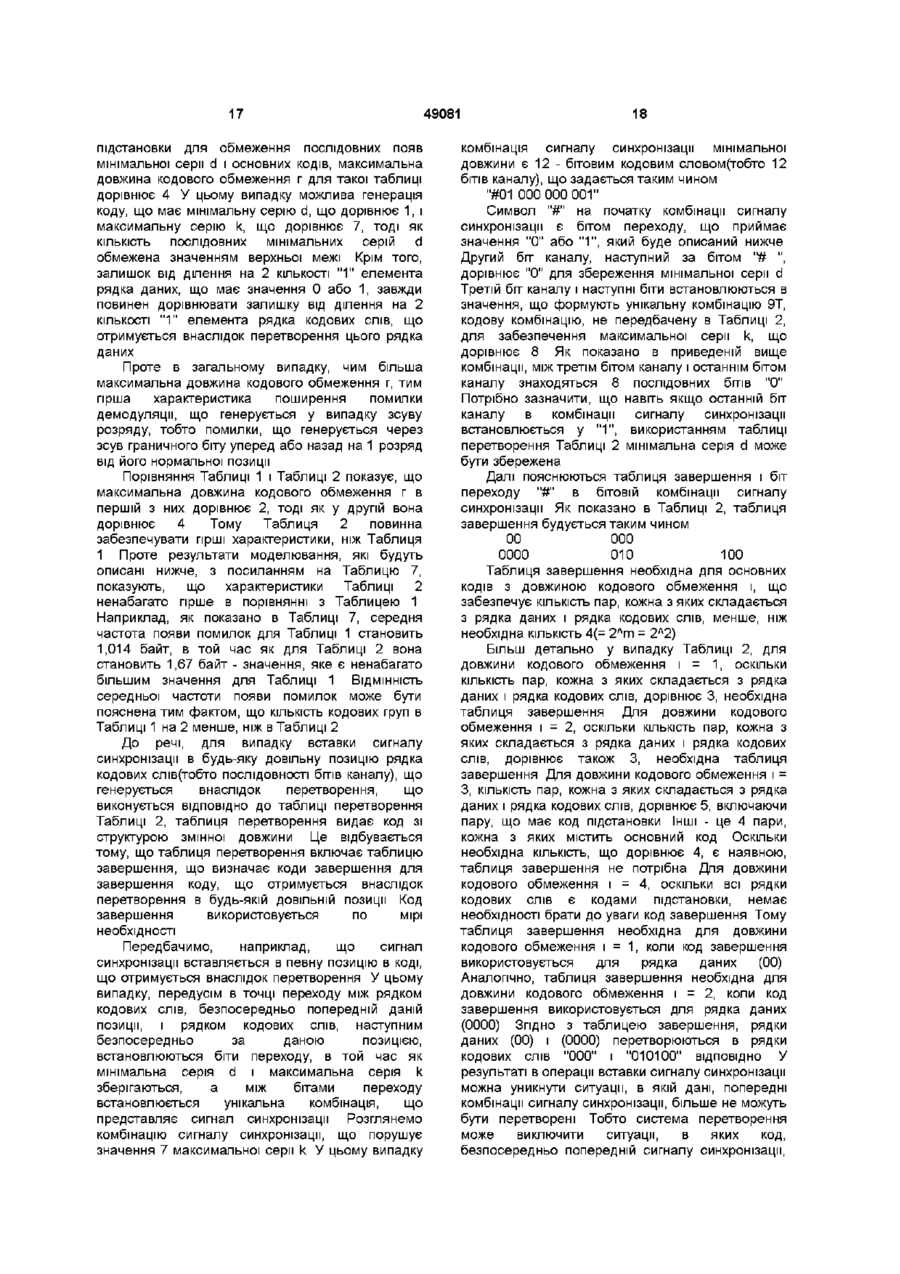

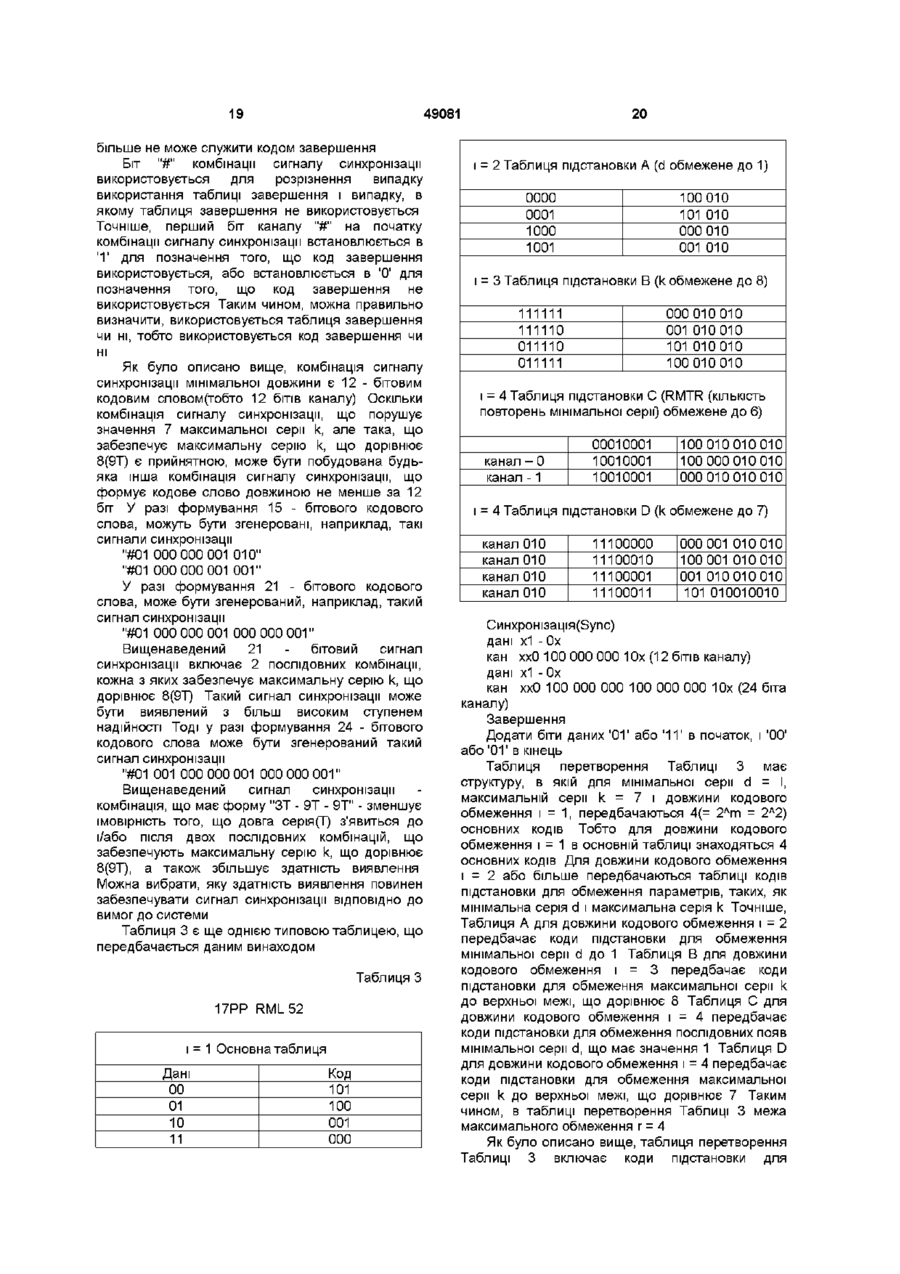

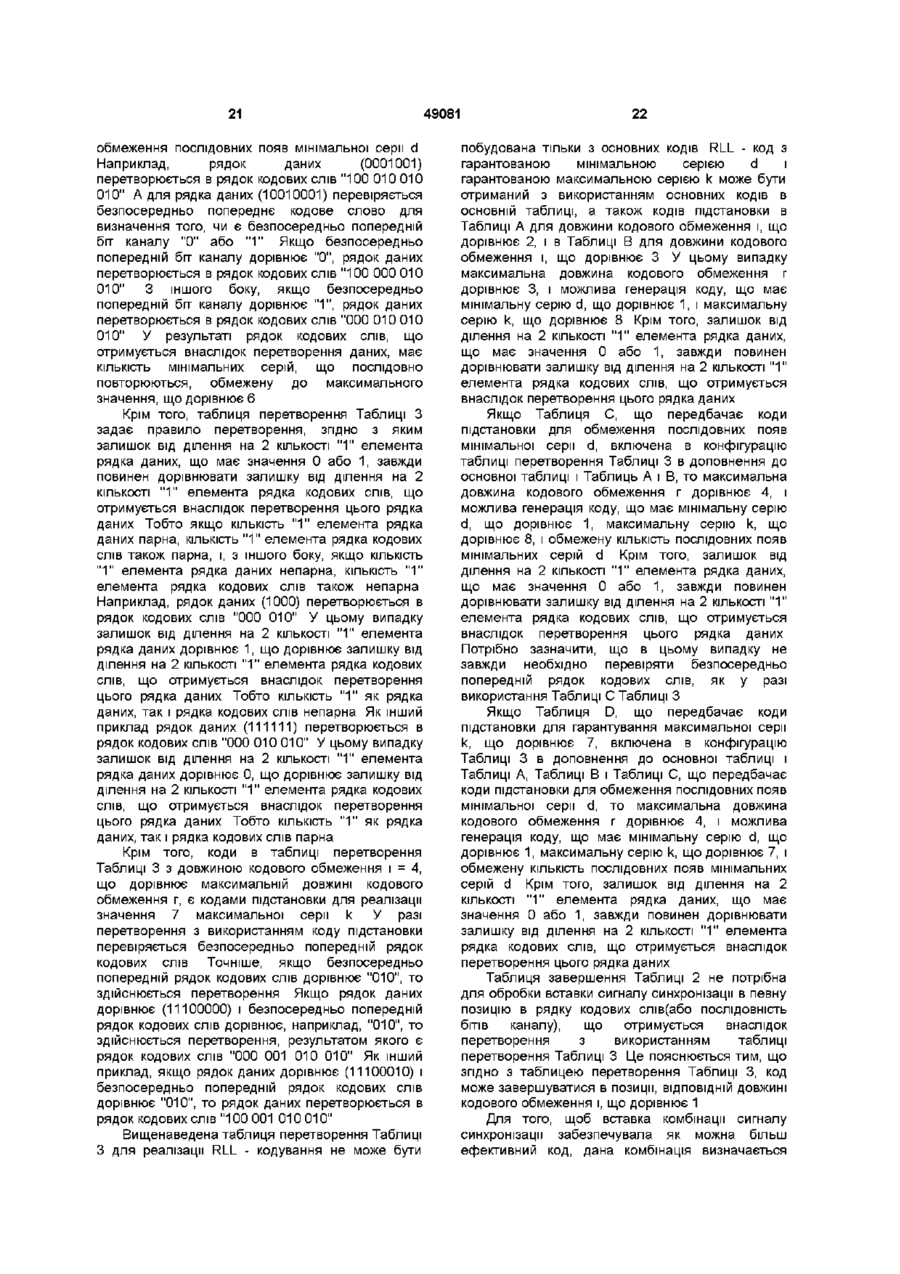

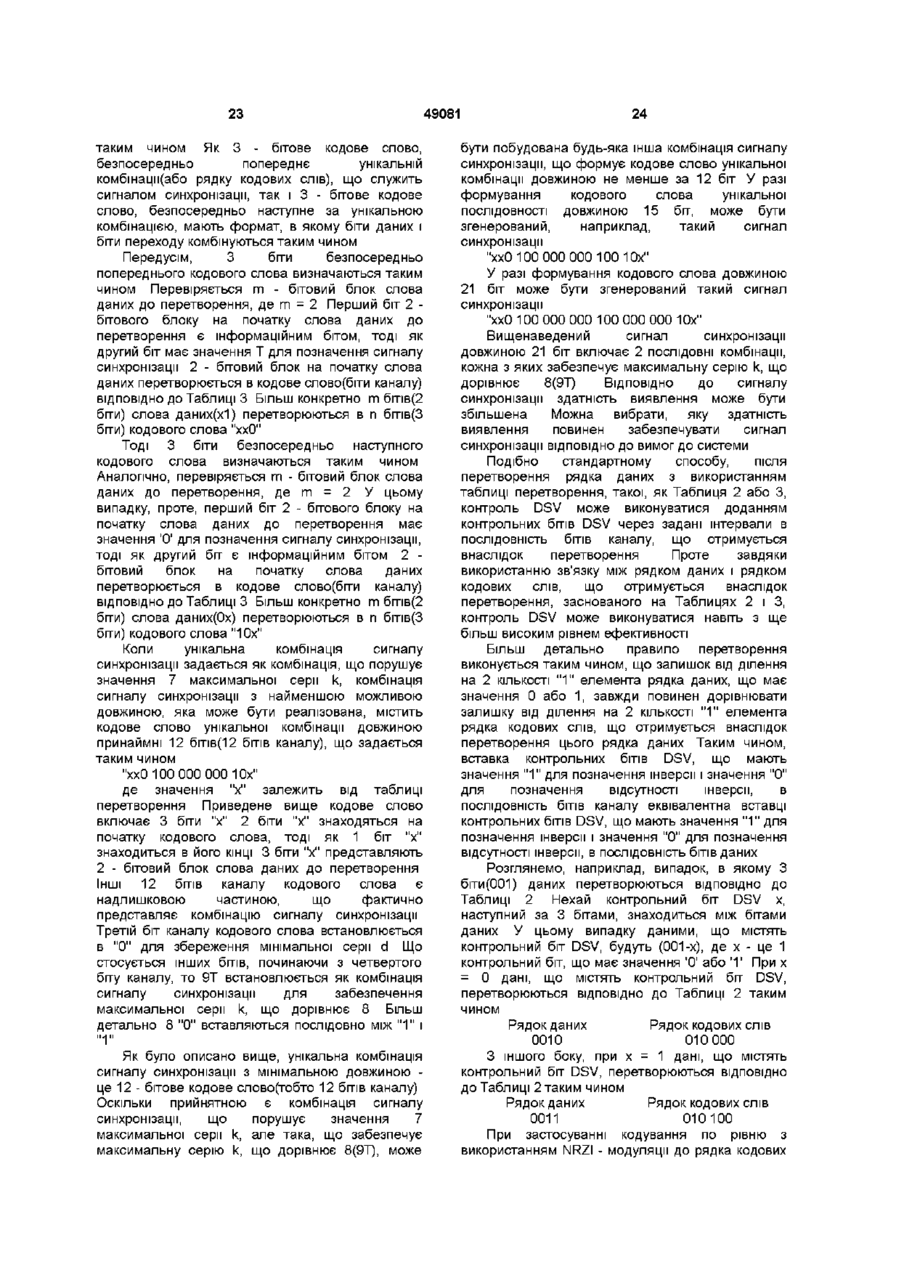

Текст