Цифровий пристрій для обчислення функцій

Номер патенту: 35014

Опубліковано: 15.03.2001

Автори: Лукашенко Валентина Максимівна, Лукашенко Андрій Германович, Ротте Сергій Вікторович, Гладченко Максим Ігорович

Формула / Реферат

Цифровий пристрій для обчислення функцій, що вміщує регістр, ланцюг диференціювання, адресну комбінаційну схему, числовий блок пам'яті, входи якого з'єднані з виходами адресної комбінаційної схеми, а виходи числового блоку пам'яті підключені до відповідних лічильних входів регістра, керуюча шина пристрою "Скид" підключена до перших керуючих входів регістру, шина "Запуск" е керуючою шиною пристрою, керуючий тригер, керуючий вхід якого підключений до шини "Скид", а лічильний - до шини "Запуск", інверсний вихід керуючого тригера підключений до керуючого входу адресної комбінаційної схеми, а прямий вихід тригера з'єднаний з другим керуючим входом регістру, який відрізняється тим, що з нього введені блок n МДП-ключів, входи яких підключені до відповідних входів адресної комбінаційної схеми та виходів регістру, а виходи відповідного МДП-ключа підключені до інформаційних входів регістру, керуючі входи відповідного МДП-ключа підключені до виходу відповідного ланцюга диференціювання, входи якого підключені до інверсного виходу керуючого тригера, кодові входи регістру є кодові входи/виходи пристрою.

Текст

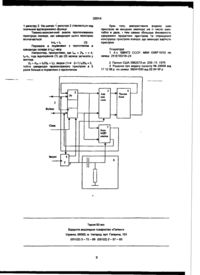

Цифровий пристрій для обчислення функцій, що вміщує регістр, ланцюг диференціювання, адресну комбінаційну схему, числовий блок пам'яті, входи якого з'єднані з виходами адресної комбінаційної схеми, а виходи числового блоку пам'яті підключені до відповідних лічильних входів регістра, керуюча шина пристрою "Скид" підключе Винахід відноситься до обчислювальної техніки і призначається для використання в інформаційних обчислювальних системах, дискретних перетворювачах координат, у системах з функціональними перетворювачами дискретної інформації- . Відомий пристрій, що вміщує блок пам'яті, регістр, адресну комбінаційну схему, блок керування, групу елементів Т , розподільний блок, блок комутаторів, групу елементів "АБО" [1J з їх відповідними зв'язками. Однак при збільшенні точності відтворення функції зменшується величина ступеню апроксимуючої функції, що збільшує число ділянок апроксимації, отже, зростає об'єм адресної частини і кількість комутаторів, це збільшує затрати обладнання, зменшує надійність і швидкодію. Відомий пристрій [2], що вміщує зміщуючий регістр, інформаційні входи якого з'єднані з інформаційними входами пристрою, адресну комбінаційну схему, інформаційні входи якої підключені до виходів зміщуючого регістру, блок пам'яті, входи якого з'єднані з виходами аресної комбінаційної схеми, керуюча шина пристрою "Скид" підключена до перших керуючих входів зміщуючого регістру і регістру, шина "Запуск" є керуючою шиною пристрою. на до перших керуючих входів регістру1 шина "Запуск" є керуючою шиною пристрою, керуючий тригер, керуючий вхід якого підключений до шини "Скид", а лічильний - до шини "Запуск", інверсний вихід керуючого тригера підключений до керуючого входу адресної комбінаційної схеми, а прямий вихід тригера з'єднаний з другим керуючим входом регістру відрізняється тим, що з нього введені блок п МДП- ключів, входи яких підключені до відповідних входів адресної комбінаційної схеми та виходів регістру, а виходи відповідного МДП-ключа підключені до інформаційних входів регістру, керуючі входи відповідного МДП-ключа підключені до виходу відповідного ланцюга диференціювання, входи якого підключені до інверсного виходу керуючого тригера, кодові входи регістру є кодові входи/виходи пристрою. кодія. Недоліком даного пристрою є низька швид Найбільш близьким до пропонованого по технічній суті є цифровий пристрій (3] для обчислення функцій, що вміщує регістр, ланцюг диференціювання, адресну комбінаційну схему, числовий блок пам'яті, входи якого з'єднані з виходами адресної комбінаційної схеми, а його виходи підключені до відповідних лічильних входів регістра, керуюча шина пристрою "Скид" підключена до перших керуючих входів регістру, шина "Запуск" є керуючою шиною пристрою, керуючий тригер, перший вхід якого підключений до шини "Скид", а другий - до шини "Запуск", інверсний вихід керуючого тригера підключений до керуючого входу адресної комбінаційної схеми, а прямий вихід тригера з'єднаний з другим керуючим входом регістру. Однак при збільшенні розрядів зростає число виходів пристрою, що зменшує швидкодію та ускладнює конструкцію пристрою. Дійсно, швидкодія цього пристрою визначається за формулою + tn (1) де t e - час вибору констант зміщення і коректуючих констант із ПЗП (постійно запам'ятовуючий пристрій); О ю є* х > х,+і) функція подається в такому вигляді F(x,) = х, Є д, (2) де х,- поточний аргумент функції, Д, - значення коректуючих констант, визначених як сума по mod 2 значення кодової ПОСЛІДОВ В основу винаходу пристрою поставлено задачу підвищення швидкодії та спрощення конструкції пристрою шляхом запропонування рішення для усіх ознак, які вказані у відрізняючій частині формули винаходу, і виявляють в процесі взаємодії характерні їм ВІДОМІ властивості що дають кожен із них окремо відомий позитивний ефект При цьому забезпечується надпщсумковий позитивний ефект зумовлений сукупністю вказаних ознак який визначається в тім, що скорочення часу відтворення функцій за рахунок схемотехнічного вирішення у вигляді паралельного зчитування констант формування імпульсів керування по передньому і задньому фронтах одного й того ж імпульсу застосування незалежного від розрядності операндів підсумовування Це дозволяє підвищити швидкодію, зумовлену порозрядним підсумовуванням (сума по mod 2) вхідного коду аргументу і відповідної коректуючої константи, причому значення коректуючої константи визначається як сума по mod 2 значення аргументу і значення відповідної функції Крім того введення блоку п МДП-ключів забезпечує використовування вхідних шин, також для зняття інформації вихідної, що зменшує число інформаційних виходів пристрою на п. та спрощує конструкцію пристрою Таким чином, пропоноване рішення задовільняє критерію "суттєві ВІДМІННОСТІ" , Ьг, bi.bo та значення вхідної незалежної змінної (х) як змінних Эт-i, , а,, , аг, аі, ао. ТОДІ обчислення значення відповідної коректуючої константи Д, зображається як сума по mod 2 залежної змінно» та незалежної змінної (bo Ф ао) = До, (Ьі Ф аі) = Ді, (Ьг © аг) = Аг, (Ь, Ф а,) = Д,, (bm Ф аш) = Дт, відповідне значення функції дорівнює (2) На фігурі зображена структурна схема пристрою Пристрій містить інформаційний "ВХІД/ВИХІД" 1, регістр 2, адресну комбінаційну схему 3, блок пам'яті 4, керуючий тригер 5 ланцюг диференціювання 6, блок п МДП-ключів 7 НОСТІ ВХІДНОГО аргументу і ВІДПОВІДНОГО йому зна чення кодової ПОСЛІДОВНОСТІ функції Наприклад, зобразимо п-значне ВІДТВОрЮВаНОЇ ФУНКЦІЇ F,(x) ЯК ЗМІННИХ Ьт-1, число , Ьі, Цифровий пристрій для обчислення функцій працює таким чином Перед перетворенням вхідної інформації, яка поступає на "ВХІД/ВИХІД" 1, по входу "Скид" пристрою імпульс встановлює у вихідний стан регістр 2 та керуючий тригер 5 Імпульс "Запуск" надходить на лічильний вхід тригера 5 і встановлює на виході регістра 2 вхідну кодову ПОСЛІДОВНІСТЬ аргументу Оскільки ДОЗВОЛЯЮЧИЙ ВХІД адрес ної комбінаційної схеми 3 відкривається інверсним виходом тригера 5, то під його дією та коду аргументу на виході схеми 3 сформується імпульс, який надходить на ВІДПОВІДНИЙ ВХІД ЧИСЛОВОГО бло ку пам'яті 4, під дією якого з виходів блока пам'яті 4 зчитується код коректуючої константи, який надходить на ВІДПОВІДНІ ЛІЧИЛЬНІ входи регістру 2 Під дією одиниць коду константи відбувається переключення ВІДПОВІДНОГО тригера в регістрі 2 на протилежне, тобто відбувається підсумовування no mod 2 коду аргументу та коду коректуючої константи Під ДІЄЮ імпульсу дозволу сформованого ланцюгом диференціювання 6, який надходить на керуючі входи ВІДПОВІДНОГО МДП-ключа з виходу ВІДПОВІДНОГО ланцюга диференціювання 6, інформація про значення функції для ВІДПОВІДНОГО значення аргументу надходить на "входи/виходи" 35014 1 регістру 2 На шинах 1 регістра 2 з'являється код значення відтворюваної функції Техніко-економічний аналіз пропонованого пристрою показує, що швидкодія цього пристрою визначається t=tB + t n (3) Перевага в порівнянні з прототипом в швидкодії складе (r t3M) часу Наприклад, припустимо, що t ) M - 2tB. r = 4, t B =t n , тоді відношення (1) до (3) можна записати у вигляді (U + П3м + tn)/(tB + t n ), ЗВІДСИ (1 +4 2+1) te/2te = 5, тобто швидкодія пропонованого пристрою в 5 разів більша в порівнянні з прототипом Література 1 А с 696472 СССР, МКИ G06F15/32 по заявці 2516193/18-24 2 Патент США 3962573 кл 235-15 1976 3 Рішення про видачу патенту № 29808 від 17 12 98 р по заявці 98041690 від 02 04 98 р _ Алр 2 ._,.. і І Крім того, використання вхідних шин пристрою як вихідних зменшує на п число шин. тобто в двоє, і тим самим збільшує ймовірність одержання придатних пристроїв та спрощення конструкції пристрою взагалі, що зменшує вартість пристрою і» Рг • 4 3 Числов блок ком схем 1 Вх/вих • Ь —_-• І І —• t Скид 7 _____ Блок МДП КЛЮЧІВ — і і 1 Запуск 6 * Т J 1 ± I Тираж 50 екз Відкрите акціонерне товариство «Патент» Україна, 88000, м Ужгород, вул Гагаріна, 101 (03122)3-72-89 (03122)2-57-03

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital device for calculation of functions

Автори англійськоюLukashenko Valentyna Maksymivna, Rotte Serhiy Viktorovych, Hladchenko Maksym Ihorovych, Lukashenko Andrii Hermanovych

Назва патенту російськоюЦифровое устройство для вычисления функций

Автори російськоюЛукашенко Валентина Максимовна, Ротте Сергей Викторович, Гладченко Максим Игоревич, Лукашенко Андрей Германович

МПК / Мітки

МПК: G06F 7/52, G06G 7/26, G06F 7/544, G06F 7/50, G06F 15/00

Мітки: цифровий, обчислення, функцій, пристрій

Код посилання

<a href="https://ua.patents.su/4-35014-cifrovijj-pristrijj-dlya-obchislennya-funkcijj.html" target="_blank" rel="follow" title="База патентів України">Цифровий пристрій для обчислення функцій</a>

Попередній патент: Електромагнітний привод вакуумного вимикача

Наступний патент: Пристрій для ділення або множення n-розрядних чисел

Випадковий патент: Спосіб вшивання ложа передміхурової залози