Пристрій для обчислення елементарних функцій

Формула / Реферат

Пристрій для обчислення елементарних функцій, який містить регістр аргументу, регістр квадранта, блок пам'яті функцій, дешифратор функцій, дешифратор адреси, блок синхронізації, блок пам'яті значень, першу, другу групи елементів І, першу групу елементів АБО, третю групу елементів І, другу групу елементів АБО, четверту групу елементів І, третю групу елементів АБО, комутатор, причому інформаційні входи блока пам'яті функцій і регістра квадранта поєднані з входом завдання виду функції пристрою, вихід блока пам'яті функцій поєднаний з першим інформаційним входом дешифратора функцій, другий інформаційний вхід якого з'єднаний з виходом регістра квадранта, другий вихід дешифратора функцій з'єднаний зі знаковим входом регістра аргументу, виходи якого з'єднані з першими входами першої та другої групи елементів І, а виходи елементів І першої групи з'єднані з інформаційними входами дешифратора адреси, виходи якого з'єднані з входами елементів АБО першої групи, виходи яких з'єднані з першими входами елементів І третьої групи, другі входи яких з'єднані з першим виходом дешифратора функцій, виходи елементів І третьої групи з'єднані з входами елементів АБО другої групи, виходи яких з'єднані з першими входами елементів І четвертої групи, а виходи елементів І четвертої групи з'єднані з входом блока пам'яті значень і входами елементів АБО третьої групи, виходи яких з'єднані з керуючим входом комутатора, інформаційні входи якого з'єднані відповідно з виходами блока пам'яті значень, а виходи комутатора з'єднані з лічильними входами регістра аргументу, причому відповідні виходи блока синхронізації з'єднані з відповідними другими входами елементів І першої групи, другої групи та другими входами елементів І четвертої групи, а також - з відповідними керуючими входами блока пам'яті функцій, регістра квадранта, регістра аргументу, керуючими входами дозволу дешифратора функції та дешифратора адреси, який відрізняється тим, що в нього додатково введено блок МДП-ключів, керуючий вхід якого з'єднаний з відповідним керуючим виходом блока синхронізації, а інформаційні входи блока МДП-ключів з'єднані з відповідними виходами групи елементів І, виходи МДП-ключів з'єднані з відповідними входами регістра аргументу, які є входом/виходом пристрою.

Текст

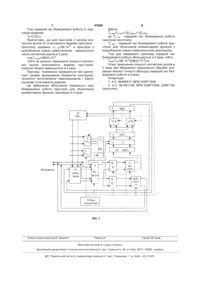

Пристрій для обчислення елементарних функцій, який містить регістр аргументу, регістр квадранта, блок пам'яті функцій, дешифратор функцій, дешифратор адреси, блок синхронізації, блок пам'яті значень, першу, другу групи елементів І, першу групу елементів АБО, третю групу елементів І, другу групу елементів АБО, четверту групу елементів І, третю групу елементів АБО, комутатор, причому інформаційні входи блока пам'яті функцій і регістра квадранта поєднані з входом завдання виду функції пристрою, вихід блока пам'яті функцій поєднаний з першим інформаційним входом дешифратора функцій, другий інформаційний вхід якого з'єднаний з виходом регістра квадранта, другий вихід дешифратора функцій з'єднаний зі знаковим входом регістра аргументу, виходи якого з'єднані з першими входами першої та другої групи елементів І, а виходи елементів І першої групи з'єднані з інформаційними входами дешифратора адреси, виходи якого з'єднані з входами елементів АБО першої групи, виходи яких з'єднані з першими U 2 (19) 1 3 47009 4 Крім того, перетворювач функцій містить реінформаційні входи блока пам'яті функцій 3 і регісгістр входу, чотири блоки пам'яті, кожний з яких тра квадранта поєднані з входом завдання виду складається з дешифратора адреси й числового функції пристрою, вихід блока пам'яті функцій поблоку пам'яті та суматора, причому входи регістра єднаний з першим інформаційним входом дешифвходу є входами перетворювача функції, а відпоратора функцій, другий інформаційний вхід якого відні виходи регістра входу підключені до відповіз'єднаний з виходом регістра квадранта, другий дних входів дешифраторів адреси, виходи яких вихід дешифратора функцій з'єднаний зі знаковим з'єднані з відповідними входами числових блоків входом регістра аргументу, виходи якого з'єднані з пам'яті, виходи яких підключені до відповідних першими входами першої та другої групами елевходів суматора, виходи якого с виходами перетментів І, а виходи елементів І першої групи з'єднаворювача функції [1]. ні з інформаційними входами дешифратора адреНедоліком пристрою є більша потужність споси, виходи якого з'єднані з входами елементів АБО живання і низькі швидкодія та надійність. першої групи, виходи яких з'єднані з першими вхоНайбільш близьким по технічній сутності до дами елементів І третьої групи, другі входи яких пропонованого є пристрій [2] для обчислення елез'єднані з першим виходом дешифратора функцій, ментарних функцій, що містить регістр аргументу, виходи елементів І третьої групи з'єднані з входарегістр квадранта, блок пам'яті функцій, дешифрами елементів АБО другої групи, виходи яких з'єдтор функцій, дешифратор адреси, блок синхронінані з першими входами елементів І четвертої зації та блок пам'яті значень, причому інформаційгрупи, а виходи елементів І четвертої групи з'єдні входи блока пам'яті функцій і регістра квадранта нані з входом блока пам'яті значень і входами поєднані з відповідними входами завдання приелементів АБО третьої групи, виходи яких з'єднані строю, вхід завдання аргументу якого з'єднаний з з керуючим входом комутатора, інформаційні вхоінформаційним входом регістра аргументу, вихід ди якого з'єднані відповідно з виходами блока паблока пам'яті функцій поєднаний з першим інформ'яті значень, а виходи комутатора з'єднані з лічимаційним входом дешифратора функцій, другий льними входами регістра аргументу, причому інформаційний вхід якого з'єднаний з виходом ревідповідні виході блоку синхронізації з'єднані з гістра квадранта, керуючі входи блока пам'яті фунвідповідними другими входами елементів І першої кцій, регістра квадранта, регістра аргументу і вхогрупи, другої групи та другими входами елементів І ди дозволу видачі дешифратора функції та четвертої групи, а також - з відповідними керуюдешифратора адреси з'єднані з першим входом чими входами блока пам'яті функцій, регістра кваблока синхронізації, чотири групи елементів І, три дранта, регістра аргументу, керуючими входами групи елементів АБО та комутатор, причому вихід дозволу дешифратора функції та дешифратора регістра аргументу з'єднаний з першими входами адреси, додатково введено блок МДП-ключів, кеелементів І першої та другої груп, другі входи та руючий вхід якого з'єднаний з відповідним керуювиходи елементів І першої групи з'єднані відповідчим виходом блоку синхронізації, а інформаційні но з першим виходом блока синхронізації та інфовходи блоку МДП-ключів з'єднані з відповідними рмаційним входом дешифратора адреси, вихід виходами групи елементів І, крім того, виходи якого з'єднаний з входами елементів АБО першої МДП-ключів з'єднані з відповідними входами регісгрупи, виходи яких з'єднані з першими входами тра аргументу, які є входом/виходом пристрою. елементів І третьої групи, другі входи яких з'єднані В основу корисної моделі поставлено задачу з першим виходом дешифратора функцій, виходи підвищення надійності, шляхом запропонування елементів І третьої групи з'єднані з входами елесхемотехнічного рішення у вигляді додатково ввементів АБО другої групи, виходи яких з'єднані з деного блоку МДП-ключів, керуючий вхід МДПпершими входами елементів І четвертої групи, ключів з'єднаний з відповідним керуючим виходом другі входи яких з'єднані з другим виходом блока блоку синхронізації, інформаційні входи з'єднані з синхронізації, виходи елементів І четвертої групи відповідними виходами другої групи елементів І, а з'єднані з входом блока пам'яті значень і входами виходи МДП-ключів з'єднані з відповідними входаелементів АБО третьої групи, виходи яких з'єднані ми регістра аргументу 1, які є входом/виходом з керуючим входом комутатора, інформаційні вхопристрою. ди та виходи якого з'єднані відповідно з виходами Отже забезпечується надпідсумковий позитиблока пам'яті значень та входами запису регістра вний ефект, зумовлений сукупністю вказаних аргументу, вхід знака якого з'єднаний з другим ознак. виходом дешифратора функцій, третій вихід блока На фігурі (Фіг.1) представлена структурна синхронізації з'єднаний з другими входами елемесхема пристрою. нтів I другої групи. Пристрій для обчислення елементарних функНедоліком пристрою є мала надійність. цій містить регістр аргументу 1, регістр квадранта Мета корисної моделі - підвищення надійності. 2, блок пам'яті функцій 3, дешифратор функцій 4, Зазначена мета досягається тим, що у придешифратор адреси 5, блок синхронізації 6, блок стрій для обчислення елементарних функцій, що пам'яті значень 7, першу 8, другу 9 групи елеменмістить регістр аргументу, регістр квадранта, блок тів І, першу 10 групу елементів АБО, третю 11 групам'яті функцій, дешифратор функцій, дешифрапу елементів І, другу 12 групу елементів АБО, четтор адреси, блок синхронізації, блок пам'яті знаверту 13 групи елементів І, третю 14 групу чень, першу, другу групи елементів І, першу групу елементів АБО, комутатор 15, блок МДП-ключів елементів АБО, третю групу елементів І, другу 16. групу елементів АБО, четверту групи елементів І, Пристрій для обчислення елементарних функтретю групу елементів АБО, комутатор, причому цій, що містить регістр аргументу 1, регістр квад 5 47009 6 ранта 2, блок пам'яті функцій 3, дешифратор фунний знаку в квадранті відтворюваної функції, з'явкцій 4, дешифратор адреси 5, блок синхронізації 6, ляється на другому виході дешифратора 4 та заблок пам'яті значень 7, першу 8, другу 9 групи писується в знакову комірку регістра 1. елементів І, першу 10 групу елементів АБО, третю При надходженні сигналу з виходу дешифра11 групу елементів І, другу 12 групу елементів тора 4 на відповідні входи першої групи 11 елемеАБО, четверту 13 групи елементів 1, третю 14 грунтів І, вихідна інформація про вибір відповідних пу елементів АБО, комутатор 15, причому інфорелементів І четвертої групи 13 проходить через маційні входи блока пам'яті функцій 3 і регістра другу групу 12 елементів АБО та надходить на квадранта 2 поєднані з входом завдання виду фувідповідні входи четвертої групи 13 елементів І, нкції пристрою, вихід блока пам'яті функцій 3 позавдяки керуючому імпульсу, що поступає з блока єднаний з першим інформаційним входом дешифсинхронізації 6, на виходах четвертої групи 13 ратора функцій 4, другий інформаційний вхід якого елементів І з'явіться сигнал, який надходить на з'єднаний з виходом регістра квадранта 2, другий відповідні входи блоку пам'яті значень 7 та через вихід дешифратора функцій 4 з'єднаний зі знакотретю групу 14 елементів АБО надходить на керувим входом регістра аргументу 1, виходи якого ючі входи комутатора 15, при цьому на його інфоз'єднані з першими входами першої 8 та другої 9 рмаційні входи надходять сигнали з виходів блоку групами елементів І, а виходи елементів І першої пам'яті значень 7, в якому зберігаються константи групи 8 з'єднані з інформаційними входами дешидля відповідних аргументу та функції. Вихідні сигфратора адреси 5, виходи якого з'єднані з входанали комутатора 15 надходять на лічильні входи ми елементів АБО першої групи 10, виходи яких регістра 1 аргументу. з'єднані з першими входами елементів І третьої В регістрі 1 встановилося значення відповідної групи 11, другівходи яких з'єднані з першим вихофункції для відповідного вхідного аргументу. По дом дешифратора функцій 4, виходи елементів І імпульсу дозволу з блоку синхронізації 6, який натретьої групи 11 з'єднані з входами елементів АБО дійшов на керуючі входи другої групи 9 елементів другої групи 12, виходи яких з'єднані з першими І, на виходах з'являється код значення функції, входами елементів І четвертої групи 13, а виходи який через блок МДП-ключів 16, під дією керуючоелементів І четвертої групи 13 з'єднані з входом го імпульсу з блоку синхронізації 6, надходить на блока пам'яті значень 7 і входами елементів АБО входи/виходи пристрою. третьої групи 14, виходи яких з'єднані з керуючим Надійність пристроїв, які створюються у вивходом комутатора 15, інформаційні входи якого гляді інтегральних мікросхем, підвищується тому, з'єднані відповідно з виходами блока пам'яті знащо інтенсивність відмов X контактних вузлів всечень 7, а виходи комутатора 15 з'єднані з лічильредині схеми на три, ..., чотири порядки менші в ними входами регістра аргументу 1, причому відпорівнянні з формуванням зовнішніх контактних повідні виходи блоку синхронізації 6 з'єднані з вузлів. відповідними другими входами елементів І першої Відомо, що основними причинами відмови групи 8, другої групи 9 та другими входами елемеприладів при зборці кристалів в корпус та устанонтів І четвертої групи 13, а також - з відповідними вці на друковану плату є недостатня механічна керуючими входами блока пам'яті функцій 3, регісміцність контактів, мала адгезія виводів до контактра квадранта 2, регістра аргументу 1, керуючими тної площадки і останньої до підложи, деградації входами дозволу дешифратора функції 4 та деконтактного опору через взаємну дифузію металів шифратора адреси 5, додатково введено блок з утворенням інтерметалевих фаз і пустот, або МДП-ключів 16, керуючий вхід якого з'єднаний з прихованого технологічного дефекту. відповідним керуючим виходом блоку синхронізаПід контактним вузлом приймається система: ції 6, а інформаційні входи блоку МДП-ключів 16 струмоведуча площина металізації - термокомпрез'єднані з відповідними виходами групи 9 елеменсія - провідник - контактний вивід корпусу - міжз'єтів І, крім того, виходи МДП-ключів 16 з'єднані з днання до струмоведучої площадки друкованої відповідними входами регістра аргументу 1, які є плати. входом/виходом пристрою. Припустимо, інтенсивність відмов кожного конПристрій працює наступним чином. тактного вузла при операціях: Після обнуління регістрів пристрою, вхідні ко- термокомпресія провідника до металізованої ди аргументу, квадранта та функції записуються площадки дорівнює -6 відповідно в регістр аргументу 1, в регістр квадра1=10 , нта 2, в блок пам'яті функції 3, за допомогою ке- термокомпресія провідника до контакту плоруючих імпульсів, що поступають з відповідних щини корпусу дорівнює -6 виходів блока синхронізації 6. 2=10 , Код аргументу з виходу регістра 1 через першу - контакт виводів корпусу 1С до друкованої групу 8 елементів 1 надходить на входи дешифраплати дорівнює -6 тора 5 адреси, по відповідному імпульсу з виходу 3=10 . блока синхронізації 6 дешифрується і сигнал проТоді загальна інтенсивність відмови одного ходить через першу групу 10 елементів АБО на контактного вузла дорівнює -6 -6 -6 -6 входи першої групи 11 елементів І, на відповідні 3= 1+ 2+ 3=10 +10 +10 =3∙10 . керуючі входи яких надходить імпульс з відповідНаприклад, у пристроях при паралельної обних перших виходів дешифратора функцій 4, після робці інформаційних операндів з розрядністю 32 того як на його входах по імпульсу з блока синхрозагальна інтенсивність відмов контактних вузлів нізації 6 подається код функції, що з'являється з дорівнює виходу блока пам'яті функцій 3, сигнал, відповід32∙ 3=32∙3∙10-6=96∙10-6. 7 47009 8 Тоді середній час безвідмовної роботи Тр приДійсно строю дорівнює Тр вин/Тр пр=(1/∑ і)вин/(1/∑ і)пр, Тр=(1/∑ і). де Тр пр - середній час безвідмовної роботи Припустимо, що для пристроїв з числом конпристрою-прототипу; тактних вузлів 32 інтенсивність відмови пристрою Тр вин - середній час безвідмовної роботи пристрою для обчислення елементарних функцій з прототипу дорівнює 3 пр=96∙10-6, а пристрою з розробленою новою схемотехнічною реалізацією. розробленою новою схемотехнікою - зменшується Тоді для наведеного прикладу середній час число контактних вузлів в 2 рази, -6 безвідмовної роботи збільшується в 2 рази, тобто тоді з вин=(96/2)∙10 , Твин/Тпр=96∙10-6/[(96/2)∙10-6]=2. тобто за рахунок зменшення кількості контактОтже, зменшення кількості контактних вузлів в них вузлів інтенсивність відмови при-строю2 рази при збереженні паралельної обробки опекорисної моделі зменшується в 2 рази. рандів високої точності збільшує середній час безПричому, порівняння проводиться при ідентивідмовної роботи в 2 рази. чних умовах формування елементів конструкції, Література технології виготовлення перетворювачів і мають 1. А.С. №492517, МПК G06F7/548. однакову інтенсивність відмови. 2. А.С. №1061136, МПК G06F7/548, G06F1/02 Це забезпечує збільшення середнього часу (прототип). безвідмовної роботи пристрою для обчислення елементарних функцій, відповідно в 2 рази. Комп’ютерна верстка М. Мацело Підписне Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for calculation of elementary functions

Автори англійськоюLukashenko Andrii Hermanovych

Назва патенту російськоюУстройство для вычисления элементарных функций

Автори російськоюЛукашенко Андрей Германович

МПК / Мітки

МПК: G06F 1/02, G06F 7/548

Мітки: елементарних, обчислення, функцій, пристрій

Код посилання

<a href="https://ua.patents.su/4-47009-pristrijj-dlya-obchislennya-elementarnikh-funkcijj.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обчислення елементарних функцій</a>

Попередній патент: Спосіб протезування молочних залоз

Наступний патент: Штучна мінералізована питна вода

Випадковий патент: Спосіб одержання однотипного волокна з лубоволокнистих культур і пристрій для його здійснення