Перетворювач двійково-к-значного коду в двійковий код

Номер патенту: 50287

Опубліковано: 15.10.2002

Автори: Макаренко Ганна Миколаївна, Штець Леонід Констянтинович, Лопухін Юрій Володимирович, Какурін Микола Яковлевич, Лопухін Ярослав Юрійович

Формула / Реферат

Перетворювач двійково-К-значного коду в двійковий код, який складається з групи n розрядних регістрів зсуву, де n - розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, з генератора імпульсів, з групи n тригерів стану, з накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з відповідними другими входами комбінаційного двійкового суматора, виходи якого з'єднані з відповідними входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами відповідних тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, з багатоканального формувача еквівалентів, кожний канал якого складається з шифратора, входи якого з'єднані з прямими виходами відповідних тригерів стану, з першого, другого і третього комбінаційних суматорів першого і другого ступеня, виходи першого і другого комбінаційних суматорів першого ступеня з'єднані з відповідними входами першого і другого доданку третього комбінаційного суматора другого ступеня, з підсумовувального лічильника імпульсів і комбінаційного зсувача, керуючі входи якого з'єднані з виходами лічильника імпульсів, підсумовувальний вхід якого з'єднано з прямим виходом генератора імпульсів, який відрізняється тим, що входи першого і другого доданку комбінаційних суматорів першого ступеня з'єднані з відповідними виходами шифраторів сусідніх каналів та виходи третього комбінаційного суматора другого ступеня з'єднані з відповідними входами комбінаційного зсувача, виходи якого з'єднані з відповідними першими входами комбінаційного двійкового суматора в накопичувальному суматорі.

Текст

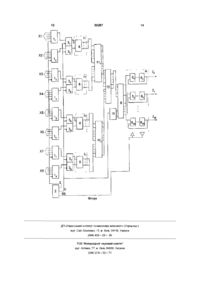

Перетворювач двійково-К-значного коду в двійковий код, який складається з групи п розрядних регістрів зсуву, де п - розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, з генератора імпульсів, з групи п тригерів стану, з накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційного двійкового суматора, виходи якого з'єднані з ВІДПОВІДНИМИ входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами ВІДПОВІДНИХ тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, з багатоканального формувача еквівалентів, кожний канал якого складається з шифратора, входи якого з'єднані з прямими виходами ВІДПОВІДНИХ тригерів стану, з першого, другого і третього комбінаційних суматорів першого і другого ступеня, виходи першого і другого комбінаційних суматорів першого ступеня з'єднані з ВІДПОВІДНИМИ входами першого і другого доданку третього комбінаційного суматора другого ступеня, з підсумовувального лічильника імпульсів і комбінаційного зсувача, керуючі входи якого з'єднані з виходами лічильника імпульсів, підсумовувальний вхід якого з'єднано з прямим виходом генератора імпульсів, який відрізняється тим, що входи першого і другого доданку комбінаційних суматорів першого ступеня з'єднані з ВІДПОВІДНИМИ виходами шифраторів сусідніх каналів та виходи третього комбінаційного суматора другого ступеня з'єднані з ВІДПОВІДНИМИ входами комбінаційного зсувача, виходи якого з'єднані з ВІДПОВІДНИМИ першими входами комбінаційного двійкового суматора в накопичувальному суматорі 1 00 Винахід відноситься до автоматики і обчислювальної техніки і може бути використаний при побудові пристроїв обробки і перетворення інформації Відомий перетворювач двійково-К-значного коду в двійковий код (авт Св СРСР N 1783618 М Кл 5 НОЗМ 7/12, Бюл 47, 1992), вміщуючий групу з п розрядних ЛІЧИЛЬНИКІВ, де п - розрядність перетворюваного коду, генератор імпульсів, першу, другу та третю групи тригерів стану, комбінаційний двійковий суматор і регістр результату, що утворюють в сукупності накопичувальний суматор, першу і другу групи елементів І, першу і другу групу елементів 1І I, групу кодових шифраторів, (п-1)-у -— групу елементів АБО, групу дешифраторів нуля, першу і другу групу дешифраторів перевищення, перший і другій елементи АБО-НІ, формувач еквівалентів, включаючий до свого складу перший, другий і третій дешифратори та шифратор, першу другу і третю групи елементів І, групу елементів АБО Такий перетворювач не забезпечує достатньо високої швидкодії, через наявність трьох кроків (1, а, Ь) перетворення та необхідності подачі N3=] (К1)/Ь [+] (Ь-1)/а [+а імпульсів для перетворення Кзначного коду, а також має значні апаратні витрати при його виготовленні внаслідок ускладнення як операційної частини перетворювача, що зумовлено введенням окрім другого, ще й третього кроку перетворювання, так і особливо ускладненням формувача еквівалентів, що повинен генерувати МЗ = т ( 2 п - 1) + 1 = 3*(2П - 1) + 1 = 1 5*2(2П - 1) + 1 = 1 5*2П+1 - 2 еквівалентів, тобто в 1 5 рази більше, ніж в двокроковому перетворювачі кодів В наведених вище формулах Ь, а, 1 - третій, другий та перший кроки перетворення ВІДПОВІДНО, m - КІЛЬКІСТЬ кроків перетворення Найбільш значною причиною різкого збіль о ю 50287 шення апаратних витрат описаного перетворювача кодів і особливо формувача еквівалентів є зростання КІЛЬКОСТІ еквівалентів у ступені від п (2П), що при великому значенні п та організації формувача еквівалентів у вигляді одного каналу призводить до вказаного вище недоліку Відомий також перетворювач двійково-Кзначного коду в двійковий код (патент України на винахід № 17979А, МІЖ 6 НОЗМ 7/12), вміщуючий групу з n-розрядних регістрів зсуву, де прозрядність перетворюваного коду, генератор імпульсів, групу з (п-1)-го тригера стану, комбінаційний двійковий суматор і регистр результату, що створюють в сукупності накопичувальний суматор, формувач еквівалентів, включаючий в свій склад групу елементів І, групу елементів АБО, шифратор, підсумовувальний лічильник імпульсів, комбінаційний зсувач Описаний перетворювач при наявності чотирьох кроків (1, а, Ь, с) перетворення, де с - четвертий крок перетворення (с = 8, b = 4, а = 2), не забезпечує достатньо високої швидкодії через необхідність подачі N4 = 5 імпульсів при перетворенні К-значних чисел (3 < К < 15) і має великі апаратні витрати, внаслідок того, що формувач еквівалентів організовано у вигляді одного каналу і повинен генерувати М4 = 2П еквівалентів Найбільш близьким по сукупності ознак щодо заявляемого є перетворювач двійково-К-значного коду в двійковий код (заява на патент України на винахід № 2000116848, МІЖ 6 НОЗМ 7/12), який складається з групи п розрядних регістрів зсуву, де n-розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, з генератора імпульсів, з групи п тригерів стану, з накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційного двійкового суматора, виходи якого з'єднані з ВІДПОВІДНИМИ входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами ВІДПОВІДНИХ тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, з багатоканального формувача еквівалентів, кожний канал якого складається з шифратора, входи якого з'єднані з прямими виходами ВІДПОВІДНИХ тригерів стану, з першого, другого і третього комбінаційних суматорів першого і другого ступеня, виходи першого і другого комбінаційних суматорів першого ступеня з'єднані з ВІДПОВІДНИМИ входами першого і другого доданку третього комбінаційного суматора другого ступеня, з підсумовувального лічильника імпульсів і комбінаційного зсувана, керуючі входи якого з'єднані з виходами лічильника імпульсів, підсумовальий вхід якого з'єднано з прямим виходом генератора імпульсів Описаний перетворювач при наявності чотирьох кроків (1, а, Ь, с) перетворення має більш високу швидкодію, бо вимагає для перетворення К-значних чисел (3 < К < 15) N5 = 4 імпульсів, а також має великі апаратні витрати, внаслідок того, що в кожному з Р каналів формувача еквівалентів використовується підсумовувальний лічильник імпульсів і комбінаційний зсувач В основу винаходу поставлено задачу створення такого перетворювача двійково-К-значного коду в двійковий код, в якому нове схемне рішення дозволило б при збереженні швидкодії зменшити його апаратні витрати Такого технічного результату може бути досягнуто, якщо в перетворювач двійково-К-значного коду в двійковий код, який складається з групи п розрядних регістрів зсуву, де n-розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, з генератора імпульсів, з групи п тригерів стану, з накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційного двійкового суматора, виходи якого з'єднані з ВІДПОВІДНИМИ входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами ВІДПОВІДНИХ тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, з багатоканального формувача еквівалентів, кожний канал якого складається з шифратора, входи якого з'єднані з прямими виходами ВІДПОВІДНИХ тригерів стану, з першого, другого і третього комбінаційних суматорів першого і другого ступеня, виходи першого і другого комбінаційних суматорів першого ступеня з'єднані з ВІДПОВІДНИМИ входами першого і другого доданку третього комбінаційного суматора другого ступеня, з підсумовувального лічильника імпульсів і комбінаційного зсувача, керуючі входи якого з'єднані з виходами лічильника імпульсів, підсумовувальий вхід якого з'єднано з прямим виходом генератора імпульсів, ВІДПОВІДНО ДО винаходу входи першого і другого доданку комбінаційних суматорів першого ступеня з'єднати з ВІДПОВІДНИМИ виходами шифраторів сусідніх каналів та виходи третього комбінаційного суматора другого ступеня з'єднати з ВІДПОВІДНИМИ входами комбінаційного зсувана, виходи якого з'єднати з ВІДПОВІДНИМИ першими входами комбінаційного двійкового суматора в накопичувальному суматоРі Введення в відомий перетворювач двійково-Кзначного коду в двійковий код нових зв'язків, а також вилучення в Р-1 каналі комбінаційних зсувачів та підсумовувальних ЛІЧИЛЬНИКІВ імпульсів, дозволило при збереженні попередньої швидкодії перетворення в чотири такти, істотно зменшити його апаратні витрати На фігурі зображена структурна схема перетворювача двійково-К-значного коду в двійковий код при К = 10, п = 8, Р = 4 Перетворювач містить п розрядних регістрів зсуву 1, де n-розрядність перетворювача коду (п = 8), паралельні інформаційні входи яких є входами перетворювача, генератор імпульсів 2, вміщуючий інверсний І (відносно прямого П) та прямий затриманий ПЗ виходи, тригери стану Зі - 3s, накопичу 50287 вальний суматор 4, виконаний з комбінаційного двійкового суматора 5 і регістра 6 результату, чотири канали (Р = 4) формувача еквівалентів 7, що складаються з шифраторів 8і - 84, комбінаційного зсувача 9, підсумовувального лічильника 10, комбінаційних суматорів першого ступеня 11і, 112 і комбінаційного суматора другого ступеня 12 Виходи регістра результату 6, є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційного двійкового суматора 5, виходи якого з'єднані з ВІДПОВІДНИМИ входами регістра результату 6, синхровхід якого з'єднаний з прямим затриманим виходом ПЗ генератора імпульсів 2, інверсний вихід І якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву 1, виходи першого біту розрядних регістрів зсуву 1 з'єднані з інформаційними входами ВІДПОВІДНИХ тригерів стану 3, входи сінхронізацм яких з'єднані з прямим виходом П генератора імпульсів 2 Багатоканальний формувач еквівалентів 7 в кожному каналі (Р = 4) складається з шифратора 8, (і = 1,4), входи якого в кожному каналі з'єднані з прямими виходами ВІДПОВІДНИХ тригерів стану Виходи першого і другого комбінаційних суматорів 11і і 112 першого ступеня з'єднані з ВІДПОВІДНИМИ входами першого і другого доданку третього комбінаційного суматора другого ступеня 12, виходи якого з'єднані з ВІДПОВІДНИМИ першими входами комбінаційного двійкового суматора 5 в накопичуючому суматорі 4, виходи якого є виходами перетворювача Керуючі входи комбінаційного зсувача 9 з'єднані з виходами підсумовувального лічильника 10, під сумову вальний вхід якого з'єднаний з прямим виходом П генератора імпульсів 2 Входи першого і другого доданку комбінаційних суматорів 11і і 112 першого ступеня з'єднані з ВІДПОВІДНИМИ виходами шифраторів 8і - 84 сусідніх каналів Ланцюги ініціювання та скидання на кресленні не наведені Пристрій працює слідуючим чином Якщо в конкретному випадку п = 8, К = 10 Р = 4, то діапазон зміни вхідного коду від 0 до (10 - 1) = 99 999 999ю В перетворювачі, що пропонується, двійковоК-значного коду в двійковий код формувачі еквівалентів, 7і - 74 за допомогою шифраторів 8і - 84, реалізують функції (1) - (4) i = ( K °d + К 1 С 2 ) d (1) 2 3 (2) 5 2 = (К 2 С 3 + К 3 С 4 ) (3) 5 3 = (\^С5 + К 5 С 6 ) S 4 = ( К и С 7 + К'С 8 ), (4) де Ci-Cs - значення (0 або 1) тригерів стану Зі -38 Перетворення коду відбувається за чотири такти Шифратори 8і - 84 в багатоканальному формувачі еквівалентів 7, перетворюють спочатку в першому такті ДВІЙКОВІ КОДИ тригерів стану (Сі.Сг), (Сз,С4), (Сб.Сє), (C7,Cs), відповідаючих значенням першого біта ВІДПОВІДНИХ розрядних регістрів 1 ]-1 з, в другому такті перетворюють ДВІЙКОВІ КОДИ (CI-CS) тригерів стану Зі - 3s, відповідаючих значенням другого біту ВІДПОВІДНИХ розрядних регістрів 11 -18, в третьому такті перетворюють ДВІЙКОВІ КОДИ ( С Г С8)тригерів стану Зі - 3s, відповідаючих значенням третього біту розрядних регістрів 1і - Is в четвертому такті шифратори 8і - 84 перетворюють ДВІЙКОВІ коди (Ci-Cs) тригерів стану Зі - 3s відповідаючих значенням четвертого біту розрядних регістрів І1-І8 Складові еквівалентів, що з'являться на виходах першого та другого шифраторів 8і і 82, третього та четвертого шифраторів 8з і 84 в першому такті будуть підсумовані ВІДПОВІДНО першим 111 та другим 112 комбінаційними двійковими суматорами першого ступеня За допомогою комбінаційного двійкового суматора другого ступеня 12і ДВІЙКОВІ коди з виходів суматорів 111 та 112 будуть складені і далі поступлять на входи комбінаційного зсувана 9, на виходах якого з'явиться накоплена з усіх каналів сума еквівалентів Двійковий код з виходів комбінаційного зсувана 9 буде складений в першому такті з початковою накопленою сумою еквівалентів, яка дорівнює нулю Аналогічні дії будуть виконані далі в другому, третьому та четвертому тактах перетворення, за винятком того, що в другому такті вихідний двійковий вход комбінаційного зсувана 9 буде зсунутий ліворуч на один розряд відносно вхідного коду (перемножений на 2), в третьому такті зсув коду відбудеться ліворуч на два розряди (перемножений на 4), в четвертому такті зсув коду ліворуч буде дорівнювати трьом двійковим розрядам (перемножений на 8) У кожному такті на задньому фронті інверсного імпульсу І ДВІЙКОВІ коди в розрядних регістрах I r i s зсуваються на один розряд (біт) праворуч, а на задньому фронті імпульсу ПЗ чергова сума еквіваленту з виходу комбінаційного зсувача 9 складається з накопиченною сумою еквівалентів, що на попередньому такті була накопичена в суматорі 4 Таким чином накопичена сума еквівалентів на виході комбінаційного зсувача 9 у кожному такті j (j = 1,4) описується виразом (5) (К°С, + К 1 С 2 + К 2 С 3 + К 3 С 4 + К 4 С 5 + К 5 С 6 + К 6 С 7 + К 7 С 8 ) , j = 1, 2(К°С 1 + К 1 С 2 + К 2 С 3 + К 3 С 4 + К 4 С 5 + К 5 С 6 + К 6 С 7 + К 7 С 8 ) , j = 2, 4(К°С 1 + К 1 С 2 + К 2 С 3 + К 3 С 4 + К 4 С 5 + К 5 С 6 + К 6 С 7 + К 7 С 8 ) , j = 3, (5) 8(К°С 1 + К 1 С 2 + К 2 С 3 + К 3 С 4 + К 4 С 5 + К 5 С 6 + К 6 С 7 + К 7 С 8 ) , j = 4, Після чотирьох тактів в накопичуючому суматорі 4 буде знаходиться двійковий код перетворенного числа, в розрядних регістрах 1i-1s після чотирьох тактів зсувів будуть знаходиться нулі Розглянемо работу приладу на наступному прикладі Нехай необхідно перетворити восьмирозрядний 10-значний код числа 8 50287 АО = 1001 0111 1000 1001 0100 0111 1 0101 1001 = 97 89 47 59(ю), який знаходиться в розрядних регистрах 1і - Is Формувачі еквівалентів 7і - 1А за допомогою шифраторів 8і - 84, реалізують функції (6) - (9) 1 Si = (10°Сі ° 10 С2) (6) 3 2 33 S2=(10 C3+10 C4) (7) 4 5 (8) S3=(10 C5+10 C6) 66 7 7 S 4 = ( 1 0 С 7 + Ю С 8 ), (9) Перетворення двійкових кодів (Сі,С 2 ), (Сз,С4), (Сб.Сє), (C7,Cs), що можуть приймати в кожній парі чотири значення 00, 0 1 , 10, 11 та ВІДПОВІДНИХ значенням перших біт розрядних регістрів 1і - Is, виконується в ВІДПОВІДНОСТІ з законом функціонуван1 2 3 ня шифраторів 8і - 8 4 (таблиця) Підсумовування двійкових кодів з виходів шифраторів 8і - 84 далі виконується комбінаційними двійковими суматорами першого 11і і 1І2 та другого 12 ступеня За допомогою комбінаційного зсувача 9 двійковий код з виходів суматора 12, або передається без зсуву на ВІДПОВІДНІ виходи комбінаційного зсувача 9 (в першому такті), або зсувається ліворуч на один розряд (у другому такті), або зсувається ліворуч на два розряди (у третьому такті), або зсувається ліворуч н а т р и розряди (у четвертому такті) Сума еквівалентів на виході комбінаційного зсувача 9 обчислюється за виразом (10) 4 5 6 7 + 1 0 С 2 + 1 0 С 3 + 1 0 С 4 + 1 0 С 5 + 1 0 С 6 + 1 0 С 7 + 1 0 С 8 ) , j = 1, 2 ( 1 0 0 C 1 + 1 0 1 C 2 + 1 0 2 C 3 + 1 0 3 C 4 + 1 0 4 C 5 + 1 0 5 C 6 + 1 0 6 C 7 + 1 0 7 C 8 ) , j = 2, 4 ( 1 0 ° C 1 + 1 0 1 C 2 + 1 0 2 C 3 + 1 0 3 C 4 + 1 0 4 C 5 + 1 0 5 C 6 + 1 0 6 C 7 + 1 0 7 C 8 ) , j = 3, 0 1 2 3 4 5 6 (10) 7 8(10 C1+10 C2+10 C3+10 C4+10 C5+10 C6+10 C7+10 C8),j = 4 де j - номер такту перетворення Підсумовувальний лічильник 10 перед початком перетворення повинен бути встановлений в початковий стан 1 1 2 Запис інформації в регістри тригерів стану Зі 3s виконується перепадом 0 - 1 прямого імпульсу П генератора імпульсів 2, зсув інформації в розрядних регістрах 11 — 1 в виконується перепадом 0-1 інверсного імпульсу І (тобто по задньому фронту імпульсу П) та запис інформації в регістр результату 6 накопичувального суматора 4 виконується перепадом 1 - 0 імпульсу з прямого затриманого виходу ПЗ генератора 2 З приходом переднього фронту першого імпу льсу на прямому виході П генератора 2 значення сигналу на цьому виході зміниться з 0 на 1, що дозволить занесення коду числа (усіх перших біт) Cs-Ci в тригери регістрів стану 3s - Зі (С 8 ,С 7 = 1 1 , 06,05 = 0 1 , С 4 ,Сз = 0 1 , С 2 ,Сі = 11) В результаті цього коди перших біт числа Ао надійдуть по два розряди (С 2 ,Сі), (С 4 ,С 3 ), (С 6 ,С 5 ), (Cs.Cy) ВІДПОВІДНО на входи шифраторів 8-і - 84 і перетворяться на складові еквівалентів Si(C2,C-i) = 1011 = 11 ю, S 2 (C 4 ,C 3 ) = 0110 0100 = ЮОю, S 3 (C 6 ,C 5 ) = 0010 0111 0001 0000 = 10 ОООю, S 4 (C 8 ,C 7 ) = 1010 0111 1101 1000 1100 0000 = 11 000 ОООю 50287 10 Таблиця Значення Значення Значення Значення Десятковий Двійковий код еквіваленту четвергах третіх других перших код Значення вихідних розрядів біт біт біт біт еквіваленту У24-У1 С8С7 С6С5 С4СЗ С2С1 S 10 00 00 00 00 0 00 00 00 01 1 000000000000000000000001 00 00 00 І0 10 000000000000000000001010 00 00 00 11 11 000000000000000000001011 00 00 00 00 0 00 00 01 00 100 00 00 1 0 00 1000 00 0 0 1 1 0 0 1100 00 00 00 0 0 0 00 01 00 00 10000 00 10 00 00 100000 00 11 00 00 110000 00 00 00 00 0 01 00 00 00 1000000 10 00 00 00 10000000 оооооооооооооооооооооооо 000000000000000001100100 000000000000001111101000 000000000000010001001100 оооооооооооооооооооооооо 000000000010011100010000 000000011000011010100000 000000011010110110110000 оооооооооооооооооооооооо 000011110100001001000000 100110001001011010000000 11 00 00 00 11000000 10ІО0І111101100011000000 Стан підсумовувального лічильника 10 з приходом переднього фронту першого імпульсу з виходу П зтшиться з 11 на 00 Комбінаційний двійковий суматор 111 в результаті додавання складових еквівалентів Si(C2,C-i) = 11 іо і S2 = 100-ю видасть на виходах двійковий код числа 111-ю, що надійде на входи першого доданку третього комбінаційного суматора 12 Комбінаційний двійковий суматор першого ступеня 112 в результаті додавання складових еквіваленту S31 S4 видасть на виході двійковий код числа 11 010 000-ю, що надходить на входи другого доданку третього комбінаційного суматора 12 В результаті додавання чисел 111 ю і 11 010 000-ю третім комбінаційним двійковим суматором 12 на його виходах утвориться двійковий код числа 11 24 1 000000000000000000000000 010 111 ю, що надходить далі на входи комбінаційного зсувача 9 і на його виходи і далі на входи накопичувального суматора 4 Задній фронт прямого затриманого імпульсу ПЗ з виходу генератора 2 виробить запис результату складання з виходів комбінаційного двійкового суматора 5 в регістр результату 6 Двійковий код числа 11 010 111ю з'явиться також і на виходах перетворювача З приходом переднього фронту другого прямого імпульсу на прямому виході П генератора 2 значення сигналу на цьому виході зміниться з 0 на 1, що дозволить занесення коду числа Ао (усіх других біт із-за зсуву на один біт праворуч першим інверсним імпульсом І) в тригери Cs - Сі регістрів стану 3 8 - Зі С8С7 = 01, С6С5 = 00, С4С3 = 01,С2Сі = 00 11 В результаті цього ДВІЙКОВІ КОДИ других біт числа Ао по два разряди ((Сг.С-і), (С4,Сз), (Сб,С5),(С8,С7)) надійдуть ВІДПОВІДНО на входи шифраторів 8-і - 84 і перетворяться на складові еквівалентів S i ( C 2 l C i ) = 0ю, S 2 (C 4 ,C 3 ) = ЮОю, S 3 (C 6 ,C 7 ) = Ою S 4 (C8,C 7 ) = 1 000 ОООю Ці складові за допомогою комбінаційних суматорів 111 112 і 12 будуть складені, внаслідок чого на виходах комбінаційного суматора 12 з'явиться двійковий код числа 1 000 ЮОю, яке за допомогою комбінаційного зсувача 9 буде збільшено в 2 рази Таким чином з виходу комбінаційного зсувача 9 на входи накопичувального суматора 4 надійде у другому такті еквівалент 2 000 200-ю, що буде складений за допомогою накопичувального суматора 4 з накопленою сумою еквівалентів на попередньому (першому) такті 11 010 111 ю Результат цього додавання 13 010 311 ю з приходом заднього фронту другого прямого затриманого імпульсу ПЗ з виходу генератора 2 буде занесено в регістр результату 6 Задній фронт другого інверсного імпульсу з виходу І генератора 2, ще до занесення результату в регістр 6, виконає зсув праворуч на один розряд числа А1о = 0100 0011 0100 0100 0010 0011 0010 0100, в результаті цього в розрядних регистрах 1s - 1-і, буде знаходиться число А11о = 0010 0001 0010 0010 0001 0001 0001 0010, тобто на МІСЦІ перших біт будуть знаходиться треті біти з вагою 4 З приходом переднего фронту третього прямого імпульсу з виходу П генератора 2 в тригери Cs - Сі регістрів стану Зз - Зі буде записане число С 8 С 7 = 0 1 , С 6 С 5 = 00, С 4 С 3 = 11 ,С 2 Сі = 10 В результаті цього за допомогою шифраторів 8і - 8 4 на їх виходах будуть сформовані ДВІЙКОВІ коди чисел Si = 10-ю, S2 = 1 ЮОю, S3 = 0ю, S 4 = 1 000 ОООю Після підсумовування комбінаційними суматорами 11-І 112, і 12 на виходах суматора 12 одержимо двійковий код числа 1 001 ЮОю Внаслідок того, що третій прямий імпульс з виходу П генератора 2 змінив стан підсумовувального лічильника з 012 на Юг, комбінаційний зсувач 9 збільшить значення числа 1 001 ЮОю У чотири рази, тобто на виходах зсувача матимемо двійковий код числа 4 004 ЮОю, яке буде складено з попередньою накопиченою сумою еквівалентів 13 010 311-ю Задній фронт третього прямого затриманого імпульсу з виходу ПЗ генератора 2 виконає запис 50287 12 результату складання цих чисел, тобто числа 17 014 751 іо в регістр 6 результату Задній фронт третього інверсного імпульсу з виходу І генератора 2, ще до занесення результату в регістр 6, виконає зсув праворуч на один розряд числа А11о = 0010 0001 0010 0010 0001 0001 0001 0010, в результаті чого в розрядних регістрах Із - 1і, буде знаходитись число А 1 1 0 = 0001 0000 0001 0001 0000 0000 0000 0001 З приходом переднього фронту четвертого прямого імпульсу з виходу П генератора 2 в тригери Cs - Сі, регістрів стану Зз - Зі буде записане число С 8 С 7 = 10С 6 С 5 = 1 1 , С 4 С 3 = 00, С 2 Сі = 01 В результаті коди четвертих біт числа Ао по два розряди (С 2 ,Сі), (С 4 ,С 3 ), (С 6 ,С 5 ), (С 8 ,С 7 ) надійдуть ВІДПОВІДНО на входи шифраторів 8і - 8 4 і перетворяться на складові еквівалентів S 1 i = 1ю, S12 = Ою, S 1 3= 110 ОООю, S 1 4 = 10 000 ОООю Після підсумовування цих складових комбінаційними суматорами 11і, 112, і 12 на виходах суматора 12 одержимо двійковий код числа 10 110 001 ю, який надійде на входи комбінаційного зсувана 9 Внаслідок того, що четвертий прямий імпульс П змінив стан підсумовувального лічильника з 10г на 112, комбінаційний зсувач 9 збільшить значення числа 1 001 ЮОю У ВІСІМ разів Таким чином на виходах комбінаційного зсувача 9 ВІДПОВІДНО матимемо загальний еквівалент 80 880 008ю Цей загальний еквівалент 80 880 008ю буде додано до накоплено! суми еквівалентів, що залишилася в регістрі результату 6 з третього такту 17 014 751ю Результат цього додавання число 97 894 759ю з приходом заднього фронту четвертого прямого затриманого імпульсу з виходу ПЗ регістра 2 буде занесено в регістр результату 6 накопичувального суматора 4 Двійковий код числа 97 894 759ю з'явиться також і на виходах перетворювача На цьому процесі перетворення закінчується Четвертий інверсний імпульс з виходу І генератора 2 призведе до повного обнуления розрядних регістрів І з - 1і Перед кожним наступним перетворенням необхідно обнулити регістр результату 6 і виконати запис перетворюваного Кзначного числа в розрядні регістри 1 з - 11 Швидкодія пристрою, що пропонується, не залежить від розрядності перетворюваного коду і для 8 < К < 16 не перевищує чотирьох тактів 50287 13 14 71 X2 72 1 2 X5 1 0 7з 8 "29 • xe 1 1 . X7 74 8 • X8 пз Фігура ДП «Український інститут промислової власності» (Укрпатент) вул Сім'ї Хохлових, 15, м Київ, 04119, Україна ( 0 4 4 ) 4 5 6 - 2 0 - 90 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)216-32-71

ДивитисяДодаткова інформація

Назва патенту англійськоюConverter for converting binary-coded k characters into binary code

Автори англійськоюKachurin Mykola Yakovych, Lopukhin Yurii Volodymyrovych, Lopukhin Yaroslav Yuriiovych, Makarenko Hanna Mykolaivna, Shtets Leonid Kostiantynovych

Назва патенту російськоюПреобразователь двоично-k-знакового кода в двоичный код

Автори російськоюКачурин Николай Яковлевич, Лопухин Юрий Владимирович, Лопухин Ярослав Юрьевич, Макаренко Анна Николаевна, Штец Леонид Константинович

МПК / Мітки

МПК: H03M 7/02

Мітки: код, перетворювач, двійково-к-значного, коду, двійковий

Код посилання

<a href="https://ua.patents.su/7-50287-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду в двійковий код</a>

Попередній патент: Шворневий вузол

Наступний патент: Спосіб одержання хлорпохідних етилену

Випадковий патент: Пристрій ортопедичний "данстеф"