Програмований логічний контролер

Номер патенту: 82759

Опубліковано: 12.05.2008

Автори: Фурман Ілля Олександрович, Малиновський Михайло Леонідович, Філіппович Валерій Петрович, Кулик Петро Дем'янович

Формула / Реферат

Програмований логічний контролер, що містить блок індикації, блок аналізу ситуацій і блок пам'яті команд, причому перший вихід блока аналізу ситуацій підключений до входу блока індикації, який відрізняється тим, що в нього введений блок пам'яті поточних станів, перетворювач форми вхідних сигналів, перетворювач форми вихідних сигналів, вихід якого є виходом пристрою, перший вхід пристрою підключений до перетворювача форми вхідних сигналів, вихід якого підключений до першого входу блока аналізу ситуацій, другий вихід блока аналізу ситуацій підключений до першого входу блока пам'яті поточних станів, другий вхід якого підключений до другого входу пристрою, вихід блока пам'яті поточних станів підключений до другого входу блока аналізу ситуацій та входу блока пам'яті команд, вихід якого підключений до перетворювача форми вихідних сигналів.

Текст

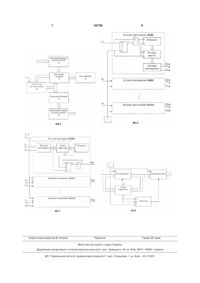

Програмований логічний контролер, що містить блок індикації, блок аналізу ситуацій і блок пам'яті команд, причому перший вихід блока аналізу ситуацій підключений до входу блока індикації, який відрізняється тим, що в нього введений блок пам'яті поточних станів, перетворювач форми вхідних сигналів, перетворювач форми вихідних сигналів, вихід якого є виходом пристрою, перший вхід пристрою підключений до перетворювача форми вхідних сигналів, вихід якого підключений до першого входу блока аналізу ситуацій, другий вихід блока аналізу ситуацій підключений до першого входу блока пам'яті поточних станів, другий вхід якого підключений до другого входу пристрою, вихід блока пам'яті поточних станів підключений до другого входу блока аналізу ситуацій та входу блока пам'яті команд, вихід якого підключений до перетворювача форми вихідних сигналів. Винахід належить до автоматики, а точніше до пристроїв програмно-логічного керування об'єктами дискретної циклічної дії. Відомий програмований логічний контролер [Пат. 39306 Україна, G05B19/18/ Заявл. 10.02.2000; Опубл. 15.10.2002. Бюл. №10], що містить блок індикації, схему порівняння, блок логічного керування, блок пам'яті станів, лічильник адреси, блок пам'яті переходів, блок пам'яті команд, причому перший (установлюючий) вхід лічильника адреси є першим входом пристрою, інформаційний вихід лічильника адреси підключений до адресних входів блоків пам'яті станів та команд а також до першого входу блока індикації, другий вхід якого з'єднаний з першим виходом схеми порівняння, перший вхід якої з'єднаний з інформаційним виходом блоку пам'яті станів, другий вхід схеми порівняння є другим входом пристрою, виходом якого є перший (інформаційний) вихід блока пам'яті команд, адресний вхід блока пам'яті переходів з'єднаний з другим входом пристрою, а перший (інформаційний) його вихід підключений до другого входу лічильника адреси, третій та четвертий входи якого підключені відповідно до першого та другого виходу вузла логічного керування, перший вхід якого з'єднаний з другим виходом блока пам'яті команд, а другий та третій входи вузла логічного керування підключені відповідно до другого виходу схеми порівняння та до другого виходу блока пам'яті переходів. Відоме рішення забезпечує програмне керування об'єктами як з детермінованою, так і з випадковою послідовністю виконуваних операцій, але характеризується двома серйозними недоліками. Перший недолік складається у тому, що в даному пристрої відсутня можливість обробки інформації, представленої у вигляді імпульсних сигналів, застосовуваних з метою забезпечення безпеки (наприклад, у системах автоматики на залізничному транспорті та інших системах критичного застосування). Другий недолік складається у тому, що даний пристрій не забезпечує можливість використання в якості ознаки сигналів їх частоти для представлення інформації як на вході, так і на виході пристрою. Найбільш близьким по сукупності ознак до пропонованого винаходу є програмований логічний контролер [Пат. 56476 Україна, G05B19/18/; Заявл. 11.06.2002; Опубл. 15.09.2004. Бюл. №9], що містить блок індикації, блок аналізу ситуацій, (19) UA (11) 82759 (13) C2 (21) a200608437 (22) 27.07.2006 (24) 12.05.2008 (46) 12.05.2008, Бюл.№ 9, 2008 р. (72) МАЛИНОВСЬКИЙ МИХАЙЛО ЛЕОНІДОВИЧ, UA, КУЛИК ПЕТРО ДЕМ'ЯНОВИЧ, UA, ФІЛІППОВИЧ ВАЛЕРІЙ ПЕТРОВИЧ, UA, ФУРМАН ІЛЛЯ ОЛЕКСАНДРОВИЧ, UA (73) ТОВАРИСТВО З ОБМЕЖЕНОЮ ВІДПОВІДАЛЬНІСТЮ НАУКОВО-КОМЕРЦІЙНЕ ПІДПРИЄМСТВО "УКРТРАНССИГНАЛ", UA (56) UA 39306 C2, 15.10.2002 UA 56476 A, 15.05.2003 UA 71200 A, 15.11.2004 SU 1721587 A1, 23.03.1992 RU 2117977 C1, 20.08.1998 KR 20040056253, 30.06.2004 3 блок пам'яті команд, причому вихід блоку аналізу ситуацій підключений до входу блоку індикації, у якому цілком усунутий перший недолік аналога: інформація на вході та на виході пристрою представлена у вигляді імпульсних сигналів, що забезпечує достовірний контроль як вхідного потоку інформації, так і результатів його логічної обробки, у наслідок чого гарантується безпечне сполучення пристрою з виконавчими об'єктами. Причини, що перешкоджають досягненню прототипом очікуваного технічного результату, полягають у наступному: контролер забезпечує обробку інформації, що представлена у вигляді імпульсних сигналів певної частоти, які синхронізуються із глобальним тактовим сигналом. В наслідок цього відсутня можливість обробки несинхронізованих імпульсних сигналів, в яких значення частоти характеризує стани виконавчих об'єктів, в яких вони знаходяться (для вхідних сигналів) або в які вони повинні перейти (для вихідних сигналів), що суттєво зменшує функціональні можливості контролера. В основу винаходу поставлена задача вдосконалення програмованого логічного контролера шляхом введення додаткових елементів і зв'язків між ними, що забезпечують підвищення функціональних можливостей контролера за рахунок використання вхідних та вихідних несинхронізованих сигналів з різними частотами для контролю станів та формування рішень з керування виконавчими механізмами. Реалізація поставленої задачі досягається тим, що в програмований логічний контролер, що містить блок індикації, блок аналізу ситуацій і блок пам'яті команд, причому перший вихід блоку аналізу ситуацій підключений до входу блоку індикації, відповідно до винаходу введений блок пам'яті поточних станів, перетворювач форми вхідних сигналів і перетворювач форми вихідних сигналів, вихід якого є виходом пристрою, перший вхід пристрою підключений до перетворювача форми вхідних сигналів, вихід якого підключений до першого входу блоку аналізу ситуацій, другий вихід блоку аналізу ситуацій підключений до першого входу блоку пам'яті поточних станів, другий вхід якого підключений до другого входу пристрою, вихід блоку пам'яті поточних станів підключений до другого входу блоку аналізу ситуацій та входу блоку пам'яті команд, вихід якого підключений до перетворювача форми вихідних сигналів. На Фіг.1 наведена блок-схема пропонуємого пристрою; на Фіг.2 наведена функціональна схема перетворювача вхідних сигналів; на Фіг.3 наведена функціональна схема перетворювача вихідних сигналів; на Фіг.4 наведена функціональна схема блоку пам'яті поточних станів. Пристрій містить блок пам'яті поточних станів 1, перетворювач форми вхідних сигналів 2, блок аналізу ситуацій 3, блок пам'яті команд 4, перетворювач форми вихідних сигналів 5, блок індикації 6, причому перший вихід блоку аналізу ситуацій 3 підключений до входу блоку індикації 6, вихід перетворювача форми вихідних сигналів 5 є виходом пристрою, перший вхід пристрою підключений до перетворювача форми вхідних сигналів 2, вихід 82759 4 якого підключений до першого входу блоку аналізу ситуацій 3, другий вихід блоку аналізу ситуацій 3 підключений до першого входу блоку пам'яті поточних станів 1, другий вхід якого підключений до другого входу пристрою, вихід блоку пам'яті поточних станів 1 підключений до другого входу блоку аналізу ситуацій 3 та входу блоку пам'яті команд 4, вихід якого підключений до перетворювача форми вихідних сигналів 5. Блок аналізу ситуацій 3 і блок пам'яті команд 4 призначені для збереження програми керування роботою обслуговуємого об'єкта, яка являє собою набір логічних рівнянь і складається з двох частин: 1) комбінації команд на включення та вимикання виконавчих механізмів (записується в блок пам'яті команд 4), 2) комбінації станів, у які повинний перейти пристрій у наступному такті роботи в залежності від його поточного стану і стану зовнішнього середовища (записується в блок аналізу ситуацій 3). Інформація про поточні стани пристрою зберігається в блоці пам'яті поточних станів 1. Блок індикації 6 призначений для відображення інформації про поточний стан пристрою та очікуваний стан датчиків. Перетворювач форми вхідних сигналів 2 забезпечує формування векторів двійкових сигналів у відповідності до комбінації частот вхідних сигналів, які поступають на інформаційні входи пристрою. Перетворювач форми вихідних сигналів 5 забезпечує формування імпульсних сигналів з частотами, які відповідають вектору двійкових сигналів, що формуються на виході блоку пам'яті команд 4. Реалізація пропонованого пристрою можлива, наприклад, з використанням стандартних програмованих логічних інтегральних схем (ПЛІС) [див. Стешенко В.Б. ПЛИС фирмы ALTERA: проектирование устройств обработки сигналов. - М.: ДОДЭКА, 2000. - 128с.]. В якості блока індикації можливе використання стандартних елементів індикації. Програмований логічний контролер працює таким чином. Встановлення його в початковий стан здійснюється за допомогою зовнішнього імпульсу початкової установки ПУ, що обнуляє блок пам'яті поточних станів. Інформація про стани виконавчих механізмів у вигляді імпульсних сигналів подається на вхід перетворювача форми вхідних сигналів, причому кількість різних частот, з якими кожний імпульсний сигнал може поступати на вхід пристрою, дорівнює кількості станів, в яких може знаходитись відповідний виконавчий механізм. Таким чином, кожна з цих частот відповідає одному з можливих станів відповідного виконавчого механізму. Перетворювач вхідних сигналів (Фіг.2) містить набір вхідних перетворювачів ВхП1, ВхП2, ... ВхПm, кількість яких дорівнює кількості вхідних сигналів fвх1, fвх2, ... fвхm , а також тактовий генератор Г. Кожний з вхідних перетворювачів ВхПі містить: - D-тригер, який спільно з логічним елементом «І» фіксує момент формування переднього фронту 5 імпульсного сигналу fax; (момент переходу вхідного сигналу з «0» у «1»), - лічильник, який фіксує кількість імпульсів тактового генератора, що надішли на вхід С за час, що дорівнює періоду сигналу fвхi, - регістр пам'яті, який фіксує двійкове число, що відповідає періоду сигналу fвхi; (або кількості імпульсів, що надішли на вхід С лічильника), - логічний перетворювач, який формує на виході вектор двійкових сигналів xi1, хi2, ... xjn, які приймають значення «0» або «1» у відповідності до значення періоду сигналу fax;, яке зберігається у регістрі пам'яті. Сигнали з виходу перетворювача форми вхідних сигналів поступають на входи блоку аналізу ситуацій. У результаті рішення логічних рівнянь на виході блоку аналізу ситуацій формуються сигнали, які надходять на входи блоку пам'яті поточних станів. Блок пам'яті поточних станів (Фіг.4) виконує функції багаторазової перевірки правильності прийняття керуючих рішень та зберігання інформації про поточний стан пристрою. Блок пам'яті поточних станів містить: - регістр пам'яті 1, який фіксує значення сигналів, що поступають на вхід блоку, - схему порівняння, яка фіксує момент зміни значень вхідних сигналів, - лічильник, який забезпечує підрахунок кількості тактів, на протязі яких не відбувається зміна значень вхідних сигналів, - регістр пам'яті 2, який фіксує значення вхідних сигналів після їх багаторазової перевірки, - тактовий генератор Г. Блок пам'яті поточних станів працює таким чином. При зміні значень вхідних сигналів на виході Е схеми порівняння з'являється логічний «0», що зберігається до приходу наступного переднього фронту сигналу синхронізації та запису нових значень вхідних сигналів у регістр пам'яті 1. З виходу Е схеми порівняння сигнал логічного «0» поступає на вхід Е лічильника, що забороняє подальший підрахунок імпульсів тактового генератора, а також на вхід R лічильника, де він інвертується та забезпечує скид лічильника. Після формування переднього фронту сигналу синхронізації оновлюється інформація, яка записана у регістр пам'яті 1, на виході Е схеми порівняння з'являється логічна 82759 6 «І», яка поступає на вхід Е лічильника і дозволяє підрахунок тактових імпульсів. Якщо надалі інформація на вході блоку не змінюється, після надходження заданої кількості тактових імпульсів на вхід С лічильника, на його виході Q з'являється сигнал логічної «І», який поступає на вхід Е регістра пам'яті 2. При надходженні чергового переднього фронту сигналу синхронізації інформація з виходу регістру пам'яті 1 записується до регістра пам'яті 2 і поступає на вихід блоку. З виходу блоку пам'яті поточних станів інформація за колом зворотного зв'язку поступає на вхід блоку аналізу ситуацій, а також на вхід блоку пам'яті команд. Після рішення логічних рівнянь інформація з виходу блоку пам'яті команд поступає на вхід перетворювача форми вихідних сигналів (Фіг.3), який містить набір вихідних перетворювачів ВихП1, ВихП2, ... ВихПh, кількість яких дорівнює кількості вихідних сигналів fвих1, fвих2, ... fвихh, а також тактовий генератор Г. Кожний вихідний перетворювач ВихПі містить: - логічний перетворювач, який, в залежності від комбінації вхідних сигналів Zi1, Zi2, ... Zik формує двійкове число, що відповідає періоду вихідного сигналу fвихі, - лічильник, який забезпечує підрахунок кількості тактових сигналів, що надходять з виходу тактового генератора Г на його вхід С, - схему порівняння, яка перевіряє на еквівалентність число, що формується на виході логічного перетворювача та відповідає заданому періоду вихідного сигналу fвихi а також число, яке формується на виході лічильника, - D-тригер, який сумісно з інвертором забезпечує формування імпульсів на виході перетворювача. Сигнали з виходів перетворювача форми вихідних сигналів поступають до виконавчих механізмів, причому частота вихідного сигналу fвихi, відповідає стану і-го виконавчого механізму, в якому він повинен знаходитись. Пропонуємий пристрій може бути використаний для програмно-логічного керування об'єктами залізничної автоматики, наприклад, стрілками та сигналами світлофорів, а також іншими об'єктами критичного застосування. 7 Комп’ютерна верстка В. Клюкін 82759 8 Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюProgrammed logical controller

Автори англійськоюMalynovskyi Mykhailo Leonidovych, Kulyk Petro Demianovych, Filipovych Valerii Petrovych, Furman Illia Oleksandrovych

Назва патенту російськоюПрограммируемый логичный контроллер

Автори російськоюМалиновский Михаил Леонидович, Кулик Петр Демьянович, Филиппович Валерий Петрович, Фурман Илья Александрович

МПК / Мітки

МПК: G05B 19/18

Мітки: програмований, контролер, логічний

Код посилання

<a href="https://ua.patents.su/4-82759-programovanijj-logichnijj-kontroler.html" target="_blank" rel="follow" title="База патентів України">Програмований логічний контролер</a>

Попередній патент: Пристрій регулювання витрати пиловугільного палива

Наступний патент: Спосіб визначення питомої ефективної витрати рідкого палива дизеля

Випадковий патент: Спосіб приготування розчину флокулянту в цукровому виробництві